第11章 DSP串行通信接口SCI

- 格式:ppt

- 大小:68.00 KB

- 文档页数:5

串行通信分为同步通信和异步通信。

串行通信接口都具有发送引脚TXD和接收引脚RXD,它们是TTL平电。

如果要利用这两个引脚与外界实行异步通信,必须将TTL电平转化为RS-232电平。

SCI是一种全双工异步串行通信接口,主要用于MCU与其他计算机或设备之间的通信,几个独立的MCU也能通过SCI实现串行通信,形成网络。

从编程角度看,先设定好波特率,通信格式,是否校验,是否允许中断等。

接着发送数据时,先检查相应的标志位是否允许发送数据,如果可以,则把数据放入SCI数据寄存器即可,剩下的工作芯片自动完成:将数据从SCI数据寄存器送到发送移位寄存器,硬件驱动将发送移位寄存器里的数据按规定发送到发送引脚TXD,供对方接收。

接收时,数据逐位从接收引脚RXD进入到接收移位寄存器,当收到一个完整字节时,芯片会自动将数据送到SCI数据寄存器,并置相应的标志位,我们就可以根据标志位的情况来读取数据了。

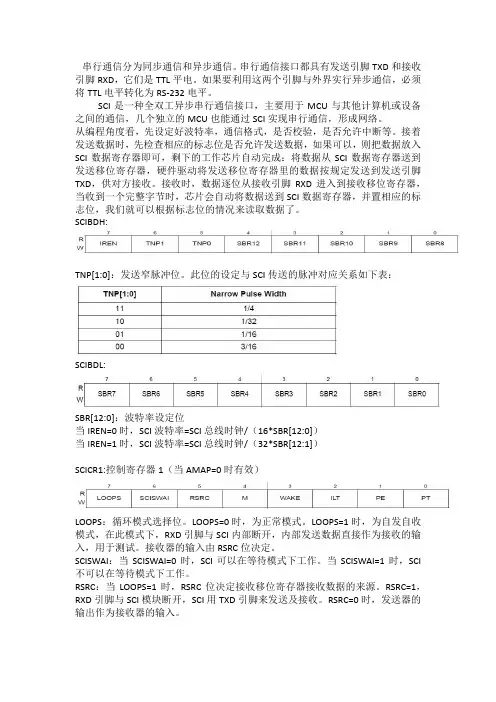

SCIBDH:TNP[1:0]:发送窄脉冲位。

此位的设定与SCI传送的脉冲对应关系如下表:SCIBDL:SBR[12:0]:波特率设定位当IREN=0时,SCI波特率=SCI总线时钟/(16*SBR[12:0])当IREN=1时,SCI波特率=SCI总线时钟/(32*SBR[12:1])SCICR1:控制寄存器1(当AMAP=0时有效)LOOPS:循环模式选择位。

LOOPS=0时,为正常模式。

LOOPS=1时,为自发自收模式,在此模式下,RXD引脚与SCI内部断开,内部发送数据直接作为接收的输入,用于测试。

接收器的输入由RSRC位决定。

SCISWAI:当SCISWAI=0时,SCI可以在等待模式下工作。

当SCISWAI=1时,SCI 不可以在等待模式下工作。

RSRC:当LOOPS=1时,RSRC位决定接收移位寄存器接收数据的来源。

RSRC=1,RXD引脚与SCI模块断开,SCI用TXD引脚来发送及接收。

RSRC=0时,发送器的输出作为接收器的输入。

第7章串行通信接口(SCI)目前几乎所有的台式电脑都带有9芯的异步串行通信口,简称串行口或COM口。

有的台式电脑带有两个串行口,分别称为COM1、COM2口。

大部分的笔记本电脑也带有串行口。

随着USB接口的普及,串行口的地位逐渐变低了。

但是,作为设备间的一种简便的通信方式,在相当长的时间内,串行口还不会消失。

因为简单且常用的串行通信只需要三根线(发送线、接收线和地线),所以,串行通信可以作为MCU与外界通信的简便方式之一。

大部分嵌入式MCU都具有串行通信接口(Serial Communication Interface,SCI),掌握SCI的编程是学习MCU的重要内容之一。

本章从掌握规范的SCI基本编程角度讨论串行通信编程,把与芯片型号相关内容和与芯片型号无关内容区别开来,便于读者融会贯通与实际应用。

本章7.1、7.2节是与芯片无关的有关串行通信的通用基础知识,只有理解这些基础知识,才能进行串行通信的应用。

7.3、7.4节阐述GP32芯片的SCI模块的编程方法,在此基础上,重点掌握7.5节给出的编程实例。

注意,在汇编程序中,只有初始化子程序与GP32相关,收发程序在整个08系列中是通用的,在C程序中,只有初始化子程序与GP32相关,收发程序对任何芯片是通用的。

当然,要注意头文件SCI.h相关位的定义。

关于串口程序的测试,最好利用教学资料中提供的PC机方的高级语言源程序进行。

根据自己对高级语言的熟悉程度选用VB、C#、VC或其他高级语言。

实际上,掌握一门PC机方的高级语言编程对嵌入式系统开发是必要的。

7.1异步串行通信的基础知识本节简要概括了串行通信中的通常使用的相关基本概念,为学习MCU的串行接口编程做准备。

对于已经了解这方面知识的读者,可以略读本节。

7.1.1基本概念“位”(bit)是单个二进制数字的简称,是可以拥有两种状态的最小二进制值,分别用“0”和“1”表示。

在计算机中,通常一个信息单位用8位二进制表示,称为一个“字节”(byte)。

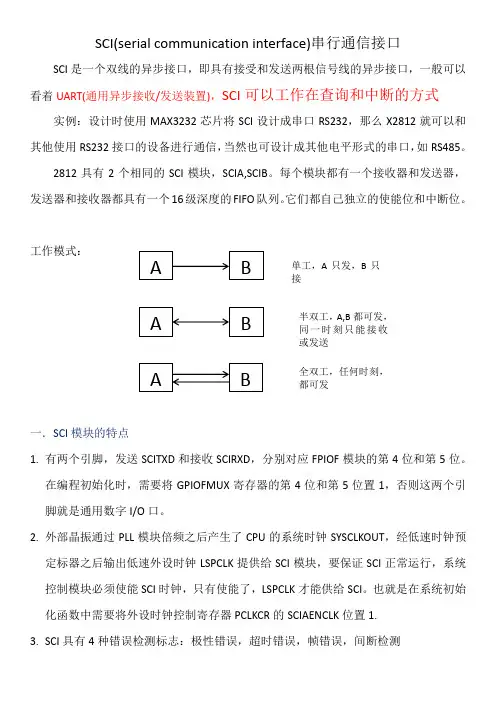

SCI(serial communication interface)串行通信接口SCI 是一个双线的异步接口,即具有接受和发送两根信号线的异步接口,一般可以看着UART(通用异步接收/发送装置),SCI可以工作在查询和中断的方式实例:设计时使用MAX3232芯片将SCI 设计成串口RS232,那么X2812就可以和其他使用RS232接口的设备进行通信,当然也可设计成其他电平形式的串口,如RS485。

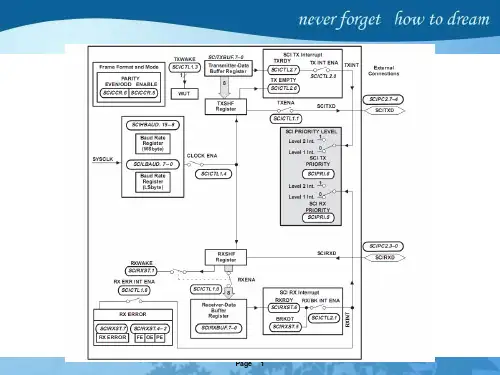

2812具有2个相同的SCI 模块,SCIA,SCIB 。

每个模块都有一个接收器和发送器,发送器和接收器都具有一个16级深度的FIFO 队列。

它们都自己独立的使能位和中断位。

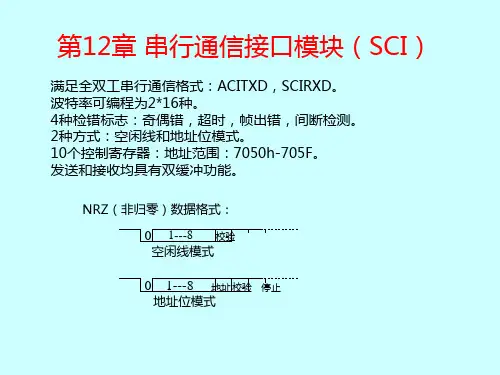

工作模式:一.SCI 模块的特点1. 有两个引脚,发送SCITXD 和接收SCIRXD ,分别对应FPIOF 模块的第4位和第5位。

在编程初始化时,需要将GPIOFMUX 寄存器的第4位和第5位置1,否则这两个引脚就是通用数字I/O 口。

2. 外部晶振通过PLL 模块倍频之后产生了CPU 的系统时钟SYSCLKOUT ,经低速时钟预定标器之后输出低速外设时钟LSPCLK 提供给SCI 模块,要保证SCI 正常运行,系统控制模块必须使能SCI 时钟,只有使能了,LSPCLK 才能供给SCI 。

也就是在系统初始化函数中需要将外设时钟控制寄存器PCLKCR 的SCIAENCLK 位置1.3. SCI 具有4种错误检测标志:极性错误,超时错误,帧错误,间断检测A A ABB B单工,A 只发,B 只接半双工,A,B 都可发,同一时刻只能接收或发送全双工,任何时刻,都可发4.具有双缓冲接收和发送功能,接收缓冲寄存器位SCIRXBUF,发送缓冲寄存器为SCITXBUF。

独立的发送器和接收器使得SCI可以工作于半双工或全双工5.可以产生两个中断:SCIRXINT和SCITXINT,即接收中断和发送中断,SCI模块具有独立的发送中断使能位和接收中断使能位,发送和接收可以通过中断方式实现,也可以查询中断方式是实现6.在多处理器模式下,SCI模块具有两种唤醒方式:空闲线方式和地址位方式。

SCI(Serial Communication Interface),即串行通信接口,是一个双线的异步串口,即具有接收和发送两根信号线的异步串口,一般可以看作是UART(通用异步接收/发送装置)。

2812的SCI模块支持CPU与采用NRZ(non-return-to-zero 不归零)标准格式的异步外围设备之间进行数字通信。

如果设计时我们的SCI使用的是RS232串行接口,那么,2812就能和其他使用RS232接口的设备进行通信。

例如2812内部的两个SCI之间,或者2812的SCI 和其他DSP的SCI之间均能实现通信。

2812内部具有两个相同的SCI模块,SCIA和SCIB,每一个SCI模块都各有一个接收器和发送器。

SCI的接收器和发送器各具有一个16级深度的FIFO(First in fist out 先入先出)队列,它们还都有自己独立的使能位和中断位,可以在半双工通信中进行独立的操作,或者在全双工通信中同时进行操作。

一. 2812-SCI模块SCI模块具有两个引脚,SCITXDA和SCIRXDA,分别实现发送数据和接收数据的功能,这两个引脚对应于GPIOF模块的第4和第5位,在编程初始化的时候,需要将GPIOFMUX寄存器的第4和第5位置为1,才能使得这两个引脚具有发送和接收的功能。

SCIA可以产生两个中断,SCIRXINTA和SCITXINTA,即发送中断和接收中断。

二. SCI模块的特点1 -- 具有4个错误检测标志:极性(parity)、溢出(overrun)、帧(framing)、中断(break)检测。

2 -- 多处理器模式下具有两种唤醒方式:空闲线方式和地址位方式。

通常使用的时候很少遇到多处理器模式,我们采用的是空闲线方式。

3 -- 通信工作于半双工或者全双工模式。

4 -- 具有双缓冲接收和发送功能,接收缓冲寄存器为SCIRXBUF,发送缓冲寄存器为SCITXBUF。

5 -- 发送和接收可以通过中断方式来实现,也可以通过查询方式来实现。

SCI:DSP和计算机之间进行数据传输查询和中断的方式来实现sci接收和发送数据两个Sci模块(16级深度的FIFO队列)单工、半双工、全双工SCITXD 发送引脚SCIRXD 接收引脚其为复用引脚,分别对应GPIOF模块的第四位和第五位,编程时需把GPIOFMUX 模块第四位和第五位置1,否则这两个引脚就是通用的数字I/O口。

SCI模块具有四种错误检测标识,分别为极性错误,超时错误,帧错误,间断检测。

接收中断,发送中断Sci的寄存器是8位的__SHF 移位寄存器每次移入一位__BUF 缓冲寄存器SCITXBUF→TXSHF→SCITXDSCIRXBUF存放cpu要读的数据,从其他处理器传过来的数据逐位移入寄存器RXSHF 装满时→RXSHF 从SCIRXD移入数据一个可编程的波特率发生器发送和接收数据的原理Scictl1的位RXENA为1即使能了SCI的接收操作如果使能了sci的FIFO功能,则RXSHF会将数据直接加载到接收队列中,CPU再从队列读取,这时简化了CPU的开销,提高了效率。

FIFO模式下,直接从从指令中进行操作。

NRZ(反向不归零制)指数字数据传输的一种形式,用数字0和1表示二进位的低和高状态通过特特殊的和持续的直流(DC)电压传输。

在正逻辑NRZ 中,低位状态用更大的负的或更小的正的电压表示,高位状态用较小的负的或较大的正的电压表示。

例子如下:逻辑0=+0.5 伏特逻辑1=+5.0 伏特逻辑0=-3.0 伏特逻辑1=0.0 伏特在负逻辑NRZ 中,低位状态用更大正的或更小的负的电压表示,高位状态用较小的正的或较大的负的电压表示。

例子如下:逻辑0=+5.0 伏特逻辑1=+0.5 伏特逻辑0=0.0 伏特逻辑1=-3.0 伏特当逻辑状态之一可能被零电压表示的时候,一些人对这个模型的名字前面为什么要加上"非" 感到奇怪。

和归零制的定义比较之后答案就变得很明显。

也可参看双极发信号,单极发信号,和RZ。

异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线异步接收器传输总线(UART)、串行通信接口(SCI)和通用串行总线(USB)等,这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文详细介绍了嵌入式系统设计的串行总线、驱动器和物理接口的特性,并为总线最优选择提供性能比较和选择建议。

由于在消费类电子产品、计算机外设、汽车和工业应用中增加了嵌入式功能,对低成本、高速和高可靠通信介质的要求也不断增长以满足这些应用,其结果是越来越多的处理器和控制器用不同类型的总线集成在一起,实现与PC软件、开发系统(如仿真器)或网络中的其它设备进行通信。

目前流行的通信一般采用串行或并行模式,而串行模式应用更广泛。

微处理器中常用的集成串行总线是通用异步接收器传输总线、串行通信接口、同步外设接口(SPI)、内部集成电路(I2C)和通用串行总线,以及车用串行总线,包括控制器区域网(CAN)和本地互连网(LIN)。

这些总线在速度、物理接口要求和通信方法学上都有所不同。

本文将对嵌入式系统设计的串行总线、驱动器和物理接口这些要求提供一个总体介绍,为选择最优总线提供指导并给出一个比较图表(表1)。

为了说明方便起见,本文的阐述是基于微处理器的设计。

串行与并行相比串行相比于并行的主要优点是要求的线数较少。

例如,用在汽车工业中的LIN串行总线只需要一根线来与从属器件进行通信,Dallas公司的1-Wire总线只使用一根线来输送信号和电源。

较少的线意味着所需要的控制器引脚较少。

集成在一个微控制器中的并行总线一般需要8条或更多的线,线数的多少取决于设计中地址和数据的宽度,所以集成一个并行总线的芯片至少需要8个引脚来与外部器件接口,这增加了芯片的总体尺寸。

相反地,使用串行总线可以将同样的芯片集成在一个较小的封装中。

另外,在PCB板设计中并行总线需要更多的线来与其它外设接口,使PCB 板面积更大、更复杂,从而增加了硬件成本。