数据采集系统实验报告AD模块的设计

- 格式:docx

- 大小:371.22 KB

- 文档页数:7

智能仪器实验指导书Revised on November 25, 2020《智能仪器》实验报告实验项目实验时间同组同学班级学号姓名2014年4月实验一多路巡回数据数据采集系统一、实验目的1.学习模/数(A/D)转换的工作原理。

2.掌握芯片ADC0809与微控制器接口电路的设计方法。

3.掌握芯片ADC0809的程序设计方法。

二、实验设备1.实验用到的模块有“SMP-201 8051模块”、“SMP-204 译码模块”、“SMP-101 8位A/D模块”、“SMP-401 静态显示模块”。

2.短的20P、40P数据线各一根。

3.长的一号导线3根,转接线一根。

三、实验原理ADC0809芯片是一种8位采用逐次逼近式工作的转换器件。

它带有8路模拟开关,可进行8路模/数转换,通过内部3-8译码电路进行选通。

启动ADC0809的工作过程:先送信道号地址到A、B、C三端,由ALE信号锁存信道号地址,选中的信道的模拟量送到A/D转换器,执行语句 MOVX @DPTR,A产生写信号,启动A/D转换。

当A/D转换结束时,ADC0809的EOC端将上升为高电平,执行语句MOVX A,@DPTR产生读信号,使OE有效,打开锁存器三态门,8位数据就读到CPU中,A/D转换结果送显示单元。

编程时可以把EOC信号作为中断请求信号,对它进行测试,用中断请求或查询法读取转换结果。

实验原理参考图1-1。

图1-1 多路巡回数据数据采集系统实验原理图本实验中ADC0809的8位模拟开关译码地址为:IN0= 8800H IN1= 8801HIN2= 8802H IN3= 8803HIN4= 8804H IN5= 8805HIN6= 8806H IN7= 8807H四、实验内容步骤1.将“SMP-201 8051模块”和“SMP-204 译码模块”分别插放到“SMP-2 主控制器单元”挂箱的CPU模块接口和译码模块接口上,将“SMP-101 8位并行AD模块”插放到“SMP-1 信号转换单元”挂箱的A/D转换模块接口上,将“SMP-401 静态显示模块”插放到“SMP-4键盘与显示单元”的显示模块接口上。

微机原理课程设计报告设计题目:A/D数据采集卡设计一.课程设计目的通过课程设计,提高理论联系实际的解决实际问题的能力;提高对接口技术等相关硬件知识的深入理解;掌握8255A的控制字的设置、工作方式、编程原理和微机接口方法。

加深理解逐次逼近法模数转换器的特征和工作原理,掌握ADC0809的接口方法以及A/D输入程序的设计和调试方法。

熟悉ADC0809模数转换器的特性和接口方法,掌握A/D输出程序的设计和调试方法,进而提高动手能力和学习兴趣为顺利进入毕业环节做必要的准备。

二.课程设计内容设计一块A/D卡,该卡具有对0~5V的模拟电压进行采集功能的能力,该卡通过系统的I/O扩展接口与微机系统连接。

选用芯片:ADC0809等。

三.设计要求画出电路原理图,说明工作原理,编写利用该卡进行256个数据的采集并显示在显示器上的程序.四.概要设计ADC0809是一种8路模拟输入、8位数字输出的逐次逼近法A/D器件,转换时间约100us,转换精度—1/512到+1/512,适合于多路采集系统。

ADC0809片内有三态输出的数据锁存器,故可以与8088微机总线直接接口。

ADC0809的CLK信号接系统的CLK输入,基准电压Vref(+)接Vcc。

一般实际应用系统中应该接精度+5v,以提高转换精度,ADC0809片选信号0809CS和/IOW、/IOR经逻辑组合后,去控制ADC0809的ALE、START、ENABLE信号。

ADC0809CS连译码输出的00H-0FH。

ADC0809的转换结束信号EOC接IOR。

本试验以延时方式等待A/D转换结束,ADC0809的通道号选择线ADD-A 、ADD-B、ADD-C接系统数据线的低3位,因此ADC0809的8个通道值地址分别为00H、01H、02H、03H、04H、05H、06H、07H。

调节电位器W1,以改变模拟电压值,用ADC0809做A/D转换,其模拟量与数字量对应关系的典型值为+5V—FFH、2.5V—80H、0V—00H。

A/D转换实验报告摘要本设计是利用AT89C51、ADC0809、CD4027芯片为核心,加以其他辅助电路实现对信号的A/D转换,其中以单片机AT89C51为核心控制A/D转换器。

先是对信号进行采集,然后用ADC0809对信号实现从模拟量到数字量的转换。

改变采样数据,调整电路,使其达到精确转换。

目录1.方案设计与论证 (1)1.1理论分析 (1)1.2输出、输入方案选择 (1)1.3显示方案 (2)1.4时钟脉冲选择 (2)2.硬件设计 (2)2.1A/D转换器模块 (2)2.2单片机模块 (3)2.3JK触发器模块 (4)3软件设计 (4)4.仿真验证与调试 (5)4.1测试方法 (5)4.2性能测试仪器 (7)4.4误差分析 (7)5.设计总结及体会 (5)附录(一)实物图 (6)附录(二)软件程序 (6)1.方案设计与论证1.1理论分析8位A/D转换由芯片内部的控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成,它具有将模拟量转换成数字量的特性,其原理图如下:AD转换原理图(1)1.2输出、输入方案选择A/D转换器有多路选择器,可选择八路模拟信号IN0~IN7中的一路进入A/D转换。

现在选择IN0通道作为输入,则对应的地址码位ADD C=0、ADD B=0、ADD A=0。

当转换完成后,OE=1,打开三态输出锁存缓冲器,将转换数据从D7~D0口输出到单片机的P0端口。

IN口输入D端口输出A/D转换器图(2)1.3显示方案单片机控制数码管显示有两种动态和静态两种方法,由于静态控制数码管每次只能显示一位,造成资源浪费,所以选择动态扫描,并增加变换频率。

1.4时钟脉冲选择方案一:可以直接用矩形波来控制方案二:ALE通过JK触发器完成二分频,然后 Q端接CLK。

因为晶振的频率是12MHz,ALE的频率为12NHz×1/6=2MHz,经过JK 触发器二分频后就是1MHz.2.硬件设计2.1 A/D转换器模块A/D转换电路图(3)模拟量从IN0端口输入,经电压比较器后输入到控制电路,转换后从D0~D7口输出,地址码位ADD C=0、ADD B=0、ADD A=0。

微机原理及接口技术之AD及DA实验一. 实验目的:1. 了解A/D芯片ADC0809和D/A芯片DAC0832的电气性能;外围电路的应用性搭建及有关要点和注意事项;与CPU的接口和控制方式;相关接口参数的确定等;2. 了解数据采集系统中采样保持器的作用和采样频率对拾取信号失真度的影响, 了解香农定理;3.了解定时计数器Intel 8253和中断控制器Intel 8259的原理、工作模式以及控制方式, 训练控制定时器和中断控制器的方法, 并学习如何编写中断程序。

4.熟悉X86汇编语言的程序结构和编程方法, 训练深入芯片编写控制程序的编程能力。

二. 实验项目:1. 完成0~5v的单极性输入信号的A/D转换, 并与实际值(数字电压表的测量值)比较, 确定误差水平。

要求全程至少10个点。

2.完成-5v~+5v的双极性输入信号的A/D转换, 并与实际值(数字电压表的测量值)比较, 确定误差水平。

要求全程至少20个点。

3.把0~FF的数据送入DAC0832并完成D/A转换, 然后用数字电压表测量两个模拟量输出口(OUT1为单极性, OUT2双极性)的输出值, 并与计算值比较, 确定误差水平。

要求全程至少16个点。

三. 仪器设备:Aedk-ACT实验箱1套(附电源线1根、通信线1根、实验插接线若干、跳线子若干);台式多功能数字表1台(附电源线1根、表笔线1付(2根)、);PC机1台;实验用软件: Windows98+LcaACT(IDE)。

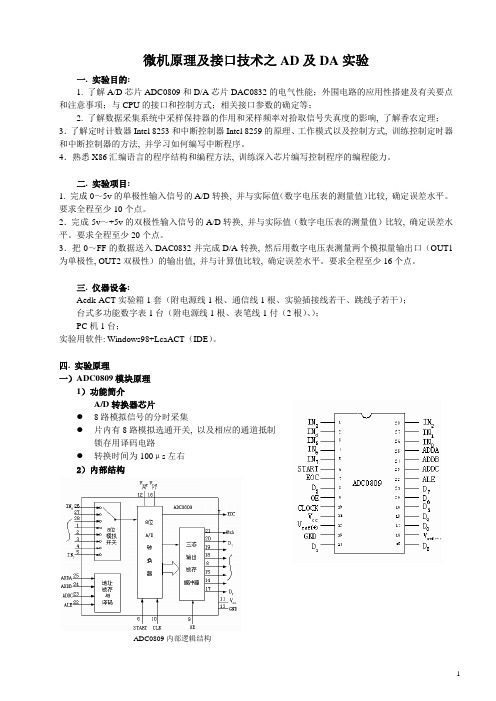

四. 实验原理一)ADC0809模块原理1)功能简介A/D转换器芯片●8路模拟信号的分时采集●片内有8路模拟选通开关, 以及相应的通道抵制锁存用译码电路●转换时间为100μs左右2)内部结构ADC0809内部逻辑结构1图中多路开关可选通8个模拟通道, 允许8路模拟量分时输入, 共用一个A/D转换器进行转换, 这是一种经济的多路数据采集方法。

地址锁存与译码电路完成对A.B.C 3个地址位进行锁存和译码, 其译码输出用于通道选择, 其转换结果通过三态输出锁存器存放、输出, 因此可以直接与系统数据总线相连。

单片机实验报告姓名: XX班级: XXXXX学号: XXXXXXX专业:电气工程与自动化实验1 名称:数据采集_A/D转换一、实验目的⑴掌握A/D转换与单片机接口的方法;⑵了解A/D芯片0809 转换性能及编程方法;⑶通过实验了解单片机如何进行数据采集。

二、实验设备装有proteus和keil软件的电脑一台三、实验说明及实验原理:A/D 转换器大致分有三类:一是双积分A/D 转换器,优点是精度高,抗干扰性好,价格便宜,但速度慢;二是逐次逼近式A/D转换器,精度、速度、价格适中;三是并联比较型A/D转换器,速度快,价格也昂贵。

实验用ADC0809属第二类,是8位A/D转换器。

每采集一次一般需100μs。

由于ADC0809A/D 转换器转换结束后会自动产生EOC 信号(高电平有效),取反后将其与8031 的INT0 相连,可以用中断方式读取A/D转换结果。

ADC0809 是带有8 位A/D转换器、8 路多路开关以及微处理机兼容的控制逻辑的CMOS组件。

它是逐次逼近式A/D转换器,可以和单片机直接接口。

(1) ADC0809 的内部逻辑结构由图1.1 可知,ADC0809 由一个8 路模拟开关、一个地址锁存与译码器、一个A/D 转换器和一个三态输出锁存器组成。

多路开关可选通8 个模拟通道,允许8 路模拟量分时输入,共用A/D 转换器进行转换。

三态输出锁器用于锁A/D 转换完的数字量,当OE 端为高电平时,才可以从三态输出锁存器取走转换完的数据。

(2) ADC0809 引脚结构ADC0809各脚功能如下:D7 ~ D0:8 位数字量输出引脚。

IN0 ~ IN7:8位模拟量输入引脚。

VCC:+5V工作电压。

GND:地。

REF(+):参考电压正端。

REF(-):参考电压负端。

START:A/D转换启动信号输入端。

ALE:地址锁存允许信号输入端。

(以上两种信号用于启动A/D转换).EOC:转换结束信号输出引脚,开始转换时为低电平,当转换结束时为高电平。

基于SAR-ADC的精密同步数据采集系统设计王炳文【摘要】For the problem of simultaneously sampling of multi-channel analog signals in a data acquiring system, the schemes of the system were discussed.Based on SAR-ADC, a kind of 16 bit AD convert system which controlled by FPGA was designed.The system could realize real-time synchronous sampling of analog signals.And the differences of sampling rate among multi-channel analog signals were well balanced in this system.The Signal to Noise and Distortion Ratio(SINAD) and Effective Number of Bits(ENOB) of the system were tested, and it was proved that the system can achieve good AC characters.%针对某精密数据采集系统中模拟信号同步采样问题,文章研究了多通道同步模拟信号采集方法,设计了一种基于SAR-ADC、使用FPGA控制的16位同步采样AD转换系统.该系统可实现模拟信号的实时同步采样,同时兼顾多路模拟信号采样频率要求的差异性,最后通过试验测试了该系统的信纳比(SINAD)和有效位数(ENOB).测试结果表明,该系统具有良好的动态性能指标.【期刊名称】《微型机与应用》【年(卷),期】2017(036)007【总页数】4页(P29-31,34)【关键词】SAR-ADC;同步采样;FPGA【作者】王炳文【作者单位】中国航空工业集团公司西安航空计算技术研究所,陕西西安 710065【正文语种】中文【中图分类】TP353在惯性测量[1]、功率因数校正[2]、电机控制等工业应用场合,系统需要采集同一时刻来自多个传感器的模拟信号,并根据当前的状态进行计算和控制。

基于FPGA的ADC采集系统的设计摘要基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。

因此,本文研究并开发了一个基于FPGA的数据采集系统。

FPGA的IO口可以自由定义,没有固定总线限制更加灵活变通。

本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。

依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

关键词FPGA A/D转换AbstractFPGA is better than microcontroller and DSP in high speed data acquisition, FPGA has higher internal clock frequency, smaller delay than DSP,and all the control logic of FPGA is completed by hardware, FPGA has fast speed, high efficiency, and so on. Therefore, this paper introduces and develops a data acquisition system which is based on FPGA.The I/O pin of FPGA can be defined yourself without fixed limit,it’s very flexible. This design of data acquisition system use FPGA as the data acquisition system core to control the timing and the logic control module. Relying on the powerful function of FPGA, FPGA can connect ADC, display devices and other peripheral circuits, finally we can achieve the requirements of the subject, and the purpose of the data collection。

一、实验目的1. 理解数据采集系统的基本原理和组成;2. 掌握数据采集系统的设计方法和步骤;3. 学会使用数据采集设备进行数据采集;4. 分析和解读采集到的数据。

二、实验原理数据采集系统是指将各种物理量、化学量、生物量等转换成数字信号,并存储、处理和分析的系统。

它由数据采集器、信号调理电路、数据传输线路和数据处理软件等组成。

三、实验器材1. 数据采集器:采用USB接口的数据采集器,可连接计算机;2. 信号调理电路:包括放大器、滤波器等;3. 计算机及数据处理软件;4. 模拟信号源:提供不同的模拟信号;5. 连接线及电源。

四、实验步骤1. 数据采集器与计算机连接,打开数据处理软件;2. 设计信号调理电路,对模拟信号进行放大、滤波等处理;3. 将信号调理电路与数据采集器连接,并连接模拟信号源;4. 设置数据采集器参数,如采样频率、分辨率等;5. 采集模拟信号,并将数据保存到计算机;6. 对采集到的数据进行处理和分析。

五、实验内容1. 采集不同频率的正弦信号,分析频率与幅值的关系;2. 采集不同带宽的滤波信号,分析带宽与滤波效果的关系;3. 采集不同放大倍数的信号,分析放大倍数与信号幅值的关系;4. 采集不同温度下的热电偶信号,分析温度与电势的关系。

六、实验结果与分析1. 频率与幅值的关系:在信号源频率不变的情况下,采集到的正弦信号的幅值随放大倍数的增大而增大,符合正比关系;2. 带宽与滤波效果的关系:在信号源带宽不变的情况下,滤波器的带宽越大,信号中的噪声成分越少,滤波效果越好;3. 放大倍数与信号幅值的关系:在信号源幅值不变的情况下,采集到的信号幅值随放大倍数的增大而增大,符合正比关系;4. 温度与电势的关系:在热电偶温度不变的情况下,采集到的电势随温度的升高而增大,符合线性关系。

七、实验结论1. 数据采集系统是进行科学实验和工程应用的重要工具,具有广泛的应用前景;2. 在数据采集过程中,信号调理电路的设计对采集结果具有重要影响;3. 通过数据处理软件对采集到的数据进行处理和分析,可以得到有价值的实验结果。

A/D 采集模块设计学院名称: 电气信息工程学院 专 业: 测控技术与仪器 班 级: 07测控 姓 名: 学 号: 指导教师:2010年12月20日JIANGSU TEACHERSUNIVERSITY OF TECHNOLOGY数据采集系统实验报告目录一、实验目的二、实验原理1.ADC0809的原理及原理图2.AD574A的原理及原理图三、实验过程四、实验结果五、结束语六、参考文献一、实验目的:学习用状态机实现对ADC0809,AD574A等A/D转换器的采样控制。

二、实验原理:1.ADC0809的原理及原理图图2.1和图2.2分别是ADC0809的工作时序图以及采样状态图。

时序图中,START为转换启动控制信号,高电平有效,ALE为模拟信号输入宣统端口地址所存信号,上升沿有效;一旦START有效后,状态信号EOC变为低电平,表示进入转换状态,转换时间约为100us。

转换结束后,EOC将变为高电平。

此后外部控制可使OE由低电平变为高电平(输出有效),此时,ADC0809的输出数据总线D[7…0]从原来的高阻态变为输出数据有效。

由状态图也可看到,状态st2中需要对ADC0809工作状态信号EOC进行测试,如果为低电平,表示转换没有结束,仍需要停留在st2状态中等待,直到变成高电平后才说明转换结束,在下一个时钟脉冲到来时转向状态st3。

在状态st3,由状态机向ADC0809发出转换好的8位数据输出允许命令,这一状态周期同时可作为数据输出稳定周期,以便能在下一状态中向锁存器中锁入可靠的数据。

在状态st4,由状态机向FPGA中的锁存器发出锁存信号(LOCK的上升沿),将ADC0809的输出数据进行锁存。

图2.1 ADC0809工作时序图2.2控制ADC0809采样状态图2.AD574A的原理及原理图(1)12位A /D 转换器芯片AD574A 特点:芯片内部包含微机接口逻辑和三态输出缓冲器,可以直接与8 位、12 位或16 位;输出可以是12位一次读出或分两次读出,先读高8位,再读低4位;输入电压可有单极性和双极性两种;对外可提供一个+10V 基准电压,最大输出电流1.5mA ;有较宽的温度使用范围。

(2) 芯片引脚功能如图2.4所示:图2.4 AD574A 引脚功能(3)启动转换的时序:在启动转换后,各控制信号不起作用,只有STS 信号标志工作状态。

读出数据也同样由CE 来启动,读时序如下图2.5所示:图2.5 AD574A 读时序图三、 实验过程本次实验是采用Quartu s Ⅱ软件进行编译与仿真。

步骤如下: 1. 打开Quartu s Ⅱ6.0软件,进入Quartu s Ⅱ欢迎界面。

2. 鼠标单击File---new ,出现如下窗口,选择“VHDL FILE ”,在弹出的窗口中输入VHDL 程序文件。

①3.输入完毕后,点击保存,由于接下来步骤繁琐,我就把它简述为保存并新建工程。

4.接下来就进行编译,选择下图processing菜单中的start complilation命令。

若有VHDL程序有错误,则编译不会完成并弹出对话框提示如下图所示,单击确定后,手动排除错误。

方法是在红色的错误提示上双击鼠标左键,软件会自动找到可能是错误的地方或者软件认为不符合规范的地方,排除错误后,再重新执行编译过程。

5.完成编译后方可进行时序波形的仿真,也称为软件仿真,仿真的前提条件是要有波形文件。

仿真的过程可以分为新建波形文件,添加节点,设置仿真时间长度,绘制波形,存储文件,启动仿真等步骤。

6.附上程序清单:(1)ADC0809程序清单LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY vhdl1 ISPORT(D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--来自0809转换好的8位数据CLK : IN STD_LOGIC; --状态机工作时钟EOC : IN STD_LOGIC; --转换状态指示,低电平表示正在转换ALE : OUT STD_LOGIC; --8个模拟信号通道地址锁存信号START : OUT STD_LOGIC; --转换开始信号OE : OUT STD_LOGIC; --数据输出3态控制信号ADDA : OUT STD_LOGIC; --信号通道最低位控制信号LOCK0 : OUT STD_LOGIC; --观察数据锁存时钟Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出END vhdl1;ARCHITECTURE behav OF vhdl1 ISTYPE states IS (st0, st1, st2, st3,st4) ; --定义各状态子类型SIGNAL current_state, next_state: states :=st0 ;SIGNAL REGL : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL LOCK : STD_LOGIC; -- 转换后数据输出锁存时钟信号BEGINADDA <= '1';--当ADDA<='0',模拟信号进入通道IN0;当ADDA<='1',则进入通道IN1Q <= REGL; LOCK0 <= LOCK ;COM: PROCESS(current_state,EOC,CLK) BEGIN --规定各状态转换方式IF CLK'EVENT AND CLK='1'THENCASE current_state ISWHEN st0=>ALE<='0';START<='0';LOCK<='0';OE<='0'; next_state<= st1; --0809初始化WHEN st1=>ALE<='1';START<='1';LOCK<='0';OE<='0'; next_state<= st2; --启动采样WHEN st2=> ALE<='0';START<='0';LOCK<='0';OE<='0';IF (EOC='1') THEN next_state<= st3; --EOC=1表明转换结束ELSE next_state<= st2; END IF ; --转换未结束,继续等待WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1'; next_state<= st4;--开启OE,输出转换好的数据WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1'; next_state<= st0;WHEN OTHERS =>next_state<= st0; END CASE ;END IF;END PROCESS COM ;REG: PROCESS (CLK)BEGINIF (CLK'EVENT AND CLK='1') THEN current_state<=next_state; END IF;END PROCESS REG ; -- 由信号current_state将当前状态值带出此进程:REGLATCH1: PROCESS (LOCK) -- 此进程中,在LOCK的上升沿,将转换好的数据锁入BEGINIF LOCK='1' AND LOCK'EVENT THEN REGL <= D ; END IF;END PROCESS LATCH1 ;END behav;(2)AD574A程序清单:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADCINT1 ISPORT(D:IN STD_LOGIC_VECTOR(11 DOWNTO 0); CLK:IN STD_LOGIC;STS:IN STD_LOGIC;CE:OUT STD_LOGIC;CS:OUT STD_LOGIC;RCN:OUT STD_LOGIC;A0:OUT STD_LOGIC;SL: OUT STD_LOGIC;LOCK0:OUT STD_LOGIC;Q:OUT STD_LOGIC_VECTOR(11 DOWNTO 0)); END ENTITY ADCINT1;ARCHITECTURE behav OF ADCINT1 ISTYPE states IS(st0,st1,st2,st3,st4,ST5);SIGNAL current_state,next_state:states:=st0;SIGNAL REGL :STD_LOGIC_VECTOR(11 DOWNTO 0); SIGNAL LOCK :STD_LOGIC;BEGINA0<='0';SL<='1';Q<=REGL;LOCK0<=LOCK;COM:PROCESS(current_state,STS)BEGINIF(CLK'EVENT AND CLK='1') THENCASE current_state ISWHEN st0=>CE<='0';CS<='0';RCN<='0';LOCK<='0'; next_state<=st1;WHEN st1=>CE<='1';CS<='0';RCN<='0';LOCK<='0';next_state<=st2;WHEN st2=>CE<='0';CS<='1';RCN<='1';LOCK<='0';IF(STS='0')THEN next_state<=st3;ELSE next_state<=st2;END IF;WHEN st3=>CE<='0';CS<='0';LOCK<='0';RCN<='1';next_state<=st4;WHEN st4=>CE<='1';CS<='0';LOCK<='0';RCN<='1';next_state<=st5;WHEN st5=>CE<='1';CS<='0';LOCK<='1';RCN<='1';next_state<=st0;WHEN OTHERS=>next_state<=st0;end case;END IF;end process COM;REG:PROCESS(CLK)BEGINIF(CLK'EVENT AND CLK='1') THEN current_state<=next_state;END IF;END PROCESS REG;LATCH1:PROCESS(LOCK)BEGINIF LOCK='1' AND LOCK'EVENT THEN REGL<=D;END IF; END PROCESS LATCH1;END behav;四、实验结果图4 ADC0809采样状态机工作时序五、结束语这次的数据采集系统课程设计,让我们有机会将课堂上所学的理论知识运用到实际中。