第三、四讲 Verilog HDL 行为语句

- 格式:ppt

- 大小:444.00 KB

- 文档页数:49

verilogHDL培训教程华为近年来,随着人工智能、物联网和5G等新兴技术的快速发展,数字电路设计和FPGA开发方面的需求也越来越迫切。

而Verilog HDL已成为数字电路设计中最受欢迎和广泛使用的硬件描述语言之一。

因此,华为公司推出了一系列的Verilog HDL培训教程,帮助从业人员快速获得这个技能。

华为Verilog HDL培训教程的特点华为Verilog HDL培训教程主要针对初学者和中级学员,旨在让学生掌握Verilog HDL基础和应用。

教程内容科学、系统,结合了中国实际情况,给人耳目一新的感觉。

华为Verilog HDL培训教程遵从"理论与实践相结合"的原则,保证学生能够灵活应用所学知识。

在理论教学方面,华为Verilog HDL培训教程先后介绍和讲解了Verilog HDL的基础概念、语法、数据类型、运算符、模块等。

在实践操作方面,华为Verilog HDL培训教程采用基于FPGA芯片的开发板完成实验,让学生能够真正体验到数字电路设计的工程化过程。

此外,华为Verilog HDL培训教程融合了多元化的教学形式,通过讲解PPT、操作演示视频、实验文档等多种形式进行教学。

教材编制过程中对各章节的课程设计进行了充分的考虑,让学生可以从基础入手,系统性、完整性地掌握Verilog HDL语言。

总之,华为Verilog HDL培训教程尽力使学习过程严谨、声音,减少因知识不足而带来的错误和困惑。

华为Verilog HDL培训教程的课程设置华为Verilog HDL培训教程旨在让学员了解数字电路设计中最常用的硬件描述语言-- Verilog HDL,并在FPGA开发板上完成一些典型实验。

华为Verilog HDL培训教程包含以下章节:第一章:Verilog HDL基础概念在本章中,学生将学习Verilog HDL的起源、产生背景、基本概念、Verilog HDL的体系结构、Verilog HDL模块体系结构等知识。

第三章 Verilog HDL的基本语法前言Verilog HDL是一种用于数字逻辑电路设计的语言。

用Verilog HDL描述的电路设计就是该电路的Verilog HDL模型。

Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。

这也就是说,既可以用电路的功能描述也可以用元器件和它们之间的连接来建立所设计电路的Verilog HDL模型。

Verilog模型可以是实际电路的不同级别的抽象。

这些抽象的级别和它们对应的模型类型共有以下五种:∙系统级(system):用高级语言结构实现设计模块的外部性能的模型。

∙算法级(algorithm):用高级语言结构实现设计算法的模型。

∙RTL级(Register Transfer Level):描述数据在寄存器之间流动和如何处理这些数据的模型。

∙门级(gate-level):描述逻辑门以及逻辑门之间的连接的模型。

∙开关级(switch-level):描述器件中三极管和储存节点以及它们之间连接的模型。

一个复杂电路系统的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

Verilog HDL行为描述语言作为一种结构化和过程性的语言,其语法结构非常适合于算法级和RTL级的模型设计。

这种行为描述语言具有以下功能:∙可描述顺序执行或并行执行的程序结构。

∙用延迟表达式或事件表达式来明确地控制过程的启动时间。

∙通过命名的事件来触发其它过程里的激活行为或停止行为。

∙提供了条件、if-else、case、循环程序结构。

∙提供了可带参数且非零延续时间的任务(task)程序结构。

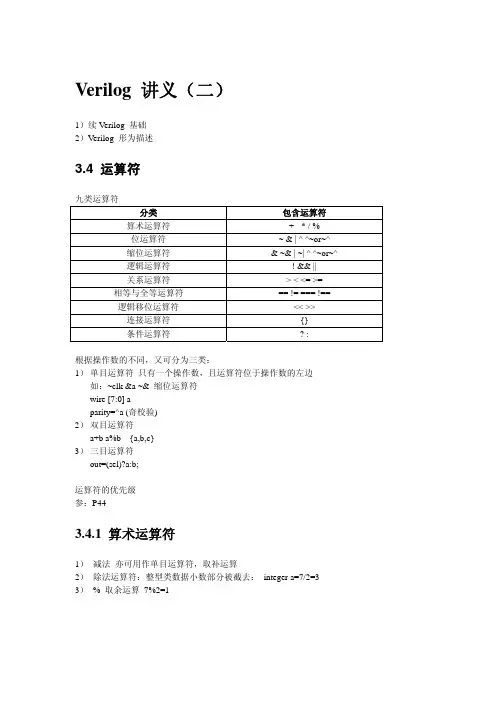

Verilog 讲义(二)1)续Verilog 基础2)Verilog 形为描述3.4 运算符九类运算符分类包含运算符算术运算符+ - * / %位运算符~ & | ^ ^~or~^缩位运算符& ~& | ~| ^ ^~or~^逻辑运算符! && ||关系运算符> < <= >=相等与全等运算符== != === !==逻辑移位运算符 <<>> 连接运算符 {}: 条件运算符 ?根据操作数的不同,又可分为三类:1)单目运算符只有一个操作数,且运算符位于操作数的左边如:~clk &a ~& 缩位运算符wire [7:0] aparity=^a (奇校验)2)双目运算符a+b a%b {a,b,c}3)三目运算符out=(sel)?a:b;运算符的优先级参:P443.4.1 算术运算符1)减法亦可用作单目运算符,取补运算2)除法运算符:整型类数据小数部分被截去: integer a=7/2=33)% 取余运算 7%2=13.4.2 位运算符1)~a 按位取反2)a&b 按位相与若a,b 位数不同,短的高位补0,(x者补x)3)^ ^~ 双目3.4.3 缩位运算符单目运算符,按位进行逻辑运算,结果产生一位的逻辑值。

A=4’b1001&a ~&a |a ~|a ^a ~^a0 1 1 0 1 0 3.4.3 逻辑运算符a&&b结果为一位的逻辑值若操作数为多位,只要有一位为1,整个操作数看作逻辑1;若有不定态,结果亦为不定态。

3.4.5关系运算符结果为一位的逻辑值。

3.4.6 相等与全等运算符结果为一位逻辑值相等:比较每一位,所有相等,关系满足,若有不定态或高阻态,不定态结果。

全等:与相等比较过程相同,亦将不定态及高阻态作为逻辑状态比较。

3.4.7 逻辑移位运算符<< >> 以0补位。

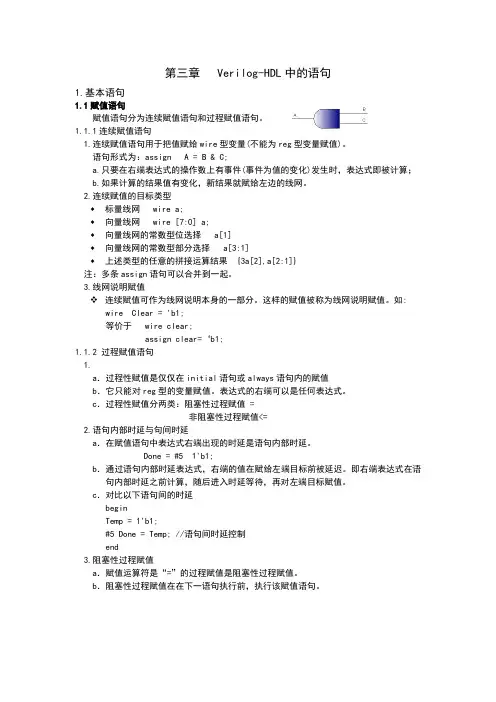

第三章 Verilog-HDL中的语句1.基本语句1.1赋值语句赋值语句分为连续赋值语句和过程赋值语句。

1.1.1连续赋值语句1.连续赋值语句用于把值赋给wire型变量(不能为reg型变量赋值)。

语句形式为:assign A = B & C;a.只要在右端表达式的操作数上有事件(事件为值的变化)发生时,表达式即被计算;b.如果计算的结果值有变化,新结果就赋给左边的线网。

2.连续赋值的目标类型♦标量线网 wire a;♦向量线网 wire [7:0] a;♦向量线网的常数型位选择 a[1]♦向量线网的常数型部分选择 a[3:1]♦上述类型的任意的拼接运算结果 {3a[2],a[2:1]}注:多条assign语句可以合并到一起。

3.线网说明赋值连续赋值可作为线网说明本身的一部分。

这样的赋值被称为线网说明赋值。

如: wire Clear = 'b1;等价于 wire clear;assign clear=‘b1;1.1.2 过程赋值语句1.a.过程性赋值是仅仅在initial语句或always语句内的赋值b.它只能对reg型的变量赋值。

表达式的右端可以是任何表达式。

c.过程性赋值分两类:阻塞性过程赋值 =非阻塞性过程赋值<=2.语句内部时延与句间时延a.在赋值语句中表达式右端出现的时延是语句内部时延。

Done = #5 1'b1;b.通过语句内部时延表达式,右端的值在赋给左端目标前被延迟。

即右端表达式在语句内部时延之前计算,随后进入时延等待,再对左端目标赋值。

c.对比以下语句间的时延beginTemp = 1'b1;#5 Done = Temp; //语句间时延控制end3.阻塞性过程赋值a.赋值运算符是“=”的过程赋值是阻塞性过程赋值。

b.阻塞性过程赋值在在下一语句执行前,执行该赋值语句。

例:initialbeginClr = #5 0;Clr = #4 1;Clr = #10 0;end4.非阻塞性过程赋值a .在非阻塞性过程赋值中,使用赋值符号“ <=”。

Verilog-HDL讲座第三讲 Verilog-HDL的基本概念

常晓明

【期刊名称】《今日电子》

【年(卷),期】2003(000)010

【摘要】@@ 3.1与门的描述rn我们通过最简单的例子来认识一下Verilog-HDL 的基本用法.

【总页数】4页(P54-57)

【作者】常晓明

【作者单位】太原理工大学

【正文语种】中文

【中图分类】TN7

【相关文献】

1.Verilog-HDL讲座第二讲构筑Verilog-HDL学习所需要的环境 [J], 常晓明

2.基于Verilog-HDL的RISC/DSP微处理器IP核的设计 [J], 陈芙蓉;张向文;曹梅双

3.Verilog-HDL讲座第六讲用Verilog-HDL做CPLD设计目标板的设计和下载软件的使用 [J], 李媛媛;常晓明

4.Verilog-HDL讲座第四讲 Verilog-HDL仿真软件的基本操作 [J], 常晓明

5.Verilog-HDL讲座第五讲典型基本逻辑路的Verilog-HDL描述 [J], 常晓明;李媛媛

因版权原因,仅展示原文概要,查看原文内容请购买。

VERILOGHDL语⾔基础第1节 Verilog HDL语⾔简介Verilog HDL语⾔简介Verilog HDL和VHDL是⽬前世界上最流⾏的两种硬件描述语⾔(HDL:Hardware Description Language),均为IEEE标准,被⼴泛地应⽤于基于可编程逻辑器件的项⽬开发。

⼆者都是在20世纪80年代中期开发出来的,前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发,后者由美国军⽅研发。

HDL语⾔以⽂本形式来描述数字系统硬件结构和⾏为,是⼀种⽤形式化⽅法来描述数字电路和系统的语⾔,可以从上层到下层来逐层描述⾃⼰的设计思想。

即⽤⼀系列分层次的模块来表⽰复杂的数字系统,并逐层进⾏验证仿真,再把具体的模块组合由综合⼯具转化成门级⽹表,接下去再利⽤布局布线⼯具把⽹表转化为具体电路结构的实现。

⽬前,这种⾃顶向下的⽅法已被⼴泛使⽤。

概括地讲,HDL语⾔包含以下主要特征:* HDL语⾔既包含⼀些⾼级程序设计语⾔的结构形式,同时也兼顾描述硬件线路连接的具体结构。

* 通过使⽤结构级⾏为描述,可以在不同的抽象层次描述设计。

HDL语⾔采⽤⾃顶向下的数字电路设计⽅法,主要包括3个领域5个抽象层次。

* HDL语⾔是并⾏处理的,具有同⼀时刻执⾏多任务的能⼒。

这和⼀般⾼级设计语⾔(例如C 语⾔等)串⾏执⾏的特征是不同的。

* HDL语⾔具有时序的概念。

⼀般的⾼级编程语⾔是没有时序概念的,但在硬件电路中从输⼊到输出总是有延时存在的,为了描述这⼀特征,需要引⼊时延的概念。

HDL语⾔不仅可以描述硬件电路的功能,还可以描述电路的时序。

2.1.1 Verilog HDL语⾔的历史1983年,Gateway Design Automation(GDA)硬件描述语⾔公司的Philip Moorby⾸创了Verilog HDL。

后来Moorby成为Verilog HDL-XL的主要设计者和Cadence公司的第⼀合伙⼈。