Cortex M3中断优先级分组的理解

- 格式:doc

- 大小:43.50 KB

- 文档页数:2

STM32中断中设置的先占式优先级与从优先级STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。

既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位可以有8种分配方式,如下:所有8位用于指定响应优先级最高1位用于指定抢占式优先级,最低7位用于指定响应优先级最高2位用于指定抢占式优先级,最低6位用于指定响应优先级最高3位用于指定抢占式优先级,最低5位用于指定响应优先级最高4位用于指定抢占式优先级,最低4位用于指定响应优先级最高5位用于指定抢占式优先级,最低3位用于指定响应优先级最高6位用于指定抢占式优先级,最低2位用于指定响应优先级最高7位用于指定抢占式优先级,最低1位用于指定响应优先级这就是优先级分组的概念。

--------------------------------------------------------------------------------Cortex-M3允许具有较少中断源时使用较少的寄存器位指定中断源的优先级,因此STM32把指定中断优先级的寄存器位减少到4位,这4个寄存器位的分组方式如下:第0组:所有4位用于指定响应优先级第1组:最高1位用于指定抢占式优先级,最低3位用于指定响应优先级第2组:最高2位用于指定抢占式优先级,最低2位用于指定响应优先级第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级第4组:所有4位用于指定抢占式优先级可以通过调用STM32的固件库中的函数选择使用哪种优先级分组方式,这个函数的参数有下列5种: NVIC_PriorityGroup_0 => 选择第0组NVIC_PriorityGroup_1 => 选择第1组NVIC_PriorityGroup_2 => 选择第2组NVIC_PriorityGroup_3 => 选择第3组NVIC_PriorityGroup_4 => 选择第4组接下来就是指定中断源的优先级,下面以一个简单的例子说明如何指定中断源的抢占式优先级和响应优先级:// 选择使用优先级分组第1组NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1);// 使能EXTI0中断NVIC_InitStructure.NVIC_IRQChannel=EXTI0_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1; // 指定抢占式优先级别1NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; // 指定响应优先级别0NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);// 使能EXTI9_5中断NVIC_InitStructure.NVIC_IRQChannel=EXTI9_5_IRQChannel;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; // 指定抢占式优先级别0NVIC_InitStructure.NVIC_IRQChannelSubPriority = 1; // 指定响应优先级别1NVIC_InitStructure.NVIC_IRQChannelCmd =ENABLE;NVIC_Init(&NVIC_InitStructure);--------------------------------------------------------------------------------要注意的几点是:1)如果指定的抢占式优先级别或响应优先级别超出了选定的优先级分组所限定的范围,将可能得到意想不到的结果;2)抢占式优先级别相同的中断源之间没有嵌套关系;3)如果某个中断源被指定为某个抢占式优先级别,又没有其它中断源处于同一个抢占式优先级别,则可以为这个中断源指定任意有效的响应优先级别。

关于cortex-M3的中断优先级的描述1. 和之前的ARM7不同,cortex-m3 使用NVIC(嵌套向量中断管理器)来管理系统的中断。

2. 每一个中断源的优先级由3个位来决定,这3个位就是中断优先级寄存器器里(PRIx)的INTn,这里的n 一般是A、B、C、D。

3. 每个中断源的优先级由2部分组成,一部分表示中断组别,一部分表示同组的优先级编号。

组别优先级高的中断源,可以打断组别优先级低的中断处理,同一个组的中断源不能打断正在处理的中断,只能在进入中断处理时,同时发生的两个中断源进行判别优先级。

4. 我们把中断源的优先级组别和同组内的中断编号分别用抢占式优先级别和子优先级别来表示。

他们的具体表现形式就是第2条提到的INTn。

5. 由于这INTn的3个位只能表示0-7 总共8个数字,所以在这3个位之外,系统安排了另一个寄存器来说明这3个位时如何使用的,这个寄存器就是APINT。

APINT中的PRIGROUP位域就是对中断优先级的这3个位如何分配使用进行说明的,它是针对整个系统而言的,而不是针对某一个中断源而言的。

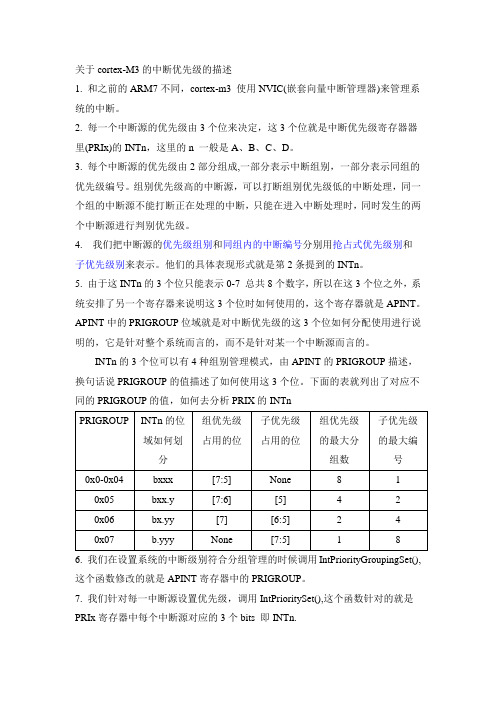

INTn的3个位可以有4种组别管理模式,由APINT的PRIGROUP描述,换句话说PRIGROUP的值描述了如何使用这3个位。

下面的表就列出了对应不同的PRIGROUP的值,如何去分析PRIX的INTn6. 我们在设置系统的中断级别符合分组管理的时候调用IntPriorityGroupingSet(), 这个函数修改的就是APINT寄存器中的PRIGROUP。

7. 我们针对每一中断源设置优先级,调用IntPrioritySet(),这个函数针对的就是PRIx寄存器中每个中断源对应的3个bits 即INTn.8. 举个例子说明,有两个中断源,A中断的中断优先级级置成INTA = b011,B 中断的中断优先级设置成INTB = b001,。

单单依靠这两个设置我们是无法判断A,B是如何进行中断调度的,我们首先要看中断的组别管理是如何的。

Stm32中断优先级相关概念与使用笔记一、基本概念1.ARM cortex_m3内核支持256个中断(16个内核+240外部)和可编程256级中断优先级的设置,与中断控制核中断优先级控制的寄存器(NVIC、SYSTICK等)属于cortex_m3内核的部分。

STM32采用了cortex_m3内核,所以这些部分仍旧保留使用,但并不是完全使用的,只是使用了一部分。

2.STM32目前支持的中断共为84个(16个内核+68个外部),和16级可编程中断优先级的设置(仅使用中断优先级设置8bit中的高4位,见后面解释)。

《参考最新101xx-107xx STM32 Reference manual, RM0008》。

以下主要对外部中断进行说明。

3.68个外部中断(通道)在STM32中已经固定的分配给相应的外部设备,每个中断通道都具备自己的中断优先级控制字节PRI_n(8位,但在STM32中只有高4位有效),每4个通道的8位中断优先级控制字(PRI_n)构成一个32位的优先级寄存器(Priority Register)。

68个通道的优先级寄存器至少有是17个32位的寄存器,它们是NVIC寄存器的一部分。

4.这4bit的中断优先级控制位还要分成2组看,从高位开始,前面的定义抢先式优先级,5.在一个系统中,通常只使用上面5种分配情况的一种,具体采用哪一种,需要在初始化时写入到一个32位寄存器AIRC(Application Interrupt and Reset Control Register)的第[10:8]这2个位中。

这3个bit位有专门的称呼:PRIGROUP(具体写操作后面介绍)。

比如你将0x05(上表的编号)写到AIRC的[10:8]中,那么也就规定了你的系统中只有4个抢先式优先级,相同的抢先式优先级下还可以有4个不同级别的子优先级。

6.AIRC中PRIGROUP的值规定了设置和确定每个外部中断通道优先级的格式。

STM32中断优先级彻底讲解一:综述STM32 目前支持的中断共为 84 个(16 个内核+68 个外部), 16 级可编程中断优先级的设置(仅使用中断优先级设置 8bit 中的高 4 位)和16个抢占优先级(因为抢占优先级最多可以有四位数)。

二:优先级判断STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。

具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪一个。

三:优先级分组既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位在NVIC应用中断与复位控制寄丛器(AIRCR)的中断优先级分组域中,可以有8种分配方式,如下:所有8位用于指定响应优先级最高1位用于指定抢占式优先级,最低7位用于指定响应优先级最高2位用于指定抢占式优先级,最低6位用于指定响应优先级最高3位用于指定抢占式优先级,最低5位用于指定响应优先级最高4位用于指定抢占式优先级,最低4位用于指定响应优先级最高5位用于指定抢占式优先级,最低3位用于指定响应优先级最高6位用于指定抢占式优先级,最低2位用于指定响应优先级最高7位用于指定抢占式优先级,最低1位用于指定响应优先级这就是优先级分组的概念。

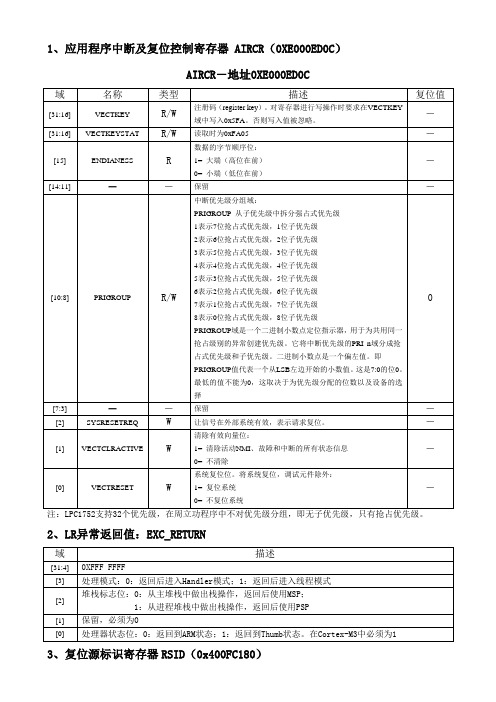

1、应用程序中断及复位控制寄存器 AIRCR(0XE000ED0C)AIRCR-地址0XE000ED0C注:LPC1752支持32个优先级,在周立功程序中不对优先级分组,即无子优先级,只有抢占优先级。

2、LR异常返回值:EXC_RETURN3、复位源标识寄存器RSID(0x400FC180)RSID-地址0x400FC180上电复位的优先级最高,可清除其它复位标志;面看门狗复位优先级最低,其它任何一类复位都可清除它的标志。

掉电复位和外部复位优先级相同,因而不能清除对方标志。

4、系统控制和状态寄存器SCS -( 0x400F C1A0)系统控制和状态寄存器SCS –地址0x400FC1A05、时钟源选择寄存器CLKSRCSEL –(0x400F C10C)时钟源选择寄存器CLKSRCSEL 地址0x400FC10C1:0CLKSRC00011011如下选择PLL0的时钟源:00:选择内部RC振荡器作为PLL0时钟源(默认)01:选择主振荡器作为PLL0时钟源10:选择RTC振荡器作为PLL0时钟源11:保留,不使用该值注:不适当地设置该值,或改变该值的不正确序列都会导致器件不能正确地操作7:2-0 保留,用户软件不要向其写入1。

从保留位读出的值未被定义NA 注:只有在PLL断开连接时,才可更换PLL输入时钟6、PLL0STAT状态寄存器对应关系图:7、PLL0控制寄存器PLL0CON –( 0x400F C080)PLL0控制寄存器PLL0CON –地址 0x400FC080位符号描述复位值0 PLLE0PLL0使能。

当该位为1并且在有效的PLL0馈送之后,该位将激活PLL0并允许其锁定到指定的频率。

(见上图中的振荡器CCO)1 PLLC0PLL0连接。

在使能和锁定PLL0,即PLLE0和PLLC0都设为1,并后面跟随有效的PLL0馈送序列后,使PLL0作为CPU时钟源、AHB外设的时钟源,以及APB外设的时钟源。

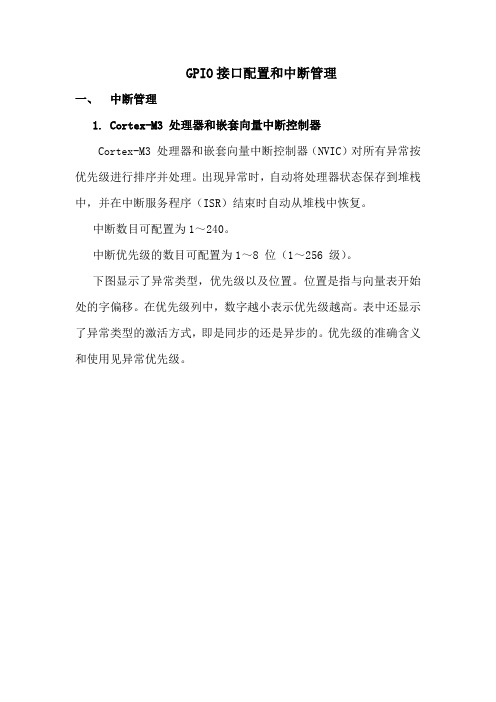

GPIO接口配置和中断管理一、中断管理1.Cortex-M3 处理器和嵌套向量中断控制器Cortex-M3 处理器和嵌套向量中断控制器(NVIC)对所有异常按优先级进行排序并处理。

出现异常时,自动将处理器状态保存到堆栈中,并在中断服务程序(ISR)结束时自动从堆栈中恢复。

中断数目可配置为1~240。

中断优先级的数目可配置为1~8 位(1~256 级)。

下图显示了异常类型,优先级以及位置。

位置是指与向量表开始处的字偏移。

在优先级列中,数字越小表示优先级越高。

表中还显示了异常类型的激活方式,即是同步的还是异步的。

优先级的准确含义和使用见异常优先级。

NVIC支持由软件指定的优先级。

通过对中断优先级寄存器的8位PRI_N区执行写操作,来将中断的优先级指定为0~255。

CM3 支持中断嵌套,使得高优先级异常会抢占(preempt)低优先级异常。

有3个系统异常:复位,NMI以及硬 fault,它们有固定的优先级,并且它们的优先级号是负数,从而高于所有其它异常。

所有其它异常的优先级则都是可编程的(但不能编程为负数)。

当发生了异常并且要响应它时, CM3 需要定位其处理例程的入口地址。

这些入口地址存储在所谓的“(异常)向量表”中当中断输入脚被 assert 后,该中断就被悬起。

即使后来中断源取消了中断请求,已经被标记成悬起的中断也被记录下来。

到了系统中它的优先级最高的时候,就会得到响应。

2.CM3响应一个中断a)入栈当处理器调用异常时,它自动将下面的 8 个寄存器按以下顺序压栈:PCxPSRr0~r3r12LR在完成压栈之后, SP 减小8个字。

入栈保护R0‐R3以及R12的原因:有一套的C函数调用标准约定(《 C/C++ Procedure Call Standard for the ARM Architecture》,AAPCS, Ref5)。

原因就在它上面:它使得中断服务例程能用C语言编写,编译器优先使用被入栈的寄存器来保存中间结果。

STM32中断优先级分组Cortex-M3 的中断优先级的分组方式最多可以有有8 种,因为CM3 强制规定:SubPriority 至少要占一个位(如果没有该强制规定,那么CM3 分组方式最多有9 种)。

我们知道:STM32 把指定中断优先级的寄存器的MSB4 位有效,共有以下5 种分组方式:第0 组方式:所有4 位用于响应优先级第1 组方式:最高1 位用于抢占式优先级,最低3 位用于响应优先级第2 组方式:最高2 位用于抢占式优先级,最低2 位用于响应优先级第3 组方式:最高3 位用于抢占式优先级,最低1 位用于响应优先级第4 组方式:所有4 位用于抢占式优先级在MISC.H 里面有:#define NVIC_PriorityGroup_0((uint32_t)0x700)#define NVIC_PriorityGroup_1((uint32_t)0x600)#defineNVIC_PriorityGroup_2((uint32_t)0x500)#defineNVIC_PriorityGroup_3((uint32_t)0x400)#defineNVIC_PriorityGroup_4((uint32_t)0x300)我们发现:第4 组方式是所有4 位用于抢占式优先级,那么这是不是与”SubPriority 至少要占一个位”相冲突呢?答案:当然不冲突了!因为虽然STM32 的”优先级配置寄存器”没有使用bit3、bit2、bit1、bit0,但是却允许从它们中分组(分组位置由应用程序中断及复位控制寄存器(AIRCR)的[10:8]决定)。

=========================第0 组采用的分组方式是bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0。

0.前言本文想解决的问题有:∙如何开启、关闭中断∙如何开启、关闭异常∙LPC177x/8x支持的中断优先级个数∙复位后,异常/中断默认的优先级∙如何设置异常/中断的优先级∙什么是优先级组,如何设置优先级组,复位后的优先级组1. Cortex-M3的异常/中断屏蔽寄存器组注:只有在特权级下,才允许访问这3个寄存器。

注:寄存器BASEPRI的有效位数受系统中表达优先级的位数影响,如果系统中只使用3个位来表达优先级,则BASEPRI有意义的值仅为0x00、0x20、0x40、0x60、0x80、0xA0、0xC0和0xE0使用MRS/MSR指令访问这三个寄存器,比如:MRS R0, BASEPRI ;读取BASEPRI到R0中MSR BASEPRI, R0 ;将R0数据写入到BASEPRI中为了快速的开关中断,CM3还专门设置了一条CPS指令,有四种用法:CPSID I ;PRIMASK=1,关中断CPSIE I ;PRIMASK=0,开中断CPSID F ;FAULTMASK=1,关异常CPSIE F ;FAULTMASK=0,开异常CMSIS-M3微控制器软件接口标准中的core_cm3.h给出了开关中断或异常的函数:1.1 开/关中断1:/**2: * @brief Set the Priority Mask value3: *4: * @param priMask PriMask5: *6: * Set the priority mask bit in the priority mask register7: */8:static __INLINE void __set_PRIMASK(uint32_t priMask)9: {10:register uint32_t __regPriMask __ASM("primask");11: __regPriMask = (priMask);12: }使用__set_PRIMASK(1)关闭中断;__setPRIMASK(0)开启中断。

Cortex-M3中断服务程序设计ISR是嵌入式应用系统获取各种事件的基本手段。

而事件是实时性问题的讨论基础和事件计算的起点。

中断优先级不同中断服务程序应有不同优先级,在允许中断嵌套时,最高优先级的中断总是能够得到响应。

只要没关中断,ISR可以中断任何任务的运行,比最高优先级的任务还要高。

Cortex-M3中断资源抢占优先级:实现中断嵌套子优先级:当抢占优先级相同的两个中断同时发生时,子优先级高的中断可以首先获得运行权。

中断优先级安排原则紧迫性:触发中断的事件允许耽误的时间越短,优先级越高。

关键性:触发中断的事件越关键,越高频繁性:触发中断的事件发生越频繁,越高快捷性:前三项相近,ISR处理越快,越高。

ISR功能应尽量简单,只要将获取的异步事件用通信手段发给关联任务就行,后续处理由关联任务完成。

1. 中断服务程序设计ISR结构4部分A:使os掌握当前中断的嵌套深度。

B:ISR功能代码。

必须调用系统通信服务函数,与其他任务进行通信。

正是这种通信功能是关联任务得到同步信号或数据,从而进入就绪状态。

不允许调用延时函数和可能被挂起的系统服务函数。

C:清除该中断的相应标志。

以便下次再次相应。

不用ISR函数,中断源的中断相应标志不同,清除中断标志的代码也不同。

D:调用退出中断函数。

实现任务调度功能。

判断是返回中断(中断嵌套)还是返回任务(原任务还是更高级任务)选择与关联任务的通信手段两种类型:A:信号型。

ISR只完成发送信号量的工作。

表示事件发生,通过信号量的同步功能出发关联任务,所有具体工作由任务完成。

B:数据型。

ISR需要完成信息采集工作,然后使用消息邮箱(消息队列)将数据发送给关联任务,由关联任务完成后续数据处理工作。

细分如下:A:触发ISR事件不包含数据。

用信号量与关联任务通信。

B:触发ISR事件包含数据低频事件。

用信号量与关联任务通信。

采集任务放在关联任务中。

C:触发ISR事件包含数据中高频事件。

Cortex-M3处理器中断和FreeRTOS中断优先级配置很多朋友对中断的一些知识还是不了解,今天就写点关于Cortex-M3处理器中断相关,以及FreeRTOS中断优先级配置的内容。

1写在前面写本文之前,先写点相关的扩展内容。

STM32属于ARM中Cortex-M系列处理器,比如:STM32F1数据Cortex-M3,STM32F7数据Cortex-M7。

可以参看我之前分享文章:从Cortex-M到Cortex-A认识ARM处理器,了解一下关于ARM 处理器的种类。

本文主要结合Cortex-M3下面STM32F1系列处理器为例来讲述中断控制相关内容。

而Cortex-M其它系列,或者说STM32其它系列关于中断的内容类似。

Cortex-M3只是STM32F1的一个内核。

反过来说STM32F1是在Cortex-M3基础上增加了一些外设(如:USART、AD等)的芯片。

2STM32中断控制NVIC:Nested Vectored Interrupt Controller,即嵌套向量中断控制器。

STM32中NVIC我们比较熟悉,编程的时候使用中断都会对NVIC进行配置。

而STM32F1中的NVIC是属于Cortex-M3中的一部分,而不是STM32增加的外设。

NVIC向量中断控制器是Cortex‐M3不可分离的一部分,它与CM3 内核的逻辑紧密耦合,有一部分甚至水乳交融在一起。

所以,NVIC相关的寄存器位于Cortex-M手册中。

讲述STM32的中断控制,还得从Cortex-M3的NVIC讲起,1.中断输入向量表Cortex-M3的NVIC支持1至240个中断输入,比如STM32中xxxIRQs,也就是中断向量表,具体的数值由芯片厂商在设计芯片时决定。

比如STM32F1的中断和异常向量表:2.中断和异常区别很多初学的朋友不知道什么是中断?什么是异常?甚至有人直接把中断和异常笼统称为“中断”。

中断和异常其实有差异,也有关联,我们常说的中断其实是包含了异常。

Cortex M3中断优先级分组的理解

学习了《EasyARM1138开发指南》中的《中断控制(Interrupt).pdf》,接触了一个新的概念——中断优先分组(Interrupt priority grouping),一开始自己不是很懂,在参考官方手册《DS-LM3S1138-11108》之后有所了解,在此分享一下自己的理解过程。

——2012/4/5

以下是《中断控制(Interrupt).pdf》中的关于中断优先分组(Interrupt priority grouping)的介绍。

ARM Cortex-M3处理器内核可以配置的中断优先级最多可以有256级。

虽然Stellaris

系列ARM只实现了8个中断优先级,但对于一个实际的应用来说已经足够了。

在较为复杂的控制系统中,中断优先级的设置会显得非常重要。

函数IntPrioritySet( )和IntPriorityGet( )用来管理一个片内外设的优先级。

当多个中断源同时产生时,优先级最高的中断首先被处理器响应并得到处理。

正在处理较低优先级中断时,如果有较高优先级的中断产生,则处理器立即转去处理较高优先级的中断。

正在处理的中断不能被同级或较低优先级的中断所打断。

函数IntPriorityGroupingSet( )和IntPriorityGroupingGet( )用来管理抢占式优先级和子优先级的分组设置,参见表1和表2的描述。

重要规则:多个中断源在它们的抢占式优先级相同的情况下,子优先级不论是否相同,如果某个中断已经在服务当中,则其它中断源都不能打断它(可以末尾连锁);只有抢占式优先级高的中断才可以打断其它抢占式优先级低的中断。

由于Stellaris系列ARM只实现了3个优先级位,因此实际有效的抢占式优先级位数只能设为0~3位。

如果抢占式优先级位数为3,则子优先级都是0,实际上可嵌套的中断层数是8层;如果抢占式优先级位数为2,则子优先级为0~1级,实际可嵌套的层数为4层;依次类推,当抢占式优先级位数为0时,实际可嵌套的层数为1层,即不允许中断嵌套。

表1 函数IntPriorityGroupingSet( )

功能设置中断控制器的优先级分组

原型void IntPriorityGroupingSet(unsigned long ulBits)

参数ulBits:指定抢占式优先级位的数目,取值0~7,但对Stellaris系列ARM取值3~7效果等同返回无

表2 函数IntPriorityGroupingGet( )

功能获取中断控制器的优先级分组

原型unsigned long IntPriorityGroupingGet(void)

参数无

返回抢占式优先级位的数目,范围0~7,但对Stellaris系列ARM返回值是3~7效果等同

我看完之后尤其不明白其中的“由于Stellaris系列ARM只实现了3个优先级位”是指3个优先等级,还是什么?如果是指3个优先等级的话,岂不是和“Stellaris系列ARM只实现了8个中断优先级”相矛盾?

对此,《DS-LM3S1138-11108》2.5.6章节明确写道:

为了增强系统控制中断的能力,NVIC支持优先级分组,将中断优先级寄存器入口分为两个区域:

●一个定义了分组后的组别所对应优先级的上层区域。

●一个定义了各组中的子优先级的下层区域。

中断异常的抢占仅仅是由组优先级决定的,也就是所谓的上层区域。

当处理器正在运行中断异常1的处理程序时,另外一个具有相同的组优先级的中断异常2产生了,那么中断异常2将不会抢占中断异常1。

如果组优先级相同的两个中断异常同时被挂起,那么他们的处理顺序是由子优先级决定的,并且他们之间不能发生嵌套,即抢占,只能等一个执行完毕后才能执行另一个。

如果组优先级和子优先级都相同,那么中断异常将按照中断向量表中中断号的顺序从小到大依次被处理。

可以总结出:组优先级高的(即值小,如1的优先级高于2)才能抢占组优先级低的中断异常;组优先级相同的中断异常之间不能相互抢占。

因此这里的组优先级即为上文提到的抢占式优先级,而子优先级就是所谓的下层区域,即分组后组内中断异常的优先等级。

有了对抢占式优先级和子优先级的认识后,我们再来看《DS-LM3S1138-11108》P120中关于优先级分组的配置。

NVIC寄存器APINT中的[10:8]为用来配置组优先级和子优先级的可配置范围,其取值与对应关系见表3。

PRIGROUP区域设置不同的值对应中断优先级寄存器PRIx中[7:5]位的二进制格式划分点的位置不同,从而选择不同的组优先级和子优先级。

表3 中断分组的组优先级和子优先级的配置

PRIGROUP 区域a 二进制格式b组优先级区域子优先级区域组优先级可配

置范围

子优先级可配

置范围

0x00~0x04 Bxxx. [7:5] 无0~7 0

0x05 Bxx.y [7:6] [7] 0~3 0~1

0x06 Bx.yy [7] [7:6] 0~1 0~3

0x07 B.yyy 无[7:5] 0 0~7

a:NVIC寄存器APINT中[10:8]位的取值

b:x表示用来控制组优先级可配置范围的二进制位,y表示用来控制子优先级可配置范围的二进制位,小数点为划分位置

理解了中断优先级分组的过程后,显而易见本文开头提出的问题:“由于Stellaris 系列ARM只实现了3个优先级位”是指3个优先等级,还是什么?明显这个“3个优先级位”是指中断优先级寄存器PRIx中[7:5]这3位二进制位,23=8正好是最多能设置8个中断抢占等级,与前面的“Stellaris系列ARM只实现了8个中断优先级”也对应起来了,这样问题就迎刃而解了!。

PS:需要保持信息的更新,手册一定要用最新版本的!

——2012/4/5

有理解有误的地方,请大家给予指正!

博文链接:/s/blog_6c5bc52e0100xfml.html。