手机开发流程框图

- 格式:docx

- 大小:21.39 KB

- 文档页数:6

Actel FPGA Libero开发流程(基础)关于Actel成立于1985年非易失性FPGA领导企业反熔丝和闪存技术2007年收益达到1.97亿美元拥有1.45亿现金和投资无债务连续72季实现预计(pro-forma)利润率 拥有550多名员工全球开发和支持中心在世界各地拥有3500多家客户100%符合RoHS标准要求需要的软件Actel 提供全套FPGA 开发软件Libero,包含Viewdraw图形输入Verilog HDL /VHDL 输入Synplify/Synplify pro 综合Designer 布局布线ModelSim AE 仿真全套软件免费下载软件License 免费使用期限一年,满一年Actel 自动发送新的License 到你的注册邮箱需要的软件(续)to: 需要的软件(续)点击客户入门,new User需要的软件(续) 给出你的信箱--Submit需要的软件(续) 完成该表格--Submit需要的软件(续)这样你就可以进行免费License 申请需要的软件(续) 申请免费License需要的软件(续) 选择一年免费Gold 。

需要的软件(续)需要的软件(续)给出你的硬盘ID ---Submit到C: dir..C868-6CBA…几分钟后你会收到license需要的软件(续)需要的软件(续)按照邮件内容设置License 即可 下载软件,顺序点击指示位置需要的软件(续)下载两个文件,安装LiberoIDE , 选择Gold,…, 再安装SP2需要的软件(续)需要的软件(续) 安装后的计算机桌面需要的软件(续)启动Libero8.5—help—license detail需要的软件(续)若license 设置不正确,软件会提示。

至此,软件已具备。

Actel FPGA 结构简介Actel的技的术优势出色的真正基于闪存的技术全面的低功耗特性较任何其它解决方案更为安全卓越的可靠性上电即用高集成度实现更低的总体成本可重编程和易失性Actel FPGAActel FPGA 技术:Flash: Flash 开关Antifuse: 反熔丝 目前产品系列FusionIGLOO\e\plusProASIC3\EProASIC PLUSAxceleratorA54SXAeXA54SXFPGA ChipRAM/FIFOCharge Pumps Pro I/OVersaTileFROM NVM JTAG ISPISP AES DecryptionPLL/CCC VersaNets设计Libero开发流程(基础)Libero Demo 设计该设计包含下列模块/单元: •1 PLL锁相环•2 两个计数器count1,count2 •1 个或门产生异步复位 •Clock 和Reset 输入•3 LED 驱动输出Libero开发流程(基础)-创建新项目-创建Count1/PLL 模块-创建Count2模块-创建顶层模块-功能仿真-使用Synplify综合-布局布线-编程设计框图Step 1 –创建新项目Libero_demo 选择Project—New Project创建新项目Libero_demo(续)键入项目名,项目位置,选择使用的语言,所有设计存储于所选位置,以项目名字为目录的子目录下,--选择下一步创建新项目Libero_demo(续)选择系列,门数和封装,并选择完成,得到右边创建锁相环PLL 分频或倍频选择右边Catalog—clock & management—PLL static-双击鼠标右健,如下图,选择相应项创建锁相环PLL 分频或倍频创建锁相环PLL 分频或倍频红色下划线数字是你真正得到的频率和相位,我们得到0.75Mhz 的时钟,选择产生,得到如下,输入pll1,--OK创建锁相环PLL 分频或倍频可以看到已产生pll1 和使用的资源报告产生计数器count1如同锁相环产生分频,选择Catalog—Basic blocks—counter—双击鼠标右健接着产生计数器如图选择实现方式,宽度,清零等,最后产生接着产生计数器可以看到有两个模块产生Count2 的产生下面我们通过HDL 编辑器产生第二个计数器,点击HDL Editer, 如下图Count2 的产生我们给文件名count2, 注意文件名和模块名可以不一致,一个文件可以包含多个模块Count2 的产生在文本编辑器里完成如图输入,击鼠标右健给予语法检查顶层模块top到目前,我们已建立了两个计数器,一个PLL 分频模块,我们需要在顶层用这些建立设计用建立计数器count2同样的方法建立top文件内容如下:module top(input CLOCK, input RESET,output[2:0] q);wire tb_clka;wire tb_aclr;wire tb_lock,tb_gla;wire [17:0]tb_q;assign tb_aclr=(~tb_lock)| RESET;/*********** pll1, counter1, counter2 instantiations *********/pll1 p1(.POWERDOWN(1),.CLKA(CLOCK),.LOCK(tb_lock),.GLA(tb_gla));count1 c1(.Aclr(tb_aclr),.Clock(tb_gla),.Q(tb_q));count2 c2(.aclr(tb_aclr),.clock(tb_q[17]),.Q(q));endmodule问题:我怎么知道PLL1和count1 模块的信号名?答案:打开相应生成的HDL 文件,Copy 模块端口即可顶层模块Libero并不知道顶层是那个模块,你需要如下设置仿真设计需要输入,这些输入在testbench模块里生成。

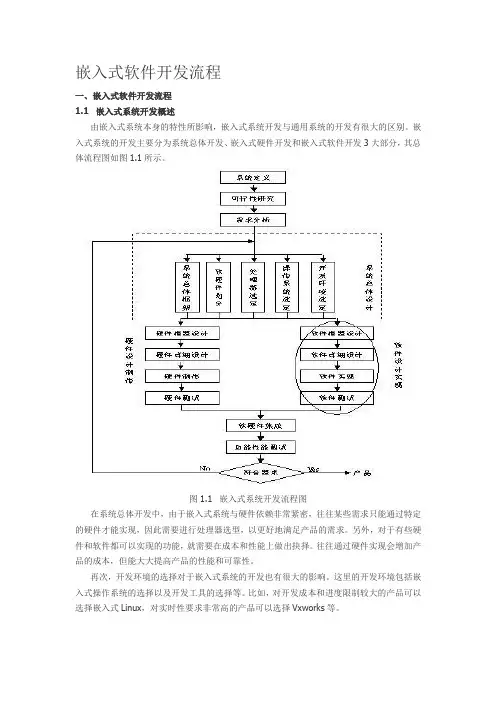

嵌入式软件开发流程一、嵌入式软件开发流程1.1 嵌入式系统开发概述由嵌入式系统本身的特性所影响,嵌入式系统开发与通用系统的开发有很大的区别。

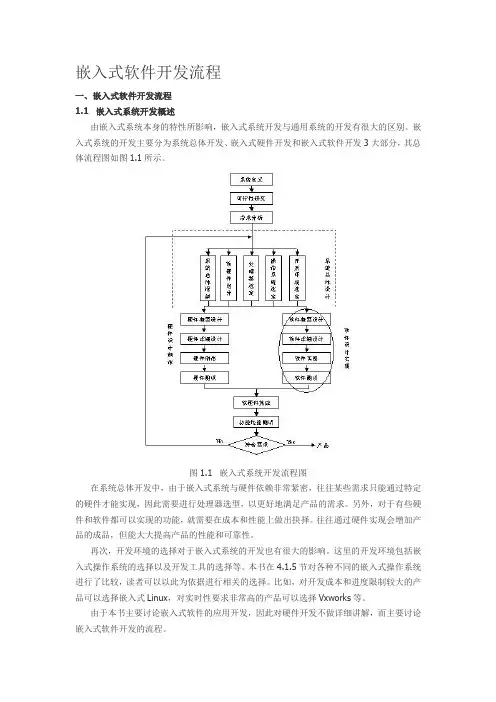

嵌入式系统的开发主要分为系统总体开发、嵌入式硬件开发和嵌入式软件开发3大部分,其总体流程图如图1.1所示。

图1.1 嵌入式系统开发流程图在系统总体开发中,由于嵌入式系统与硬件依赖非常紧密,往往某些需求只能通过特定的硬件才能实现,因此需要进行处理器选型,以更好地满足产品的需求。

另外,对于有些硬件和软件都可以实现的功能,就需要在成本和性能上做出抉择。

往往通过硬件实现会增加产品的成本,但能大大提高产品的性能和可靠性。

再次,开发环境的选择对于嵌入式系统的开发也有很大的影响。

这里的开发环境包括嵌入式操作系统的选择以及开发工具的选择等。

比如,对开发成本和进度限制较大的产品可以选择嵌入式Linux,对实时性要求非常高的产品可以选择Vxworks等。

1.2 嵌入式软件开发概述嵌入式软件开发总体流程为图4.15中“软件设计实现”部分所示,它同通用计算机软件开发一样,分为需求分析、软件概要设计、软件详细设计、软件实现和软件测试。

其中嵌入式软件需求分析与硬件的需求分析合二为一,故没有分开画出。

由于在嵌入式软件开发的工具非常多,为了更好地帮助读者选择开发工具,下面首先对嵌入式软件开发过程中所使用的工具做一简单归纳。

嵌入式软件的开发工具根据不同的开发过程而划分,比如在需求分析阶段,可以选择IBM的Rational Rose等软件,而在程序开发阶段可以采用CodeWarrior(下面要介绍的ADS 的一个工具)等,在调试阶段所用的Multi-ICE等。

同时,不同的嵌入式操作系统往往会有配套的开发工具,比如Vxworks有集成开发环境Tornado,WindowsCE的集成开发环境WindowsCE Platform等。

此外,不同的处理器可能还有对应的开发工具,比如ARM的常用集成开发工具ADS、IAR和RealView等。

a n d r o i d开发计算器设计开发报告Revised by Petrel at 2021《安卓开发》程序设计报告题目简单计算器开发专业(班级)网工111班姓名张波波学号指导教师赵(老师)日期2014.5.7目录一、设计说明: (4)1.设计内容:Android简单应用程序开发,简单计算器。

(4)2程序说明: (4)二、开发环境: (4)三、概要设计: (4)3.1系统的总体 (4)四、程序流程和系统功能设计 (5)4.1程序流程设计 (5)4.2.系统功能设计 (6)4.3基于Android平台系统具体设计 (6)4.3.1总体模块详细设计 (6)4.3.2输入模块详细设计 (6)4.3.3显示模块详细设计 (7)4.3.4计算模块详细设计 (7)五、计算器系统实现 (8)5.1Android应用程序构成 (8)六、截图说明 (9)1、图标 (9)2界面 (9)3运算界面 (9)4错误输入 (9)5设计平台界面 (9)6签名导出apk (9)七、总结 (9)课程设计任务书一、设计说明:1.设计内容:Android简单应用程序开发,简单计算器。

2程序说明:1、计算器界面友好,方便使用。

2、具有基本的加、减、乘、除功能,还有+—、开方、平方功能。

3、能够判断用户输入运算数是否正确。

4、4、支持小数运算。

5、具有退格功能,能够删除最后一个输入,ce。

6、具有清除功能,删除所有,c。

7、具有结果存储功能,能够显示存储器状态,支持触屏手机。

8、9、支持最低版本2.0,最高版本4.4。

开发时为4.2二、开发环境:开发环境:本系统是采用Eclipse+EclipseMe+JDK+ADT作为开发平台。

事实上为了节约时间就直接用Google公司安给的直接绑定好的adt-bundle-windows-x86_64开发,只需要配置下环境变量,无需要关联等操作。

三、概要设计:3.1系统的总体整个程序基于android技术开发,出总体模块外主要分为输入模块、显示模块以及计算模块(包括一些其她功能)这三大部分。

嵌入式软件开发流程一、嵌入式软件开发流程1.1 嵌入式系统开发概述由嵌入式系统本身的特性所影响,嵌入式系统开发与通用系统的开发有很大的区别。

嵌入式系统的开发主要分为系统总体开发、嵌入式硬件开发和嵌入式软件开发3大部分,其总体流程图如图1.1所示。

图1.1 嵌入式系统开发流程图在系统总体开发中,由于嵌入式系统与硬件依赖非常紧密,往往某些需求只能通过特定的硬件才能实现,因此需要进行处理器选型,以更好地满足产品的需求。

另外,对于有些硬件和软件都可以实现的功能,就需要在成本和性能上做出抉择。

往往通过硬件实现会增加产品的成品,但能大大提高产品的性能和可靠性。

再次,开发环境的选择对于嵌入式系统的开发也有很大的影响。

这里的开发环境包括嵌入式操作系统的选择以及开发工具的选择等。

本书在4.1.5节对各种不同的嵌入式操作系统进行了比较,读者可以以此为依据进行相关的选择。

比如,对开发成本和进度限制较大的产品可以选择嵌入式Linux,对实时性要求非常高的产品可以选择Vxworks等。

由于本书主要讨论嵌入式软件的应用开发,因此对硬件开发不做详细讲解,而主要讨论嵌入式软件开发的流程。

1.2 嵌入式软件开发概述嵌入式软件开发总体流程为图4.15中“软件设计实现”部分所示,它同通用计算机软件开发一样,分为需求分析、软件概要设计、软件详细设计、软件实现和软件测试。

其中嵌入式软件需求分析与硬件的需求分析合二为一,故没有分开画出。

由于在嵌入式软件开发的工具非常多,为了更好地帮助读者选择开发工具,下面首先对嵌入式软件开发过程中所使用的工具做一简单归纳。

嵌入式软件的开发工具根据不同的开发过程而划分,比如在需求分析阶段,可以选择IBM的Rational Rose等软件,而在程序开发阶段可以采用CodeWarrior(下面要介绍的ADS 的一个工具)等,在调试阶段所用的Multi-ICE等。

同时,不同的嵌入式操作系统往往会有配套的开发工具,比如Vxworks有集成开发环境Tornado,WindowsCE的集成开发环境WindowsCE Platform等。

基于WiFi的智能LED照明控制系统的设计引言随着互联网技术的不断发展,智能家居的出现为人们享受生活提供了一个广阔的平台。

无线传输技术被广泛应用到具有远程控制功能的智能LED照明系统中,通过手机APP远程控制终端设备的应用越来越多。

目前,主流的无线传输技术主要有NRF905或者NRF2401等短距离无线通信、Zigbee技术、蓝牙、GSM和WiFi等。

WiFi技术具有速度快、可靠性高的特点,可以方便组建网络,对于普通的家庭照明控制,它是实现无线智能照明系统的较好的解决方案[1,2]。

设计一个基于WiFi的智能LED 照明控制系统,实现移动终端远程控制智能家居中的LED灯,具有很好的市场应用价值。

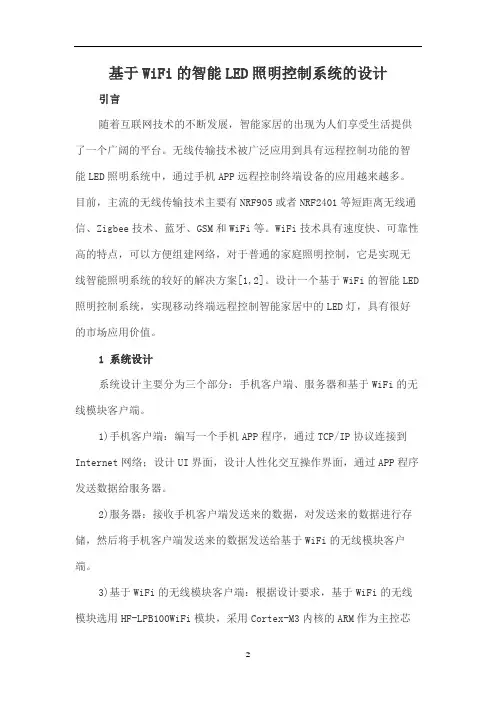

1 系统设计系统设计主要分为三个部分:手机客户端、服务器和基于WiFi的无线模块客户端。

1)手机客户端:编写一个手机APP程序,通过TCP/IP协议连接到Internet网络;设计UI界面,设计人性化交互操作界面,通过APP程序发送数据给服务器。

2)服务器:接收手机客户端发送来的数据,对发送来的数据进行存储,然后将手机客户端发送来的数据发送给基于WiFi的无线模块客户端。

3)基于WiFi的无线模块客户端:根据设计要求,基于WiFi的无线模块选用HF-LPB100WiFi模块,采用Cortex-M3内核的ARM作为主控芯片,控制WiFi模块。

通过TCP/IP协议连接服务器,然后接收手机客户端发送来的数据,识别后通过控制继电器来实现控制LED的通断、色度和亮度[3],系统总体设计如图1所示。

图1 系统框图Fig.1 Diagram of system block2 硬件电路设计1)LED电路。

为了实现LED的色度控制,选用RGB红绿蓝七彩色LED 灯珠,控制器的P2口接地控制所有LED的通断,P1口控制蓝色LED,P3口控制绿色LED,P4口控制红色LED。

通过P1、P3和P4三原色合成七种颜色,设计中通过一个GPIO和三个PWM可实现控制整个LED输出不同的颜色和亮度。

基于手机APP的闸机远程控制系统设计刘虹羚【期刊名称】《《电子世界》》【年(卷),期】2019(000)022【总页数】2页(P149-150)【作者】刘虹羚【作者单位】南京科技职业学院电气与控制学院【正文语种】中文本系统用于自动检票机设备,主要实现自动检票机的远程控制和状态数据的获取与分析。

系统包括闸机通道控制器模块,闸机主控单元模块和闸机监控器模块。

系统设计的核心是闸机监控器模块,分为硬件设计和软件设计两个方面。

闸机监控器能够与闸机主控单元实现通讯,获取设备故障信息、报警信息、工作信息等状态数据,并通过GPRS模块将状态数据上传到云端服务器,进行数据的分析与统计。

手机APP应用软件,能够对闸机数据进行获取和显示,并且可以对闸机进行远程操作。

引言:自动检票机,也称闸机,是一种智能通道管理设备,用于管理不同身份人员的通行,可应用于写字楼、景区、地铁、学校、工厂等场所。

闸机设备最基本的功能是实现身份验证(或支付),并对通过授权的人员进行放行,适用于各种收费、门禁场合的出入口通道处。

目前,国内外市场上的闸机能通过有线网将设备内的数据信息与后台服务器进行交互,工作人员需要通过管理计算机对闸机进行远程控制与管理,但是无法让现场管理员在本地方便地对闸机设备进行实时的设置、状态监测和远程控制,这给本地现场的设备管理工作带来了一定的难度。

本文介绍的基于手机APP的闸机远程控制系统,本地管理员可以通过手机APP对闸机进行远程控制和状态监测,闸机监控器可以将闸机数据与后台云端联网,实现设备的预测性维护以及全生命周期管理。

本文在系统总体设计基础上,重点研究了闸机监控器子系统的设计,包括硬件设计和软件设计两个部分。

1 系统总体设计整个闸机控制系统结构如图1所示,主要包含工控机、通道控制器、通道传感器、伺服控制器、闸机监控器等。

工控机是闸机的主控单元,与读卡器、人脸识别器、二维码扫描器等身份验证模块连接,实现对票卡、人员、或二维码的有效性验证,并将验证结果,发送给通道控制器。

PSoC开发流程和一般MCU开发流程有什么区别?低调的华丽——PSoC 6 BLE Pioneer Kit 评测系列之二前言老子有云:大音希声,大象无形。

低调而不失张扬,这是笔者初见PSoC 6 BLE Pioneer 时的感受。

虽然早已在媒体介绍上见过PSoC 6 BLE Pioneer的宣传照片,但是第一次看到PSoC 6 BLE Pioneer摆在面前,还是小小的惊喜了一下。

PSoC 6 BLE Pioneer无论在设计还是包装,到软件开发等方面,都为我们带来了更好的体验!PSoC是Cypress推出的可编程片上系统,2002年推出第一款商用产品PSoC 1,十几年来不断推陈出新,今天的PSoC 6系列,可谓是PSoC产品的集大成者。

硬件内核也从最初的M8C演变到了今天的ARM Cortex-M4,PSoC 63则使用了双核,即包含ARM Cortex-M4及ARM Cortex-M0 。

PSoC 6 BLE Pioneer套件还为我们带来了CapSense电容触控和最新的BLE 5及USB Type-C的全新体验,加上一块2.7吋的墨水屏,配合PSoC 6的业内最低功耗特性,配置不可谓不华丽。

先简单科普下PSoC。

PSoC的全称是Programmable System-on-Chip,即可编程片上系统或可编程片上芯片。

PSoC一般由内核、可配置的模拟及数字模块以及可编程的互联线路组成。

与FPGA相比,二者都需要在上电时对设备进行配置,不同的是PSoC通过从内置闪存中加载指令来进行配置。

可配置模块是PSoC与其它微控制器最大的区别。

开箱与PSoC 4 Pioneer Kit不同的是,PSoC 6 BLE Pioneer套件中还配备了墨水屏,所以体积也大了许多,看上去倒像是个手机盒子。

PSoC 6 BLE Pioneer的目标很明确,面向IoT应用,主打低功耗、灵活配置及内置安全功能,不过以文无第一,武无第二的角度来看,Cypress此次显得非常自信,宣称是自己是最低功耗的领导者。