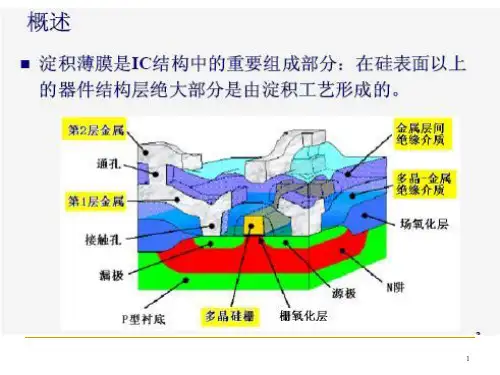

第六章 薄膜淀积

- 格式:ppt

- 大小:3.89 MB

- 文档页数:129

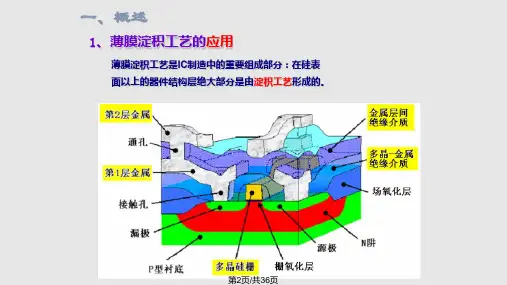

常用真空薄膜淀积技术一、物理汽相淀积所谓PVD是原子直接以气态形式从淀积源运动到衬底表面从而形成固态薄膜。

它是一种近乎万能的薄膜技术,应用PVD技术可以制备化合物、金属、合金等薄膜,PVD主要可以分为蒸发淀积、溅射淀积。

蒸发淀积是将源的温度加热到高温,利用蒸发的物理现象实现源内原子或分子的运输,因而需要高的真空,蒸发淀积中应用比较广泛的热蒸发和电子束蒸发。

电子束蒸发和热蒸发主要是加热方式不同,热蒸发的特点是工艺简单、成本低,由于热蒸发的受自身的加热方式限制,很难达到很高的温度,因此不适合制备难熔金属和一些高熔点的化合物,同时因为热蒸发是通过加热坩埚来加热坩埚内的金属,而坩埚在高温下会也会存在蒸发现象,所以热蒸发的最大的缺点是淀积过程中容易引入污染。

电子束蒸发最大的优点是几乎不引入污染。

因为其加热方式是电子束直接轰击金属,同时电子束蒸发可以制备更多种类的薄膜,唯一的缺点是在淀积过程中会有X射线产生。

表1是热蒸发和电子束蒸发的比较。

溅射可以分为直流溅射、直流磁控溅射、射频溅射、溅射主要利用惰性气体的辉光放电现象产生离子,用高压加速离子轰击靶材产生加速的靶材原子从而淀积在衬底表面,溅射技术的最大优点是理论上它可以制备任何真空薄膜,同时在台阶覆盖和均匀性上要优于蒸发淀积。

表2是蒸发和溅射技术的比较。

当然,除了上文介绍的主流PVD,还有激光脉冲淀积、等离子蒸发、分子束外延等补充形式。

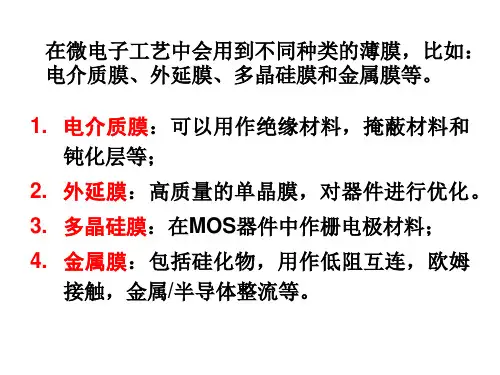

二、化学汽相淀积CVD一词最早出现在20世纪6O年代,所谓CVD是反应物以气态到达加热的衬底表面发生化学反应,形成固态薄膜和气态产物。

利用化学气相淀积可以制备,从金属薄膜也可以制备无机薄膜。

化学气相淀积种类很多,主要有:常压CVD (APCVD),低压CVD(LPCVD)、超低压CVD(VLPCVD)、等离子体增强型CVD (PECVD)、激光增强型CVD(LECVD),金属氧化物CVD(MOCVD),其他还有电子自旋共振CVD(ECRCVD)、汽相外延(VPE)等方法,按着淀积过程中发生化学的种类不同可以分为热解法、氧化法、还原法、水解法、混合反应等。