ATmega128 单片机硬件电路设计

- 格式:docx

- 大小:19.93 KB

- 文档页数:6

基于ATmega128单片机的时序控制器的设计探空火箭主要用于近地空间的探测和科学试验,探空火箭一般为无控火箭,其自身无飞行控制和制导设备,结构简单、成本低廉。

时序控制器为箭上火工品提供点爆时序,使探空火箭在预定高度释放有效载荷进行探测,或实现多级探空火箭箭体的分离。

作为探空火箭上唯一的控制器,要求时序控制器必须准确、可靠地进行点爆控制,保障试验过程的安全性。

为满足某探空火箭上火工品的准确、可靠点爆,用ATmega128单片机设计了一种时序控制器,对其软、硬件及可靠性设计等进行了阐述。

1 系统硬件设计时序控制系统由地面测发控台和箭上时序控制器组成。

地面测发控台在地面测试时向箭上时序控制器发送一系列测试指令,并将任务要求的箭上火工品点爆时间发给时序控制器储存,即时序装订。

时序控制器在地面测试时检测自身状态,在收到每一条测试指令后向地面测发控台返回应答信息,以保证双方通信的可靠性,并完成时序装订、转电、模拟测试等功能;在火箭飞行过程中,时序控制器在装订时刻发出控制信号,完成箭上各火工品的起爆。

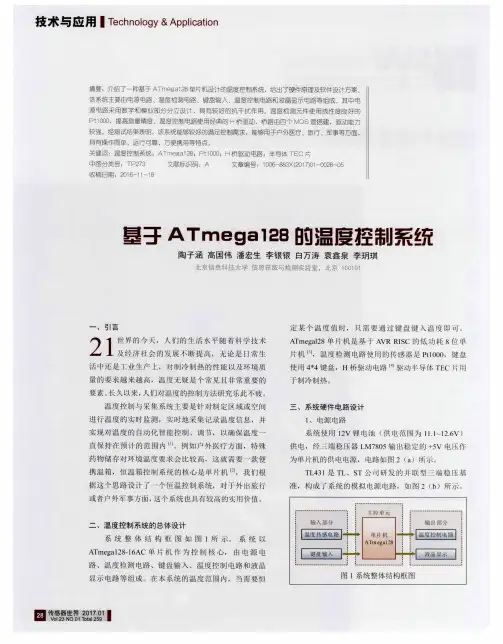

时序控制器主要由RS422通讯接口、单片机、转电控制、点爆控制电路等组成,系统的功能框图如图1所示。

RS422通讯接口主要由带有电气隔离功能的RS422驱动器MAX1490B实现。

具有限摆率特性的MAX1490B驱动器可以降低电磁辐射,并减小因错误的终端连线造成的影响,允许数据无误传输的最高速率为250kbps。

1.1 单片机模块时序控制器的控制核心是单片机。

选用的ATmega128是ATMEL公司基于AVR RISC结构的8位低功耗CMOS微处理器,其外设包括2个16位的计数器/定时器,2个可编程的串行USART,8路10位ADC等;具有上电复位以及可编程的掉电检测功能,省去了外部复位电路,增加了复位的可靠性;具有128K字节的系统内可编程Flash 和4K字节的EEPROM非易失性数据存储器,均可用于数据存储,EEPROM寿命可达100,000次写/擦除周期[1]。

基于Atmega128单片机设计的嵌入式控制器

采用Atmega128单片机设计的嵌入式控制器,模拟量输入通道用

Atmega128片内A/D转换器,输出用AD421D/A转换器,数字量I/O通道配

置高速先耦器件.用LCCavr编译器修改OSTaskStklnit()函数及其相关文件,

定义数据类型等以实现MICroC/OS-Ⅱ的移植.

1 引言

嵌入式控制器是机电设备实现自动化的核心部件。

故以大型机电设备为控制对象,利用高性能Atmega 128微处理器,设计了具有现场总线(CANBUS)网络通信和一定通用性的多功能嵌入式智能控制器。

2 硬件设计

系统的硬件结构如图1。

本控制器的核心采用64管脚TQFP封装的Atmega128芯片,具有53个

可编程的I/O引脚,片内集成有128KB闪存、4KB EEPROM 和

4KBSRAM,适合I/O通道和存储空间的需求。

ATmega128 单片机硬件电路设计在本系统中,本小节主要讲ATmega128 单片机的内部资源、工作原理和硬件电路设计等。

2.5.1 ATmega128 芯片介绍ATmega128 为基于AVR RISC 结构的8 位低功耗CMOS 微处理器。

片内ISP Flash 可以通过SPI 接口、通用编程器,或引导程序多次编程。

引导程序可以使用任何接口来下载应用程序到应用Flash 存储器。

通过将8 位RISC CPU 与系统内可编程的Flash 集成在一个芯片内,ATmega128 为许多嵌入式控制应用提供了灵活而低成本的方案。

ATmega128 单片机的功能特点如下:(1)高性能、低功耗的AVR 8 位微处理器(2)先进的RISC 结构①133 条指令大多数可以在一个时钟周期内完成② 32x8 个通用工作寄存器+外设控制寄存器③全静态工作④工作于16 MHz 时性能高达16 MIPS ⑤只需两个时钟周期的硬件乘法器(3)非易失性的程序和数据存储器① 128K 字节的系统内可编程Flash ②寿命: 10,000 次写/ 擦除周期③具有独立锁定位、可选择的启动代码区(4)通过片内的启动程序实现系统内编程① 4K 字节的EEPROM ② 4K 字节的内部SRAM ③多达64K 字节的优化的外部存储器空间④可以对锁定位进行编程以实现软件加密⑤可以通过SPI 实现系统内编程(5)JTAG 接口(与IEEE 1149.1 标准兼容)①遵循JTAG 标准的边界扫描功能②支持扩展的片内调试③通过JTAG 接口实现对Flash,EEPROM,熔丝位和锁定位的编程(6)外设特点①两个具有独立的预分频器和比较器功能的8 位定时器/ 计数器②两个具有预分频器、比较功能和捕捉功能的16 位定时器/ 计数器③具有独立预分频器的实时时钟计数器④两路8 位PWM ⑤ 6 路分辨率可编程(2 到16 位)的PWM ⑥输出比较调制器⑦ 8 路10 位ADC ⑧面向字节的两线接口⑨两个可编程的串行USART ⑩可工作于主机/ 从机模式的SPI 串行接口(7)特殊的处理器特点①上电复位以及可编程的掉电检测②片内经过标定的RC 振荡器③片内/ 片外中断源④ 6 种睡眠模式: 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及扩展的Standby 模式⑤可以通过软件进行选择的时钟频率⑥通过熔丝位可以选择ATmega103 兼容模式⑦全局上拉禁止功能ATmega128 芯片有64 个引脚,其中60 个引脚具有I/O 口功能,资源比较丰富,下面对ATmega128 的各个引脚做简单介绍:VCC:数字电路的电源。

A VR的中断源比较多,尤其是ATmega128,一共有35个外部以及内部中断源。

通常情况下,Flash程序存储器空间的最低位置(0x0000-0x0045)定义为复位和中断向量空间。

完整的中断向量见第二章表2-23。

在中断向量表中,处于低地址的中断向量所对应的中断拥有高优先级,所以,系统复位RESET拥有最高优先级。

A.中断设计注意点:1.具备Bootloader功能的A VR,其中断向量区可以在Flash程序存储器空间最低位置和Bootloader区的头部来回迁移,这主要用于配合Bootloader程序的应用。

如果不使用Bootloader功能,一般不要中断向量区进行迁移。

2.Flash较小的A VR芯片,其一个中断向量占据1个字的空间,用于放置一条相对转移RJMP指令(范围-2K~+2K字),跳到中断服务程序。

对于不使用的中断,在中断向量区中应放置1条中断返回指令RETI,增强程序的抗干扰性。

3.ATmega128的Flash空间为64K字节,因此它的一个中断向量占据2个字的空间,用于放置一条绝对转移JMP指令(指令长度为2个字),跳到中断服务程序。

对于不使用的中断,在中断向量区中应连续放置2条中断返回指令RETI,增强程序的抗干扰性。

当使用汇编语言编写系统程序时应注意。

4.当MCU响应一个中断时,其硬件系统会自动中断返回地址压入系统堆栈,并将关闭全局中断响应(硬件将中断标志I位清0),清除该中断的中断标志位;执行中断返回指令RETI时,硬件会先允许全局中断响应(硬件将中断标志I位置1),然后从系统堆栈中弹出返回地址到PC程序计数器中,继续执行被中断打断的程序。

除此之外,MCU的硬件没有对中断保护做其他处理。

5.因此,用户在编写中断服务程序时,首先要编写中断现场保护程序,如保护MCU的状态寄存器等。

在中断返回之前,不要忘记恢复中断现场。

6.如果设置和允许外部中断响应,即使是外部INT0..7引脚设置为输出方式,在引脚上的电平变化也会触发外部中断的发生,这一特性提供了使用软件产生中断的途径。

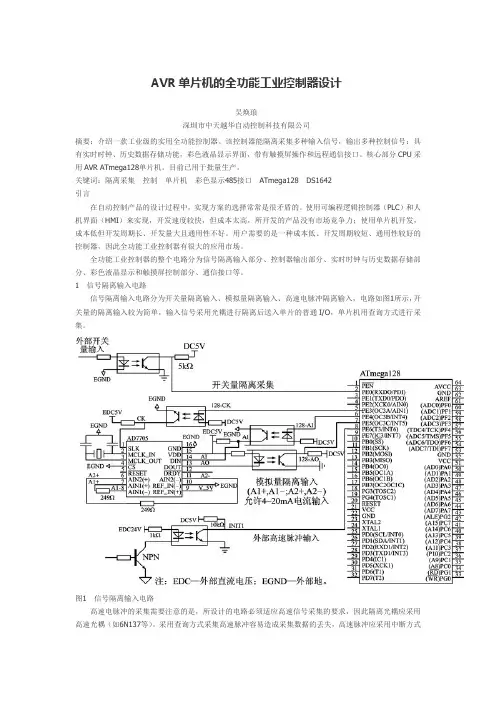

AVR单片机的全功能工业控制器设计吴焕琅深圳市中天越华自动控制科技有限公司摘要:介绍一款工业级的实用全功能控制器。

该控制器能隔离采集多种输入信号,输出多种控制信号;具有实时时钟、历史数据存储功能,彩色液晶显示界面,带有触摸屏操作和远程通信接口。

核心部分CPU采用AVR ATmega128单片机。

目前已用于批量生产。

关键词:隔离采集控制单片机彩色显示485接口ATmega128DS1642引言在自动控制产品的设计过程中,实现方案的选择常常是很矛盾的。

使用可编程逻辑控制器(PLC)和人机界面(HMI)来实现,开发速度较快,但成本太高,所开发的产品没有市场竞争力;使用单片机开发,成本低但开发周期长、开发量大且通用性不好。

用户需要的是一种成本低、开发周期较短、通用性较好的控制器,因此全功能工业控制器有很大的应用市场。

全功能工业控制器的整个电路分为信号隔离输入部分、控制器输出部分、实时时钟与历史数据存储部分、彩色液晶显示和触摸屏控制部分、通信接口等。

1信号隔离输入电路信号隔离输入电路分为开关量隔离输入、模拟量隔离输入、高速电脉冲隔离输入,电路如图1所示,开关量的隔离输入较为简单,输入信号采用光耦进行隔离后送入单片的普通I/O,单片机用查询方式进行采集。

图1信号隔离输入电路高速电脉冲的采集需要注意的是,所设计的电路必须适应高速信号采集的要求,因此隔离光耦应采用高速光耦(如6N137等)。

采用查询方式采集高速脉冲容易造成采集数据的丢失,高速脉冲应采用中断方式进行采集。

模拟量隔离采集是本控制器的一个重点和难点,笔者之前采用了线性光耦等多种方式进行模拟量的隔离采集实验,均未获满意的效果。

这里采用一种先将模拟量数字化(使用AD7705),然后通过有光耦隔离的数据口送到CPU进行模拟量隔离采集的方式,效果理想。

2控制器输出电路控制器的输出方式有继电器输出、晶体管输出、模拟电压输出,如图2所示。

继电器输出和晶体管输出电路较为简单,这里不作详细的介绍。

基于ATmega128单片机的压电式贾卡控制系统设计0 引言贾卡经编机贾卡装置自1884 年问世以来,已从机械式发展到电磁式和现在的压电式,即Piezo 贾卡系统,彻底改变了贾卡装置需要通丝、移位针等繁杂部件的特点,使贾卡经编机提花部分的机构大大简化,速度有了很大提高。

此外,与计算机辅助花型设计系统配合,加快了贾卡经编织物的设计,简化了上机工艺,缩短了产品更新周期。

Piezo 贾卡的成功开发促进了经编机设备的不断发展进步,目前机器速度已经大大提高,提花原理也得到了进一步的发展。

Piezo 贾卡导纱针主要由三部分组成:压电陶瓷、导纱针握持端和可替换的贾卡导纱针。

Piezo 贾卡元件用于控制经编机上贾卡导纱针的左右偏移。

它由两片压电陶瓷组成,中间由玻璃纤维层隔离(绝缘)。

压电陶瓷具有“逆压电效应”,将其置于外电场将产生几何变形。

通过控制贾卡元件两侧交替加上去的正负电压,使电陶瓷变形,进而使导纱针向左或向右偏移。

由于压电陶瓷效果像电容一样,使得压电式导纱针能保持在它的偏移位置上。

贾卡导纱针左右两面都有定位快,可以保证精确的隔离。

设计贾卡控制系统的主要目的就足要根据经编机的需求,把花型数据准确适时地执行到导纱针,实现经编机的提花。

本文根据实际经编机设备的开发需求,选用AVR 系列单片机ATmega128 为主控芯片,设计了压电式贾卡控制系统,包括控制系统的软、硬件设计,压电陶瓷贾卡装置的驱动电路等。

系统将计算机技术和传统的提花工艺结合,较好地解决了传统提花工艺中存在的问题,降低了成本,简化了操作过程,缩短了新产品的开发周期。

该系统由于成本低,结构简单,特别适用于实际贾卡经编机设备控制部分的技术改进,具有较好的可靠性与实用性。

本系统的设计原理和结构的可靠性与实用性已通过样机试运行得以证实。

1 硬件设计1.1 系统总体结构图1 所示为系统总体结构框图。

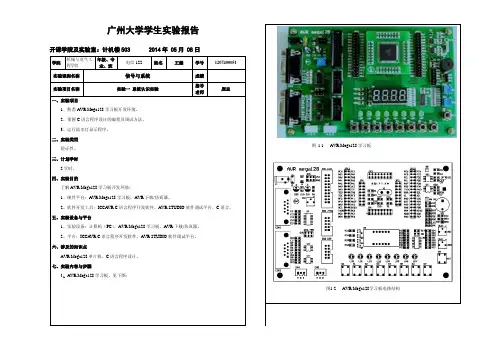

广州大学学生实验报告开课学院及实验室:计机楼503 2014年 05月 08日学院机械与电气工程学院年级、专业、班电信122 姓名王健学号1207400051实验课程名称信号与系统成绩实验项目名称实验一系统认识实验指导老师庞志一、实验项目1、熟悉AVR Mega128学习板开发环境。

2、掌握C语言程序设计的编程及调试方法。

3、运行流水灯显示程序。

二、实验类型验证性。

三、计划学时2学时。

四、实验目的了解AVR Mega128学习板开发环境:1、硬件平台:AVR Mega128学习板,AVR下载/仿真器。

2、软件开发工具:ICCA VR C语言程序开发软件、AVR STUDIO软件调试平台、C语言。

五、实验设备与平台1、实验设备:计算机(PC),AVR Mega128学习板,AVR下载/仿真器。

2、平台:ICCA VR C语言程序开发软件、AVR STUDIO软件调试平台。

六、涉及的知识点AVR Mega128单片机、C语言程序设计。

七、实验内容与步骤1、AVR Mega128学习板,见下图:图 1.1 AVR Mega128学习板图1.2 AVR Mega128学习板电路结构图1.3 AVR Mega128学习板硬件系统组成连接系统步骤:1)连接AVR下载/仿真器:将AVR下载/仿真器的排线接到AVR Mega128学习板的CH2 JTAG 插座;使用USB连线将AVR下载/仿真器和PC 连接起来。

2)连接AVR Mega128学习板电源:将电源线的圆插头插入到AVR Mega128学习板的J1插座,另一端扁形插头插入PC的USB口,系统运行内置的程序。

2、修改、编译程序1)打开ICCA VR软件,选择Project下拉菜单的Open…打开工程。

图1.4 打开工程示意图2)打开例子程序里面的工程文件01LED.prj:图1.5 打开工程文件示意图3)打开工程后,工程栏里面显示工程包含文件信息,双击右边工程栏中的main.c文件,程序显示在编辑区,可以修改程序。

第24卷第7期V o l .24N o .7荆楚理工学院学报J o u r n a l o f J i n g c h u U n i v e r s i t y o f T e c h n o l o g y 2009年7月J u l .2009[收稿日期]2009-06-17[作者简介]汤剑锋(1964-),男,福建华安人,漳州职业技术学院讲师。

研究方向:电子技术应用。

A T m e g a 128单片机仿真系统设计及实现汤剑锋(漳州职业技术学院电子工程系,福建漳州 363000)[摘 要] 本仿真系统采用A T m e g a 128单片机作为控制核心,利用其强大的兼容性和处理能力,以及丰富的接口等特点使整个系统的电路结构简单、可靠性高。

A T m e g a 128单片机仿真系统的硬件部分由电源电路、复位电路、晶振电路、模/数转换滤波电路、I S P 下载接口电路、J T A G 仿真接口电路、蜂鸣器驱动电路、M A X 232串口模块、按键模块以及各种显示模块组成。

[关键词] A T m e g a 128;单片机;仿真系统[中图分类号] T N 702 [文献标识码] A [文章编号] 1008-4657(2009)07-0025-070 引言A T m e g a 128为基于A V RR I S C 结构的8位低功耗C M O S 微处理器。

由于其先进的指令集以及单周期指令执行时间,A T m e g a 128的数据吞吐率高达1M I P S /M H z ,从而可以缓减系统在功耗和处理速度之间的矛盾。

A T m e g a 128具有如下特点:128K 字节的系统内可编程F l a s h (具有在写的过程中还可以读的能力,即R W W)、4K 字节的E E P R O M 、4K 字节的S R A M 、53个通用I /O 口线、32个通用工作寄存器、实时时钟R T C 、4个灵活的具有比较模式和P W M 功能的定时器/计数器(T /C )、两个U S A R T 、面向字节的两线接口T W I 、8通道10位A D C (具有可选的可编程增益)、具有片内振荡器的可编程看门狗定时器、S P I 串行端口、与I E E E 1149.1规范兼容的J T A G 测试接口(此接口同时还可以用于片上调试),以及六种可以通过软件选择的省电模式。

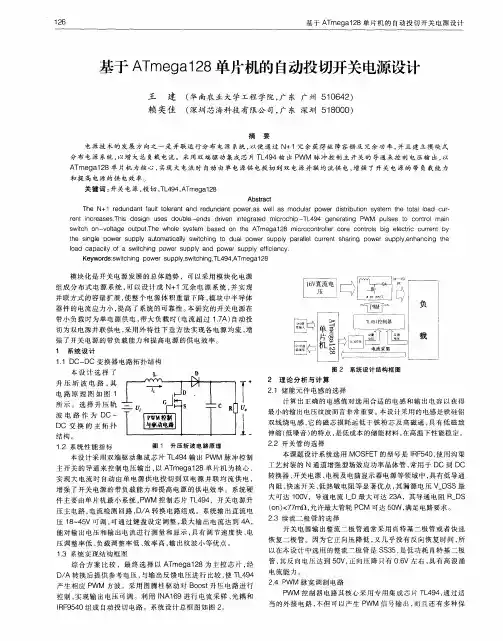

基于ATmega128单片机自动投切开关电源设计

模块化是开关电源发展的总体趋势,可以采用模块化电源组成分布式电源系统,可以设计成N+1冗余电源系统,并实现并联方式的容量扩展,使整个电源体积重量下降,模块中半导体器件的电流应力小,提高了系统的可靠性。

本研究的开关电源在带小负载时为单电源供电,带大负载时(电流超过1.7A)自动投切为双电源并联供电,采用外特性下垂方法实现各电源均流,增强了开关电源的带负载能力和提高电源的供电效率。

系统设计

1、DC-DC 变换器电路拓扑结构

本设计选择了升压斩波电路,其电路原理图如图1所示。

选择升压轨波电路作为DC -DC 变换的主拓扑结构。

图1 升压斩波电路原理

2、系统性能指标

本设计采用双端驱动集成芯片TL494 输出PWM 脉冲控制主开关的导通来控制电压输出,以ATmega128 单片机为核心,实现大电流时自动由单电源供电投切到双电源并联均流供电,增强了开关电源的带负载能力和提高电源的供电效率。

系统硬件主要由单片机最小系统,PWM 控制芯片TL494,开关电源升压主电路,电流检测回路,D/A 转换电路组成。

系统输出直流电压18~45V 可调,可通过键盘设定调整,最大输出电流达到4A,能对输出电压和输出电流进行测量和显示,具有调节速度快、电压调整率低、负载调整率低、效率高,输出纹波小等优点。

基于Atmega128单片机无人车控制系统电路设计该方案基于Atmega128单片机和无线通信技术设计,其创新点是采用了PC控制模式和单兵运行模式两种方式对无人车进行控制,极大地增强了无人车的功能性和环境适应能力。

该方案可广泛应用于短途货运客运、应急救援、恶劣环境下自动作业等领域。

智能无人车是一种履带式移动机器人,目前市场上的无人车大多采用单片机对其进行控制,其优点是体积小,成本低,结构简单,但仅仅依靠单片机远不能使无人车在复杂多变的工作环境中进行及时调整,并且极大地限制了其功能的扩展。

基于此不足,本设计主要利用PC机与无人车的无线通信,使无人车在PC机无线指令下完成前进、后退、转弯、打击、生命值显示、调速和自动行驶等功能,并通过车载摄像头实时获取无人车所处环境信息,实现了远程监控。

在执行任务时,如遭遇敌方车辆干扰通信,无人车在抵御干扰信号同时进行敌我识别,适时作出反击。

无人车系统工作原理为:打开教学无人车电源时,Atmega128单片机通过语音模块使扬声器发出启动提示。

当上位机无线控制台及PC端软件准备好后,PC端控制软件通过USB口向无线控制台单片机发出指令,使其配置无线模块相关寄存器,芯片进入指令发射模式;下位机由Atmega128单片机控制,在接收到上位机的指令后通过其集成的PWM外设模块产生2路PWM波和4 条转向控制线经电机驱动模块增大驱动能力后控制左右2个电机产生相应的动作。

例如,当PC端发出左转的指令时,下位机的无线模块接受成功后会自动返回接受成功应答信号。

接着Atmega128单片机通过PA口控制L298P,使左侧电机反向转动,右侧电机正向转动,从而实现左转的功能;当PC端发出打击指令时,Atmega128则通过PE5口使红外发射管发出相应码制的红外进攻信号;当PC端发出自动行驶指令时,Atmega128结合接收霍尔传感器采集回来。

科技广场2010.80引言自爱迪生点亮了我们的世界,照明就成了我们生活中不可或缺的一部分。

传统的照明系统配有传统镇流器的日光灯以100HZ的频率闪动,这种频闪会使眼睛疲劳。

智能照明系统的可调光电子镇流器是工作在40-70HZ的频率中,这样不仅克服了频闪,而且消除了起辉时的亮度不稳定,为人们提供了健康、舒适的环境。

最重要的是它能进行预设,它不仅可控制照明光源的发光时间、亮度,而且能在不同的应用场合做出相应的灯光场景。

智能照明系统是整个智能家居的基础部分,为了使用方便,我们采用人体红外感应作为感应开关,当有人走到感应区域的时候灯就会自动打开,较于传统开关灯更加的深入人心。

另外智能控制照明系统还能达到节约能源的目的,借助不同的智能元件对系统进行控制。

采用光敏检测对不同时间不同环境的光照度进行检测,检测后通过A/D转换控制LED灯的点亮频率和占空比来实现调光节能,这种自动调节亮度的方式,充分利用了室外的自然光,达到了环保节能效果。

1方案论证与比较该系统可自由控制灯的亮度、颜色和情景模式,另外还加入自动检测亮度调节和人体红外感应开关等功能。

首先确定了该系统分为控制模块(包括主机和分机控制)、触摸模块、电源模块、无线接收发送模块、人体红外感应模块和环境亮度检测模块构成。

系统框图如图一所示:基于Atmega128单片机的智能照明系统设计Atmega128-based Design of Intelligent Lighting System张仁朝谢谨Zhang Renchao Xie Jin(广州铁路职业技术学院,广东广州510430)(Guangzhou Institute of Railway Technology,Guangdong Guangzhou510430)摘要:本文主要采用AVR单片机Atmega128作为主机控制器,辅以太阳能充电电源模块、触摸控制模块、无线发送模块,分机采用单片机Atmega8L作为控制,以无线接收模块、人体红外感应检测模块、环境亮度检测模块、LED照明模块,总体构成了一个基于单片机控制的智能照明系统。

广州大学学生实验报告开课学院及实验室:计机楼503 2014年 05月 08日学院机械与电气工程学院年级、专业、班电信122 姓名王健学号1207400051实验课程名称信号与系统成绩实验项目名称实验2 1×8键盘和LED显示实验指导老师庞志一、实验项目利用连接在PE口的8个按键分别控制连接在PB口的8盏LED 的亮灭。

二、实验类型验证性。

三、计划学时2学时。

四、实验目的1、熟悉A VR单片机的I/O口配置方法。

2、掌握A VR单片机I/O口控制LED显示的方法。

3、掌握A VR单片机I/O口检测按键的方法。

五、实验设备与平台1、实验设备:计算机(PC),AVR Mega128学习板,AVR下载/仿真器。

2、软件平台:ICCA VR C语言程序开发软件,AVR STUDIO软件调试平台。

六、涉及的知识点A VR单片机I/O口的原理及其配置、LED亮灭控制、读按键。

七、实验相关知识1、电路原理图2.1 8个按键和8盏LED位置示意图图2.28个按键和8盏LED电路图2、与I/O口相关的寄存器8个按键8盏LED表2.1 端口A数据寄存器PORTAPORTA 位功能描述初始值PORTA[7:0] [7:0] 当引脚配置为输出时,若PORTAn为“1”,引脚输出高电平,否则输出低电平。

当引脚配置为输入时,若PORTAn 为“1”,上拉电阻将使能。

如果需要关闭这个上拉电阻,可以将PORTAn清零,或者将这个引脚配置为输出。

三态PORTA寄存器地址:0x3B表2.2 端口A数据方向寄存器DDRADDRA 位功能描述初始值DDRA7 [7] 1=输出0=输入0 DDRA6 [6] 1=输出0=输入0 DDRA5 [5] 1=输出0=输入0 DDRA4 [4] 1=输出0=输入0 DDRA3 [3] 1=输出0=输入0 DDRA2 [2] 1=输出0=输入0 DDRA1 [1] 1=输出0=输入0 DDRA0 [0] 1=输出0=输入0寄存器DDRA地址:0x3A表2.3 端口A输入引脚寄存器PINAPINA 位功能描述初始值PINA[7:0] [7:0] 通过读取PINAn可获得端口A各引脚电平:0=低电平1=高电平不定寄存器PINA地址:0x39表2.4 端口B数据寄存器PORTBPORTB 位功能描述初始值PORTB[7:0] [7:0] 当引脚配置为输出时,若PORTBn为“1”,引脚输出高电平,否则输出低电平。

ATmega128 单片机硬件电路设计

在本系统中,本小节主要讲ATmega128 单片机的内部资源、工作原理和硬件电路设计等。

2.5.1 ATmega128 芯片介绍ATmega128 为基于AVR RISC 结构的8 位低功耗CMOS 微处理器。

片内ISP Flash 可以通过SPI 接口、通用编程器,或引导程序多次编程。

引导程序可以使用任何接口来下载应用程序到应用Flash 存储器。

通过将8 位RISC CPU 与系统内可编程的Flash 集成在一个芯片内,ATmega128 为许多嵌入式控制应用提供了灵活而低成本的方案。

ATmega128 单片机的功能特点如下:(1)高性能、低功耗的AVR 8 位微处理器(2)先进的RISC 结构①133 条指令大多数可以在一个时钟周期内完成② 32x8 个通用工作寄存器+外设控制寄存器③全静态工作④工作于16 MHz 时性能高达16 MIPS ⑤只需两个时钟周期的硬件乘法器(3)非易失性的程序和数据存储器① 128K 字节的系统内可编程Flash ②寿命: 10,000 次写/ 擦除周期③具有独立锁定位、可选择的启动代码区(4)通过片内的启动程序实现系统内编程① 4K 字节的EEPROM ② 4K 字节的内部SRAM ③多达64K 字节的优化的外部存储器空间④可以对锁定位进行编程以实现软件加密⑤可以通

过SPI 实现系统内编程(5)JTAG 接口(与IEEE 1149.1 标准兼容)①遵循JTAG 标准的边界扫描功能②支持扩

展的片内调试③通过JTAG 接口实现对Flash,EEPROM,熔丝位和锁定位的编程(6)外设特点①两个具有独立的预分频器和比较器功能的8 位定时器/ 计数器②两个具

有预分频器、比较功能和捕捉功能的16 位定时器/ 计数器③具有独立预分频器的实时时钟计数器④两路8 位PWM ⑤ 6 路分辨率可编程(2 到16 位)的PWM ⑥输出比较调制器⑦ 8 路10 位ADC ⑧面向字节的两线接口⑨两个可编程的串行USART ⑩可工作于主机/ 从机模式的SPI 串行接口(7)特殊的处理器特点①上电复位以及可编程的掉电检测②片内经过标定的RC 振荡器③片内/ 片外中断源④ 6 种睡眠模式: 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及扩展的Standby 模式⑤可以通过软件进行选择的时钟频率⑥通过熔丝

位可以选择ATmega103 兼容模式⑦全局上拉禁止功能ATmega128 芯片有64 个引脚,其中60 个引脚具有I/O 口功能,资源比较丰富,下面对ATmega128 的各个引脚做简单介绍:VCC:数字电路的电源。

GND:接地。

端口(PA7..PA0)、(PB7..PB0)、(PC7..PC0)、(PD7..PD0)、(PE7..PE0)、(PF7..PF0)、(PG4..PA0):为8 位双向I/O 口,并具有可编程的内部上拉电阻。

其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。

作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将

输出电流。

复位发生时端口为三态。

这些端口在其他情况下有特殊功能,在此不一一列举。

RESET:复位输入引脚。

超过最小门限时间的低电平将引起系统复位,低于此时间的脉冲不能保证可靠复位。

XTAL1:反向振荡器放大器及片内时钟操作电路的输入。

XTAL2:反向振荡器放大器的输出。

AVCC:AVCC 为端口F 以及ADC 转换器的电源,需要与VCC 相连接,即使没有使用ADC也应该如此。

使用ADC 时应该通过一个低通滤波器与VCC 连接。

AREF:AREF 为ADC 的模拟基准输入引脚。

PEN:PEN 是SPI 串行下载的使能引脚。

在上电复位时保持PEN 为低电平将使器件进入SPI 串行下载模式。

在正常工作过程中PEN 引脚没有其他功能。

2.5.2 ATmega128 内部结构ATmega128 内部主要包括CPU 内核、存储器、系统时钟、系统控制和复位、I/O 端口和定时器/计数器等。

(1)CPU 内核ATmega128 单片机采用了Harvard 结构,具有独立的数据和程序总线,程序存储器的指令通过一级流水线运行。

(2)ATmega128 存储器AVR 结构具有三个线性存储空间:程序存储器、数据存储器和EEPROM存储器。

系统内有可编程的Flash 程序存储器,ATmega128 具有128K 字节的在线编程Flash。

因为所有的AVR 指令为16 位或32 位,故FLASH 组织成64K x 16 的形式。

ATmega128 还可以访问直到64K 的外部数据SRAM,其起始紧跟在内部SRAM之后。

ATmega128

包含4K 字节的EEPROM。

它是作为一个独立的数据空间而存在的,可以按字节读写。

EEPROM 的寿命至少为100,000 次(擦除)。

ATmega128 的所有I/O 和外设都被放置在I/O 空间。

在32 个通用工作寄存器和I/O 之间传输数据。

(3)系统时钟CPU 时钟:CPU 时钟与操作AVR 内核的子系统相连,如通用工作寄存器文件、状态寄存器以及保存堆栈指针的数据存储器。

终止CPU 时钟将使内核停止工作和计算。

I/O时钟:I/O时钟用于主要的I/O 模块,如定时器/ 计数器、SPI 和USART。

I/O 时钟还用于外部中断模块。

但是有些外部中断由异步逻辑检测,因此即使I/O 时钟停止了这些中断仍然可以得到监控。

此外,TWI 模块的地址识别功能在没有I/O 时钟的情况下也是异步实现的,使得这个功能在任何睡眠模式下都可以正常工作。

Flash 时钟:Flash 时钟控制Flash 接口的操作。

此时钟通常与CPU 时钟是同步的。

异步定时器时钟:异步定时器时钟允许异步定时器/ 计数器直接由外部32 kHz 时钟晶体驱动,使得此定时器/ 计数器即使在睡眠模式下仍然可以为系统提供一个实时时钟。

ADC 时钟:ADC 具有专门的时钟。

这样可以在ADC 工作的时候停止CPU 和I/O 时钟以降低数字电路产生的噪声,从而提高ADC 转换精度。

(4)系统控制和复位复位时所有的I/O 寄存器都被设置为初始值,程序从复位向量处开始执行。

复位源生效时I/O 端口立即复位

为初始值,不需要任何时钟的辅助。

ATmega128 有5 个

复位源:上电复位:当电源电压低于上电复位门限(V POT )时MCU 复位。

外部复位:当复位引脚上的低电平持续时

间大于最小脉冲宽度时MCU 复位。

看门狗复位:当看门狗使能并且看门狗定时器超时时复位发生。

掉电检测复位:当掉电检测复位功能使能,且电源电压低于掉电检测复位门限(V BOT )时MCU 即复位。

JTAG AVR 复位:当复位寄存器为1 时MCU 即复位。

(4)I/O 端口所有AVR I/O 端口都具有真正的读-修改-写功能。

有以下3 个8 位寄存器用于控制I/O 端口的设置:端口方向控制寄存器DDRx,数据寄存器PORTx,输入引脚寄存器PINx (5)定时器/计

数器(T/C)ATmega128 内有四个定时器/计数器,其中包括8 位的定时器/计数器0(T/C0)和定时器/计数器2

(T/C2)、16 位的定时器/计数器1(T/C1)和定时器/计数器3 (T/C3)。

除以上主要资源外,ATmega128 还输出

比较调制器、串行通信接口(SPI)、两线串行接口(TWI)、USART、模拟比较器和数模转换器(A/D)等。

2.5.3 ATmega128 系统电路设计在本系统中,ATmega128 控制板采用最小系统模式,包括ISP、JTAG 仿真接口电路、USB 供电及通信电和引脚扩展电路。

晶振采用16MHz 和8MHz

两种模式,可以根据跳线的接法设置不同的晶振源,在本

系统设计中晶振采用8MHz。

系统采用供电和下载于一体的

ISP(在线系统编程)接口,无需将存储芯片从设备上取出就能对其进行编程,其优点是:即使器件焊接在电路板上,仍可对其(重新)进行编程。

系统也设置有JTAG 仿真接口,它的编程方式是在线编程,利用边界扫描技术,设置

快捷。

在本系统中由于需要下载到存储器中,故采用ISP 下载模式,其接口电路如图2.15 所示:图2.15ISP 和JTAG 接口电路系统复位电路和晶振电路如下图2.16和2.17所示,晶振采用8MHz 外接33pF 电容构成并联谐振电路,复位电路与89C52 单片机不同,ATmega128 采用的是低电平复位,在VCC 和GND 之间接一个开关二极管4148,起着保

护电路的作用,当按键按下时,ATmega128 单片机会进入复位,默认状态下复位端为高电平。

图2.16 ATmega128 复位电路图2.17ATmega128 晶振电路K 1 K E Y G N D C 1 1 μ F R 1 1 0 k Ω D 1 4 1 4 8 V C C REST Y 1 8MHz C 3 3 3 μ F C 2 3 3 μ F G N D X T A L 1 X T A L 2。