EDA考试复习重点难点总结

- 格式:ppt

- 大小:247.50 KB

- 文档页数:17

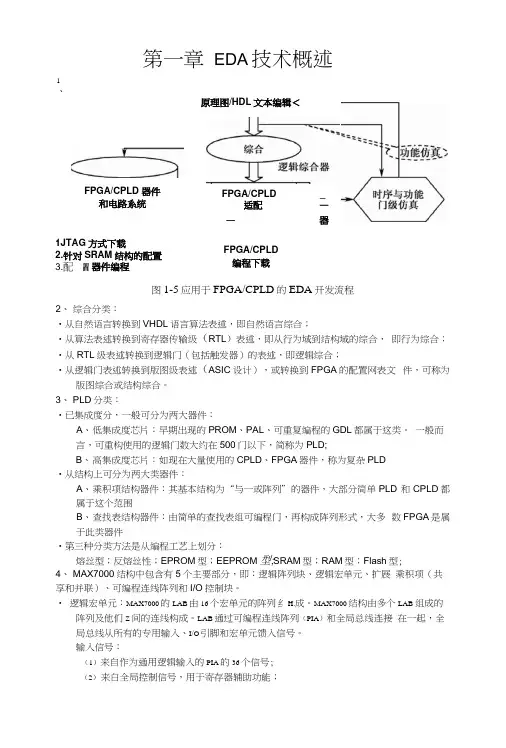

第一章EDA技术概述图1-5应用于FPGA/CPLD的EDA开发流程2、综合分类:•从自然语言转换到VHDL语言算法表述,即自然语言综合;•从算法表述转换到寄存器传输级(RTL)表述,即从行为域到结构域的综合,即行为综合;•从RTL级表述转换到逻辑门(包括触发器)的表述,即逻辑综合;•从逻辑门表述转换到版图级表述(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

3、PLD分类:•已集成度分,一般可分为两大器件:A、低集成度芯片:早期出现的PROM、PAL、可重复编程的GDL都属于这类。

一般而言,可重构使用的逻辑门数大约在500门以下,简称为PLD;B、高集成度芯片:如现在大量使用的CPLD、FPGA器件,称为复杂PLD•从结构上可分为两大类器件:A、乘积项结构器件:其基本结构为“与一或阵列”的器件,大部分简单PLD 和CPLD都属于这个范围B、查找表结构器件:由简单的查找表组可编程门,再构成阵列形式,大多数FPGA是属于此类器件•第三种分类方法是从编程工艺上划分:熔丝型;反熔丝性;EPROM型;EEPROM型;SRAM型;RAM型;Flash型;4、MAX7000结构中包含有5个主要部分,即:逻辑阵列块、逻辑宏单元、扩展乘积项(共享和并联)、可编程连线阵列和I/O控制块。

• 逻辑宏单元:MAX7000的LAB由16个宏单元的阵列纟H.成。

MAX7000结构由多个LAB 组成的阵列及他们Z间的连线构成。

LAB通过可编程连线阵列(PIA)和全局总线连接在一起,全局总线从所有的专用输入、I/O引脚和宏单元馈入信号。

输入信号:(1)来自作为通用逻辑输入的PIA的36个信号;(2)来白全局控制信号,用于寄存器辅助功能;1、FPGA/CPLD 器件和电路系统原理图/HDL文本编辑<FPGA/CPLD _适配——器1JTAG方式下载2.针对SRAM结构的配置3.配器件编程FPGA/CPLD编程下载(3)从I/O引脚到寄存器的直接输入通道。

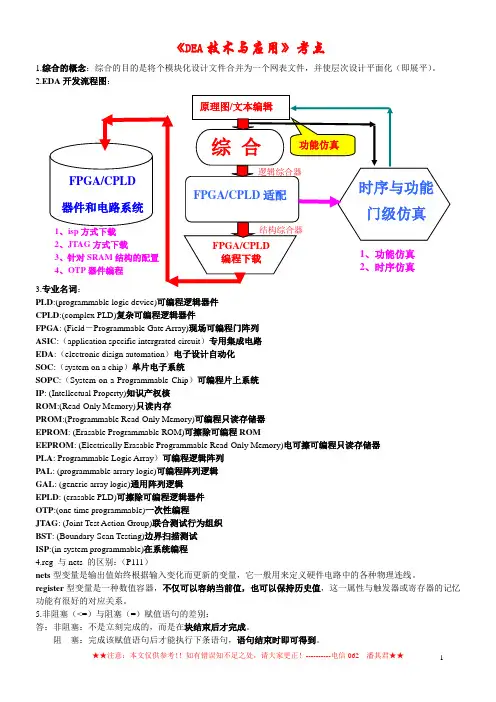

《DEA 技术与应用》考点1.综合的概念:综合的目的是将个模块化设计文件合并为一个网表文件,并使层次设计平面化(即展平)。

2.EDA 开发流程图:3.专业名词:PLD :(programmable logic device)可编程逻辑器件CPLD :(complex PLD)复杂可编程逻辑器件FPGA : (Field -Programmable Gate Array)现场可编程门阵列ASIC :(application specific intergrated circuit )专用集成电路EDA :(electronic disign automation )电子设计自动化SOC :(system on a chip )单片电子系统SOPC :(System-on-a-Programmable-Chip )可编程片上系统IP : (Intellectual Property)知识产权核ROM :(Read-Only Memory)只读内存PROM :(Programmable Read-Only Memory)可编程只读存储器EPROM : (Erasable Programmable ROM)可擦除可编程ROMEEPROM : (Electrically Erasable Programmable Read-Only Memory)电可擦可编程只读存储器PLA : Programmable Logic Array )可编程逻辑阵列PAL : (programmable arrary logic)可编程阵列逻辑GAL : (generic array logic)通用阵列逻辑EPLD : (erasable PLD)可擦除可编程逻辑器件OTP :(one time programmable)一次性编程JTAG : (Joint Test Action Group)联合测试行为组织BST : (Boundary-Scan Testing)边界扫描测试ISP :(in system programmable)在系统编程4.reg 与nets 的区别:(P111)nets 型变量是输出值始终根据输入变化而更新的变量,它一般用来定义硬件电路中的各种物理连线。

EDA考试必考知识点好嘞,以下是为您创作的关于“EDA 考试必考知识点”的文案:咱先来说说 EDA 这玩意儿,这可在电子信息领域里有着相当重要的地位!对于准备 EDA 考试的小伙伴们,下面这些必考知识点可得好好掌握啦。

先说 EDA 工具的使用,就像咱平时用的手机,得知道每个功能咋用才能玩得转。

比如说像 Cadence、Synopsys 这些主流的 EDA 工具,得熟悉它们的操作界面,知道怎么去画原理图、做版图设计。

我记得有一次,我带着学生做一个简单的电路设计项目,有个同学对工具的使用不太熟练,画个简单的电阻都找半天工具按钮,那着急的样子真让人哭笑不得。

这就告诉咱,熟练掌握工具的使用,那是基础中的基础。

再说说硬件描述语言,Verilog HDL 和 VHDL 那可是重点中的重点。

就好比我们说话得有语法,写代码也得遵循一定的规则。

得搞清楚怎么用这些语言去描述逻辑电路,怎么写状态机,怎么进行时序控制。

记得我之前参加一个竞赛,团队里有个小伙伴因为对硬件描述语言的一些细节没掌握好,导致整个模块的功能出现了偏差,最后我们不得不加班加点去修改,那叫一个累啊!还有数字电路的设计原理,像组合逻辑电路、时序逻辑电路这些,那是必须要搞明白的。

比如加法器、计数器、寄存器,得清楚它们的工作原理和实现方法。

我曾经在一次实验课上,看到一个学生设计的计数器总是出错,后来一检查,原来是对时钟信号的理解不到位,这可让他吃了大亏。

另外,EDA 中的综合优化技术也别忽略。

怎么把写好的代码优化得更高效,占用资源更少,这可是个技术活。

就像咱们收拾房间,得把东西整理得井井有条,既节省空间又方便取用。

还有仿真验证,这就像是考试前的模拟测试,得保证设计的电路能正常工作。

学会怎么设置仿真条件,怎么分析仿真结果,找出问题所在。

我之前指导过一个毕业设计,学生做完设计觉得没问题了,一仿真,结果出来一堆错误,这时候才发现自己忽略了很多细节。

总之,要想在 EDA 考试中取得好成绩,上面这些知识点可得牢牢掌握。

“比较完整了”EDA复习简答1. EDA的设计流程方案设计,系统规划,代码输入,编译器,功能仿真,综合器,时序仿真,适配器,编程文件,硬件测试2. 竞争与冒险产生、判断及如何处理产生:由于延迟时间的存在,当一个输入信号经过多条路径传送后又重新会合到某个门上,由于不同路径上门的级数不同,或者门电路延迟时间的差异,导致到达会合点的时间有先有后,从而产生瞬间的错误输出。

判断:1)代数法:逻辑函数表达式中,若某个变量同时以原变量和反变量两种形式出现,就具备了竞争条件。

2)卡诺图法:只要在卡诺图中存在两个相切但不相交的圈(“0”冒险是1构成的圈,“1”冒险是0构成的圈),就会产生冒险。

处理方法:1)修改设计法: a、代数法,在产生冒险现象的逻辑表达式上,加上冗余项或乘上冗余因子;b、卡诺图法,将卡诺图中相切的圈用一个多余的圈连接起来。

2)选通法: 在电路中加入选通信号,在输出信号稳定后,选通允许输出,从而产生正确输出;3)滤出法: 由于冒险脉冲是一个非常窄的脉冲,一二可以在输出端接一个几百微法的电容,将其滤出掉。

3、TTL与CMOS兼容问题由于电路相互之间的电源电压和输入、输出电平及负载能力等参数不同,因此他们之间的连接必须通过电平转换或电流转换电路,使前级器件的输出的逻辑电平满足后级器件对输入电平的要求,并不得对器件造成损坏。

逻辑器件的接口电路主要应注意电平匹配和输出能力两个问题,并与器件的电源电压结合起来考虑。

1)CMOS到TTL的连接需要进行电流匹配。

2)TTL到CMOS的连接需要进行电压匹配。

4、EDA的烧写方式1)按计算机接口:串口下载,并口下载,USB口下载等方式2)按器件:CPLD编程,FPGA下载,存储器编程EPC1、EPC2等。

5、同步电路与异步电路的判断1)同步电路是说电路里的时钟相互之间是同步的。

2)异步电路主要是组合逻辑电路,没有统一的时钟。

所以只要判断时钟是否同步,就可分辨同步或者异步。

EDA技术复习资料(完全版)EDA技术复习资料⼀、填空1、EDA设计流程包括设计准备、设计输⼊、设计处理、和器件编程序四个步骤。

2、EDA的设计验证包括功能仿真、时序仿真和器件测试三个过程。

3、EDA的设计输⼊主要包括⽂本输⼊⽅式、图形输⼊⽅式、和波形输⼊⽅式。

4、⽂本输⼊是指采⽤硬件描述语⾔进⾏电路设计的⽅式。

5、功能仿真实在设计输⼊完成以后,选择具体器件进⾏编译之前进⾏的逻辑功能验证,因此⼜称为前仿真。

6、时序仿真实在选择了具体器件并完成布局、布线之后进⾏的时序关系仿真,因此⼜被称为后仿真或延时仿真。

7、当前最流⾏的并成为IEEE标准的硬件描述语⾔包括VHDL、和VERILOG HDL。

8、EDA⼯具⼤致分为设计输⼊编辑器、仿真器、HDL综合器、适配器(或布局布线器)、以及下载器等五个模块。

9、IEEE于1987年将VHDL采纳为IEEE#1076标准。

10、⽤VHDL语⾔书写的源⽂件。

即是程序⼜是⽂档,即是⼯程技术⼈员之间交换信息的⽂件,⼜可作为合同签约者之间的⽂件。

11、⽤VHDL设计的电路,既可以被⾼层次的系统调⽤,成为系统的⼀部分,也可以作为⼀个电路的功能快独⽴存在和独⽴运⾏。

12、VDHL设计实体的基本结构由库、程序包、实体、结构体和配臵等部分构成。

13、实体和结构体是设计实体的基本组成部分,它们可以构成最基本的VHDL程序。

14、根据VHDL语法规则,在程序中使⽤的⽂字、数据对象、数据类型都需要预先定义。

15、VHDL的实体由实体声明部分和结构体组成。

16、VHDL的实体声明部分制订了设计单元的输⼊输出端⼝或引脚,它是设计实体对外的⼀个通信界⾯,是外界可以看到的部分。

17、VDHL的结构体⽤来描述设计实体的逻辑结构和逻辑功能,它由VHDL语句构成,是外界看不到的部分。

18、在VHDL的端⼝声明语句中,端⼝⽅向包括IN、OUT、INOUT和BUFFER。

19、VHDL的数据型⽂字包括整数⽂字、实数⽂字、以数制基数表⽰的⽂字和物理量⽂字。

EDA基础知识复习要点EDA(探索性数据分析)是指对数据集进行初步的探索,以了解数据的特征、相互关系和隐藏的模式。

它是数据分析的重要环节,可以帮助我们发现数据中的特殊特征、异常值和缺失值,为后续的建模和决策提供基础。

下面是EDA基础知识的复习要点。

1.数据集的基本情况-数据集的大小和维度:了解数据集包含的样本数量和特征数量。

-数据类型和缺失值:检查每个特征的数据类型并确定是否存在缺失值。

-数据的摘要统计信息:计算每个特征的基本统计指标,如均值、中位数、标准差等。

-数据可视化:使用直方图、箱线图、散点图等可视化工具来展示数据的分布和异常值。

2.数据的清洗和预处理-处理缺失值:根据缺失值的情况选择适当的方法填充或删除缺失值。

-处理重复值:检查是否存在重复的样本或特征,并根据需要删除或合并重复值。

-异常值处理:通过设定阈值或使用统计方法来检测和处理异常值。

-标准化和归一化:对于数据集中的数值型特征,可以进行标准化或归一化处理,使其具有相同的尺度。

3.特征工程-特征选择:根据特征的重要性和相关性选择最相关的特征,减少特征的维度。

-特征构建:使用原始特征衍生出新的特征,例如添加多项式特征、交互特征等。

4.数据探索-变量间的关系:分析变量之间的相关性和因果关系,帮助了解特征之间的影响。

-群组分析:将数据集中的样本划分为不同的组群,发现数据的内在结构和模式。

-关键性因素:识别影响特定结果的重要因素,找到数据集中的关键趋势和影响因素。

5.可视化分析-直方图:显示定量变量的分布情况,帮助了解数据的偏态和尾部情况。

-箱线图:显示定量变量的中位数、上下四分位数和异常值,有助于观察数据的离散情况。

-散点图:显示两个变量之间的关系,帮助检测变量之间的线性关系或异常值。

-折线图:显示变量随时间变化的趋势,用于分析时间序列数据。

6.结果解释和报告-对EDA结果进行总结和解释,包括数据集的特点、重要特征、异常值等。

-以清晰和可视化的方式呈现结果,如使用图表、表格等形式。

EDA考试必考知识点咱先来说说 EDA 这玩意儿哈,这在考试里可重要得很呢!就像你去参加一场刺激的冒险,EDA 知识就是你手中的关键地图。

首先,EDA 的基本概念那是必考的。

啥是 EDA 呢?简单来说,就是电子设计自动化,它能帮工程师们更高效地设计电路和系统。

比如说,有一次我去一个电子厂参观,看到工程师们坐在电脑前,用 EDA软件就像变魔术一样,把复杂的电路设计得井井有条。

那场面,真让人惊叹!然后就是 EDA 工具的使用。

像那些常见的 EDA 工具,比如Cadence、Altium Designer 等等,你得熟悉它们的操作界面、功能模块。

我记得有个学生,在考试前拼命练习工具的使用,结果考试的时候碰到一个相似的题目,轻松就拿下了高分。

再说说硬件描述语言,像 VHDL 和 Verilog 这俩“大佬”。

你得搞清楚它们的语法规则、数据类型、控制结构。

想象一下,你要用这些语言来给电路“说话”,告诉它该怎么做。

这就好比你指挥一个机器人,得把指令说得明明白白。

还有数字电路设计,这也是重点中的重点。

什么组合逻辑电路、时序逻辑电路,都得弄得清清楚楚。

我曾经遇到过一个实际的案例,一个电路出现故障,就是因为时序逻辑没设计好,导致整个系统都乱套了。

另外,系统级设计也是必考的一块儿。

从顶层到底层,怎么把一个大的系统分解成一个个小模块,再把它们整合起来,这可需要不少功夫。

在 EDA 考试中,仿真和验证也是不能忽视的。

你设计好的电路到底行不行,得通过仿真来验证一下。

就像你做好了一道菜,得尝尝味道对不对。

最后,可别忘了综合和布局布线。

这就像是给你的电路找个合适的“家”,让它能舒舒服服地工作。

总之,EDA 考试的必考知识点就像一个个宝藏,你得用心去挖掘、去掌握。

只要你认真学习,多做练习,相信在考试中一定能取得好成绩,顺利开启你的电子设计之旅!加油吧!。

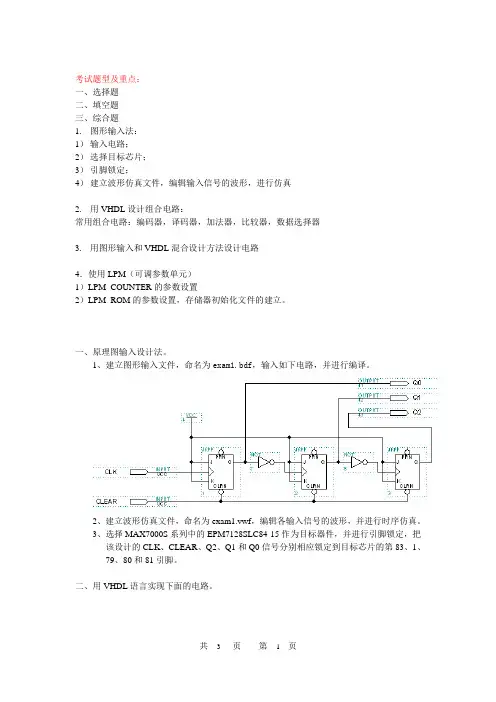

考试题型及重点:一、选择题二、填空题三、综合题1.图形输入法:1)输入电路;2)选择目标芯片;3)引脚锁定;4)建立波形仿真文件,编辑输入信号的波形,进行仿真2.用VHDL设计组合电路:常用组合电路:编码器,译码器,加法器,比较器,数据选择器3.用图形输入和VHDL混合设计方法设计电路4.使用LPM(可调参数单元)1)LPM_COUNTER的参数设置2)LPM_ROM的参数设置,存储器初始化文件的建立。

一、原理图输入设计法。

1、建立图形输入文件,命名为exam1.bdf,输入如下电路,并进行编译。

2、建立波形仿真文件,命名为exam1.vwf,编辑各输入信号的波形,并进行时序仿真。

3、选择MAX7000S系列中的EPM7128SLC84-15作为目标器件,并进行引脚锁定,把该设计的CLK、CLEAR、Q2、Q1和Q0信号分别相应锁定到目标芯片的第83、1、79、80和81引脚。

二、用VHDL语言实现下面的电路。

三、利用VHDL语言设计法,建立文本文件,命名为exam3.vhd,设计一个3线-8线译码器,要求有A2~A0代码输入端,Y7~Y0为输出端,并进行编译。

四、VHDL与原理图混合设计。

1、编译源文件adder2.vhd,并为其创建元件符号。

adder2为两位的加法器,其中a,b为两个加数输入端,cin为进位输入端,s为和输出,cout为进位输出。

LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.std_logic_unsigned.all;Entity adder2 isport (cin : in std_logic;a,b : in std_logic_vector(1 downto 0);s: out std_logic_vector(1 downto 0);cout : out std_logic);end adder2;architecture adder2_body of adder2 ISsignal sint : std_logic_vector(2 downto 0);signal aa,bb: std_logic_vector(2 downto 0);beginaa<='0'&a;bb<='0'&b;sint<=aa+bb+cin;s<=sint(1 downto 0);cout<=sint(2);end adder2_body;2、建立图形输入文件,命名为exam4.bdf,利用1中创建的元件符号设计一个4位的加法器。

1、三大技术的重点转移,即:分立元件像集成电路转移、模拟技术像数字技术转移、固定器件向可编程器件转移。

原因:简化设计、减小体积、提高系统的可靠性、提高可测性、缩短设计周期。

2、自顶向下的优势:设计的主要方针和调试过程在高层次上完成的,这有利于早起发现结构设计上的错误,避免设计工作的浪费,同时也减少了功能仿真的工作量,提高了设计的一次成功率。

现代EDA技术采用“自顶向下”的高层次的电子设计方法,代表了当今电子技术的最新发展方向。

3、电子电路设计与仿真工具包括SPICE/PSPICE、MultiSIM、Matlab 等。

4、PCB(Printed—Circuit Board)设计软件种类很多,如:Altium Disigner、orCAD、PowerPCB等,目前我国多采用Altium Disigner。

5、PLD(可编程逻辑器件)是一种可以完全代替74系列及GAL、PLA的新型电路,只要有数字电路基础,会使用计算,就可以进行PLD的开发。

PLD的在线编程能力和强大的开发软件,使工程师可以再几天、甚至几分钟内就可以完成一额昂几周才能完成的工作,并可将数百万门的复杂设计集成在一颗芯片内。

PLD技术在发达国家已成为电子工程师必备的技术。

6、EDA是电子设计自动化(Electronic Design Automation.)英文的缩写简称。

7、EDA技术的含义:以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

8、广义的EDA技术包括:电子电路设计、PCB设计和IC设计。

9、狭义的EDA技术特指以可编程浅见(包含可编程逻辑器件和模拟器件)为物理载体,以图形或硬件描述为主要功能的表达方式,利用EDA工具自动完成现代电子系统构架夫人设计技术。

1、数字系统的设计可以再一下几个层次上进行:(1)传统的数字系统逻辑设计方法,(2)专用集成电路的设计方法,(3)自顶向下的现代数字系统设计方法。

《EDA技术及应用》考试复习要点一.名词解释(5个小题,15分):包括1.1,1.3,1.6,3.2~3.8,4.2,5.1~5.4等章节的基本概念,基础知识.二.填空题(10空,共20分):包括1.1,1.3,1.6,3.2~3.8,4.2,5.1~5.4等章节的基本概念,基础知识.三.选择题(5个小题,共15分):包括1.1,1.3,1.6,3.2~3.8,4.2,5.1~5.4等章节的基本概念,基础知识.四.程序阅读_功能修改题(1个小题,10分)五.VHDL程序设计题(2个小题,共40分)包括3.9,3.10,6.3,6,5,6.6等章节,主要考试的程序设计类型有:触发器和锁存器;计数器(至少掌握3种方法,参见教材P283,P187-189);分频器(至少掌握2种方法,参见教材P287,327);数据动态扫描显示电路(包括计数,选择,译码等基本电路,主要是实验里每次都要用);数据寄存器(数码寄存器和移位寄存器)(参见教材185,186);序列信号发生器和检测器(参见教材P189,P191);读写存储器SRAM(参见教材P193-195)。

欧伟明2011年4月28日附:数据动态扫描显示电路的一个VHDL参考程序。

【例1】用VHDL设计一个8bits并行半加器,要求将被加数、加数和运算结果用动态扫描的方式,在7个共阴LED数码管上同时显示出来,其对应的数据动态扫描显示电路外围器件接线如图1所示,并使用MAX+plus II进行仿真。

图1 数据动态扫描显示电路外围器件接线图--DISPLAY.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;--实体说明ENTITY DISPLAY ISPORT(CLK:IN STD_LOGIC; --动态扫描显示时钟,24HZ以上AIN: IN STD_LOGIC_VECTOR(7 DOWNTO 0); --8位被加数BIN: IN STD_LOGIC_VECTOR(7 DOWNTO 0); --8位加数SUM0,SUM1,SUM2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--仿真观测输出COM:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管COM端的选择输出端SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --数码管8段显示驱动输出端END ENTITY DISPLAY;ARCHITECTURE ART OF DISPLAY ISSIGNAL AA, BB,SINT: STD_LOGIC_VECTOR(8 DOWNTO 0);SIGNAL CNT:STD_LOGIC_VECTOR(2 DOWNTO 0);SIGNAL BCD:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGIN--进行运算前的准备及加法运算AA<='0'&AIN;BB<='0'&BIN;SINT<=AA+BB;SUM0<=SINT(3 DOWNTO 0); --运算结果的仿真观测输出SUM1<=SINT(7 DOWNTO 4); --运算结果的仿真观测输出SUM2<="000"&SINT(8); --运算结果的仿真观测输出--产生动态扫描显示的控制信号PROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1' THENIF CNT="111" THENCNT<="000";ELSECNT<=CNT+'1';END IF ;END IF;END PROCESS;PROCESS(CNT)BEGIN--显示数据的选择,对应显示数码管公共端的选通,低电平有效 CASE CNT ISWHEN "000" =>BCD<=AIN(3 DOWNTO 0);COM<="1111110"; WHEN "001" =>BCD<=AIN(7 DOWNTO 4);COM<="1111101"; WHEN "010" =>BCD<=BIN(3 DOWNTO 0);COM<="1111011"; WHEN "011" =>BCD<=BIN(7 DOWNTO 4);COM<="1110111"; WHEN "100" =>BCD<=SINT(3 DOWNTO 0);COM<="1101111"; WHEN "101" =>BCD<=SINT(7 DOWNTO 4);COM<="1011111"; WHEN "110" =>BCD<="000"&SINT(8);COM<="0111111";WHEN OTHERS=>BCD<="0000";COM<="1111111";END CASE;--将BCD码转换成数码管的8段驱动信息,高电平有效CASE BCD ISWHEN "0000" => SEG<="00111111";WHEN "0001" => SEG<="00000110";WHEN "0010" => SEG<="01011011";WHEN "0011" => SEG<="01001111";WHEN "0100" => SEG<="01100110";WHEN "0101" => SEG<="01101101";WHEN "0110" => SEG<="01111101";WHEN "0111" => SEG<="00000111";WHEN "1000" => SEG<="01111111";WHEN "1001" => SEG<="01101111";WHEN "1010" => SEG<="01110111";WHEN "1011" => SEG<="01111100";WHEN "1100" => SEG<="00111001";WHEN "1101" => SEG<="01011110";WHEN "1110" => SEG<="01111001";WHEN "1111" => SEG<="01110001";WHEN OTHERS => SEG<="00000000";END CASE ;END PROCESS;END ARCHITECTURE ART;图1.33 数据动态扫描显示程序仿真图。

EDA复习的知识要点及答案EDA知识要点:1、EDA技术的含义。

EDA(Electronic Design Automation)即电子设计自动化:是以计算机为工作平台以EDA软件工具为开发环境以软件描述语言为设计语言以ASIC为实现载体的电子产品自动化设计过程。

2、简述EDA技术经历了那几个发展阶段。

EDA技术:计算机辅助设计CAD、计算机辅助工程CAE、电子系统设计自动化ESDA.3、可编程器件(PLD)分为哪两类4、可编程器件分为哪些类?可编程逻辑器件分为:简单可编程逻辑器件SPLD、复杂可编程逻辑器件CPLD、现场可编程门阵列FPGA、在系统可编程ISP逻辑器件。

5、简述EDA技术的CPLD/FPGA的设计流程。

6、目前国际上较大的PLD器件制造公司有那几家公司。

三大公司:Altera、Xilinx西林、Lattice来迪恩。

7、目前较流行的集成EDA开发环境(软件)有那些?Altera公司的QuartusⅡ和maxplusⅡ、Xilinx公司的ISE、Lattice公司的ispLEVER Adbanced System。

8、目前流行的HDL语言有那些?ABEL-HDL、AHDL、VHDL9、硬件描述语言(HDL)的种类很多?10、什么是ASIC。

ASIC(Application Specific Intergrated Circuits)即专用集成电路,按照设计方法不同可分为:全定制ASIC、半定制ASIC、可编程ASIC11、VHDL作为工业标准,是由那个机构制定并公布的。

IEEE12、VHDL是由什么机构制定并公布的。

IEEE1076、IEEE1076-199313、VHDL的两大类基本描述语句是什么。

VHDL的基本描述语句有并行语句(Concurrent Statements)和顺序语句(Sequential Statements)两大类14、从执行方式看VHDL的基本描述语句包括哪两大基本描述语句?15、MAX+PLUSⅡ平台上,原理图、仿真波形文件、VHDL文件的扩展名是什么?原理图.gdf、仿真.scf、vhdl.vhd。

数字系统EDA技术复习第一章EDA技术基础一、EDA技术的定义:以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算桩、大规模可编程器件的开发软件及实验开发系统为设计工具,自动完成用软件方式描述的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割.逻辑综合及优化、布局布线、逻辑仿真,直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门多学科融合的新技术。

第一章EDA技术基础第一章EDA技术基础三、传统方法与EDA方法比较:传统方法1.从下至上2•通用的逻辑元、器件3.系统硬件设计的后期进行仿真和调试4.主要设计文件是电原理图EDA方法1.自上至下2.可编程逻辑器件二、EDA的工程设计流程第一章EDA技术基础3•系统设计的早期进行仿真和修改4•多种设计文件,发展趋势以HDL描述文件为主第一章EDA技术基础1、设计输入子模块用图形编辑器、文本编辑器作设计描述,完成语义正确性、语法规则的检查.2、设计数据库子模块系统的库单元、用户的设计描述、中间设计结果•3、分析验证子模块各个层次的模拟验证.设计规则的检查.故障诊断。

第一章EDA技术基础4、综合仿真子模块综合模块:将电路的高级语言描述转换成低级的,可与FPGA/CPLD或构成ASIC的门阵列基本结构相映射的网表文件.仿真模块实现对所描述电路的功能.逻辑和时序等进行验证.5、布局布线子模块完成由逻辑设计到物理实现的映射。

CPLD和FPGAFPGA (Field Programmable Gates Array )CPLD ( Complex Programmable Logic Device )FPGA:内部互连结构由多种长度不同的连线资源组成,每次布线的延迟可不同,属统计型结构。

逻辑单元主体为由靜态存储器(SRAM)构成的函数发生器,即查找表。

通过查找表可实现逻辑函数功能。

1.RTL/行为级建模2.基本概念如常用基础定义、时序及延迟部分、总线和流水新章节a)时序和延迟集总延迟(基于每个模块,将全部延时集中到最后输出门)b)分布延迟(延迟值赋给电路中独立的元件)用assign分布延时有两个缺点:1.在结构描述中随规模的增大而变得异常复杂。

2.仍然不能描述基本单元(primitive)中不同引脚上的不同延时。

c)路径延迟(针对每条输入/输出路径分别指定延迟)在专用的specify块描述模块从输入端到输出端的路径延时。

精确性:所有路径延时都能精确说明。

模块性:时序与功能分开说明Specify块包含下列操作语句:①给穿过模块的所有路径指定引脚到引脚的时序延迟②在电路中设置时序检查③定义specparam常量3.状态机a)为什么要设计有限状态机如果我们能设计这样一个电路:i.1)能记住自己目前所处的状态;ii.2)状态的变化只可能在同一个时钟的跳变沿时刻发生,而不可能发生在任意时刻;iii.3)在时钟跳变沿时刻,如输入条件满足,则进入下一状态,并记住自己目前所处的状态,否则仍保留原来的状态;iv.4)在进入不同的状态时刻,对系统的开关阵列做开启或关闭的操作。

b)什么是有限状态机i.有限状态机是由寄存器组和组合逻辑构成的硬件时序电路;ii.其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只能在同一时钟跳变的情况下才能转向另一个状态;iii.究竟转向哪一状态不但取决于各个输入值,还取决于当前状态。

iv.状态机可产生在时钟跳变沿时刻进行开关的复杂的控制逻辑,是数字逻辑的控制核心。

c)有限状态机三要素状态(当前状态,下一个状态);输入信号(事件);输出控制信号(相应操作).d)显式FSM:i.可以在过程块中用单一时钟边沿和case语句显式地描述FSM。

ii.必须声明定义状态机的状态变量。

iii.要改变当前状态,必须在时钟边沿改变状态变量的值。

iv.给通常不会发生的条件指定缺省动作(default)是一个很好的描述方式。

1.课程重点基于EDA工具的系统设计技术的掌握,包括HDL硬件描述语言、综合与时序仿真技术、EDA软件工具的熟练应用,软硬件系统联合设计与测试等。

2.课程的难点一是熟练掌握VHDL语言进行电子线路系统的设计技术;二是软硬件系统的联合设计与测试,且在工作速度、精度、可靠性、容错性、电磁兼容性及资源利用率等放面都能满足工程实际应用的要求。

3.解决办法1)突破传统的VHDL语言教学模式和流程,采用全新的教学理念和教学方式,将语言与EDA工程技术有机结合,以实现良好的教学效果,同时大大缩短了授课时数。

2)教学中以电子线路设计为基点,从实例的介绍中引出VHDL语句语法内容。

在典型示例的说明中,自然地给出完整的VHDL描述,同时给出其综合后的RTL电路图及表现该电路系统功能的时序波形图。

通过一些简单、直观、典型的实例,将VHDL中最核心、最基本的内容解释清楚,使学生在很短的时间内就能有效地掌握VHDL的主干内容,并付诸设计实践。

而传统的方法大多数是按部就班地讲解所有的VHDL语句,包括许多很少用到的非RTL语句,影响了效率。

3)根据EDA技术课程实践性强的特点,设计由浅入深、自主创新等开放类实验项目。

各实验除给出详细的实验目的、原理、思考题和实验报告要求外,每个实验还包括多个实验项目(层次),即:第一实验层次是与该课内容相关的验证性实验,提供了详细的设计程序和实验方法,使学生能有章可循,快速入门;第二实验层次是在上一实验基础上提出一些要求,让学生能做进一步的自主发挥;第三、第四实验层次属于自主设计或创新性质的实验,在其中给出实验的基本原理,实验功能,技术指标要求和设计提示等。

实验题目包括一些全国大学生电子设计竞赛的典型赛题、工程实际项目等。

4)综合相关因素,优化教学效果。

理论教学与创新实验相结合、创新能力培养与学生科技活动( 包括电子设计竞赛)相结合、完成教学任务与适应人才市场专业需求相结合、和外校技术培训与经验交流相结合。