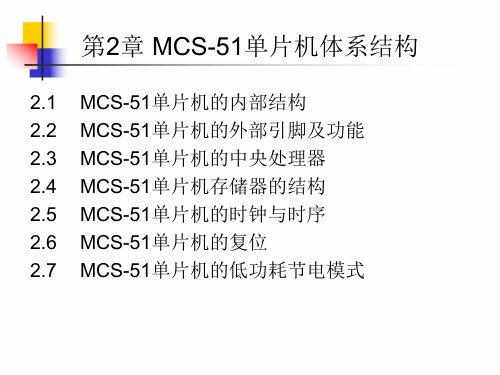

2-2引脚

- 格式:ppt

- 大小:409.00 KB

- 文档页数:39

单片机各个引脚功能概述单片机是一种集成电路,其中具有多个引脚,每个引脚都具有不同的功能。

下面是单片机各个引脚的功能概述:1.VCC:VCC引脚为单片机的电源引脚,通常连到电池或电源电压上。

它为单片机提供正向电源,电压通常为3.3V或5V。

2.GND:GND引脚为单片机的接地引脚,通常使用地线连接到电路板的地方。

该引脚为单片机提供回路的参考点。

3.XTAL1和XTAL2:XTAL1和XTAL2引脚是单片机的振荡器引脚,通常连接到晶体振荡器或陶瓷谐振器中的引脚。

这些引脚提供时钟脉冲,以控制单片机的时序和计时。

4.RESET:RESET引脚是单片机的复位引脚,通常使用它来将单片机恢复到初始状态。

当RESET引脚被拉低时,单片机将重新启动。

5.P0.0-P0.7:P0.0-P0.7是单片机的I/O端口0引脚,用于连接外部设备。

这些引脚可以被配置为输入或输出端口,以与外部设备通信。

6.P1.0-P1.7:P1.0-P1.7是单片机的I/O端口1引脚,用于连接外部设备。

这些引脚也可以被配置为输入或输出端口,以与外部设备通信。

7.P2.0-P2.7:P2.0-P2.7是单片机的I/O端口2引脚,用于连接外部设备。

这些引脚可以被配置为输入或输出端口,以与外部设备通信。

8.P3.0-P3.7:P3.0-P3.7是单片机的I/O端口3引脚,用于连接外部设备。

这些引脚也可以被配置为输入或输出端口,以与外部设备通信。

9.INT0和INT1:INT0和INT1引脚是单片机的外部中断引脚,用于检测外部中断事件。

这些引脚通常用于响应外部事件,例如按下按钮或检测外部信号。

10.TXD和RXD:TXD引脚是单片机的串行传输引脚,用于发送串行数据。

RXD引脚是单片机的串行接收引脚,用于接收串行数据。

这些引脚通常用于单片机与其他设备(例如计算机或传感器)之间的通信。

11.ADC0-ADC7:ADC0-ADC7引脚是单片机的模拟输入引脚,用于连接模拟传感器或外部设备。

《计算机维修技术第2版》易建勋编著清华大学出版社2009.8附件3-6:64位DDR2SDRAM Unb-DIMM内存条引脚功能定义(240脚)Pin Name Pin Name Pin Name Pin Name Pin Name Pin Name 1VREF41VSS81DQ33121VSS161NC(CB4)201VSS 2VSS42NC(CB0)*82VSS122DQ4162NC(CB5)*202DM4 3DQ043NC(CB1)*83DQS4123DQ5163VSS203NC 4DQ144VSS84DQS4124VSS164NC(DM8)*204VSS 5VSS45NC(DQS8)*85VSS125DM0165NC205DQ38 6DQS046NC(DQS8)*86DQ34126NC166VSS206DQ39 7DQS047VSS87DQ35127VSS167NC(CB6)*207VSS 8VSS48NC(CB2)*88VSS128DQ6168NC(CB7)*208DQ44 9DQ249NC(CB3)*89DQ40129DQ7169VSS209DQ45 10DQ350VSS90DQ41130VSS170VDDQ210VSS 11VSS51VDDQ91VSS131DQ12171CKE1211DM5 12DQ852CKE092DQS5132DQ13172VDD212NC 13DQ953VDD93DQS5133VSS173A15213VSS 14VSS54BA294VSS134DM1174A14214DQ46 15DQS155NC95DQ42135NC175VDDQ215DQ47 16DQS156VDDQ96DQ43136VSS176A12216VSS 17VSS57A1197VSS137CK1177A9217DQ52 18NC58A798DQ48138CK1178VDD218DQ53 19NC59VDD99DQ49139VSS179A8219VSS 20VSS60A5100VSS140DQ14180A6220CK2 21DQ1061A4101SA2141DQ15181VDDQ221CK222DQ1162VDDQ102NC,TEST1142VSS182A3222VSS23VSS63A2103VSS143DQ20183A1223DM624DQ1664VDD104DQS6144DQ21184VDD224NC25DQ1765VSS105DQS6145VSS185CK0225VSS26VSS66VSS106VSS146DM2186CK0226DQ5427DQS267VDD107DQ50147NC187VDD227DQ5528DQS268NC108DQ51148VSS188A0228VSS29VSS69VDD109VSS149DQ22189VDD229DQ6030DQ1870A10/AP110DQ56150DQ23190BA1230DQ6131DQ1971BA0111DQ57151VSS191VDDQ231VSS32VSS72VDDQ112VSS152DQ28192RAS232DM733DQ2473WE113DQS7153DQ29193S0233NC34DQ2574CAS114DQS7154VSS194VDDQ234VSS35VSS75VDDQ115VSS155DM3195ODT0235DQ6236DQS376S1116DQ58156NC196A13236DQ6337DQS377ODT1117DQ59157VSS197VDD237VSS38VSS78VDDQ118VSS158DQ30198VSS238VDDSPD 39DQ2679VSS119SDA159DQ31199DQ36239SA040DQ2780DQ32120SCL160VSS200DQ37240SA1DDR2内存引脚Front BackPin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol Pin Symbol1VREF31DQ1961A491VSS121VSS151VSS181VDDQ211DM5/DQS14 2VSS32VSS62VDDQ92DQS5#122DQ4152DQ28182A3212NC/DQS14# 3DQ033DQ2463A293DQS5123DQ5153DQ29183A1213VSS4DQ134DQ2564VDD94VSS124VSS154VSS184VDD214DQ465VSS35VSS65VSS95DQ42125DM0/DQS9155DM3/DQS12185CK0215DQ476DQS0#36DQS3#66VSS96DQ43126NC/DQS9#156NC/DQS12#186CK0#216VSS7DQS037DQS367VDD97VSS127VSS157VSS187VDD217DQ528VSS38VSS68PAR_IN98DQ48128DQ6158DQ30188A0218DQ539DQ239DQ2669VDD99DQ49129DQ7159DQ31189VDD219VSS10DQ340DQ2770A10/AP100VSS130VSS160VSS190BA1220RFU11VSS41VSS71BA0101SA2131DQ12161CB4191VDDQ221RFU12DQ842CB072VDDQ102NC132DQ13162CB5192RAS#222VSS13DQ943CB173WE#103VSS133VSS163VSS193S0#223DM6/DQS15 14VSS44VSS74CAS#104DQS6#134DM1/DQS10164DM8/DQS17194VDDQ224NC/DQS15# 15DQS1#45DQS8#75VDDQ105DQS6135NC/DQS10#165NC/DQS17#195ODT0225VSS16DQS146DQS876S1#106VSS136VSS166VSS196NC/A13226DQ5417VSS47VSS770DT1107DQ50137RFU167CB6197VDD227DQ5518RESET#48CB278VDDQ108DQ51138RFU168CB7198VSS228VSS19NC49CB379VSS109VSS139VSS169VSS199DQ36229DQ6020VSS50VSS80DQ32110DQ56140DQ14170VDDQ200DQ37230DQ6121DQ1051VDDQ81DQ33111DQ57141DQ15171CKE1201VSS231VSS22DQ1152CKE082VSS112VSS142VSS172VDD202DM4/DQS13232DM7/DQS16 23VSS53VDD83DQS4#113DQS7#143DQ20173NC203NC/DQS13#233NC/DQS16# 24DQ1654NC/BA284DQS4114DQS7144DQ21174NC204VSS234VSS25DQ1755ERR_OUT85VSS115VSS145VSS175VDDQ205DQ38235DQ6226VSS56VDDQ86DQ34116DQ58146DM2/DQS11176A12206DQ39236DQ6327DQS2#57A1187DQ35117DQ59147NC/DQS11#177A9207VSS237VSS28DQS258A788VSS118VSS148VSS178VDD208DQ44238VDDSPD29VSS59VDD89DQ40119SDA149DQ22179A8209DQ45239SA030DQ1860A590DQ41120SCL150DQ23180A6210VSS240SA1Note:Pin196is NC for512MB,or A13for1GB and2GB;pin54is NC for512MB and1GB,or BA2for2GB.Pin DescriptionsPin numbers may not correlate with symbols;refer to Pin Assignment table above for more information.Pin Numbers Symbol Type Description195ODT0Input On-Die Termination:ODT(registered HIGH)enables termination resistance internal to the DDR2SDRAM.When enabled,ODT is only applied to each of the following pins:DQ,DQS,DQS#,RDQS,RDQS#,CB,and DM.The ODT input will be ignored if disabled via the LOAD MODE command.185,186CK0,CK0#Input Clock:CK and CK#are differential clock inputs.All address and control input signals are sampled on thecrossing of the positive edge of CK and negative edge of CK#.Output data(DQs and DQS/DQS#)isreferenced to the crossings of CK and CK#.52CKE0Input Clock Enable:CKE(registered HIGH)activates and CKE(registered LOW)deactivates clocking circuitry onthe DDR2SDRAM.The specific circuitry that is enabled/disabled is dependent on the DDR2SDRAMconfiguration and operating mode.CKE LOW provides PRECHARGE POWER-DOWN and SELFREFRESH operations(all device banks idle),or ACTIVE POWERDOWN(row ACTIVE in any device bank).CKE is synchronous for POWER-DOWN entry,POWER-DOWN exit,output disable,and for SELFREFRESH entry.CKE is asynchronous for SELF REFRESH exit.Input buffers(excluding CK,CK#,CKE,and ODT)are disabled during POWER-DOWN.Input buffers(excluding CKE)are disabled during SELFREFRESH.CKE is an SSTL_18input but will detect a LVCMOS LOW level once VDD is applied duringfirst power-up.After Vref has become stable during the power on and initialization sequence,it must bemaintained for proper operation of the CKE receiver.For proper self-refresh operation VREF must bemaintained to this input.193S0#Input Chip Select:S#enables(registered LOW)and disables(registered HIGH)the command decoder.Allcommands are masked when S#is registered HIGH.S#provides for external rank selection on systems withmultiple ranks.S#is considered part of the command code.73,74,192RAS#,CAS#,Input Command Inputs:RAS#,CAS#,and WE#(along with S#)define the command being entered.WE#54(2GB),71,190BA0,BA1,BA2(2GB)Input Bank Address Inputs:BA0–BA1/BA2define to which device bank an ACTIVE,READ,WRITE,or PRECHARGE command is being applied.BA0–BA1define which mode register including MR,EMR,EMR(2),and EMR(3)is loaded during the LOAD MODE command.57,58,60,61,63,70,176,177,179,180, 182,183,188,196(1GB,2GB)A0–A12(512MB)A0–A13(1GB,2GB)Input Address Inputs:Provide the row address for ACTIVE commands,and the column address and auto prechargebit(A10)for Read/Write commands,to select one location out of the memory array in the respective bank.A10sampled during a PRECHARGE command determines whether the PRECHARGE applies to one devicebank(A10LOW,device bank selected by BA0–BA1/BA2)or all device banks(A10HIGH).The addressinputs also provide the op-code during a LOAD MODE command.3,4,9,10,12,13,21,22,24,25,30,31,33,34,39,40,80,81,86,87,89,90,95,96,98,99,107,108,110,111,116,117,122,123,128,129,131,132,140,141,143,144,149,150,152,153,158,159,199,200,205,206,208,209,214,215,217,218,226,227,229,230,235,236DQ0–DQ63I/O Data Input/Output:Bidirectional data bus.6,7,15,16,27,28,36,37,45,46,83,84, 92,93,104,105,113,114,126,135,147, 156,165,203,212,224,233125,134,146, 155,164,202,211,223,232DQS0–DQS8,DQS0#–DQS17#,DM0–DM8(DQS9–DQS17)I/O Data Strobe:Output with read data,input with write data for source synchronous operation.Edge-alignedwith read data,center aligned with write data.DQS#is only used when differential data strobe mode isenabled via the LOAD MODE command.Input Data Mask:DM is an input mask signal for write data.Inputdata is masked when DM is sampled HIGH along with that input data during a WRITE access.DM issampled on both edges of DQS.Although DM pins are input-only,the DM loading is designed to match thatof DQ and DQS pins.If RDQS is disabled,DQS0–DQS17become DM0–DM8and DQS9#–DQS17#are notused.42,43,48,49,161,162,167,168CB0–CB7I/O Check Bits.68PAR_IN Input Parity bit for the address and control bus.55ERR_OUT Output Parity error found on the address and control bus.120SCL Input Serial Clock for Presence-Detect:SCL is used to synchronize the presence-detect data transfer to and fromthe module.101,239,240SA0–SA2Input Presence-Detect Address Inputs:These pins are used to configure the presence-detect device.119SDA I/O Serial Presence-Detect Data:SDA is a bidirectional pin used to transfer addresses and data into and out of thepresence-detect portion of the module.18RESET#Input Asynchronously forces all registered outputs LOW when RESET#is LOW.This signal can be used duringpower up to ensure that CKE is LOW and DQs are High-Z.VDD Supply Power Supply:1.8V±0.1V.53,59,64,67,69,172,178,184,187,189,197,51,56,62,72,75,78,170,175,181,191,VDDQ Supply DQ Power Supply:1.8V±0.1V.194,1VREF Supply SSTL_18reference voltage.VSS Supply Ground.2,5,8,11,14,17,20,23,26,29,32,35,38,41,44,47,50,65,66,79,82,85,88,91,94,97,100,103,106,109,112,115,118,121,124,127,130,133,136,139,142,145,148,151,154,157,160,163,166,169,198,201,204,207,210,213,216,219,222,225,228,231,234,237238VDDSPD Supply Serial EEPROM positive power supply:+1.7V to+3.6V.19,54(512MB,1GB),76,77,102,171,NC—No Connect:These pins should be left unconnected.196(512MB),173,174,137,138,220,221RFU—Reserved for future use.。

有篇关于光耦的小文章推荐你看看:光电耦合器(简称光耦)是开关电源电路中常用的器件。

光电耦合器分为两种:一种为非线性光耦,另一种为线性光耦。

常用的4N系列光耦属于非线性光耦常用的线性光耦是PC817A—C系列。

非线性光耦的电流传输特性曲线是非线性的,这类光耦适合于弄开关信号的传输,不适合于传输模拟量。

线性光耦的电流传输手特性曲线接进直线,并且小信号时性能较好,能以线性特性进行隔离控制。

开关电源中常用的光耦是线性光耦。

如果使用非线性光耦,有可能使振荡波形变坏,严重时出现寄生振荡,使数千赫的振荡频率被数十到数百赫的低频振荡依次为号调制。

由此产生的后果是对彩电,彩显,VCD,DCD等等,将在图像画面上产生干扰。

同时电源带负载能力下降。

在彩电,显示器等开关电源维修中如果光耦损坏,一定要用线性光耦代换。

常用的4脚线性光耦有PC817A----C。

PC111 TLP521等常用的六脚线性光耦有:TLP632 TLP532 PC614 PC714 PS2031等。

常用的4N25 4N26 4N35 4N36是不适合用于开关电源中的,因为这4种光耦均属于非线性光耦。

以下是目前市场上常见的高速光藕型号:100K bit/S:6N138、6N139、PS87031M bit/S:6N135、6N136、CNW135、CNW136、PS8601、PS8602、PS8701、PS9613、PS9713、CNW4502、HCPL-2503、HCPL-4502、HCPL-2530(双路)、HCPL-2531(双路)10M bit/S:6N137、PS9614、PS9714、PS9611、PS9715、HCPL-2601、HCPL-2611、HCPL-2630(双路)、HCPL-2631(双路)光耦合器的增益被称为晶体管输出器件的电流传输比(CTR),其定义是光电晶体管集电极电流与LED正向电流的比率(ICE/IF)。

光电晶体管集电极电流与VCE有关,即集电极和发射极之间的电压。

RS232DB9公头母头串⼝引脚定义转⾃:DB9 公头母头串⼝引脚定义1.RS-232端(DB9母头/孔型)引脚定义引脚序号 2 3 5 1、4、6 7、8信号定义 TXD RXD GND 内部相连内部相连注:该⼝可直接插⼊计算机的COM⼝2.RS-232端(DB9公头/针型)引脚定义引脚序号 2 3 5 1、4、6 7、8信号定义 RXD TXD GND 内部相连内部相连注:该⼝可接与计算机通讯的设备下⾯是:公⼝介绍,请欣赏~~~说明:实际开发接⼝时,⼀般只要2,3,5,即收、发和地三根线,就能实现通信。

DB9和DB25的常⽤信号脚说明;RS232接⼝针脚定义Pin 1 Received Line Signal Detector (Data Carrier Detect) Pin 2 Received Data Pin 3 Transmit Data Pin 4 Data Terminal Ready Pin 5 Signal Ground Pin 6 Data Set Ready Pin 7 Request To Send Pin 8 Clear To Send Pin 9 Ring IndicatorRS232接⼝针脚定义 25针的接⼝定义: Pin 1 Protective Ground Pin 2 Transmit Data Pin 3 Received Data Pin 4 Request To Send Pin 5 Clear To Send Pin 6 Data Set Ready Pin 7 Signal Ground Pin 8 Received Line Signal Detector (Data Carrier Detect)Pin 20 Data Terminal Ready接线说明1.DB9和DB25的常⽤信号脚说明9针串⼝(DB9) 25针串⼝(DB25)针号功能说明 缩写 针号功能说明 缩写1 数据载波检测 DCD 8 数据载波检测 DCD2 接收数据 RXD3 接收数据 RXD3 发送数据 TXD 2 发送数据 TXD4 数据终端准备 DTR 20 数据终端准备 DTR5 信号地 GND 7 信号地 GND6 数据设备准备好 DSR 6 数据准备好 DSR7 请求发送 RTS 4 请求发送 RTS8 清除发送 CTS 5 清除发送 CTS9 振铃指⽰ DELL 22 振铃指⽰ DELL2.RS232C串⼝通信接线⽅法(三线制)9针-9针 25针-25针 9针-25针 2 - 33 - 2 2 - 23 - 2 2 - 3 3 - 3 5 - 5 7 - 7 5 - 7RS-232接⼝RS-232串⾏接⼝标准 ⽬前RS-232是PC机与通信⼯业中应⽤最⼴泛的⼀种串⾏接⼝。

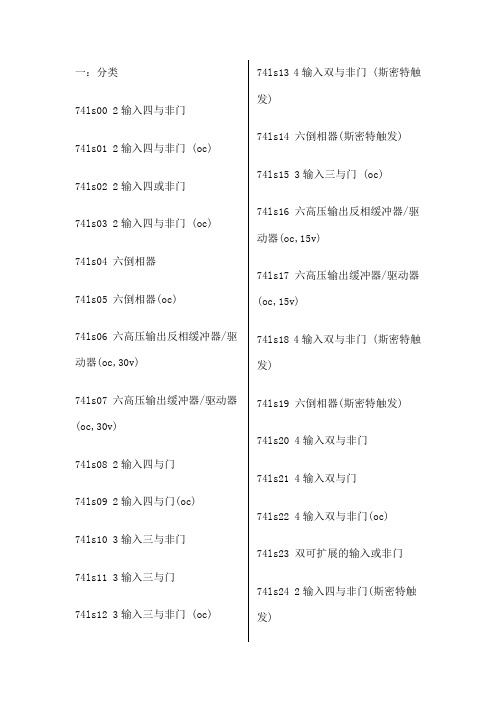

一:分类74ls00 2输入四与非门74ls01 2输入四与非门 (oc) 74ls02 2输入四或非门74ls03 2输入四与非门 (oc) 74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v)74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门 (oc) 74ls13 4输入双与非门 (斯密特触发)74ls14 六倒相器(斯密特触发) 74ls15 3输入三与门 (oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v)74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门 (斯密特触发)74ls19 六倒相器(斯密特触发) 74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通) 74ls26 2输入四高电平接口与非缓冲器(oc,15v)74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出)74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通) 74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出74ls39 2输入四或非缓冲器(集电极开路输出)7 4ls40 4输入双与非缓冲器7 4ls41 bcd-十进制计数器7 4ls42 4线-10线译码器(bcd输入)7 4ls43 4线-10线译码器(余3码输入)7 4ls44 4线-10线译码器(余3葛莱码输入)7 4ls45 bcd-十进制译码器/驱动器7 4ls46 bcd-七段译码器/驱动器4ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展)74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)4ls53 四路2-2-2-2输入与或非门(可扩展)74ls53 四路2-2-3-2输入与或非门(可扩展)74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展4ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门 74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk 触发器74ls71 与输入r-s 主从触发器74ls72 与门输入主从jk 触发器74ls73 双j-k 触发器(带清除端)4ls74 正沿触发双d 型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k 触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k 触发器(带预置端,公共清除端和公共时钟端)74ls80 门控全加器74ls81 16位随机存取存储器4ls82 2位二进制全加器(快速进位) 4ls83 4位二进制全加器(快速进位)7 4ls84 16位随机存取存储器74ls85 4位数字比较器7 4ls86 2输入四异或门7 4ls87 四位二进制原码/反码/oi单元7 4ls89 64位读/写存储器7 4ls90 十进制计数器7 4ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)7 4ls93 4位二进制计数器7 4ls94 4位移位寄存器(异步)7 4ls95 4位移位寄存器(并行io)7 4ls96 5位移位寄存器7 4ls97 六位同步二进制比率乘法器4ls100 八位双稳锁存器74ls103 负沿触发双j-k 主从触发器(带清除端)74ls106 负沿触发双j-k 主从触发器(带预置,清除,时钟)74ls107 双j-k 主从触发器(带清除端)74ls108 双j-k 主从触发器(带预置,清除,时钟)74ls109 双j-k 触发器(带置位,清除,正触发)4ls110 与门输入j-k 主从触发器(带锁定)74ls111 双j-k 主从触发器(带数据锁定)74ls112 负沿触发双j-k 触发器(带预置端和清除端)74ls113 负沿触发双j-k 触发器(带预置端)74ls114 双j-k 触发器(带预置端,共清除端和时钟端)74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器4ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器4ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器 74ls139 双2-4线译码器/多路转换器4ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器 74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)4ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出)74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)4ls160 可预置bcd 计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步)74ls162 可预置bcd 计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步)74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)4ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d 触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d 型寄存器(带清除端)74ls174 六d 触发器4ls175 四d 触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器4ls184 bcd-二进制转换器74ls185 二进制-bcd 转换器74ls190 同步可逆计数器(bcd,二进制)74ls191 同步可逆计数器(bcd,二进制)74ls192 同步可逆计数器(bcd,二进制)74ls193 同步可逆计数器(bcd,二进制)74ls194 四位双向通用移位寄存器4ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制)74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器4ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出)74ls241 八缓冲器/线驱动器/线接收器(原码三态输出)74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器4ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器4ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)4ls271 2048位rom (256位八字节,oc)74ls273 八d 触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk 触发器74ls278 四位可级联优先寄存器74ls279 四s-r 锁存器74ls280 9位奇数/偶数奇偶发生器/较验器4ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)4ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出4ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器 74ls368 六反向三态缓冲器/线驱动器 74ls373 八d 锁存器4ls374 八d 触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d 触发器74ls378 六d 触发器74ls379 四d 触发器74ls381 算术逻辑单元/函数发生器 74ls382 算术逻辑单元/函数发生器 74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器4ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出)74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器 74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出) 74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出) 74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除)74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器LM12瓦运算放大器LM124 LM224 LM324 LM2902 低电压双路运算放大器LM324 低电压双路运算放大器LM129 LM329 精密电压基准芯片LM135 LM235 LM335 精密温度传感器芯片LM1458 LM1558 双运算放大器LM158 LM258 LM358 LM2904 低压双运算放大器LM18293 四通道推拉驱动器LM1868 调幅/调频收音机芯片LM1951 1安培固态开关LM2574 降阶式电压调节器LM1575 LM2575 1A 降阶式电压调节器LM2576 3A 3A 降阶式电压调节器LM1577 LM2577 降阶式电压调节器LM2587 5A 返馈开关式电压调节器LM1893 LM2893 载体电流收发器LM193 LM293 LM393 LM2903 双路低压低漂移比较器LM2907 LM2917 频率电压转换器LM101A LM201A LM301A 运算放大器芯片LM3045 LM3046 LM3086 晶体管阵列LM111 LM211 LM311 电压比较器LM117 LM317 三端可调式稳压器LM118 LM218 LM318 运算放大器LM133 LM333安培可调负电压调节器LM137 LM337 可调式三端负压稳压器LM34 精密华氏温度传感器LM342 三端正压稳压器LM148 LM248 LM348 / LM149 LM349 双LM741运算放大器LM35 精密摄氏温度传感器LM158 LM258 LM358 LM2904 低压双运算放大器LM150 LM350 3安培可调式电压调节器LM380 瓦音频放大器LM386 低压音频功率放大器LM3886 高性能68瓦音频功率放大器/带静音LM555 LM555C 时基发生器电路LM556 LM556C 双时基发生器电路LM565 相位跟随器LM567 音频译码器LM621 无刷电机换向器LM628 LM629精密位移控制器LM675功率运算放大器LM723 电压调节器LM741 运算放大器LM7805 LM78xx 系列稳压器LM7812 LM78xx 系列稳压器LM7815 LM78xx 系列稳压器LM78L00 三端正压调节器LM78L05 三端正压调节器LM78L09三端正压调节器LM78L12三端正压调节器LM78L15 三端正压调节器LM78L62 三端正压调节器LM78L82 三端正压调节器LM340 LM78Mxx 三端正压稳压器LM7905 三端负压调节器LM7912 三端负压调节器LM7915 三端负压调节器LM79Mxx三端负压调节器LF147 LF347 宽带J型场效应输入运算放大器LF351 宽带J型场效应输入运算放大器LF353 宽带J型场效应输入运算放大器LF444 双低压J型场效应输入运算放大器(1) 74LS00双输入四与非门,管脚图如附图1-27所示。

存储芯片AT24C02

如图2-2为AT24C02的芯片引脚图。

图2-2 AT24C02的芯片引脚图

特点:低压和标准电压运行模式

– 2.7 (VCC = 2.7V to 5.5V)

– 1.8 (VCC = 1.8V to 5.5V)

内建128x8存储序列,2线制串行接口,双向数据传送协议,100kHz(1.8V,2.5V,2.7V) 和400kHz(5V)兼容,写同步时钟(最大10ms),高可靠性,极限:1M写时钟周期,数据保存:100年,不断推进的芯片等级扩大了设备的可用温度范围。

AT24C02提供电可擦除的串行1024位存储或可编程只读存储器(EEPROM)128字(8位/字)。

芯片在低压的工业与商业应用中进行了最优化。

设备操作:

CLOCK 和DATA变化:SDA管脚通常外部要拉高。

SDA管脚上的数据只能在SCL低期间改变。

数据在SCL高期间改变定义为一个开始或停止信号。

开始状态:在任何操作之前必须有一个开始信号----在SCL为高时SDA上产生一个下降沿。

停止状态: SCL为高时SDA产生一个上升沿是停止信号,停止信号后将停止所有通信。

在一个读的序列之后,停止信号将让EEPROM进入备用电源模式。

串口引脚定义图管脚定义vpc电脑串行口的典型是RS-232C及其兼容接口,串口引脚有9针和25针两类。

而一般的个人电脑中使用的都是9针的接口,25针串行口具有20mA电流环接口功能,用9、11、18、25针来实现。

我们只介绍常用9针的rs232c串口引脚的接口定义。

《串口引脚图》9针串行口的针脚功能:针脚功能针脚功能1 载波检测(DCD)2 接受数据(RXD)3 发出数据(TXD)4 数据终端准备好(DTR)5 信号地线(SG)6 数据准备好(DSR)7 请求发送(RTS)8 清除发送(CTS)9 振铃指示(RI)DB9 公头母头串口引脚定义1.RS-232端(DB9母头/孔型)引脚定义引脚序号 2 3 5 1、4、6 7、8 信号定义TXD RXD 地内部相连内部相连注:该口可直接插入计算机的COM口2.RS-232端(DB9公头/针型)引脚定义引脚序号 2 3 5 1、4、6 7、8 信号定义RXD TXD 地内部相连内部相连PC/XT 机上的串行口是25 针公插座,引脚定义为Transmit Data Request to SendData Terminal Ready硬件握手原理:第二种是使用硬件线握手。

和Tx和Rx线一样,RTS/CTS和DTR/DSR一起工作,一个作为输出,另一个作为输入。

第一组线是RTS (Request to Send)和CTS(Clear to Send)。

当接收方准备好接收数据,它置高RTS线表示它准备好了,如果发送方也就绪,它置高CTS,表示它即将发送数据。

另一组线是DTR(Data Terminal Ready)和DSR(Data Set Ready)。

这些现主要用于Modem通信。

使得串口和Modem通信他们的状态。

例如:当Modem已经准备好接收来自PC的数据,它置高DTR线,表示和电话线的连接已经建立。

读取DSR线置高,PC机开始发送数据。

一个简单的规则是DTR/DSR用于表示系统通信就绪,而RTS/CTS用于单个数据包的传输。