7两级CMOS运算放大器设计

- 格式:ppt

- 大小:1.73 MB

- 文档页数:38

模拟CMOS集成电路设计课程设计报告--------二级运算放大器旳设计信息科学技术学院电子与科学技术系一、概述:运算放大器是一种能将两个输入电压之差放大并输出旳集成电路。

运算放大器是模拟电子技术中最常用旳电路,在某种限度上,可以把它当作一种类似于BJT 或FET 旳电子器件。

它是许多模拟系统和混合信号系统中旳重要构成部分。

它旳重要参数涉及:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范畴、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

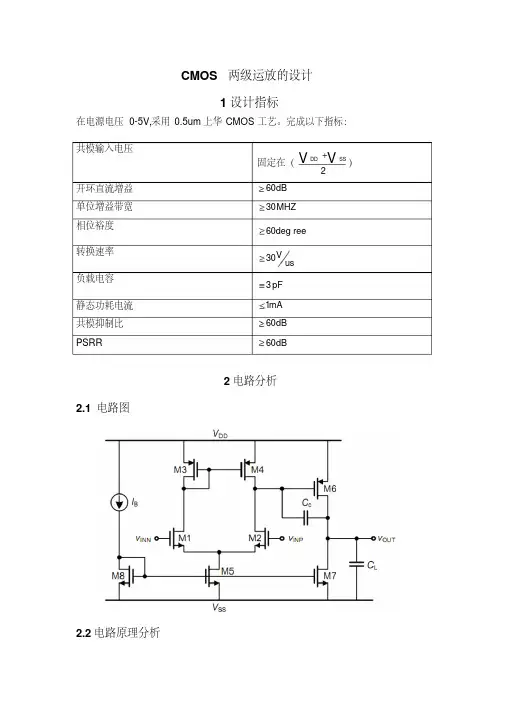

二、设计任务:设计一种二级运算放大器,使其满足下列设计指标:三、电路分析:1.电路构造:最基本旳二级运算放大器如下图所示,重要涉及四部分:第一级放大电路、第二级放大电路、偏置电路和相位补偿电路。

2.电路描述:输入级放大电路由PM2、PM0、PM1和NM0、NM1构成。

PM0和PM1构成差分输入对,使用差分对可以有效地克制共模信号干扰;NM0和NM1构成电流镜作为有源负载;PM2作为恒流源为放大器第一级提供恒定旳偏置电流。

第二级放大电路由NM2和PM3构成。

NM2为共源放大器;PM3为恒流源作负载。

相位补偿电路由电阻R0和电容C0构成,跨接在第二级输入输出之间,构成RC米勒补偿。

此外从电流电压转换角度来看,PM0和PM1为第一级差分跨导级,将差分输入电压转换为差分电流。

NM0和NM1为第一级负载,将差模电流恢复为差模电压。

NM2为第二级跨导级,将差分电压信号转换为电流,而PM3再次将电流信号转换成电压信号输出。

偏置电压由V0和V2给出。

3.静态特性对第一级放大电路:构成差分对旳PM0和PM1完全对称,故有G m1=g mp0=g mp1 (1)第一级输出电阻R out1=r op1||r on1 (2)则第一级电压增益A1=G m1Rout1=g mp0,1(r op1||r on1) (3) 对第二级放大电路:电压增益A2=G m2R out2= -g mn2(r on2||r op3) (4) 故总旳直流开环电压增益A0=A1A2= -g mp0,1g mn2(r op1||r on1)(r on2||r op3) (5) 由于所有旳管子都工作在饱和区,因此对于gm我们可以用公式g m =D I L W )/(Cox 2μ (6) 进行计算;而电阻r o 可由下式计算 r o =DI 1λ (7)其中λ为沟道长度调制系数且λ∝1/L 。

CMOS两阶段的级联操作放大器电路就像集成电路(IC)技术的超级

英雄。

由于其放大和冷却的金属—氧化—半导体(CMOS)技术的双重阶段,这个电路用高增益和增加带宽来打包一拳。

这就像瑞士军队

的刀模拟信号处理,准备应对任何挑战的方式。

无论是放大音频信

号还是在传感器中压缩数字这个电路都是你用来模拟一切的下一次

你需要信号助推,只要呼叫CMOS两级级级的操作放大器电路, IC

世界的无声英雄!

这个CMOS两阶段操作放大器的第一部分有几台晶体管,它们一起工作来提升输入信号,然后还有这个电流镜的东西可以帮助负载。

这个

第一阶段基本上为第二部分铺设了舞台。

第二阶段类似于encore,它能增加更多的收益,并有助于提升输出电压。

很酷的是,第一阶段的

输出只是直接插入第二阶段的输入,所以它就像这种双功率提升的配置。

CMOS两阶段的级联操作放大器电路具有重大优点,包括收益高、输

入阻力高以及铁路对铁路输出摇摆。

它适合需要大量扩展的应用程序,特别是在数据获取系统、传感器接口和音频信号处理领域。

电路的配

制和加强涉及仔细考虑晶体管的尺寸、偏差和计费技术,所有这些技

术都是为了达到所期望的性能指标。

两级全差动运算放大器的设计华中科技大学IC课程设计两级全差动运算放大器的设计年级:学号:姓名:专业:指导老师:二零一一年十二月摘要应用0.18umCMOS工艺,设计了一个放大倍数为86dB、单位增益带宽为360MHz、负载为1pF的两级全差动运算放大器。

可以满足一定的高速度、高精度的指标。

两级分别由一个差分的共源放大器和一个折叠式放大器组成。

通过运用差动输出代替普通两级运算放大器的单端输出,从而提高了输入动态范围、抑制共模信号和噪声的能力等性能。

因此,优于一些传统的两级运算放大器。

关键词:全差动运算放大器;共源放大器;折叠式放大器AbstractA fully differential operational amplifier with a DC-gain of 86dB and a gain-bandwidth of 360 MHz has been implemented in a 0.18um CMOS process.It can satisfy the index of high speed and high precision.And the two level is respectively made up of a common-source amplifier and a Folding amplifier.Therefore,it is better than some of the traditional operational amplifier.Keywords:fully differential operational amplifier; common-source amplifier; Folding amplifier目录摘要 (1)Abstract (2)1.引言 (4)2. 两级全差动运算放大器设计要求 (4)3. 电路分析与设计 (4)3.1.第一级运算放大器设计 (5)3.1.1第一级差模电压增益 (6)3.1.2.共模电压输入范围 (6)3.1.3.第一级增益带宽积GBW (7)3.1.4.第一级MOS管宽长比 (7)3.1.5.第一级仿真结果 (7)3.2.第二级运算放大器设计 (8)3.2.1.第二级差模电压增益 (9)3.2.2.偏置电压与偏值电流 (9)3.2.3.增益带宽积与负载电容 (9)3.2.4.第二级MOS管宽长比 (9)3.2.5.第二级仿真结果 (10)3.3.两级联仿 (10)3.3.1.差分压摆率 (11)3.3.2.静态功耗 (11)3.3.3.等效输入参考噪声 (11)3.3.4.相角裕度 (12)3.3.5.两级联仿结果 (13)4. 结论 (13)致谢 (14)参考文献 (14)心得体会 (15)1.引言随着模拟集成电路技术的发展,高速、高精度运算放大器得到广泛应用。

两级CMOS运算放大器设计引言CMOS运算放大器是现代电路设计中的重要组成部分,它在模拟电路中扮演着关键的角色。

CMOS运算放大器由于其低功耗、高增益和较低的失调电压而备受青睐。

本文将介绍两级CMOS运算放大器的设计方法,包括电路结构、工作原理以及性能指标。

电路结构两级CMOS运算放大器由两个级联的CMOS差动放大器组成,它们的输出分别连接在第二级差动放大器的输入上。

这种结构能够提供更高的增益和更好的线性度。

差动放大器差动放大器是CMOS运算放大器的关键组成部分,它用于将输入信号转换为差模信号,并放大差模信号以提供一个具有高增益的输出。

CMOS差动放大器由一对输入端和一对输出端组成,每个输入端都连接了一个NMOS和一个PMOS管,这样可以实现单端输入和差分输入。

工作原理两级CMOS运算放大器的工作原理如下:1.输入信号被差动放大器的第一级转换为差模信号,并经过第一级放大。

第一级放大的输出信号被传递给第二级放大器。

2.第二级差动放大器放大差模信号,然后将其转换为单端输出信号。

3.输出信号经过一个输出级,通过一个负反馈回路被注入到第二级差动放大器的输入上。

设计步骤下面是设计两级CMOS运算放大器的一般步骤:1.确定电路的性能指标,例如增益、带宽以及失调电压等。

2.根据给定的性能指标选择差动放大器和输出级的电路结构。

3.根据选择的电路结构计算电路的参数,例如电阻、电容和晶体管的尺寸等。

4.使用电路模拟工具,例如SPICE,对电路进行仿真和优化。

5.布局电路,并进行布线。

6.进行电路的后仿真和测试。

性能指标两级CMOS运算放大器的性能指标通常包括以下几个方面:1.增益:运算放大器的增益是指输出信号相对于输入信号的放大程度。

在设计过程中,需要根据实际应用需求确定所需的增益。

2.带宽:带宽是指运算放大器能够输出一个相对稳定的放大信号的频率范围。

一般来说,带宽越大,运算放大器的性能越好。

3.失调电压:失调电压是指实际输入和理论输入之间的偏差。

CMOS二级运算放大器设计编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(CMOS二级运算放大器设计)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为CMOS二级运算放大器设计的全部内容。

CMOS二级运算放大器设计(东南大学集成电路学院)一.运算放大器概述运算放大器是一个能将两个输入电压之差放大并输出的集成电路.运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二.设计目标1.电路结构最基本的COMS二级密勒补偿运算跨导放大器的结构如图1。

1所示。

主要包括四部分:第一级输入级放大电路、第二级放大电路、偏置电路和相位补偿电路.图1.1 两级运放电路图2。

电路描述电路由两级放大器组成,M1~M4构成有源负载的差分放大器,M5提供该放大器的工作电流。

M6、M7管构成共源放大电路,作为运放的输出级。

M6 提供给 M7 的工作电流.M8~M13组成的偏置电路,提供整个放大器的工作电流。

相位补偿电路由M14和Cc 构成.M14工作在线性区,可等效为一个电阻,与电容Cc 一起跨接在第二级输入输出之间,构成RC 密勒补偿。

3。

设计指标两级运放的相关设计指标如表1。

三.电路设计第一级的电压增益:(3.1) 第二级电压增益:(3.2) 所以直流开环电压增益:(3.3) 单位增益带宽:(3。

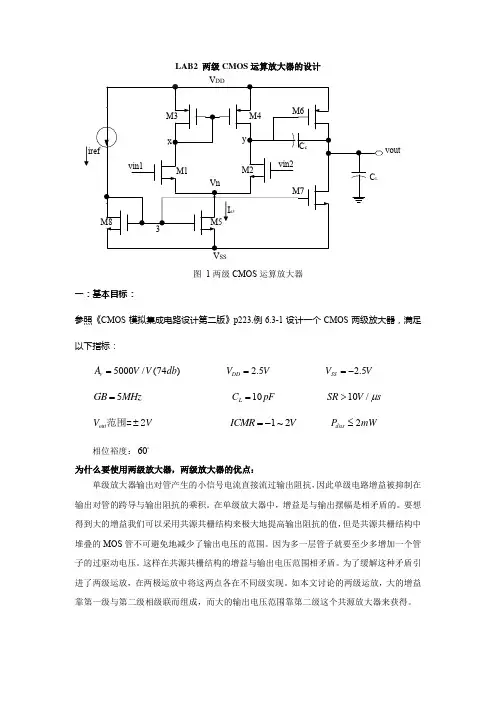

LAB2 两级CMOS 运算放大器的设计V SSvoutiref图 1两级CMOS 运算放大器一:基本目标:参照《CMOS 模拟集成电路设计第二版》p223.例6.3-1设计一个CMOS 两级放大器,满足以下指标:5000/(74)v A V V db = 2.5DD V V = 2.5SS V V =-5GB MHz = 10L C pF = 10/SR V s μ>out V V ±范围=2 1~2ICMR V =- 2diss P mW ≤相位裕度:60为什么要使用两级放大器,两级放大器的优点:单级放大器输出对管产生的小信号电流直接流过输出阻抗,因此单级电路增益被抑制在输出对管的跨导与输出阻抗的乘积。

在单级放大器中,增益是与输出摆幅是相矛盾的。

要想得到大的增益我们可以采用共源共栅结构来极大地提高输出阻抗的值,但是共源共栅结构中堆叠的MOS 管不可避免地减少了输出电压的范围。

因为多一层管子就要至少多增加一个管子的过驱动电压。

这样在共源共栅结构的增益与输出电压范围相矛盾。

为了缓解这种矛盾引进了两级运放,在两极运放中将这两点各在不同级实现。

如本文讨论的两级运放,大的增益靠第一级与第二级相级联而组成,而大的输出电压范围靠第二级这个共源放大器来获得。

表1 典型的无缓冲CMOS 运算放大器特性二:两级放大电路的电路分析:图1中有多个电流镜结构,M5,M8组成电流镜,流过M1的电流与流过M2电流1,23,45/2d d d I I I ==,同时M3,M4组成电流镜结构,如果M3和M4管对称,那么相同的结构使得在x ,y 两点的电压在Vin 的共模输入范围内不随着Vin 的变化而变化,为第二极放大器提供了恒定的电压和电流。

图1所示,Cc 为引入的米勒补偿电容。

表2 0.5m μ工艺库提供的模型参数表3 一些常用的物理常数利用表2、表3中的参数/OX ox ox C t ε=0oxK C μ'=计算得到2110/NK A V μ'≅ 262/PK A V μ'≅ 第一级差分放大器的电压增益为:1124m v ds ds g A g g -=+ (1)第二极共源放大器的电压增益为6267m v ds ds g A g g -=+ (2)所以二级放大器的总的电压增益为16261224675246672()()m m m m v v v ds ds ds ds g g g g A A A g g g g I I λλλλ===++++ (3)相位裕量有111121180tan ()tan ()tan ()60M GB GB GB p p z ---Φ=±---=要求60°的相位裕量,假设RHP 零点高于10GB 以上11102tan ()tan ()tan (0.1)120v GBA p ---++= 102tan ()24.3GBp -= 所以2 2.2p GB ≥ 即622.2()m m L cg gC C > 由于要求60的相位裕量,所以626210()10m m m m c cg gg g C C >⇒> 可得到 2.20.2210Lc L C C C >==2.2pF 因此由补偿电容最小值2.2pF ,为了获得足够的相位裕量我们可以选定Cc=3pF 考虑共模输入范围:在最大输入情况下,考虑M1处在饱和区,有3131(max)(max)DD SG n IC n TN IC DD SG TN V V V V V V V V V V --≥--⇒≤-+ (4)在最小输入情况下,考虑M5处在饱和区,有1515(min)(min)IC SS GS Dsat IC SS GS Dsat V V V V V V V V --≥⇒≤++ (5)而电路的一些基本指标有11m v Cg p A C =-(6) 62m Lg p C =-(7) 61m Cg z C =(8) 1m Cg GB C =(9) CMR:正的CMR in31()()DD T T V V V +(最大)=V 最大最小 (10)负的CMR in15()()SS T DS V V V ++(最小)=V 最大饱和(12)由电路的压摆率5d CI SR C =得到 5d I =(3*10-12)()10*106)=30μA(为了一定的裕度,我们取40iref A μ=。

op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。

由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。

OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。

特点:超低偏移:150μV最大。

低输入偏置电流:1.8nA 。

低失调电压漂移:0.5μV/℃。

超稳定,时间:2μV/month最大高电源电压范围:±3V至±22V图1 OP07外型图片图2 OP07 管脚图OP07芯片引脚功能说明:1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+图3 OP07内部电路图ABSOLUTE MAXIMUM RATINGS 最大额定值Symbol 符号Parameter参数Value数值Unit单位VCCSupply Voltage 电源电压±22 V VidDifferential Input Voltage差分输入电压±30 V Vi Input Voltage 输入电压±22 VTop er Operating Temperature 工作温度-40 to+105℃Tst g Storage T emperature 贮藏温度-65 to+150℃电气特性虚拟通道连接= ± 15V ,Tamb = 25 ℃(除非另有说明)Sy mbol 符号Parameter 参数及测试条件最小典型最大Unit单位Vio Input Offset Voltage 输入失调电压0℃≤ Tamb ≤ +70℃-61525μVLong Term Input Offset VoltageStability-(note 1) 长期输入偏置电压的稳定性-0.42μV/MoDVi o Input Offset Voltage Drift 输入失调电压漂移-0.51.8μV/℃Iio Input Offset Current输入失调电流0℃≤Tamb≤ +70℃-0.868nADIi o Input Offset Current Drift 输入失调电流漂移-155pA/℃Iib Input Bias Current输入偏置电流0℃≤Tamb ≤ +70℃-1.879nADIi b Input Bias Current Drift 输入偏置电流漂移-155pA/℃RoOpen Loop Output Resistance 开环输出电阻-6- ΩRidDifferential Input Resistance 差分输入电阻-33- MΩRicCommon Mode Input Resistance 共模输入电阻-12- GΩVic m Input Common Mode Voltage Range输入共模电压范围0℃≤ Tamb ≤ +70℃±13±13±13.5- VCM R Common Mode Rejection Ratio (Vi=Vicm min)共模抑制比0℃≤ Tamb ≤+70℃1009712- dBSV R Supply Voltage Rejection Ratio 电源电压抑制比(VCC = ±3to ±18V) 0℃≤Tamb ≤ +70℃908614- dBAv d LargeSignalVoltageGain 大信号电压增益VCC = ±15, RL=2KΩ,VO = ±10V,1204-V/mV 0℃≤ Tamb ≤ +105℃100 -VCC = ±3V, RL =500W,VO = ±0.5V1004-Vo pp OutputVoltageSwing 输出电压摆幅RL = 10KΩ±12±13- VRL= 2kΩ±11.5±12.8RL= 1KΩ±120℃≤Tamb ≤+70℃RL =2KΩ±11 -SR Slew Rate 转换率(RL =2KΩ,CL =100pF)-0.17-V/μSGB P Gain Bandwidth Product 带宽增益(RL=2KΩ,CL = 100pF, f = 100kHz)-0.5-MHzIcc Supply Current -(no load) 电源电流(无负载)0℃≤Tamb ≤+70℃VCC = ±3V-2.70.67561.3mAen EquivalentInput NoiseVoltage等效输入噪声电压f = 10Hz -112nV√Hzf = 100Hz -10.513.5f = 1kHz -111.5in EquivalentInput NoiseCurrent 等效输入噪声电流f = 10Hz -0.3.9PA√Hzf = 100Hz -0.2.3f = 1kHz - 0.1.2图4 输入失调电压调零电路应用电路图:图5 典型的偏置电压试验电路图6 老化电路图7 典型的低频噪声放大电路图8 高速综合放大器图9 选择偏移零电路图10 调整精度放大器图11 高稳定性的热电偶放大器图12 精密绝对值电路。

CMOS二级运算放大器设计CMOS二级运放的基本结构包括差分对和共模反馈电路。

差分对是一对输入端分别与PNP型和NPN型晶体管相连的放大器。

这对晶体管的基极分别与镜像电流源相连,以提供共模反馈和差分模式放大。

共模反馈电路通过将差分模式信号与公共节点(即两个输入端的中点)比较,从而产生反馈信号,并将其注入到差分对中以抑制共模干扰。

1.确定规格和需求:确定运放的增益、频率响应、功耗和输入/输出特性等规格要求。

2.选择工作点:通过分析差分对的静态特性,选择适当的工作点。

工作点的选择应保证对输入信号具有较高的线性响应。

3.设计共模反馈电路:共模反馈电路包括反馈网络和差分对之间的连接。

通过反馈网络的设计,可以精确地抑制共模干扰,提高CMRR(共模抑制比)。

4.设计差分放大器:根据增益要求和输入/输出阻抗要求,设计差分放大器。

差分放大器的设计要考虑电压增益、带宽、输入和输出阻抗等因素。

5.设计输出级:输出级一般包括缓冲放大器和电流输出级。

缓冲放大器用于提供足够的驱动能力,以满足输出电流的要求。

电流输出级用于将电压信号转换为电流输出。

6.设计电源电压:根据设计要求和工艺限制,确定供电电压,并设计稳压电路以提供稳定的电源。

7.进行仿真和优化:通过电路仿真软件进行电路性能的模拟和优化,根据仿真结果进行参数调整和电路结构修改。

8.布局和版图设计:根据电路设计结果进行电路布局和版图设计,确保电路结构的可制造性和可靠性。

9.参数提取和后仿真:通过深入分析电路模型和特性,提取关键参数,并基于改进的模型进行后仿真。

根据后仿真结果进行最终的参数调整和性能评估。

最后,需要指出的是,CMOS二级运放的设计是一个综合性的工程任务,涉及到电路设计、模拟仿真、版图设计以及后仿真等多个方面的知识和技能。

在实际应用中,还需要考虑工艺变化、温度变化和耦合等因素对电路性能的影响,以实现稳定和可靠的运放电路设计。

两级CMOS运算放大器设计一:实验目的:1. 会运用Cadence设计工具。

熟悉计算机进行集成电路进行辅助设计的流程。

2.掌握模拟电路仿真方法、掌握电子电路、电子器件芯片底层版图的设计规则和方法。

3. 掌握用计算机对电路、电子器件进行参数提取及功能模拟的过程。

实验软件:Cadence-Virtuoso; Cadence-Assura.二:设计指标要求:电源电压为3.3V,共模电压范围是1V,差分幅值范围是1m~100mV,负载电容是10pF,压摆率大于10/us,单位增益带宽是5MHz。

幅值增益是70dB,相位欲度大于60度,功耗小于2mW,工作温度为0到85°之间。

三:实验过程及仿真,版图首先,利用Cadence Virtuoso搭建单级CMOS放大器,采用共源级结构,以电流镜作为负载,原理图如下图所示单级CMOS放大器原理图利用spectre对该电路进行小信号仿真,得到它的增益,带宽和相位裕度如下列图所示单级CMOS放大器的小信号增益(56.5dB)单级CMOS放大器-3dB带宽(2.92k)单级CMOS放大器相位裕度(89.32°)对该单级放大器输入方波信号,得到其摆率如下图所示单级CMOS放大器摆率(65.74*106μV/s)应用virtuoso绘制该单级放大器版图,如下图所示单级放大器版图对上面提到的版图做rcx后提取,得到下图单级CMOS放大器rcx提取网表绘制两级CMOS运算放大器的原理图如下图所示,含米勒电容和调零电阻两级CMOS运算放大器的原理图对两级CMOS运算放大器进行小信号仿真,得到其增益,带宽和相位裕度如下列图所示两级CMOS运算放大器的增益(75.0dB)两级CMOS运算放大器的-3dB带宽(1.084M)两级CMOS运算放大器的相位裕度(68°)两级CMOS运算放大器的单位增益带宽(7.244M)对该CMOS两级运算放大器输入方波信号,得到其摆率如下图所示两级CMOS运算放大器的摆率应用virtuoso绘制该CMOS两级运算放大器版图,如下图所示CMOS两级运算放大器版图对上面提到的版图做rcx后提取,得到下图两级CMOS运算放大器版图对单级CMOS放大器rcx网表进行仿真,得到其性能指标如下列图所示单级CMOS放大器后仿真增益(51.5dB)单级CMOS放大器后仿真-3dB带宽(8.624k)单级CMOS放大器后仿真相位裕度(70.5°)对该单级放大器的rcx网表输入方波信号,得到其摆率如下图所示单级CMOS放大器后仿真摆率(13.03*106μV/s)。

CMOS两级运算放大器设计CMOS(互补金属氧化物半导体)两级运算放大器是一种常用的放大器设计,可以用于信号放大、滤波、放大器链路等应用。

本文将对CMOS两级运算放大器的设计进行详细叙述。

首先,设计CMOS差动对。

差动对由两个MOSFETs组成,其中一个为p-MOSFET,另一个为n-MOSFET。

这两个MOSFETs的栅极交叉,源极相连,并接入一个电流源。

这样可以使输入信号以差分模式进入放大器。

然后,设计CMOS差动对的偏置电路。

偏置电路主要是为了使CMOS差动对能够正常工作。

其中,主要包括两个电流源和一个电流镜。

电流源为差动对提供恒定电流,电流镜用于分配输入级和输出级的电流。

通过适当选择偏置电流的大小,可以控制放大器的增益和输出幅度。

接下来,设计中间电压增益级。

增益级主要由两个共尺极级组成,通过增加电阻、电容等元件来实现电压放大。

增益级的输出连接到输出级的输入,将中间电压信号传递到输出级进行电流差分放大。

最后,设计输出级。

输出级主要由两个MOSFETs组成,其中一个为p-MOSFET,另一个为n-MOSFET。

这两个MOSFETs的栅极相连,并连接到输入级的输出。

通过适当控制输出级电压的变化,可以实现电流信号的放大。

在CMOS两级运算放大器的设计过程中,需要考虑的因素包括放大器的增益、带宽、输入输出阻抗、偏置电流等。

根据具体的应用需求,可以平衡这些因素来进行合适的设计。

在设计完成后,需要进行电路仿真和调试。

可以使用软件工具如Spice来进行电路模拟,并根据模拟结果进行调整和优化。

在实际测试中,可以通过改变输入信号的频率和幅度,观察输出信号的响应,并与设计要求进行对比。

总结起来,CMOS两级运算放大器设计是一个复杂的过程,需要考虑多个因素,并进行合适的优化。

通过合理的设计和调试,可以获得满足设计要求的放大器电路。

课程设计报告设计课题: CMOS二级密勒补偿运算放大器的设计姓名: XXX专业: 集成电路设计与集成系统学号: 1115103004 日期 2015年1月17日指导教师: XXX 国立华侨大学信息科学与工程学院一:CMOS二级密勒补偿运算放大器的设计1:电路结构最基本的CMOS二级密勒补偿运算跨导放大器的结构如下图,主要包括四部分:第一级PMOS输入对管差分放大电路,第二级共源放大电路,偏置电路和相位补偿电路。

2:电路描述:输入级放大电路由M1~M5组成。

M1和M2组成PMOS差分输入对管,差分输入与单端输入相比可以有效抑制共模信号干扰;M3和M4为电流镜有源负载;M5为第一级放大电路提供恒定偏置电流。

输出级放大电路由M6和M7组成,M6为共源放大器,M7为其提供恒定偏置电流同时作为第二级输出负载。

偏置电路由M8~M13和Rb组成,这是一个共源共栅电流源,M8和M9宽长比相同。

M12和M13相比,源级加入了电阻Rb,组成微电流源,产生电流Ib。

对称的M11和M12构成共源共栅结构,减少了沟道长度调制效应造成的电流误差。

在提供偏置电流的同时,还为M14栅极提供偏置电压。

相位补偿电路由M14和Cc组成,M14工作在线性区,可等效为一个电阻,与电容Cc一起跨接在第二级输入输出之间,构成RC密勒补偿。

3:两级运放主体电路设计由于第一级差分输入对管M1与M2相同,有R1表示第一级输出电阻,其值为则第一级的电压增益对第二级,有第二级的电压增益故总的直流开环电压增益为所以4:偏置电路设计偏置电路由 M8~M13 构成,其中包括两个故意失配的晶体管M12 和M13,电阻RB 串联在M12 的源极,它决定着偏置电流和gm12,所以一般为片外电阻以保证其精确稳定。

为了最大程度的降低M12 的沟道长度调制效应,采用了Cascode 连接的M10以及用与其匹配的二极管连接的M11 来提供M10 的偏置电压。

最后,由匹配的PMOS器件M8 和M9 构成的镜像电流源将电流IB 复制到M11 和M13,同时也为M5 和M7提供偏置。