乒乓操作

- 格式:docx

- 大小:64.83 KB

- 文档页数:3

乒乓ram简介在现在的数据采集分析系统中,随着采集数据的速度剧增,每次都对这些庞大的数据量直接进行分析,这将会占用很多的CPU,使得CPU不能及时的去做其它的事情。

我们可以在传输这些数据的时候提供适当的通道,建立一个缓冲电路,来实现数据流的无缝缓存和处理,提高系统的处理速度和性能。

输入输出缓存电路一般有三种结构和形式:①双口ram结构:双口RAM是在一个SRAM存储器上具有两套完全独立的数据线、地址线、读写控制线、并允许两个独立的系统同时对该存储器进行随机访问。

②FIFO结构:FIFO(First In First Out)是一种先进先出的数据缓存器,可以进行双端操作,但是数据必须先进先出,不能进行随机性的访问。

从容量大小来看,双口RAM比FIFO要大一些,但总的来说,这两种缓冲结构的存储容量还是相对较小,对高速图像处理系统而言,还不是特别适合。

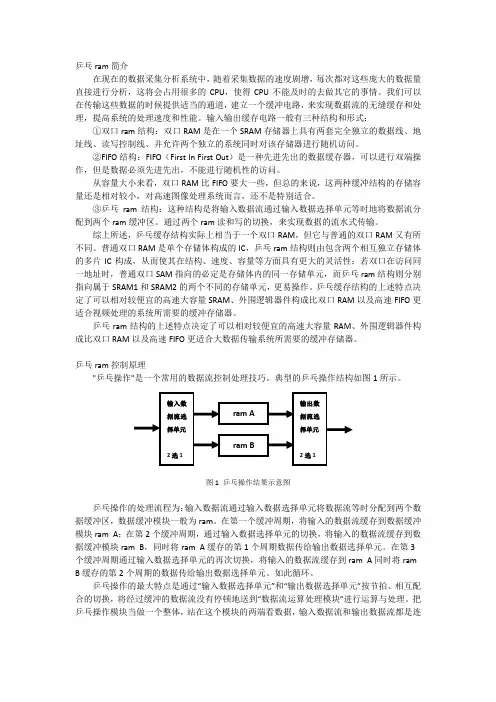

③乒乓ram结构:这种结构是将输入数据流通过输入数据选择单元等时地将数据流分配到两个ram缓冲区。

通过两个ram读和写的切换,来实现数据的流水式传输。

综上所述,乒乓缓存结构实际上相当于一个双口RAM,但它与普通的双口RAM又有所不同。

普通双口RAM是单个存储体构成的IC,乒乓ram结构则由包含两个相互独立存储体的多片IC构成,从而使其在结构、速度、容量等方面具有更大的灵活性;若双口在访问同一地址时,普通双口SAM指向的必定是存储体内的同一存储单元,而乒乓ram结构则分别指向属于SRAM1和SRAM2的两个不同的存储单元,更易操作。

乒乓缓存结构的上述特点决定了可以相对较便宜的高速大容量SRAM、外围逻辑器件构成比双口RAM以及高速FIFO更适合视频处理的系统所需要的缓冲存储器。

乒乓ram结构的上述特点决定了可以相对较便宜的高速大容量RAM、外围逻辑器件构成比双口RAM以及高速FIFO更适合大数据传输系统所需要的缓冲存储器。

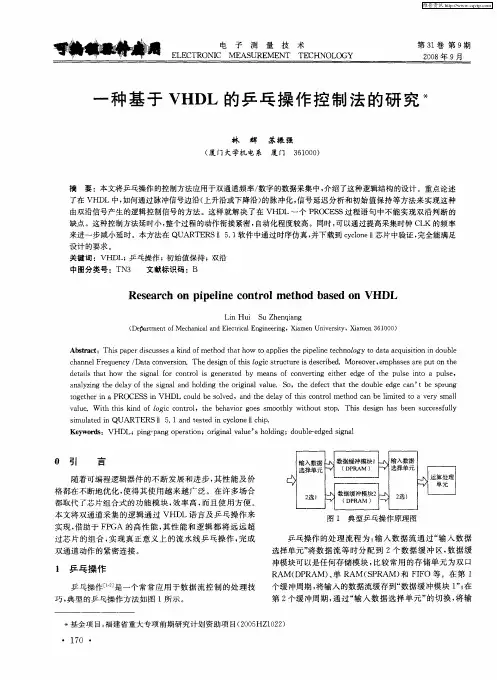

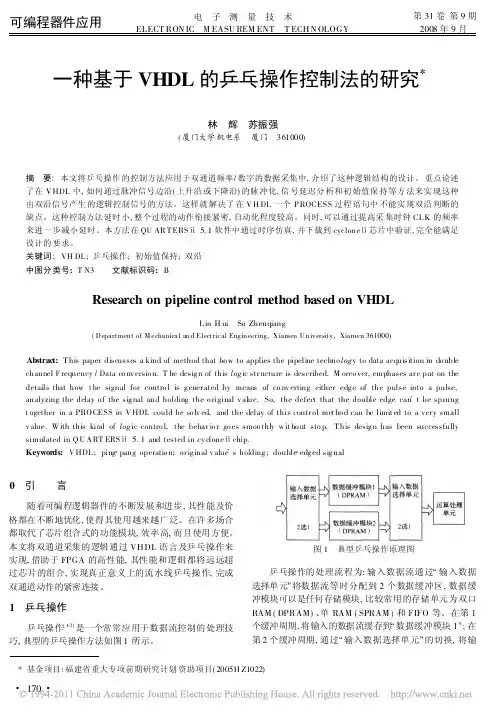

乒乓ram控制原理"乒乓操作"是一个常用的数据流控制处理技巧。

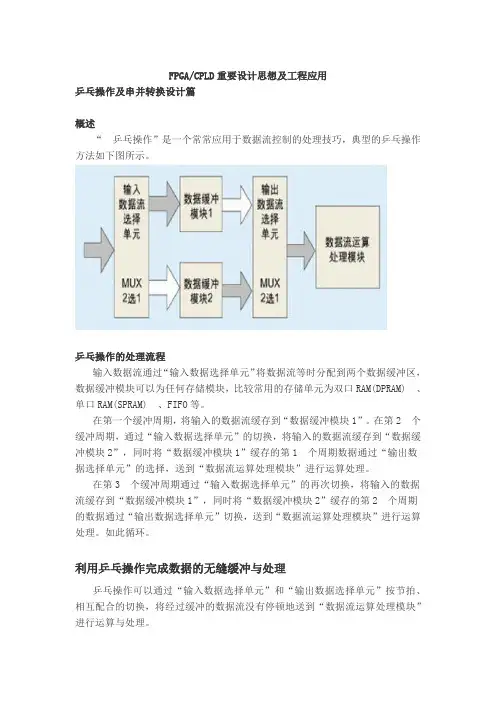

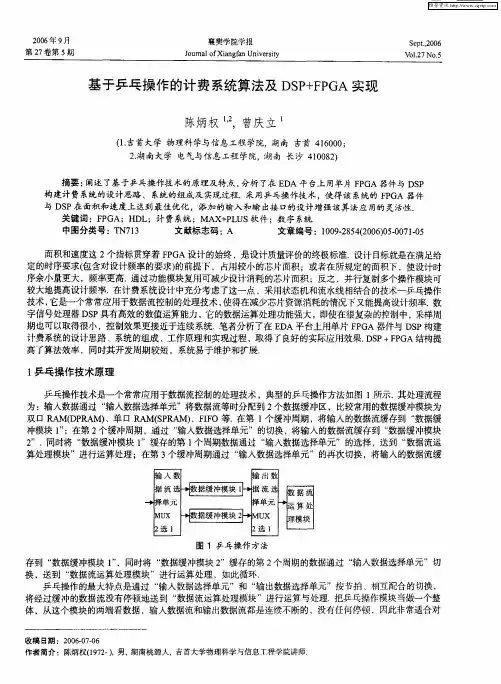

FPGA/CPLD重要设计思想及工程应用乒乓操作及串并转换设计篇概述“乒乓操作”是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如下图所示。

乒乓操作的处理流程输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO等。

在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”。

在第2 个缓冲周期,通过“输入数据选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1 个周期数据通过“输出数据选择单元”的选择,送到“数据流运算处理模块”进行运算处理。

在第3 个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,同时将“数据缓冲模块2”缓存的第2 个周期的数据通过“输出数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。

如此循环。

利用乒乓操作完成数据的无缝缓冲与处理乒乓操作可以通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。

把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。

所以乒乓操作常常应用于流水线设计中,完成数据的无缝缓冲与处理。

串并转换串并转换是FPGA 设计的一个重要技巧,它是高速数据流处理的常用手段,串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO 等实现。

若想数据的缓冲区开得很大,可以通过DPRAM 实现了数据流的串并转换,对于数量比较小的设计可以采用寄存器完成串并转换。

如无特殊需求,系统中应该用同步时序设计完成串并之间的转换。

数据乒乓操作原理数据乒乓操作原理数据乒乓操作是指在数据库中进行读取和修改数据的过程中,使用缓存机制来提高性能和效率的一种技术。

本文将详细介绍数据乒乓操作的原理。

一、什么是数据乒乓操作?在数据库中,读取和修改数据通常都需要进行I/O操作,而I/O操作是比较耗时的。

为了提高性能和效率,我们可以使用缓存机制来避免频繁进行I/O操作。

而数据乒乓操作就是利用缓存机制来实现对数据库的读取和修改。

二、数据乒乓操作的原理1. 缓存机制在进行数据乒乓操作时,我们首先需要了解缓存机制。

缓存就是将一些经常使用的数据保存在内存中,当需要访问这些数据时,直接从内存中读取,避免频繁进行磁盘IO操作。

2. 数据库连接池为了防止频繁地打开和关闭数据库连接造成性能损失,我们可以使用数据库连接池来管理数据库连接。

连接池会维护一定数量的数据库连接,并且提供对这些连接的管理和分配。

3. 读写分离为了进一步提高性能和效率,在进行数据读取时,我们可以采用读写分离策略。

读写分离是指将数据库的读操作和写操作分别放在不同的服务器上进行,这样可以减轻单台服务器的压力,提高系统的响应速度。

4. 数据乒乓操作在进行数据乒乓操作时,我们可以将数据库中的数据复制到缓存中,并且设置一个缓存过期时间。

当需要访问数据时,首先从缓存中读取,如果缓存中不存在该数据或者已经过期,则从数据库中读取,并且将数据更新到缓存中。

在进行修改操作时,我们首先对缓存中的数据进行修改,并且记录下来需要更新到数据库中的操作。

当达到一定条件(如时间间隔、修改次数等)时,才会将缓存中的修改操作批量提交到数据库中。

三、数据乒乓操作的优点1. 提高性能和效率通过使用缓存机制、连接池和读写分离等技术手段,可以大大提高系统性能和效率。

2. 减少I/O操作由于使用了缓存机制,在访问数据时可以避免频繁进行I/O操作,减少了系统负担和响应时间。

3. 提高并发能力通过使用连接池和读写分离等技术手段,可以提高系统的并发能力。

FPGA设计的四种常用思想与技巧乒乓操作FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以根据需要重新配置其内部硬件电路。

在FPGA设计中,有许多常用的思想和技巧,其中之一就是乒乓操作。

乒乓操作是指通过交替使用两个资源或状态来实现其中一种功能或优化设计的一种方法。

本文将介绍FPGA设计中的四种常用思想与技巧乒乓操作。

1.数据缓冲乒乓操作:数据缓冲乒乓操作是指在设计中使用两个缓冲区交替存储数据。

一个缓冲区用于接收数据,另一个缓冲区用于处理数据。

当一个缓冲区正在接收数据时,另一个缓冲区可以同时进行数据处理。

这种乒乓操作可以提高数据处理的效率,减少数据处理的延迟。

2.时钟域乒乓操作:时钟域乒乓操作是指在设计中使用两个时钟域交替操作。

一个时钟域用于采样输入数据,另一个时钟域用于处理数据。

这种乒乓操作可以实现不同时钟域之间的数据交换和同步。

例如,可以将输入数据从一个时钟域同步到另一个时钟域,然后再进行处理。

这种乒乓操作可以解决时钟域之间的异步问题,提高设计的可靠性和性能。

3.状态机乒乓操作:状态机乒乓操作是指在设计中使用两个状态机交替执行其中一种功能。

一个状态机用于执行一些任务,另一个状态机用于处理其他任务。

这种乒乓操作可以实现多任务的并行处理。

例如,可以将一个状态机用于处理输入数据,另一个状态机用于处理输出数据。

这种乒乓操作可以提高设计的并行度,加快任务的执行速度。

4.存储器乒乓操作:存储器乒乓操作是指在设计中使用两个存储器交替读写数据。

一个存储器用于读取数据,另一个存储器用于写入数据。

这种乒乓操作可以实现数据的连续读写,提高存储器的访问效率。

例如,可以将一个存储器用于读取输入数据,另一个存储器用于写入输出数据。

这种乒乓操作可以减少存储器的读写延迟,提高数据的传输速度。

综上所述,FPGA设计中的乒乓操作是一种常用的思想和技巧,可以提高设计的效率和性能。

通过数据缓冲乒乓操作、时钟域乒乓操作、状态机乒乓操作和存储器乒乓操作,可以实现数据的并行处理、时钟域的同步、多任务的执行和存储器的高效访问。

verilog乒乓操作的工作原理Verilog乒乓操作的工作原理:Verilog是一种硬件描述语言(HDL),用于描述数字电路。

乒乓操作是Verilog中的一种重要操作,用于实现信号或数据的交换。

乒乓操作可以通过两个变量之间的交换,实现数据传输,并且在硬件电路中具有高效的执行速度。

乒乓操作的工作原理是通过使用一个中间变量来完成变量值的交换。

在Verilog中,我们通常使用临时变量(temp)来实现乒乓操作。

下面是一个乒乓操作的示例代码:```verilogmodule PingPong;reg [7:0] a, b, temp;// 乒乓操作的过程always @(posedge clk) begintemp <= a; // 将变量a的值赋给tempa <= b; // 将变量b的值赋给ab <= temp; // 将temp的值赋给变量b,实现了a和b的值交换endinitial begin// 初始化a和b的值a = 8'b10101010;b = 8'b01010101;#10; // 等待10个时钟周期$display("a的值:%b", a);$display("b的值:%b", b);endendmodule```在上述代码中,我们使用了一个8位的临时变量temp来完成变量a和变量b的交换。

在always块中,当时钟的上升沿到来时,乒乓操作被执行。

首先,我们将变量a的值赋给temp,然后将变量b的值赋给a,最后将temp的值赋给b,实现了a和b的交换。

通过不断重复这个过程,我们可以实现连续的交换操作。

在initial块中,我们对变量a和变量b进行了初始化,并等待了10个时钟周期。

最后,通过$display函数输出了交换后的a和b的值。

乒乓操作是一种非常常用的操作,在数字电路设计中起到了重要的作用。

通过Verilog的语法,我们可以方便地描述和实现乒乓操作,并在硬件电路中实现高效的数据传输。

实时视频采集系统的SDRAM控制器设计0 引言在PAL→VGA的实时视频采集系统中,由于视频数据流的数据量大、实时性要求高。

需要高速大容量的存储器作为图像数据的缓存。

SDRAM作数据缓存不仅具有大容量和高速度的特点,而且在价格和功耗方面也占有很大的优势。

但是SDRAM控制较复杂,需要处理预充、刷新、换行等操作,因此有必要设计SDRAM控制器来完成和SDRAM的接口。

并且为了保证数据流的连续性,实时视频采集系统通常采用通过对两片SDRAM的乒乓操作来完成图像数据的缓存。

针对SDRAM是高速设备,工作频率上限最高可以达到166 MHz,而该系统中前端图像采集模块的像素时钟为27 MHz,后端VGA显示的像素时钟为31.5 MHz。

在此介绍了一种使用1片SDRAM的不同BANK进行乒乓操作,且相对容易实现的SDRAM控制器设计方法。

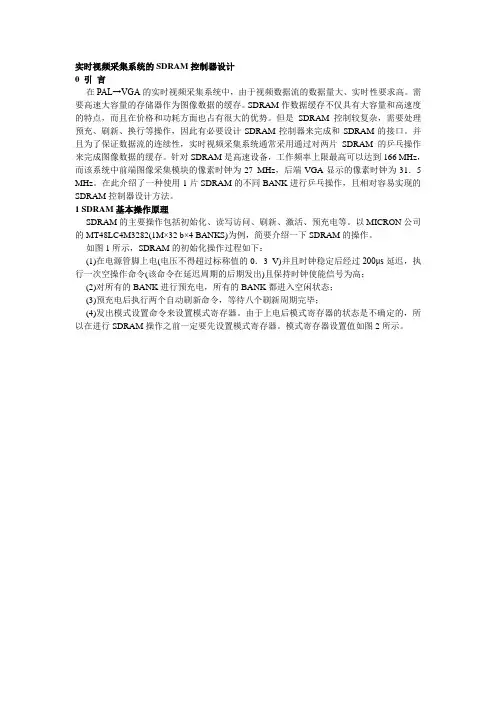

1 SDRAM基本操作原理SDRAM的主要操作包括初始化、读写访问、刷新、激活、预充电等。

以MICRON公司的MT48LC4M3282(1M×32 b×4 BANKS)为例,简要介绍一下SDRAM的操作。

如图1所示,SDRAM的初始化操作过程如下:(1)在电源管脚上电(电压不得超过标称值的0.3 V)并且时钟稳定后经过200μs延迟,执行一次空操作命令(该命令在延迟周期的后期发出)且保持时钟使能信号为高;(2)对所有的BANK进行预充电,所有的BANK都进入空闲状态;(3)预充电后执行两个自动刷新命令,等待八个刷新周期完毕;(4)发出模式设置命令来设置模式寄存器。

由于上电后模式寄存器的状态是不确定的,所以在进行SDRAM操作之前一定要先设置模式寄存器。

模式寄存器设置值如图2所示。

对SDRAM的读写访问先要以激活命令选择具体的BANK和行,地址线BA1/BA0用来选择BANK,A0~A11用来选择所要访问的行;然后发出读或写命令,地址线A0~A7用来选择所要访问的起始列。

基于乒乓操作的异步FIFO设计及VHDL实现乒乓操作是一种常用的同步操作,可以实现数据的交换和缓存。

基于乒乓操作的异步FIFO设计,则是在原有的乒乓操作基础上,加入异步读写功能,实现了先进先出的数据存储。

在设计过程中,我们需要考虑以下几个关键点:1.写入数据的操作:当有新的数据要写入到FIFO中时,首先需要判断FIFO是否已满。

如果已满,则需要等待读取操作后再进行写入;如果未满,则直接将数据写入到空闲位置,并更新写指针。

2.读取数据的操作:当有读取操作时,首先需要判断FIFO是否为空。

如果为空,则需要等待写入操作后再进行读取;如果不为空,则从第一个有效数据开始读取,并将读取完的数据位置清空,并更新读指针。

3.FIFO的容量:FIFO的容量应该根据实际需求进行设置。

当FIFO中的数据量达到容量上限时,写操作将被阻塞,直到有读取操作释放空间。

基于以上设计思路,下面是一个简单的基于乒乓操作的异步FIFO的VHDL实现代码:```vhdllibrary ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity Async_FIFO isgenericWIDTH : integer := 8; -- 数据位宽DEPTH : integer := 16 -- FIFO深度portclk : in std_logic; -- 时钟reset : in std_logic; -- 复位write : in std_logic; -- 写操作使能信号read : in std_logic; -- 读操作使能信号data_in : in std_logic_vector(WIDTH-1 downto 0); -- 输入数据data_out: out std_logic_vector(WIDTH-1 downto 0); -- 输出数据empty : out std_logic; -- FIFO为空标志位full : out std_logic -- FIFO为满标志位end Async_FIFO;architecture behavioral of Async_FIFO istype fifo_type is array (0 to DEPTH-1) ofstd_logic_vector(WIDTH-1 downto 0); -- FIFO存储类型signal fifo : fifo_type; -- FIFO数组signal write_ptr : integer range 0 to DEPTH-1 := 0; -- 写指针signal read_ptr : integer range 0 to DEPTH-1 := 0; -- 读指针signal count : integer range 0 to DEPTH := 0; -- FIFO计数器beginprocess(clk, reset)beginif reset = '1' then--复位write_ptr <= 0;read_ptr <= 0;count <= 0;elsif rising_edge(clk) then--写操作if write = '1' and count < DEPTH thenfifo(write_ptr) <= data_in;write_ptr <= write_ptr + 1;count <= count + 1;end if;--读操作if read = '1' and count > 0 thendata_out <= fifo(read_ptr);fifo(read_ptr) <= (others => '0');read_ptr <= read_ptr + 1;count <= count - 1;end if;end if;end process;empty <= '1' when count = 0 else '0';full <= '1' when count = DEPTH else '0';end behavioral;```上述代码中,首先定义了一个`fifo_type`类型,它是一个包含`DEPTH`个元素的数组,每个元素的大小为`WIDTH`位。

FPGA之乒乓操作1.乒乓操作原理 乒乓操作是⼀个主要⽤于数据流控制的处理技巧,典型的乒乓操作如图所⽰: 外部输⼊数据流通过“输⼊数据选择控制”模块送⼊两个数据缓冲区中,数据缓冲模块可以为任何存储模块,⽐较常⽤的存储单元为双⼝RAM(Dual RAM),SRAM,SDRAM,FIFO等。

在第1个缓冲周期,将输⼊的数据流缓存到“数据缓冲1”模块,在第2个缓冲周期,“输⼊数据选择控制”模块将输⼊的数据流缓存到“数据缓冲2”模块的同时,“输出数据选择控制”模块将“数据缓冲1”模块第⼀个周期缓存的数据流送到“后续处理”,模块进⾏后续的数据处理,在第三个缓冲周期,在“输⼊数据选择控制”模块的再次切换后,输⼊的数据流缓存到“数据缓冲1”模块,与此同时,“输出数据选择控制”模块也做出切换,将“数据缓冲2”模块缓存的第⼆个周期的数据送到“后续处理模块”,如此循环。

这⾥正是利⽤了乒乓操作完成数据的⽆缝缓冲与处理,乒乓操作可以通过“输⼊数据选择控制”和“输出数据选择控制”按节拍,相互配合地进⾏来回切换,将经过缓冲的数据流没有停顿的送到“后续处理模块”。

⽐如将乒乓操作运⽤在液晶显⽰的控制模块上,如图所⽰。

对于外部接⼝传输的图像数据,以⼀帧图像为单位进⾏SDRAM的切换控制,当SDRAM1缓存图像数据时,液晶显⽰的是SDRAM2的数据图像;反之,当SDRAM2缓存图像数据时,液晶显⽰的是SDRAM1的数据图像,如此反复,这样出路的好处在于液晶显⽰图像切换瞬间完成,掩盖了可能⽐较缓慢的图像数据流变换过程。

2.FPGA乒乓操作代码2.1 FPGA设计代码1module pingpang2 (3input clk ,4input rst_n ,5input [7:0] data_in , // 输⼊数据6output reg [7:0] data_out // 输出数据7 );89// ------------------------------------------------------ //10reg [7:0] buffer1 ; // 缓存111reg [7:0] buffer2 ; // 缓存212reg wr_flag ; // 写标志,wr_flag=0,写buffer1,wr_flag=1,写buffer213reg rd_flag ; // 读标志,rd_flag=0,读buffer2,rd_flag=1,读buffer114reg state ; // 状态机,0:写1读2,1:写2读1,状态转移和输出分开编码15// ------------------------------------------------------ //16// 状态转移17always @ (posedge clk or negedge rst_n)18begin19if(rst_n == 1'b0)20begin21 state <= 'b0;22end23else24begin25 state <= !state;26//case(state)27// 1'b0 : state <= 1'b0; // 写1读2->写2读128// 1'b1 : state <= 1'b1; // 写2读1->写1读229// default : state <= 1'b0;30//endcase31end32end33// ------------------------------------------------------ //34// 状态输出35always @ (state)36begin37case(state)381'b0:39begin40 wr_flag = 1'b0; // 写141 rd_flag = 1'b0; // 读242end431'b1:44begin45 wr_flag = 1'b1; // 写246 rd_flag = 1'b1; // 读147end48default:49begin50 wr_flag = 1'b0;51 rd_flag = 1'b0;52end53endcase54end55// ------------------------------------------------------ //56// 写buffer数据57always @ (posedge clk or negedge rst_n)58begin59if(rst_n == 1'b0)60begin61 buffer1 <= 8'b0;62 buffer2 <= 8'b0;63end64else65begin66case(wr_flag)671'b0 : buffer1 <= data_in; // wr_flag = 0,写buffer1 681'b1 : buffer2 <= data_in; // wr_flag = 1,写buffer2 69default :70begin71 buffer1 <= 8'b0;72 buffer2 <= 8'b0;73end74endcase75end76end77// ------------------------------------------------------ //78// 读buffer数据79always @ (posedge clk or negedge rst_n)80begin81if(rst_n == 1'b0)82begin83 data_out <= 8'b0;84end85else86begin87case(rd_flag)881'b0 : data_out <= buffer2; // rd_flag=0,读buffer2 891'b1 : data_out <= buffer1; // rd_flag=1,读buffer1 90default : data_out <= 8'b0;91endcase92end93end94// ------------------------------------------------------ //95endmodule2.2 FPGA仿真代码`timescale 1ns / 1psmodule pingpang_tb();reg clk ;reg rst_n ;reg [7:0] data_in ;wire[7:0] data_out;always #10 clk = ~clk;initialbeginrst_n <= 1'b0 ;clk <= 1'b0 ;#2010;rst_n <= 1'b1 ;endalways @(posedge clk or negedge rst_n)beginif(!rst_n)data_in <= 'd0;elsedata_in <= data_in + 1'b1;endpingpang dut(.clk (clk ),.rst_n (rst_n ), .data_in (data_in ),.data_out (data_out ) );endmodule3.仿真结果。

FPGA与CPLD的区别系统的比较,与大家共享:尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点:①CPLD更适合完成各种算法和组合逻辑,FPGA更适合于完成时序逻辑。

换句话说,FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限而乘积项丰富的结构。

②CPLD的连续式布线结构决定了它的时序延迟是均匀的和可预测的,而FPGA的分段式布线结构决定了其延迟的不可预测性。

③在编程上FPGA比CPLD具有更大的灵活性。

CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FPGA可在逻辑门下编程,而CPLD是在逻辑块下编程。

④FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现。

⑤CPLD比FPGA使用起来更方便。

CPLD的编程采用E2PROM或FASTFLASH技术,无需外部存储器芯片,使用简单。

而FPGA的编程信息需存放在外部存储器上,使用方法复杂。

⑥CPLD的速度比FPGA快,并且具有较大的时间可预测性。

这是由于FPGA是门级编程,并且CLB之间采用分布式互联,而CPLD是逻辑块级编程,并且其逻辑块之间的互联是集总式的。

⑦在编程方式上,CPLD主要是基于E2PROM或FLASH存储器编程,编程次数可达1万次,优点是系统断电时编程信息也不丢失。

CPLD又可分为在编程器上编程和在系统编程两类。

FPGA大部分是基于SRAM编程,编程信息在系统断电时丢失,每次上电时,需从器件外部将编程数据重新写入SRAM中。

其优点是可以编程任意次,可在工作中快速编程,从而实现板级和系统级的动态配置。

⑧CPLD保密性好,FPGA保密性差。

⑨一般情况下,CPLD的功耗要比FPGA大,且集成度越高越明显。

随著复杂可编程逻辑器件(CPLD)密度的提高,数字器件设计人员在进行大型设计时,既灵活又容易,而且产品可以很快进入市场。

乒乓操作的工作原理

乒乓操作,也被称为乒乓纤维传输,是一种在通信系统中实现数据传输的技术。

它的工作原理基于光的物理特性和光纤的传输能力。

乒乓操作主要利用了光波在光纤中传播的特性。

光波在光纤中的传播是通过多次反射的方式进行的。

具体而言,光波从光纤的发送端输入,通过以一定角度斜向入射到光纤内部,然后沿着光纤中心轴传播。

当光波遇到光纤壁上的杂散光时,一部分光波被散射掉,一部分光波则被反射回来。

这些反射的光波再次沿着光纤传播,直至到达接收端。

乒乓操作的关键在于控制光纤中的两个方向的传播模式:正向传播和反向传播。

在乒乓操作中,数据的传输是通过在两个方向之间切换传播模式来实现的。

发送端通过调节切换频率,使光波在正向传播模式和反向传播模式之间来回切换。

当光波处于正向传播模式时,它会沿着光纤的正向方向传播,直到到达接收端。

然后,当光波到达接收端后,乒乓操作会切换为反向传播模式,将光波沿着光纤的反向方向传播回发送端。

这样,数据就完成了在光纤中的传输过程。

乒乓操作具有许多优点。

首先,它可以实现全双工通信,即同时进行双向数据传输。

其次,乒乓操作在光纤中的传输损耗相对较小,可以传输大量的数据。

此外,光信号在光纤中的传输速度较快,可以实现高速数据传输。

最后,乒乓操作还具有较高的安全性,因为光信号在光纤中传播,很难被未经授权的人截获。

综上所述,乒乓操作是一种基于光波在光纤中传播的技术,通过在正向传播模式和反向传播模式之间切换,实现了数据在光纤中的传输。

其优势包括全双工通信、低损耗、高速传输和高安全性等。

乒乓操作的工作原理乒乓球是一项富有趣味和激烈竞争的运动,它要求运动员在有限的空间里使用乒乓球和乒乓球拍,进行高速、精准的运动。

在这项运动中,乒乓球拍是一个非常重要的工具,它的设计和使用方式能够直接影响到运动员的技术水平和比赛成绩。

乒乓球拍不仅要求具有良好的手感和控制性能,还要求具有一定的弹性和速度。

下面,我们将从乒乓球拍的工作原理入手,为大家详细解析关于乒乓球操作的工作原理。

乒乓球拍的工作原理主要包括材料选择、拍面设计和拍柄结构。

在打乒乓球时,运动员需要通过乒乓球拍将自己的能量传递给乒乓球,使之快速、准确地飞向对方球场。

乒乓球拍的材料要求具有一定的弹性和韧性,能够提供足够的力量来打击乒乓球,并且能够让球在拍面上产生适当的旋转和飞行轨迹。

拍面的设计也需要具有一定的粗糙度和摩擦力,以便能够更好地控制乒乓球的飞行轨迹和旋转。

而拍柄则需要具有一定的舒适性和握持性,以便运动员能够更好地控制乒乓球拍的运动方向和力度。

乒乓球拍的材料选择是决定其工作原理的重要因素之一。

目前,乒乓球拍的主要材料包括木材、橡胶和碳纤维等。

在这些材料中,木材是乒乓球拍的主要构成材料,它通常用于制作拍面和拍柄。

木材具有良好的弹性和韧性,可以提供足够的力量来打击乒乓球,并且能够在球拍挥动时提供适当的支撑和稳定性。

木材还能够帮助球拍在和乒乓球接触时产生适当的反弹和旋转,从而使得球拍可以更好地控制乒乓球的飞行轨迹和旋转。

而橡胶是乒乓球拍拍面的主要材料,它的摩擦力和粘附性能能够帮助运动员更好地控制乒乓球的旋转和飞行轨迹。

碳纤维等新型材料的应用也使得乒乓球拍在提升弹性和速度的不失控制性能和手感,使得运动员既能够保持球拍的控制性,又能够提高球拍的速度和回弹力度,从而更好地完成各种技术动作和战术打法。

乒乓球拍的拍面设计也是其工作原理的重要组成部分。

乒乓球拍的拍面设计需要具有一定的摩擦力和粗糙度,以便能够更好地控制乒乓球的飞行轨迹和旋转。

在拍面的设计中,通常会采用不同材质和纹路的橡胶来调整球拍的摩擦力和旋转性能。

唉。

写好testbench后一定要将顶层模块写进,不然怎么会有结果呢!!其实乒乓操作用面积换速度。

具体如何应用于实际中,不知道,只是知道怎么回事。

比如串并转换中,必须先对串入数据进行处理,然后将其送出。

这在通讯中应该会用到吧。

如果处理发现错误则丢弃数据,那么在处理数据的时候就不能够允许数据更改,这样就限制了速度。

(当然也可以用寄存器将结果先寄存处理)。

不过写这个对Verilog又有了进一步的了解:

1.模块化!写程序前要想清楚如何划分模块,模块之间的接口。

这样方便仿真出错时候查错误,而且会使模块内部逻辑关系变简单。

2.非阻塞赋值是beginend执行完后就改变数据,因此,对于某些信号我们可以根据触发条件进行选择。

如模块2选一输入中的oden 1和oden2的选择

module sp_top(clk,nrst,serial_in,data_out,serial_en1,serial_en2,oden1,oden2);

input clk,nrst,serial_in;

output[3:0] data_out;

output serial_en1,serial_en2;

output oden1,oden2;

wire oden1,oden2;

wire serial_en1,serial_en2;

wire[3:0] parallel_out1,parallel_out2;

sp_imux21 Ssp_imux21(nrst,oden1,oden2,serial_en1,serial_en2);

sp_buf Ssp_buf1(serial_en1,clk,nrst,serial_in,oden1,parallel_out1);

sp_buf Ssp_buf2(serial_en2,clk,nrst,serial_in,oden2,parallel_out2);

sp_omux21 Ssp_omux21(clk,oden1,oden2,nrst,parallel_out1,parallel_out2,data_out);

endmodule

//sp_mux41:serial to parallel data_buf choose

module sp_imux21(nrst,oden1,oden2,serial_en1,serial_en2);

input nrst;

input oden1,oden2;

output serial_en1,serial_en2;

reg serial_en1,serial_en2;

always@(posedge oden1 or posedge oden2 or negedgenrst)

if(!nrst) begin serial_en1=1'b1;serial_en2=1'b0;end

else if(oden1) begin serial_en1<=1'b0;serial_en2<=1'b1;end

else if(oden2) begin serial_en1<=1'b1;serial_en2<=1'b0;end

// else serial_en<=serial_en;

endmodule

//sp_buf:serial to parallel data input buffer

module sp_buf(iden,clk,nrst,serial_in,oden,parallel_out);

input iden;//data input enable

input clk,nrst;

input serial_in;

output oden;//output enable

output[3:0] parallel_out;

reg oden;

reg[1:0] count;

reg [3:0] parallel_out;

reg [3:0] inbuf_r;

always@(posedge clk or negedgenrst)

begin

if(!nrst) begin oden<=1'b0;count<=1'b0;inbuf_r=4'dz;end

else if(iden)

begin

inbuf_r<={inbuf_r[2:0],serial_in};

count<=count+1'b1;

if(count==2'd3) oden<=1'b1;

else oden<=1'b0;

end

else begin oden<=1'b0;end

end

always@(posedge oden or negedgenrst)

begin

if(!nrst) parallel_out<=4'dz;

else if(oden)

parallel_out<=inbuf_r;

// else parallel_out<=4'dz;

end

endmodule

//sp_omux21:serial input and parallel output output mux

module sp_omux21(clk,oden1,oden2,nrst,parallel_in1,parallel_in2,data_out); input clk,oden1,oden2,nrst;

input[3:0] parallel_in1,parallel_in2;

output[3:0] data_out;

reg[3:0] data_out;

always@(posedge clk or negedgenrst)

begin

if(!nrst) data_out<=4'dz;

else if(oden1) data_out<=parallel_in1;

else if(oden2) data_out<=parallel_in2;

end

endmodule

`timescale 1ns/1ns

module sp_tb;

reg clk,nrst,serial_in;

wire [3:0] data_out;

wire den1,den2;

wire serial_en1,serial_en2;

reg[28:0] serial_in_buf;

initial

begin

clk=1'b0;

nrst=1'b0;

serial_in_buf=28'b1110_0100_1010_1110_0101_1001_0011;

#2 nrst=1'b1;

#5 nrst=1'b0;

#10 nrst=1'b1;

end

always #5 clk<=~clk;

always@(posedge clk or negedgenrst)

begin

if(!nrst) begin

serial_in=1'bz;

serial_in_buf=28'b1110_0100_1010_1110_0101_1001_0011;

end

else

begin

serial_in=serial_in_buf[27];

serial_in_buf=(serial_in_buf<<1);

end

end

sp_top Ssp_top(clk,nrst,serial_in,data_out,serial_en1,serial_en2,den1,den2); endmodule。