一种实用的峰值保持电路

- 格式:pdf

- 大小:89.30 KB

- 文档页数:2

简单峰值保持电路简单峰值保持电路是一种常用的电子电路,用于保持输入信号的峰值,并将保持后的信号输出。

它可以应用于各种领域,例如通信系统、音频处理、测量仪器等。

峰值保持电路的工作原理是在输入信号中检测到峰值,并将其存储在一个电容器中。

当检测到下一个峰值时,电容器的电压被更新为新的峰值,并且保持这个峰值直到下一个峰值出现。

这种方式可以有效地保持输入信号的峰值,而不受信号变化的影响。

简单峰值保持电路的基本结构包括一个运算放大器、一个二极管和一个电容器。

运算放大器的作用是放大输入信号,并将其传递给二极管。

二极管的正极连接到电容器的一端,负极连接到运算放大器的输出端。

当输入信号的峰值大于电容器的电压时,二极管导通,将新的峰值电压存储在电容器中。

当输入信号的峰值小于电容器的电压时,二极管截断,电容器的电压保持不变。

这样,电容器的电压就始终保持着输入信号的峰值。

在实际应用中,简单峰值保持电路可以用于音频信号的保持和采样。

例如,在音频处理中,可以使用峰值保持电路来检测音频信号的峰值,以控制音量的增益。

另外,在测量仪器中,峰值保持电路可以用于检测信号的峰值,并将其转换为数字信号进行处理和显示。

除了简单峰值保持电路,还有一些改进型的峰值保持电路,例如全波峰值保持电路和样保持电路。

全波峰值保持电路可以检测输入信号的正、负半周的峰值,并将其保持。

样保持电路可以在某个时刻对输入信号进行采样,并将采样值保持在一段时间内,以便后续处理。

简单峰值保持电路是一种常用的电子电路,可以有效地保持输入信号的峰值。

它在各种领域都有广泛的应用,如通信系统、音频处理、测量仪器等。

通过合理设计和调整电路参数,可以实现不同的峰值保持功能,满足不同应用的需求。

第27卷 第2期核电子学与探测技术Vol.27 No.2 2007年 3月Nuclear Elect ronics &Detection TechnologyMarch 2007 一种适用于高速窄脉冲的峰值保持电路彭 宇1,2,苏 弘1,董成富1,李 勇1,2,李素琴1,2,李小刚1,马晓莉1,千奕1,2(1.中国科学院近代物理研究所,兰州730000;2.中国科学院研究生院,北京100049)摘要:介绍一种适用于高速窄脉冲的峰值保持电路,该电路输入信号的幅度≥50mV 、前沿≤3ns 、脉宽≤15ns 、频率≥20M Hz 、增益为3,峰展宽时间可调(0.4~5μs )。

该电路结构简单,可靠性好。

关键词:速;窄脉冲;峰展宽;电路中图分类号: TN78 文献标识码: A 文章编号: 025820934(2007)022*******收稿日期:2005212221作者简介:彭宇(1980—),男,贵州人,博士 该电路主要功能是对前端放大器的输出信号进行峰展宽或称峰值保持,以便后续电路采样,进而进行数据处理。

该电路是一种通用型峰展宽电路,它也适用于其他信号特别是高速窄脉冲信号的峰展宽,从而为高速窄脉冲信号的峰值测量提供了一种方法与手段。

该电路可以接受脉宽≤15ns ,前沿≤3ns ,频率≥20M Hz ,幅度≥50mV 的输入信号。

与一般的的峰值保持电路相比,该电路具有较高的灵敏度,频带宽,反应速度快,小信号响应好的特点。

1 电路基本结构[1]电路在结构上包括模拟部分和数字部分,模拟部分完成对信号的积分保持,而数字部分完成对输入信号获取和积分信号泻放的逻辑控制。

其原理框图如图1所示。

输入信号分成两路,一路通过模拟开关进入积分电路,一路经过高速比较器和逻辑电路产生控制逻辑,来控制模拟开关以便完成对输入信号的获取和积分信号的泻放,最后,通过一级放大器输出驱动后续获取电路。

2 电路原理分析2.1 一般峰值保持电路存在的问题图1 电路结构框图图2为一般的峰值保持电路。

史上最实用较深刻的峰值检测电路实例与分析峰值检测电路是一种广泛应用于信号处理系统中的电路,用来检测信号中的峰值或最大值。

它可以应用于多种应用领域,例如音频处理、通信系统和图像处理等。

本文将介绍一个实用较深刻的峰值检测电路实例,并对其进行分析。

峰值检测电路的主要功能是检测输入信号的峰值,并将其保持在输出端,以便进一步处理或显示。

典型的峰值检测电路由一个整流电路和一个低通滤波器组成。

整流电路将输入信号的负半周转换为正半周,并得到一个最大值。

而低通滤波器则用于平滑输出信号,以避免过高的响应速度。

在这个实例中,我们将介绍一种基于操作放大器的峰值检测电路。

它可以检测输入信号的峰值,并将输出保持在峰值的水平上。

以下是该电路的原理图:整个电路可以分为四个关键部分:输入缩放电阻(R1和R2)、操作放大器(A1和A2)、整流电路(D1和D2)和输出低通滤波器(R3、C1和A3)。

首先,输入缩放电阻R1和R2用于调整输入信号的幅度。

这是为了适应不同幅度的信号,并将其缩放到操作放大器的工作范围内。

操作放大器A1和A2构成了一个峰值检测器的核心部分。

A1用于检测输入信号的峰值,并通过负反馈使得A2输出与A1输入相等,以保持峰值。

通过这种方式,我们可以将输入信号的峰值保持在电路的输出端。

整流电路D1和D2用于将输入信号的负半周转换为正半周。

它们通过将负半周的信号与零电平比较,并选择较大的值作为输出。

这样,我们可以在整个波形周期内得到输入信号的最大值。

最后,输出低通滤波器R3、C1和A3用于平滑输出信号,并避免过高的响应速度。

通过选择合适的滤波器参数,可以使得输出信号更加平滑,并适应不同的应用需求。

以上是该峰值检测电路的分析。

它能够实时检测输入信号的峰值,并将其保持在输出端。

这对于很多应用领域都是非常实用的,例如音频处理中的音量调节、通信系统中的信号强度检测和图像处理中的边缘检测等。

总结起来,峰值检测电路是一种实用且较深刻的电路设计。

简单峰值保持电路简单峰值保持电路是一种常见的电路设计,用于将输入信号的峰值保持在一个固定的电平上。

这种电路常用于信号采集、测量和控制系统中,可以有效地处理高频信号和变化较快的信号。

简单峰值保持电路由一个运算放大器、一个电容和若干个电阻组成。

其基本原理是通过运算放大器将输入信号进行放大,并将放大后的信号通过电容器进行储存。

当输入信号的幅值变化时,电容器会根据输入信号的峰值自动调整电压,使输出信号始终保持在输入信号的峰值水平上。

在简单峰值保持电路中,运算放大器起到了放大和缓冲的作用。

它将输入信号放大后,输出到电容器上,同时还可以根据需要进行增益调整。

电容器则起到了储存信号的作用,保持输入信号的峰值水平。

而电阻则用于限制电流流过电容器,以保证电路的稳定工作。

简单峰值保持电路的工作过程如下:首先,当输入信号的幅值变化时,运算放大器会将其放大,并通过电容器将放大后的信号储存起来。

然后,电容器会根据输入信号的峰值自动调整电压,使输出信号始终保持在输入信号的峰值水平上。

当输入信号的幅值变化较大时,电容器会迅速调整电压,以保持输出信号的稳定性。

而当输入信号的幅值变化较小时,电容器则会缓慢调整电压,以保持输出信号的平滑性。

简单峰值保持电路具有以下优点:首先,它可以有效地保持输入信号的峰值水平,使得信号处理更加准确和可靠。

其次,它可以适应高频信号和变化较快的信号,具有较高的带宽和响应速度。

此外,它的电路结构简单,成本较低,易于实现和维护。

然而,简单峰值保持电路也存在一些不足之处。

首先,由于电容器的存在,该电路对直流信号的处理较差,只适用于交流信号的处理。

其次,由于运算放大器的放大和缓冲作用,该电路的功耗较高,对电池供电的系统不太适用。

此外,该电路在高温和高湿度环境下容易受到影响,对工作环境有一定的要求。

简单峰值保持电路是一种常见且实用的电路设计,用于保持输入信号的峰值水平。

它通过运算放大器、电容和电阻的协同作用,使得输出信号始终保持在输入信号的峰值水平上。

史上最实用较深刻的峰值检测电路实例与分析一、前言峰值检测电路(PKD,Peak Detector)的作用是对输入信号的峰值进行提取,产生输出V o = Vpeak,为了实现这样的目标,电路输出值会一直保持,直到一个新的更大的峰值出现或电路复位。

峰值检测电路在AGC(自动增益控制)电路和传感器最值求取电路中广泛应用,自己平时一般作为程控增益放大器倍数选择的判断依据。

有的同学喜欢用AD637等有效值芯片作为程控增益放大器的判据,主要是因为集成的方便,但个人认为是不合理的,因为有效值和信号的正负峰值并没有必然联系;其次,实际应用中这类芯片太贵了。

当然,像电子设计竞赛是可以的,因为测试信号总是正弦波,方波等。

(本文参加了TI公司的博文比赛,觉得还行的话,希望大家帮顶一下、回复一个,谢谢大家,我会更努力的:-)二、峰值检测电路原理顾名思义,峰值检测器(PKD,Peak Detector)(本文默认以正峰值检测为例)就是要对信号的峰值进行采集并保持。

其效果如下如(MS画图工具绘制):根据这样的要求,我们可以用一个二极管和电容器组成最简单的峰值检测器。

如下图(TINA TI 7.0绘制):这时候我们可以选择用面包板搭一个电路,接上信号源示波器观察结果,但在这之前利用仿真软件TINA TI进行简单验证会节省很多时间。

通过简单仿真(输入正弦信号5kHz,2Vpp),我们发现仅仅一个二极管和电容器组成的峰值检测器可以工作,但性能并不是很理想,对1nF的电容器,100ms后达到稳定的峰值,误差达10%。

而且,由于没有输入输出的缓冲,在实际应用中,电容器中的电荷会被其他部分电路负载消耗,造成峰值检测器无法保持信号峰值电压。

既然要改进,首先要分析不足。

上图检测的误差主要来自与二极管的正向导通电压降,因此我们可以用模电书上说的“超级二极管”代替简单二极管(TINA TI 7.0绘制):从仿真结果来看,同等测试条件下,检测误差大大减小。

峰值保持电路AD8330正向输出端信号为窄脉冲,目前常用的AD 采样电路难以捕捉到窄脉冲的幅值,所以需要采用峰值保持电路,该电路的作用是获取压控放大电路输出信号的峰值并保持一段时间,从而使后续电路有足够的时间将其转换为数字信号,用于计算目标方位。

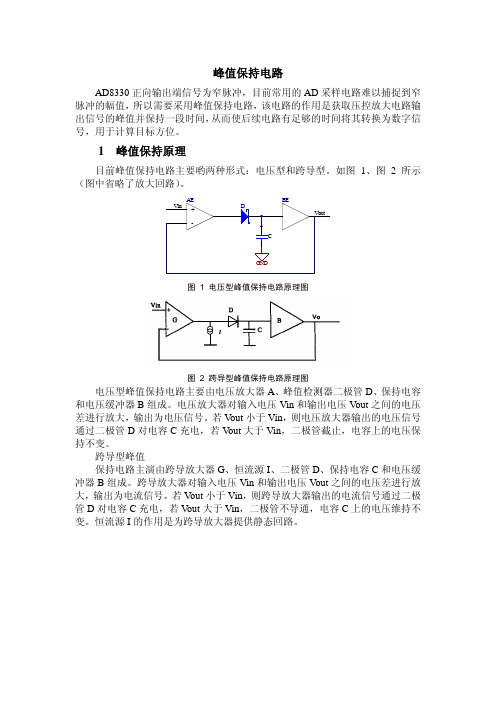

1 峰值保持原理目前峰值保持电路主要哟两种形式:电压型和跨导型。

如图 1、图 2 所示(图中省略了放大回路)。

图 1 电压型峰值保持电路原理图图 2 跨导型峰值保持电路原理图电压型峰值保持电路主要由电压放大器A 、峰值检测器二极管D 、保持电容和电压缓冲器B 组成。

电压放大器对输入电压Vin 和输出电压V out 之间的电压差进行放大,输出为电压信号。

若V out 小于Vin ,则电压放大器输出的电压信号通过二极管D 对电容C 充电,若V out 大于Vin ,二极管截止,电容上的电压保持不变。

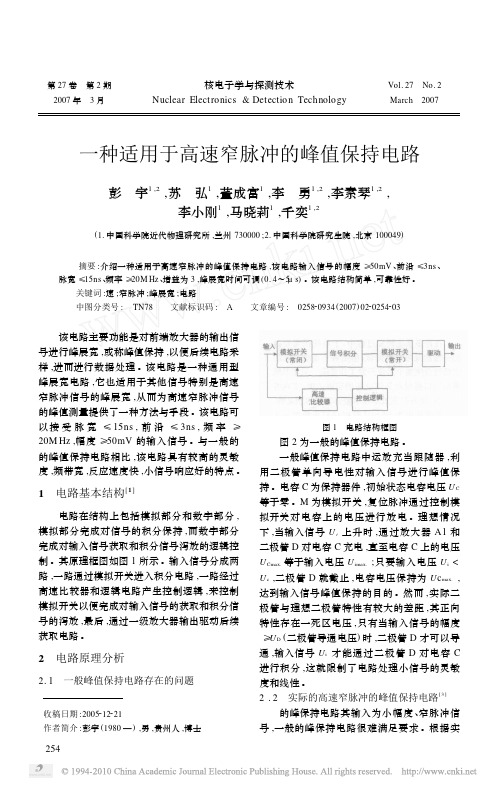

跨导型峰值保持电路主演由跨导放大器G 、恒流源I 、二极管D 、保持电容C 和电压缓冲器B 组成。

跨导放大器对输入电压Vin 和输出电压V out 之间的电压差进行放大,输出为电流信号。

若V out 小于Vin ,则跨导放大器输出的电流信号通过二极管D 对电容C 充电,若V out 大于Vin ,二极管不导通,电容C 上的电压维持不变。

恒流源I 的作用是为跨导放大器提供静态回路。

图3 电压型与跨导型波形比较传统的峰值保持电路是电压型的,电路原理简单,但积分非线性大,响应速度慢,很难处理高速脉冲信号。

目前也有人在这方面进行不断的研究希望能够解决这个难题,又不少的人已经研究出采用高速电压放大器构成的峰值保持电路,使用逻辑电路控制保持电容C的充放电过程,并且对峰值保持信号进行了展宽,为峰值保持电路的实际提供了新的思路,但没有解决保持误差的问题。

跨导型峰值保持电路具有响应速度快、动态范围大和误差小等优点,但结构比较复杂。

PKD01、AD585和AD783 是AD公司的三款高速、高精度采样跟踪保持放大器(SHA),它们内部均采用跨导型峰值保持电路结构。

第29卷 第2期核电子学与探测技术

Vol.29 No.2 2009年 3月

Nuclear Elect ronics &Detection Technology

Mar. 2009

一种实用的峰值保持电路

胡创业,席宏强

(南华大学核科学技术学院,衡阳 421001)

摘要:介绍了一种以采样/保持器L F398芯片为主要器件的峰值保持电路。

该电路具有结构简单、

调试方便、性能优良等优点,可广泛应用于各种脉冲分析系统。

关键词:峰值提取保持;脉冲幅度分析器

中图分类号: TN78 文献标识码: A 文章编号: 025820934(2009)022*******

收稿日期:2008210208

作者简介:胡创业(1979-),男,南华大学核科学技术学院讲师,主要从事核电子学与探测技术研究。

峰值保持电路是核物理实验中的重要线路

单元[1]。

峰值保持电路实际包含峰值提取和峰值保持两种电路。

在核物理通过脉冲幅度鉴别粒子类型实验中,主线性放大器输出模拟信号的峰值是代表着带电粒子在核辐射探测器中所沉积的能量,根据模拟信号峰值幅度的大小就可以鉴别粒子的类型;因此模拟信号峰值的提取就显得尤为重要,否则该方法就无法用来鉴别粒子类型。

峰值保持电路是在峰值提取电路设计基础上提出的,模拟峰值信号要转换成数字信号需要通过A/D 转换电路,它需要一定的时间来完成转换,在转换期间要保证模拟峰值信号的稳定,因此模拟信号峰值的保持同样重要。

鉴于此,峰值的提取/保持电路便应运而生。

峰值保持电路在其它测量控制方面用途也非常广泛,如:最大冲击力、振动过程中的最大幅值、共振最大强度以及测试工业过程中的最高温度、最大流量、最大压力等。

峰值保持电路是多道脉冲幅度分析器的重要核心电路之一。

在N IM 插件式的多道脉冲幅度分析器中多用三极管和MOS 管等分立器件来搭建,该电路具有结构复杂和调试麻烦等

特点;而在用于野外测量的便携式智能型多道脉冲幅度分析器设计中,需要整体电路结构简单实用、集成化程度高和调试方便。

传统的N IM 插件式峰值保持电路必须整合,本文就是

在此基础上提出一种简单实用的峰值保持电路设计。

峰值保持电路通常分为电压型的和跨导型[2]两种,本文提出的是建立在电压型的设计基础上,提出用采样/保持器L F398芯片配合简单外围电路来达到设计要求。

1 多道能谱仪的峰值保持电路

峰值保持电路探测核脉冲幅度信号并在脉冲峰值时刻通知保持峰值,同时向单片机提出中断申请信号,使单片机响应中断启动A/D 转换;转换结束后单片机使采样保持器复原为采样状况,实现系统的逻辑控制。

峰值保持电路原理图如图1所示。

U4是芯片L F398,它是美国国家半导体

公司研制的集成采样保持器。

它只需外接一个保持电容就能完成采样保持功能,其采样保持控制端可直接接于T TL ,CMOS 逻辑电平。

U1和U2是比较器L M311,U3是D 触发器74L S74,U5A 是与门74L S08。

放大后的脉冲

核信号一路输入到下阈比较器,另一路接输入到L F398。

当核信号大于下阈时,比较器U1输出高电平,得到上升沿,上升沿再触发U3A ,

9

73

图1 峰值保持电路原理图

它的Q 端输出高电平和U3B 的Q 非端相与得

到高电平,去控制L F398的采样控制端进入采样状态。

当L F398的输出端信号幅度比输入端大时,即到达峰值时,比较器U2出高电平,得到上升沿,上升沿再触发U3B ,它的Q 非端输出低电平,U5A 输出变为低电平,L F398进入保持状态。

U3B 的Q 非端输出的下跳沿作为单片机的中断信号,当A/D 转换结束后,单片输出放电和清零CL R 信号使采样保持器复原。

电路波形见图2。

2 结束语

本文介绍的用集成采样保持芯片L F398

设计的采样保持电路,电路结构简单,集成化程度高,成本低,调试方便;经设计的多道脉冲幅度分析器整体测试性能可靠,达到了设计要求,为开发便携式多道脉冲幅度分析器提供了简单适用模块,已用于开发研究工作,达到预期目的。

图2 峰值保持电路波形

参考文献:

[1]孟烈.几种峰值屏宽器.核电子学与探测技术[J ].

1986,6(1):63265.

[2]陈勇,李延国,吴枚.新型高性能脉冲峰值保持电路

[J ].核电子学与探测技术,1997,17(4):2412247.[3]Buckens PF ,Veatch MS.A high performance peak 2

detect &hold circuit for pulse height analysis [J ].IEEE T rans Nucl Sci ,1992,NS 39(4):7532757.

A kind of Practical Pulse Peak H old Circuit

HU Chuang 2ye ,XI Hong 2qiang

(School of Nuclear Science And Technology ,University of South China ,hengyang ,421001)

Abstract :A kind of peak 2hold circuit is introduced in t his paper ,whose main component is sampling /holder L F398chips.The circuit has a simple structure ,easy to debug ,performance advantages ,which can be widely used in a variety of pulse analysis system.K ey w ords :peak 2detect &hold circuit ,Pulse amplit ude analyzer

83。