微机原理与接口技术习题答案5章(供参考)

- 格式:doc

- 大小:9.42 MB

- 文档页数:8

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

判断题1.EPROM是指可擦除可编程随机读写存储器。

2.在查询方式下输入输出时,在I/O接口中设有状态寄存器,通过它来确定I/O设备是否准备好。

输入时,准备好表示已满;输出时,准备好表示已空。

3.无条件式的I/O是按先读状态口,再读数据口的顺序传送数据的。

4.I/O数据缓冲器主要用于协调CPU与外设在速度上的差异。

5.查询式输入输出是按先读状态端口,后读/写数据端口的顺序传送数据的。

6.连接CPU和外设的接口电路中必须要有状态端口。

7.总线是专门用于完成数据传送的一组信号线。

8.I/O接口的基本功能之一是完成数据的缓冲。

9.要实现微机与慢速外设间的数据传送,只能利用查询方式完成。

1) Y 2 ) Y3) Y4) Y 5) Y6) X 7) X 8)Y9) X1.单片8259A最多可接8个中断源。

2.在可屏蔽中断的嵌套原则中,不允许低级中断打断高级中断,但允许同级中断相互打断。

3.同一片8259的8个中断源的中断向量在中断向量表中可以不连续存放。

(不要求)4.利用8259A对外中断进行管理时,只能管理8个中断源。

5.在中断接口电路中,由中断请求寄存器来保存外设的中断请求信号。

6.8259A送给CPU的中断请求信号是通过INT发出的。

1Y 2X 3X 4X 5Y 6Y填空题1、在微机系统中,端口编址方式一般有___________和___________两种方式。

2、微机系统与外设间的信息交换方式有————、————、————和————.3.用2K×8的SRAM芯片组成32K×16的存储器,共需SRAM芯片()片。

4.为保证动态RAM中的内容不消失,需要进行( ) 操作。

5.构成64K*8的存储系统,需8K*1的芯片( )片。

1、统一编址,独立编址2、无条件,查询,中断,DMA3、324、定时刷新5、646、8086和8088的地址总线有()根,能寻址()MB的存储器空间。

7.8086CPU从偶地址中按字节读时,存储器数据进入数据总线的( ) ;从奇地址按字节读时,进入数据总线的( )。

第二章 8086 体系结构与80x86CPU1.8086CPU 由哪两部份构成?它们的主要功能是什么?答:8086CPU 由两部份组成:指令执行部件<EU,Execution Unit>和总线接口部件<BIU,Bus Interface Unit>。

指令执行部件〔EU 主要由算术逻辑运算单元<ALU>、标志寄存器F R、通用寄存器组和E U 控制器等4个部件组成,其主要功能是执行指令。

总线接口部件<BIU>主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或者I/O 端口读取操作数参加E U 运算或者存放运算结果等。

2.8086CPU 预取指令队列有什么好处? 8086CPU 内部的并行操作体现在哪里?答: 8086CPU 的预取指令队列由6个字节组成,按照8086CPU 的设计要求, 指令执行部件〔EU 在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在C PU 内部,EU 从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU 内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086 系统中物理地址的形成过程。

8086 系统中的物理地址最多有多少个?逻辑地址呢?答: 8086 系统中的物理地址是由20 根地址总线形成的。

8086 系统采用分段并附以地址偏移量办法形成20 位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部份构成,都是16 位二进制数。

通过一个20 位的地址加法器将这两个地址相加形成物理地址。

具体做法是16 位的段基址左移4位<相当于在段基址最低位后添4个"0">,然后与偏移地址相加获得物理地址。

5.10为什么输人接口的数据缓冲寄存器必须有三态输出功能,而输出接口却不需要?解:输人接口的数据缓冲寄存器的谕出端是直接接在数据总线上的,如果数据寄存器没有三态输出功能,则无论数据寄存器被寻中还是未被寻中,其数据都会被送上数据总线,若此时总线上真正要传送的数据与该输人缓存器的内容不一致时,就会发生总线冲突。

所以输人接口的数据缓冲寄存器必须有三态输出功能,以便接口未被寻中时,其输出端处于高阻态而与总线隔离。

对于输出接口来说,其输人端与数据总线相连,而输出端与外设相连,因此其输出不影响总线状态;并且外设一般只与一个输出数据缓存器相连,所以输出接口的数据缓存器无需三态输出功能。

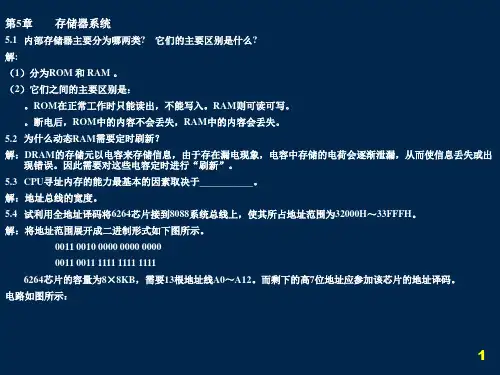

5.11已知PC 机系统中某接口板的I/O 端口译码电路如图5.4所示,试分析出各I/O 端 口和I/O 芯片的端口地址或地址范围。

解:74LS138使能信号12B G G 、的逻辑表达式为:19G A =27654B G A A A A = 即仅当9754A A A A = 11111时,使能信号1G = 1, 2B G = 0有效。

此时,若328A A A = 000, 0Y =0; 328A A A =001, 1Y =0; 328A A A =111, 7Y = 0;所以,各I/O 芯片的地址范围为: I/O 芯片1:1111110000B —11111100113B 即3F0H 一3F3H;I/O 芯片2: l011110100B--1011110111.即2F4H 一2F7H;I/O 芯片3:1111111100B 一11111111113,即3FCH 一3FFH0Y 译出的地址范围2F0H~2F3H 再经一级74LS139译码器对1A 和0A 进行二次译码。

分 别得到4个读端口和4个写端口。

各I/O 端口的地址为:输出口1和输人口1为2F0H ;输出口2和输入口2为2F1H;输出门3和输入口3为2F2H;输出口4和输入口4为2F3H5.12已知PC.机系统中某接口板的板地址译码电路如图5.5所示。

第1章习题答案1.答:计算机硬件的基本组成部分有:运算器、控制器、存储器、输入设备和输出设备五大组成部分;运算器功能:完成各种算术运算或逻辑运算;控制器功能:发出各种控制信息,使计算机各部件协调工作;存储器功能:存储程序和数据;输入设备:将程序和数据输入的部件;输出设备:将结果数据输出的部件。

2.答:以微型计算机为核心,配以鼠标、键盘等外围设备、电源、接口电路,以及控制计算机工作的软件构成微型计算机系统。

3.答:主板与外部设备之间的数据传输必须通过系统总线,所以系统总线包含的信号线必须满足下列各种输入/输出操作的需要:①访问分布于主板之外的存储器;②访问I/O接口;③适应外部中断方式;④适应存储器直接与外部设备交换信息。

总线控制逻辑的任务就是产生和接受这些操作所需要的信号。

4.答:计算机有运算器、控制器、存储器、输入设备和输出设备五大部分组成,计算机内部采用二进制数据的格式表示数据和指令。

程序将事先保存在内存储器中,计算机在工作时,不需要操作人员干预,自动逐条取出指令并执行。

5.答:CPU首先执行主板上BIOS中的自检程序;执行引导装入程序,依次搜寻硬盘、光盘等;读出引导记录,装入引导程序;由引导程序将操作系统装入内存;执行操作系统。

6.答:BIOS是Basic Input Output System的缩写,指的是基本输入输出系统"。

它是一组固化到计算机ROM芯片上的程序,保存着计算机最重要的基本输入输出的程序、系统设置信息、开机后自检程序和系统自启动程序。

7.答:略。

2第3章习题答案1.(1)答:物理地址:物理地址(PA)是20位无符号二进制数,是CPU访问存储器的实际地址。

每个存储单元对应一个物理地址。

8086存储空间的物理地址范围是:00000H~FFFFFH。

逻辑地址:采用分段结构的存储器中,把通过段地址和偏移地址来表示的存储单元的地址称为逻辑地址,记为:段地址:偏移地址。

段地址:8086规定各逻辑段从节的整数边界开始,即段首地址二进制值的低4位是0000,把段首地址的高16位称为段基址或段地址。

微机原理及接⼝技术习题答案第⼀章习题及答案1. 微处理器内部包含哪三⼤部分?解:运算器、控制器和寄存器组。

2. 完成下列数制的转换①解:②0.11B=()D 解:0.11B=0.75D 。

③211.25=( )B =( )H 解:④10111.0101B=( )H=( )BCD解:10111.0101B=17.5H=23.3125D=(0010 0011.0011 0001 0010 0101)BCD3. 已知X=+1011010B ,Y =–0011011B ,设机器数为8位,分别写出X 、Y 的原码、反码和补码。

解:4. 已知X 的真值为32,Y 的真值为–19,求[]?Y X =+补解:[]00001101B X Y +=补5. 已知X=51,Y=–86,⽤补码完成下列运算,并判断是否产⽣溢出(设字长为8位)。

① X +Y ② X -Y ③ –X +Y ④ –X -Y 解:67C C 0⊕=,所以未产⽣溢出。

676. 若使与门的输出端输出⾼电平,则各输⼊端的状态是什么?解:各输⼊端为⾼电平。

7. 若使与⾮门的输出端输出低电平,则各输⼊端的状态是什么?解:各输⼊端为⾼电平。

8. 如果74LS138译码器的Y 4端输出低电平,则C 、B 、A 三个输⼊端的状态分别是什么?解:C 、B 、A 三个输⼊端的状态分别是‘1’,‘0’,‘0’。

第⼆章习题及答案1. 8086/8088CPU 由哪两⼤功能部分所组成?简述它们的主要功能? 解:8086/8088CPU 由EU 和BIU 两⼤功能部分组成。

执⾏单元EU主要完成指令的译码和执⾏。

执⾏单元通过EU控制电路从BIU中取出指令,经过指令译码形成各种定时控制信号,向EU内各功能部件发出相应的控制命令,以完成指令所规定的操作。

总线接⼝单元BIU是8086/8088同外部联系的接⼝。

它负责所有涉及外部总线的操作,包括取指令、读操作数、写操作数、地址转换和总线控制等。

微机原理与接口技术习题参考答案第一章p201、参考答案:冯诺伊曼计算机的设计思想EDVAC方案:存储程序通用电子计算机方案:①计算机分为计算器、控制器、存储器、输入和输出装置五个部分;②计算机内采用二进制;③将程序存储在计算机内,简称“程序存储”;其中第三点是冯诺依曼计算机设计的精华,所以人们又把冯诺依曼原理叫做程序存储原理,即程序由指令组成并和数据一起存放在存储器中,机器则按程序指定的逻辑顺序把指令从存储器中读出来并逐条执行,从而自动完成程序描述的处理工作;冯诺伊曼计算机主要以运算器和控制器为中心,结构框图如下图所示;2、参考答案:微处理器就是中央处理器CPU,是计算机的核心,单独的CPU不能构成计算机系统;微型计算机由微处理器、主存储器、I/O接口注意:不是I/O设备组成;而微型计算机系统除了包括微型计算机外,还有系统软件即操作系统、应用软件、外存储器和I/O设备等;微型计算机系统结构如下图所示;3、答案略,见p6~74、答案略,见图2,或教材图1-35、答案略,见p12~136、参考答案:由于8086微处理器的地址总线的宽度为20位,所以它可寻址220=1M字节的存储空间;而PentiumII微处理器的地址总线的宽度为36位,所以它可寻址236=64G字节的存储空间;7、参考答案:①PCIPeripheral Component Interconnect:外围设备互联,是Intel 公司1992年发布486微处理器时推出的32/64位标准总线,数据传输速率位132MB/s,适用于Pentium微型计算机;PCI总线是同步且独立于微处理器的具有即插即用PNP:Plug and play,所谓即插即用,是指当板卡插入系统时,系统会自动对板卡所需资源进行分配,如基地址、中断号等,并自动寻找相应的驱动程序的特性.PCI总线允许任何微处理器通过桥接口连接到PCI总线上;②USBUniversal Serial Bus:通用串行总线,是1994年由Compaq,IBM,Microsoft 等多家公司联合提出的;USB有两种规格:和,USB 传输速度为12M/秒,而USB 提高至360到480M/秒;USB 是向下兼容USB ,这意味着将一个USB 的设备插到USB 口中,只能按USB 的速度运行;USB连接方式十分灵活,支持热插拔,不需要单独的供电系统;可以通过一条4线串行线缆访问USB设备,用于连接键盘、鼠标、投影仪、数码相机等,现在成为每一台计算机都必须配备的标准接口;8、参考答案:DB----Define byte 定义一个字节类型的变量,并为该变量分配内存DW…Define word 定义一个字类型的变量,并为该变量分配内存DD….Define double word 定义一个双字类型的变量,并为该变量分配内存9、参考答案:1=或2=3=4=如何转换例如:=1×25+1×23+1×2+1+1×2-2+1×2-4= 32+8+2+1++=10、参考答案:1=10×16+3+3×16-1=2=1×162+2×16+9+12×16-1=3=10×16+12+13×16-1+12×16-2=4=15×162+10×16+11+3×16-1=11、参考答案:123=10111B=27Q=17H2107=1101011B=153Q=6BH492=1011100B=134Q=5CH12、参考答案:即把下面的数用8位补码表示13、参考答案:压缩BCD码就是用4位二进制表示一个0~9之间的十进制数非压缩的BCD码就是用8位二进制表示一个0~9之间的十进制数,8位二进制的最高4位可以位任何数,例如0000,0~9的ASCII码实际上就是0~9的非压缩BCD 码的表示;14、参考答案:如果二进制最高位为0,则该数为正数,反之,如果最高位为1,则该数为负数,对其做求补运算就得到其相反数;200110011B=+5115、参考答案:一个单精度浮点数占4个字节双字,即32位二进制,其中符号位占1位,指数部分占8位,尾数部分占23位;十进制数表示成单精度浮点数的方法如下:①填充符号位,如果是正数填0,如果是负数填1②将数表示成二进制形式,并进行规格化③对于单精度浮点数,指数加上1277FH;对于双精度浮点数,指数要加上1023 3FFH,并填充指数位④填充尾数位1+ ①由于是正数,所以符号位为0;②写成二进制并规格化得到×20,③由于2的指数是0,所以指数部分以0+127=01111111填充;④由②写成十六进制数为:+=3F C0 00 00H2=C12A0000H3+=42C88000H4=C4960000H16、参考答案:21 01111111 00000000000000000000000B=第二章p55~p561、答案略,见p22~242、答案略,见p24~273、答案略,见p334、参考答案其他可以参照本章相关内容:① CPU:又称微处理器,是计算机系统的核心,一般由逻辑运算、控制单元和一些组成;这些寄存器用于CPU在处理过程中数据的暂时保存;它主要完成从存储器中取指令,指令译码;算术逻辑运算;在处理器和存储器或I/O接口之间传送数据;程序的流向控制等;②存储器:是计算机系统的记忆部件,主要用来存储程序和数据;存储器一般分为内部存储器和外部存储器两大类;内部存储器内存存放当前正在使用或经常使用的程序和数据,CPU可以直接访问;外存存放“海量”数据,相对来说不经常使用,CPU使用时要先调入内存;内部存储器又可以分为随机存取存储器RAM和只读存储器ROM;计算机系统存储器的三层结构:按存储容量由低到高或按存取速度由高到低分为高速缓冲存储器CACHE、主存、辅存三层;③堆栈Stack:堆栈是在存储器中开辟一个区域,用来存放需要暂时保存的数据;当前栈顶单元一般采用SP指向,栈底设在存储器的高地址区,堆栈地址由高到低增长;堆栈的工作方式是“后进先出”,用入栈指令PUSH 和出栈指令POP可将数据压入堆栈或从堆栈中弹出数据,栈顶指针SP的变化由CPU自动管理,入栈操作SP减小,出栈操作SP增大;堆栈的操作以字为单位;④机器语言Machine Language:计算机唯一能接受和执行的语言;机器语言由二进制码组成,每一串二进制码叫做一条指令,一条指令规定了计算机执行的一个动作,一台计算机所能懂得的指令的全体,叫做这个计算机的指令系统,不同型号的计算机的指令系统不同;使用机器语言编写程序是一种相当烦琐的工作,既难于记忆也难于操作,编写出来的程序全是由0和1的数字组成,直观性差、难以阅读;不仅难学、难记、难检查、又缺乏通用性,给计算机的推广使用带来很大的障碍;⑤汇编语言Assembly Language:是一种符号语言,它和机器语言几乎一一对应,在书写时使用字符串组成的助记符Mnemonic代替操作码,用地址符号Symbol 或标号Label代替地址码;使用汇编语言编写的程序,机器不能直接识别,要由一种程序将汇编语言翻译成机器语言,这种起翻译作用的程序叫汇编程序,如微软的宏汇编程序;汇编程序把汇编语言翻译成机器语言的过程称为汇编;汇编语言比机器语言易于读写、调试和修改,同时具有机器语言全部优点;但在编写复杂程序时,相对高级语言代码量较大,而且汇编语言依赖于具体的处理器体系结构,不能通用,因此不能直接在不同处理器体系结构之间移植;⑥指令Instruction:指令是能被计算机识别并执行的二进制代码,它规定了计算机能完成的某一操作;一条指令通常由两个部分组成:操作码+操作数;:指明该指令要完成的操作的类型或性质,如取数、做加法或输出数据等;操作数:指明操作对象的内容或所在的存储单元地址地址码,操作数在大多数情况下是地址码,地址码可以有0~3个;9、参考答案:注意:①段起始地址和段结束地址均为20位的物理地址;②段起始的偏移量为0000H,所以段起始地址为段基地址×16+偏移地址;③由于每个段的最大容量为64K字节,段结束的偏移量为FFFFH,所以段结束地址为段基地址×16+偏移地址=段基地址×16+FFFFH10、参考答案:a)CS:IP=1000H:2000H 下一条指令的存储器地址为CS×16+IP=12000Hb)CS:IP=2000H:1000H 下一条指令的存储器地址为CS×16+IP=21000Hc)CS:IP=1A00H:B000H 下一条指令的存储器地址为CS×16+IP=25000Hd)CS:IP=3456H:AB09H 下一条指令的存储器地址为CS×16+IP=3F069 H11、参考答案:a)DS=1000H,DI=2000H 存储单元地址为:DS×16+DI=12000Hb)SS=2300H,BP=3200H 存储单元地址为:SS×16+BP=26200Hc)DS=A000H,BX=1000H 存储单元地址为:DS×16+BX=A1000Hd)SS=2900H,SP=3A00H 存储单元地址为:SS×16+SP=2CA00H12、参考答案:①堆栈段在存储器中的物理地址即堆栈段的起始地址为:SS×16+0000H=35000H②入栈10个字节后,SP=0800H-10=07F6H③再出栈6个字节,SP=07F6H+6=07FCH13、参考答案:示意图如左图所示,如果要读取这两个字,则需要对存储器进行三次操作;①由于字2A8CH存放在偶地址开始的单元,所以只进行一次存储器操作就可以读取该字;②由于字1EE5H存放在奇地址开始的单元,所以需要进行两次存储器操作才可以读取该字;14、参考答案:段段起始地址段结束地址DS 10E40H 20E3FHES 10F40H 20F3FH可见,①DS和ES有部分的重叠,重叠区域大小为:20E3FH-10F40H+1=FF00H字节;②ES和SS之间有空隙,空隙的大小为:21F00H-20F3FH+1=0FC2H字节;③SS和CS 之间有空隙,空隙的大小为:31FF0H-31EFFH+1=00F2H字节④OF SF ZF CF 均为017、参考答案:IF标志位控制INTR引脚20、答案略,见p4921、答案略第三章p121~p1241、参考答案:对于IN指令,如果是长格式,源操作数的数字不是立即数,而是端口地址,所以源操作数的寻址方式是直接寻址;如果是短格式,即端口地址存放在DX寄存器中,则源操作数的寻址方式为寄存器间接寻址,如:IN AX,DX对于OUT指令,如果是长格式,目的操作数的数字不是立即数,而是端口地址,所以目的操作数的寻址方式是直接寻址,如OUT 20H,AL;如果是短格式,即端口地址存放在DX寄存器中,则目的操作数的寻址方式为寄存器间接寻址,如:OUT DX,AX 2、参考答案:题号源操作数寻址方式源操作数有效地址源操作数物理地址指令执行后AX中的内容1 立即寻址------- ------ 0200H2 直接寻址0200H 10200H 2A10H3 寄存器寻址------- ------ 0200H4 寄存器相对寻址0203H 10203H 5946H5 基址变址寻址0202H 10202H 463CH6 相对基址变址寻址0204H 10204H 6B59H注:10200H~10205H单元存储状况如左图所示3、参考答案:题号源操作数寻址方式源操作数有效地址源操作数物理地址4、答案略5、参考答案:1该数据段的存储状况如下表所示:注:①表格的第一行为变量名称;②第三行的每个小格子代表一个存储单元;③第二行为存储单元的偏移地址以十六进制表示,从中可以看出各变量在数据段中的偏移地址,A的偏移地址为0000H,B的偏移地址为0002H,C的偏移地址为000AH,D的偏移地址为000EH,E的偏移地址为0013H;④第三行为存储单元的具体内容,以十六进制表示;2写出各条指令执行后的结果6、参考答案:7、程序片段如下:LEA BX,TABLE MOV AL,57MOV AH,0MOV DL,10DIV DLPUSH AXXLATMOV CH,ALPOP AXMOV AL,AHXLATMOV CL,ALMOV BX,CX9、已知AX=1234H,BX=3456H,CX=5678H,DX=789AH,CF=1则单独执行下列各条指令后,各相关寄存器内容是什么10、参考程序片段如下:;定义数据段DATA SEGMENTARRAY DB 60,65,72,76,77,66,79NEW DB 7 DUP0SUM DB 0AVERAGE DB 0DATA ENDS;程序代码如下……MOV CX,7MOV SUM,0MOV SI,0NEXT:MOV AL,ARRAYSIADD SUM,AL ;总分存入SUM中ADD AL,5MOV NEWSI,ALINC SILOOP NEXTMOV AL,SUMMOV AH,0MOV CL,7DIV CLMOV AVERAGE,AL ;平均分存入AVERAGE中12、参考答案:1程序片段如下:LEA SI,STRINGLEA DI,GET_CHARMOV CX,26CLDREP MOVSB2程序片段如下:先定义一个附加段,用来存放’The computer’EXTRA SEGMENTS2 DB ‘The computer’EXTRA ENDS…LEA SI,STRINGLEA DI,S2MOV CX,12CLDREPZ CMPSBJZ NEXT ;若比较的两个字符串相同,则跳到NEXT执行MOV AL,0 ; 若比较的两个字符串不相同SUB CL,12NEG CLMOV BL,CL ;比较的次数存入BL中RETNEXT:MOV AL,1MOV BL,12RET3程序片段如下:LEA DI,STRING ;被查找的字符串STRING作为目的串MOV AL,’&’MOV CX,26CLDREPNZ SCASBJNZ EXIT ;如果没有找到,直接退出DEC DI ;找到’&’字符的位置MOV BYTE PTR ES:DI,20H ;用空格字符替换EXIT: RET4完整的程序如下:;这里的DATA既作为数据段,又作为附加段,即数据段和附加段公用一个段DATA SEGMENTSTRING DB ‘The Personal Computer & TV’COUNT EQU $-STRINGCAPS DB COUNT DUP0CHART DB COUNT DUP0DATA ENDSCODE SEGMENTASSUME DS:DATA,ES:DATA,CS:CODEMAIN PROC FARPUSH DSXOR AX,AXPUSH AXMOV AX,DATAMOV DS,AXMOV ES,AX;把字符串中大写字母传送到CAPS开始的单元中LEA SI,STRINGLEA DI,CAPSMOV CX,COUNTCLDAGAIN1:LODSBCMP AL,41HJB NEXT1CMP AL,5AHJA NEXT1STOSBNEXT1:LOOP AGAIN1;把字符串中其余字母传送到CHART开始的单元中LEA SI,STRINGLEA DI,CHARTMOV CX,COUNTCLDAGAIN2:LODSBCMP AL,41HJB NEXTCMP AL,5AHJBE NEXT2NEXT: STOSBNEXT2:LOOP AGAIN2;将STRING字符串清零LEA DI,STRINGMOV AL,0MOV CX,COUNTCLDREP STOSBRETMAIN ENDPCODE ENDSEND MAIN13、完整的程序如下:CODE SEGMENTASSUME CS:CODEMAIN PROC FARPUSH DSXOR AX,AXPUSH AXXOR SI,SI ;SI中存放DX中1的个数XOR DX,DXMOV AX,1234HMOV CX,16AGAIN:ROR AX,1JNC NEXTINC SIPUSH CXDEC CLMOV BX,1SHL BX,CLOR DX,BXPOP CXNEXT: LOOP AGAINRETMAIN ENDPCODE ENDSEND MAIN程序的运行结果:AX=1234H DX=2C48H SI=0005H,结果正确如果是段内转移,跳转指令只改变IP寄存器的内容,前三条跳转指令是段内跳转;如果是段间跳转,跳转指令同时改变IP和CS寄存器的内容,后两条跳转指令是段间跳转;15、参考答案:注意:三个循环指令LOOP 、LOOPE 和LOOPNE 终止循环的条件是不一样的; 16、参考答案:中断向量表的作用:中断向量表用于存放256种中断的中断服务程序的入口地址,每种类型中断的中断服务程序的入口地址占用4个字节,存储CS 和IP,总共需要1024个字节,即1K 字节; 中断向量表位于内存的最低1K 字节,地址范围为:00000H~003FFH;类型3的中断的中断服务程序的入口地址存放在:0000CH~0000FH 这四个单元; 17、参考答案:如下图所示解释:①由于中断类型号为2,所以该类型中断的中断服务程序入口地址占据内存最低1K 字节的2×4,2×4+1,2×4+2,2×4+3四个单元;②前两个单元存放中断服务程序IP 值,即0016H,后两个单元存放中断服务程序的CS 值,即0485H;③由于CS 和IP 值均为一个字,所以在存放中断服务程序入口地址的CS 和IP 值时,低位字节存放在低地址区,高位字节存放在高地址区; 18、参考答案: 1中断类型号为162该中断服务程序的起始地址是:CS:IP=D169H:240BH 解释:①由于中断向量表中地址为0040H 开始存放某类型中断的中断服务程序的入口地址,所以0040H 除以4就可以得到该类型中断的中断类型号n,即n=16;②中断服务程序的入口地址的CS 值存放在0042H 单元里,IP 值存放在0040H 单元里;20、参考答案:MOV CX,N;4个时钟周期NEXT:NOP ;N ×3个时钟周期 NOP ;N ×3个时钟周期LOOP NEXT;N-1×17+1×5个时钟周期由f =5MHz,t =,延时5ms 需要25000102.010563=⨯⨯--个时钟周期 所以:4+N ×3+N ×3+N-1×17+1×5=25000 解得:N=1087第四章p205~p2061、参考答案写出各变量在内存中的存储状况A1 DW 23H,5678HA2 DB 3 DUP,0AH,0DH,’$’A3 DD 5 DUP1234H,567890HA4 DB 4 DUP3 DUP1,2,’ABC’①变量A1占4个字节,在内存中的存储状况以十六进制表示,从左到右地址依次增加,以下同:23 00 78 56②变量A2占6个字节,在内存中的存储状况:00 00 00 0A 0D 24③变量A3占40个字节,在内存中的存储状况:34 12 00 00 90 78 56 00 再重复4遍④变量A4占60个字节,在内存中的存储状况:01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43 01 02 41 42 43带下画线部分重复4遍2、参考答案写出各指令执行后的结果3、参考答案:L=6,L的值实际就是BUF变量在内存中占有的字节数;4、参考答案:PLENGTH=22,PLENGTH的值实际就是三个变量PAR、PNAME和COUNT在内存中占有的总的字节数;5、参考答案:AX=1 BX=20 CX=16、参考答案:AH=00H7、1利用中断调用产生5秒延时data segments db '5 second is gone',13,10,'$'data endscode segmentassume cs:code,ds:datamain proc farmov ax,datamov ds,axmov ah,2chint 21h ;取得当前时间:ch时 cl分 dh秒 dl1/100秒mov bl,dhcontinue:mov ah,2chint 21hsub dh,blcmp dh,5jb continue ;判断两次取得时间间隔是否为5秒钟,如果不是则继续读取时间lea dx,s ;如果达到5秒,则显示一条信息mov ah,9int 21hmov ax,4c00hint 21hmain endpcode endsend main2利用中断调用,在屏幕上显示1~9之间的随机数思路:利用DOS系统功能调用得到当前时间,其中的dl寄存器中存放的是1/100秒,可以用来产生随机数;code segmentassume cs:codemain proc farmov ah,2chint 21hmov al,dl ;取得1/100秒,不同时间运行该程序时得到的这个数字也不一样,具有随机性mov ah,0mov bl,9 ;除以9div bl ;相除后的余数ah的范围为0~8inc ah ;加1后得到1~9之间的数add ah,30h ;转换为ASCII码mov dl,ahmov ah,2int 21h ;在屏幕上显示该数mov ax,4c00hint 21hmain endpcode endsend main8、1二进制到压缩BCD码的转换;把AX中的二进制数转换为压缩的BCD码,仍然存放AX寄存器中;例如:如果AX中的二进制数为0010 0110 1001 0100B=2694H,化成十进制数是9876,其压缩的BCD码是1001 1000 0111 0110,用十六进制表示是9876H;即这种转换实际就是把2694H转换为9876H;考虑到AX中能够存放的最大的四位压缩BCD数为9999H,所以在转换之前需要判断AX中的二进制数不能超过9999,即270FH;第五章p237~2382、ROM、PROM、EPROM、EEPROM在功能上各有何特点答案略见教材p2083、DRAM的CAS和RAS输入的用途是什么答:为了提高DRAM的集成度,减少引脚的数目,DRAM的地址线分成行地址和列地址两部分,在对存储器进行访问时,先由行地址选通信号RAS把行地址送入行地址锁存器,再由列地址选通信号CAS把列地址送入列地址锁存器,并由读写信号控制数据的读出或写入;4、什么CACHE作用是什么处于微处理机中的什么位置答:CACHE即高速缓冲存储器,通常由SRAM组成;其作用是:将经常访问的代码和数据保存到由SRAM 组成的高速缓冲存储器中,把不经常访问的数据保存到由DRAM组成的主存中,这样使存储器系统的价格降低,同时又降低了接近零等待的性能,大大的提高了系统的性能;CACHE位于CPU和主存储器之间;7、用1024×1位的RAM芯片组成16K×8位的存储器,需要多少芯片在地址线中有多少位参与片内寻址多少位合成片选信号设地址总线为16位答:需要16×8=128片RAM芯片,其中每8片为一组,总共有16组;地址线中有10位参与片内寻址;由于有16组芯片,余下的6根地址线中至少需要4根合成片选信号,来选中其中的一组芯片;8、现有一存储器芯片的容量为512×4位,若要用它组成4KB的存储器,需要多少这样的芯片每块芯片需要多少寻址线整个存储系统最少需要多少寻址线答:需要的芯片的数目为16片,每两片为一组,共有8组;每块芯片需要9根寻址线;由于共有8组芯片,至少需要3根地址线合成片选信号用来选择8组芯片中的一组;整个存储器系统至少需要9+3=12根地址线;9、利用1024×8位的RAM芯片组成4K×8位的存储器系统,用A15~A12地址线用线性选择法产生片选信号,存储器地址的分配有什么问题写出各芯片的地址分配;答:①需要的芯片的数目:4片②片内寻址需要的地址线的数目:由于每片RAM芯片内部有1024个存储单元,所以需要10根地址线用于选中其中某一个存储单元,占用地址总线的低10位A9~A0③片间寻址需要的地址线的数目:由于需要4片存储器芯片,所以至少需要2根地址线进行译码用于选择4片芯片中的一片,这样占用地址总线的A11和A10;余下的地址总线用线性选择法产生片选信号,这样A15~A12的电平的不同组合就产生了不同的地址空间,使得存储器芯片的地址空间产生重叠;如果A15~A12的电平组合为:A15=1,其余的均为0,则4片存储器芯片的地址范围分别为:A15 A14 A13 A12 A11 A10 A9…A01:1 0 0 0 0 0 0 … 0 =8000H1 0 0 0 0 0 1 … 1 =83FFH2:1 0 0 0 0 1 0 … 0 =8400H1 0 0 0 0 1 1 … 1 =87FFH3:1 0 0 0 1 0 0 … 0 =8800H1 0 0 0 1 0 1 … 1 =8BFFH4:1 0 0 0 1 1 0 … 0 =8C00H1 0 0 0 1 1 1 … 1 =8FFFH10、当从存储器偶地址单元读一个字节数据时,写出存储器的控制信号和它们的有效电平8086工作在最小模式;答案如下表所示:11、当要将一个字写入到存储器奇地址开始的单元中,列出存储器的控制信号和他们的有效电平8086工作在最小模式;答案如下表所示:分两次写入:第一次:第二次:12、设计一个64K×8的存储器系统,采用74LS138和EPROM 2764器件,使其寻址空间范围为:40000H~4FFFFH;解题步骤如下:①存储器芯片数目的确定:由于每片2764芯片为8K×8位,要组成64K×8的存储器系统,需要8片2764芯片,编号为1~8;②片内寻址地址线的选择:由于每片2764芯片为8K×8位,即有8K213=8K个存储单元,所以需要13根地址线A12~A0分别接到芯片的13个地址引脚,来选通片内某个存储单元;③片间寻址地址线的分配:A15、A14和A13分别连接到74LS138的C、B、A端,74LS138的8个输出④余下的地址线的连接:A19~A16和M/IO信号通过逻辑电路接到74LS138的三个控制端G1、G2A和G2B,具体的逻辑电路的设计与题目给定的寻址空间范围有关,如果题目没有给定寻址空间范围,逻辑电路由读者自行设计;⑤根据寻址空间范围设计控制端的逻辑电路:把最低地址40000H表示成二进制形式为:0100 0000 0000 0000 0000,可知20位地址总线高4位A19~A16的电平组合为A19=0,A18=1,A17=0,A16=0,加上M/IO=1,由此可以设计出74LS138的三个控制端G1、G2A和G2B的逻辑电路;M/IO信号可以同G1端直接相连;A18反向后与A19通过二输入负逻辑与非门即或门接到G2A端,A17和A16通过二输入负逻辑与非门或门连接到G2B端;⑥其他控制信号的连接:数据总线D7~D0直接与存储器芯片的8根数据引脚相连接;RD信号直接芯片的允许输出引脚相连;具体的电路图略;13、用8K×8的EPROM 2764,8K×8的RAM 6264和74LS138构成一个16K字ROM,16K字RAM的存储器子系统;8086工作在最小模式,系统带有地址锁存器8282,数据收发器8286;画出存储器系统与CPU的连接图,写出各芯片的地址分配;解题步骤如下:①存储器芯片数目的确定:需要EPROM芯片4片,每两片组成一组两片存储器芯片构成一个字存储器,一片为奇地址存储体,另一片为偶地址存储体,共有2组,编号为1和2;需要RAM芯片4片,每两片组成一组两片存储器芯片构成一个字存储器,一片为奇地址存储器,另一片为偶地址存储器,共有2组,编号为3和4;②片内寻址地址线的选择:由于每片2764芯片和6364芯片均为8K×8位,即有8K213=8K个存储单元,所以需要13根地址线A13~A1分别接到芯片的13个地址引脚,来选通片内某个存储单元;注意:A0不参与片内寻址,用来作为奇偶存储体的选择信号;A0与BHE信号相配合来读/写每一组中的奇偶存储体;③片间寻址地址线的分配:A16、A15和A14分别连接到74LS138的C、B、A端,74LS138的8个输出中的4个输出端分别选择4组包括2组EPROM芯片和2组RAM芯片存储器芯片中的一组;④三个控制端相连;可以由读者自行设计;如果选择A19=1,A18=0,A17=0,M/IO信号可以同G1端直接相连;A19反向后接到G2A端,A18和A17通过二输入负逻辑与非门或门连接到G2B端;⑤二次译码:由于每一组存储器由两片存储器芯片组成,一片为奇地址存储体,另一片为偶地址存储体,这两个存储体的选择需要A0和BHE信号;因此,74LS138的每个输出Y0~Y3还需要同这两个信号进行二次译码产生两个信号分别连到该组存储器的两个存储器芯片的CS端;例如:对于第1组存储器,Y0与A0通过二输入或门连到1的偶地址存储器芯片的CS端;Y0与BHE通过二输入或门连到1的奇地址存储器芯片的CS端;其他三组的二次译码电路以此类推;⑥各组芯片的地址范围:1:80000H~83FFFH2:84000H~87FFFH3:88000H~8BFFFH4:8C000H~8FFFFH每组的两个存储器芯片分别占用其中的奇地址和偶地址;14、上题中若从74LS138的Y2开始选择ROM和RAM芯片,写出各块芯片的地址分配;解答:若从74LS138的Y2开始选择ROM和RAM芯片,那么片间寻址A16、A15和A14组合如下表所示则各组芯片的地址范围为:1:88000H~8BFFFH2:8C000H~8FFFFH3:90000H~93FFFH4:94000H~97FFFH第六章p2627、某微机系统中,有8块I/O接口芯片,每个芯片占有8个端口地址,若起始地址为9000H,8块芯片的地址连续分布,用74LS138作译码器,画出译码电路,并说明每块芯片的端口地址范围;解答:①片内寻址地址线的分配:由于每个芯片占有8个端口地址,则需要3个地址线用于片内寻址以访问片内8个端口,这样占用地址总线的最低3位,即A2、A1和A0;②片间寻址地址线的分配:由于总共有8块I/O接口芯片,则需要8根地址线,并接到74LS138的3个输入端C、B和A,74LS138的8个输出端Y0~Y7分别接8个I/O接口芯片的CS端,以寻址8块芯片中的一块,这样占用地址总线的A5、A4和A3位;③74LS138的控制端的连接:根据起始地址9000H可知,剩下的地址线A15~A6的组合为A15=1,其余的地址线的电平信号为低电平,加上M/IO=0,据此可以求出74LS138的3个控制端的连线逻辑;④各个芯片的地址范围:1 9000H~9007H2 9008H~900FH3 9010H~9017H4 9018H~901FH,同理可写出剩下的4块芯片的地址范围;第七章p302~3031~4题略5、中断服务子程序中中断指令STI放在不同位置会产生什么不同的结果中断嵌套时STI指令应如何设置解答:在进入中断服务程序时,中断允许标志位IF被清0,以屏蔽其他外部中断,在中断服务程序中可以用STI指令重新开中断,即IF=1;①STI指令放在中断服务程序开头和中间的某个位置,可以允许中断嵌套,CPU能响应更高级别的中断请求;②STI指令放在中断服务程序结束之前,几乎没什么作用,因为当前的中断服务快要结束了,中断结束后,自动恢复标志位IF,使IF=1,CPU又可以响应中断了;如果允许中断嵌套,则在中断服务子程序的开头用STI指令开中断;6、中断结束命令EOI放在程序的不同位置会产生什么不同的结果解答:EOI命令能够使中断控制器的ISR中断服务寄存器的相应位清0,允许同级别或级别较低的中断请求;在中断服务子程序中,EOI指令可以放在①中断服务程序的开头和中间的某个位置,则在中断处理中提前发出了EOI命令,则清除了正在执行的中断服务,ISR置“1”位被清0,允许响应同级别或低级的中断申请,但是这样会出现重复嵌套,使优先级高的中断不能及时得到服务;②放在中断服务程序返回指令IRET之前,这样当前中断结束之后,同级别或低级的中断申请同样可以得到响应,也不会出现重复嵌套,优先级高的中断也能够得到及时服务;建议在中断返回指令IRET指令前面使用EOI命令;7、中断向量表的功能是什么。

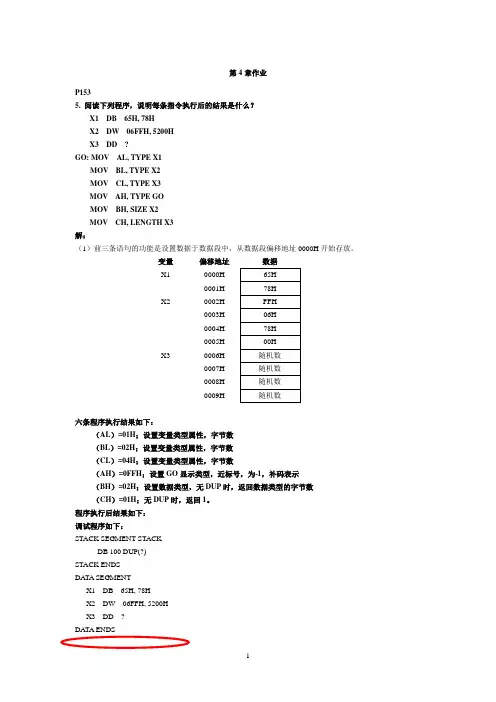

第4章作业P1535. 阅读下列程序,说明每条指令执行后的结果是什么?X1 DB 65H, 78HX2 DW 06FFH, 5200HX3 DD ?GO: MOV AL, TYPE X1MOV BL, TYPE X2MOV CL, TYPE X3MOV AH, TYPE GOMOV BH, SIZE X2MOV CH, LENGTH X3解:(1)前三条语句的功能是设置数据于数据段中,从数据段偏移地址0000H开始存放。

变量偏移地址数据X1 0000H0001HX2 0002H0003H0004H0005HX3 0006H0007H0008H0009H六条程序执行结果如下:(AL)=01H;设置变量类型属性,字节数(BL)=02H;设置变量类型属性,字节数(CL)=04H;设置变量类型属性,字节数(AH)=0FFH;设置GO显示类型,近标号,为-1,补码表示(BH)=02H;设置数据类型,无DUP时,返回数据类型的字节数(CH)=01H;无DUP时,返回1。

程序执行后结果如下:调试程序如下:STACK SEGMENT STACKDB 100 DUP(?)STACK ENDSDATA SEGMENTX1 DB 65H, 78HX2 DW 06FFH, 5200HX3 DD ?DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACKSTART: PUSH DSMOV AX,DA TAMOV DS,AXGO: MOV AL, TYPE X1MOV BL, TYPE X2MOV CL, TYPE X3MOV AH, TYPE GOMOV BH, SIZE X2MOV CH, LENGTH X3POP DSHLTCODE ENDSEND START6. 画出示意图,说明下列变量在内存中如何让存放?A1 DB 12H, 34HA2 DB ‘Right.’A3 DW 5678HA4 DB 3 DUP(?)(1)设置数据于数据段中,从数据段偏移地址0000H开始存放。

第二章作业2-2简述微处理器的工作方式、各工作方式的含义和区别是什么?它们之间是如何切换的?答:1.五种工作方式:实地址方式、保护虚地址方式、虚拟86方式、系统管理方式以及IA-32E方式。

2.含义:(1)实地址方式是指处理器工作在8086/8088编程环境下的工作方式,其最大地址空间为1MB。

(2)保护地址方式,又称保护虚地址方式,简称保护方式,是真正发挥处理器潜能的一种工作方式。

所谓保护是指在执行多任务操作时,对不同任务使用的不同存储空间进行完全隔离,保护每个任务顺利执行,能够寻址的地址空间为实际的物理地址空间即2m(m为处理器外部地址线的引脚条数)。

(3)虚拟86方式是指一个多任务的环境,即模拟多个8086的工作方式。

在这个方式之下,处理器被模拟成多个8086微处理器同时工作。

(4) 系统管理方式(SMM)是为实现特定功能及系统安全提供的一种工作方式,SMM的功能主要包括电源管理以及为操作系统和正在运行的程序提供安全性。

SMM最显著的应用就是电源管理。

以上四种方式是IA-32所有处理器所具有的工作方式。

(5)从后期的P4到以Core为核心的处理器开始支持64位扩展技术,引入了IA-32E工作方式。

在这种方式下,处理器支持两种模式即兼容的工作方式(兼容IA-32处理器的方式)和64位工作方式。

在兼容模式下,允许在64位操作系统下运行原来的16位和32位应用程序,可使用前缘REX访问64位数据,最大支持的32位地址空间,而在64位方式下,采用EM64T技术,支持64位操作,同时支持36位的地址(从Pentium Pro开始处理器的外部地址线就提供36条),支持64位线性地址,默认的地址空间为64位,默认的数据宽度为32位,指令允许32/64地址和32/64数据的混合使用,因此又把Core为核心的处理器称为32/64处理器,与真正64位处理器有区别,可称之为具有64位功能的32位处理器。

3.工作方式的相互转换如下图所示。

微机原理与接⼝技术第五章课后答案第五章参考答案1.简述SRAM 芯⽚与DRAM 芯⽚的共同点与不同点。

答:SRAM 与DRAM 的共同点:都属于随机存取存储器,具有易失性。

SRAM 与DRAM 的共同点:SRAM 利⽤双稳态触发器电路保存信息,集成度⽐DRAM 低,功耗⽐DRAM ⼤;DRAM 利⽤MOS 管栅极和源极之间的极间电容C 保存信息,需要刷新电路保证信息较长时间保存。

2.叙述ROM 芯⽚的常见分类,各种ROM 芯⽚的特点及其适⽤场合。

答:ROM 的常⽤分类结果:掩膜ROM :⽣产完成的芯⽚已保存了信息,保存的信息⽆法修改,适⽤于⼤批量的定型产品中。

PROM :PROM 可以⼀次写⼊信息,⼀旦写⼊⽆法更改,适⽤于⼩批量的定型产品中。

EPROM :紫外线擦除可多次编程的存储器,适⽤于新产品的开发。

EEPROM :电擦除可多次编程的存储器,适⽤于需要在线修改的场合。

3.利⽤4⽚6116(2K ×8位)芯⽚设计连续存储器,采⽤全地址译码。

设起始地址为60000H ,求存储器的最后⼀个单元地址。

答:存储器的最后⼀个单元地址为:61FFFH.4.⽤6264 RAM (8K ×8位)芯⽚构成256K 字节存储器系统,需要多少⽚6264芯⽚20位地址总线中有多少位参与⽚内寻址有多少位可⽤作⽚选控制信号答:需要32⽚6264芯⽚。

20位地址总线中有13位参与⽚内寻址;有7位可⽤作⽚选控制信号。

5.某微机系统中ROM 区有⾸地址为9000H ,末地址为FFFFH ,求其ROM 区域的存储容量。

答:其ROM 区域的存储容量为28K 。

6.在8088CPU 的系统中扩展32K 字节的RAM ,其扩充存储空间的起始地址为08000H 。

设系统的地址总线为A 19~A 0,数据总线为D 7~D 0,存储器芯⽚选⽤6264。

利⽤74LS138译码器设计译码电路,并画出扩充的存储器系统的连线图。

微机原理与接口技术课后部分习题参考答案第一章2. 第3项任务,根据状态标志位的状态决定转移方向。

3. 程序存储是将要执行的程序的全部指令存储到存储器中,程序控制指程序开始执行后,通过指令流控制数据或计算机,完成设定的任务。

4. 分BIU 总线接口部件和EI执行部件两大部件,其中总线接口部件BIU负责取指令和数据,执行部件EI负责执行指令及运算。

在执行一条指令的同时可以取下一条指令,重叠运行,速度快。

5. 有6个状态标志,分别为进位标志CF、溢出标志OF、零标志ZF、奇偶标志PF、负标志SF、辅助进位标志AF。

3个控制标志分别为中断允许标志IF、单步标志TF、方向标志DF。

标志位的内容可以通过标志位操作指令来操作,例如CLC指令清除进位位,即使CF=0,STC指令使CF=1,CLI指令使IF=0,禁止中断,STI指令使IF=1,允许中断。

还可以通过LAHF指令取来标识寄存器的内容修改后用SAHF指令送回去。

也可以用PU SHF/POPF指令来修改标志寄存器的内容。

6. 实模式下分段靠4个段寄存器实现。

段寄存器中的值就是段地址,当偏移地址为0时的段地址+偏移地址就是该段的起始地址。

物理地址是由段地址左移4位后与偏移地址相加形成的20位地址。

7. 说法不一定正确。

对顺序执行指令的计算机是对的。

对重叠或流水线的计算机就不对了。

例如对8086CPU,由于采用了取指令与执行指令的一次重叠,尽管执行一条指令的总时间并没有变化,但连续执行n条指令时,总的时间会大大缩短,可以简单的比喻成总时间为原时间的二分之一,快了一倍。

8. 引入流水线后,执行一条指令的总时间并没有变化。

9. 高速缓存的目的是提高存储器的速度,进而提高了CPU的速度。

虚拟存储器的目的是为了给程序员或程序一个大的存储或运行空间。

10。

8086采用总线接口部件BIU与执行部件EU分开提高了速度,286将8086的BIU进一步分成3个部件,提高了并行性。

微机原理与接口技术(第二版)课后习题答案第1章作业答案1.1 微处理器、微型计算机和微型计算机系统三者之间有什么不同?解:把CPU(运算器和控制器)用大规模集成电路技术做在一个芯片上,即为微处理器。

微处理器加上一定数量的存储器和外部设备(或外部设备的接口)构成了微型计算机。

微型计算机与管理、维护计算机硬件以及支持应用的软件相结合就形成了微型计算机系统。

1.2 CPU在内部结构上由哪几部分组成?CPU应该具备哪些主要功能? 解:CPU主要由起运算器作用的算术逻辑单元、起控制器作用的指令寄存器、指令译码器、可编程逻辑阵列和标志寄存器等一些寄存器组成。

其主要功能是进行算术和逻辑运算以及控制计算机按照程序的规定自动运行。

1.3 微型计算机采用总线结构有什么优点?解:采用总线结构,扩大了数据传送的灵活性、减少了连线。

而且总线可以标准化,易于兼容和工业化生产。

1.4 数据总线和地址总线在结构上有什么不同之处?如果一个系统的数据和地址合用一套总线或者合用部分总线,那么要靠什么来区分地址和数据?解:数据总线是双向的(数据既可以读也可以写),而地址总线是单向的。

8086CPU为了减少芯片的引脚数量,采用数据与地址线复用,既作数据总线也作为地址总线。

它们主要靠信号的时序来区分。

通常在读写数据时,总是先输出地址(指定要读或写数据的单元),过一段时间再读或写数据。

1.8在给定的模型中,写出用累加器的办法实现15×15的程序。

解: LD A, 0LD H, 15LOOP:ADD A, 15DEC HJP NZ, LOOPHALT第 2 章作业答案2.1 IA-32结构微处理器直至Pentillm4,有哪几种?解:80386、30486、Pentium、Pentium Pro、Peruium II 、PentiumIII、Pentium4。

2.6 IA-32结构微处理器有哪几种操作模式?解:IA一32结构支持3种操作模式:保护模式、实地址模式和系统管理模式。

第5章 总线及其形成

1. 微处理器的外部结构表现为 数量有限的输入输出引脚 ,它们构成了微处理器级总线。

2. 微处理器级总线经过形成电路之后形成了 系统级总线 。

3. 简述总线的定义及在计算机系统中采用标准化总线的优点。

答:总线是计算机系统中模块(或子系统)之间传输数据、地址和控制信号的公共通道,

它是一组公用导线,是计算机系统的重要组成部分。

采用标准化总线的优点是:

1) 简化软、硬件设计。

2) 简化系统结构。

3) 易于系统扩展。

4) 便于系统更新。

5) 便于调试和维修。

4. 在微型计算机应用系统中,按功能层次可以把总线分成哪几类。

答:在微型计算机应用系统中,按功能层次可以把总线分成:片内总线、元件级总线、

系统总线和通信总线。

5. 简述RESET 信号的有效形式和系统复位后的启动地址。

答:RESET 为系统复位信号,高电平有效,其有效信号至少要保持四个时钟周期,且复

位信号上升沿要与CLK 下降沿同步。

系统复位后的启动地址为0FFFF0H 。

即:(CS )=0FFFFH ,(IP )=0000H 。

6. 8086 CPU 的IO M/信号在访问存储器时为 高 电平,访问I/O 端口时为 低 电平。

7. 在8086系统总线结构中,为什么要有地址锁存器?

答:8086CPU 有20条地址线和16条数据线,为了减少引脚,采用了分时复用,共占了

20条引脚。

这20条引脚在总线周期的T1状态输出地址。

为了使地址信息在总线周期的其

他T 状态仍保持有效,总线控制逻辑必须有一个地址锁存器,把T1状态输出的20位地址信

息进行锁存。

8. 根据传送信息的种类不同,系统总线分为 数据总线 、 地址总线 和 控制总线 。

9. 三态逻辑电路输出信号的三个状态是 高电平 、 低电平 和 高阻态 。

10. 在8086的基本读总线周期中,在1T 状态开始输出有效的ALE 信号;在2T 状态开始输出

低电平的RD 信号,相应的DEN 为__低__电平,R DT/为__低__电平;引脚AD 15 ~ AD 0

上在1T 状态期间给出地址信息,在4T 状态完成数据的读入。

11. 利用常用芯片74LS373构成8086系统的地址总线, 74LS245作为总线收发器构成数

据总线,画出8086最小方式系统总线形成电路。

答:8086最小方式系统总线形成电路如图5.1所示。

图5.1 8086最小方式系统总线形成电路

12. 微机中的控制总线提供 H 。

A. 数据信号流;

B. 存储器和I/O 设备的地址码;

C. 所有存储器和I/O 设备的时序信号;

D. 所有存储器和I/O 设备的控制信号;

E. 来自存储器和I/O 设备的响应信号;

F. 上述各项;

G. 上述C ,D 两项;

H.上述C,D和E三项。

13.微机中读写控制信号的作用是 E 。

A.决定数据总线上数据流的方向;

B.控制存储器操作读/写的类型;

C.控制流入、流出存储器信息的方向;

D.控制流入、流出I/O端口信息的方向;

E.以上所有。

14.8086 CPU工作在最大方式,引脚MX

MN/应接__地__。

15.RESET信号在至少保持4个时钟周期的高电平时才有效,该信号结束后,CPU内部

的CS为 0FFFFH ,IP为 0000H ,程序从 0FFFF0H 地址开始执行。

16.在构成8086最小系统总线时,地址锁存器74LS373的选通信号G应接CPU的 ALE 信

号,输出允许端OE应接地;数据收发器74LS245的方向控制端DIR应接DI/信号,输出允许端E应接DEN信号。

R

17.8086 CPU在读写一个字节时,只需要使用16条数据线中的8条,在一个总线周期

内完成;在读写一个字时,自然要用到16条数据线,当字的存储对准时,可在一个总线周期内完成;当字的存储为未对准时,则要在两个总线周期内完成。

T状态开始检查READY信号,__高_电平时有效,说明存储器或I/O端口准18.CPU在

3

备就绪,下一个时钟周期可进行数据的读写;否则,CPU可自动插入一个或几个等待周期(T W),以延长总线周期,从而保证快速的CPU与慢速的存储器或I/O端口之间协调地进行数据传送。

19.8086最大系统的系统总线结构较最小系统的系统总线结构多一个芯片 8288总线控制

器_。

20.微机在执行指令 MOV [DI],AL时,将送出的有效信号有 B C 。

M/信号 C.WR D.RD

A.RESET B.高电平的IO

21.设指令MOV AX,DATA 已被取到CPU的指令队列中准备执行,并假定DATA为偶地址,

试画出下列情况该指令执行的总线时序图:

(1)没有等待的8086最小方式;

(2)有一个等待周期的8086最小方式。

答:(1)没有等待的8086最小方式时序如图5.2所示。

图5.2 没有等待的8086最小方式时序(2)有一个等待周期的8086最小方式时序图如图5.3所示。

图5.3有一个等待周期的8086最小方式时序图

22.上题中如果指令分别为:

(1)MOV DA TA+1,AX

(2)MOV DA TA+1,AL

(3)OUT DX,AX (DX的内容为偶数)

(4)IN AL,0F5H

重做上题(1)。

答:(1)因为DA TA为偶地址,则DATA+1为奇地址。

故要完成本条指令,需要两个总线周期。

时序图如图5.4所示。

图5.4 执行MOV DA TA+1,AX指令的时序参考图

(2)DA TA+1虽然为奇地址,但是AL为八位存储器,故本条指令需用一个总线周期,时序图如图5.5所示。

图5.5 执行MOV DA TA+1,AL指令的时序参考图

(3)执行OUT DX,AX(DX的内容为偶数)指令的时序图如图5.6所示。

图5.6 执行OUT DX,AX指令的时序参考图

(4)执行IN AL,0F5H指令的时序图如图5.7所示。

图5.7 执行IN AL ,0F5H 指令的时序参考图

23.8086最小方式下,读总线周期和写总线周期相同之处是:在 1T 状态开始使ALE 信号变为有效 高 电平,并输出IO M/信号来确定是访问存储器还是访问I/O 端口,同时送出20位有效地址,在1T 状态的后部,ALE 信号变为 低 电平,利用其下降沿将20位地址和BHE 的状态锁存在地址锁存器中;相异之处从 2T 状态开始的数据传送阶段。