微型计算机原理 第5章(2)微机原理与接口技术(第三版)

- 格式:ppt

- 大小:880.00 KB

- 文档页数:12

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

微型计算机原理与接口技术第三版(张荣标)答案微型计算机原理与接口技术第三版答案第1章练习题1.选择题(1)B C A (2) A (3) D A (4) C2.填空(1) 10, 12(2)取出指令,执行指令(3)(4)内部码3.简答题(1)微处理器,微型计算机和微型计算机系统三者有何联系与区别?答:微处理器是把原来的中央处理单元 CPU 的复杂电路(包括运算器和控制器)做在一片或几片大规模集成电路的芯片上。

把这种微缩的 CPU 大规模集成电路称为微处理器。

微型计算机是以微处理器为核心,再配备上用大规模集成电路工艺制成的存储器和 I/O 接口就构成了微型计算机。

以微计算机为核心,再配备上系统软件、I/O 设备、辅助电路和电源就构成了微机系统。

微型计算机系统包括硬件和软件了两大部分。

(2)计算机中为什么采用二进制数表示?答:计算机是一种电器设备,内部采用的都是电子元件,用电子元件表示两种状态是最容易实现的,比如电路的通和断、电压高低等等,而且也稳定和容易控制。

把两种状态用0,1来表示,就是用二进制数表示计算机内部的数据。

(3)简述程序的运行过程。

答:即取指令—分析指令—执行指令。

根据程序计数器PC中的值从程序存储器读出现行指令,送到指令寄存器。

将指令寄存器中的指令操作码取出后进行译码,分析其指令性质,然后执行指令。

(4)设两个正的浮点数如下。

1)若是否一定有?2)若S1和S2均为规格化的数,且,是否一定有?答:1)若不一定有。

若S1 =11100101B,S2 =00100101B当P1 =01B时,P2 =10B时,故2)若S1和S2均为规格化的数,且,一定有。

浮点规格表示要求对浮点二进制正数,其尾数数字S部分的最高位必须是1,故不会出现上述情况,当时,一定有。

4.计算题(1)计算十进制数-47的原码、反码、补码(8位二进制的形式表示),并说明8位二进制原码、反码、补码所能表示的数值范围(用十进制表示)。

第二章 8086 体系结构与80x86CPU1.8086CPU 由哪两部份构成?它们的主要功能是什么?答:8086CPU 由两部份组成:指令执行部件<EU,Execution Unit>和总线接口部件<BIU,Bus Interface Unit>。

指令执行部件〔EU 主要由算术逻辑运算单元<ALU>、标志寄存器F R、通用寄存器组和E U 控制器等4个部件组成,其主要功能是执行指令。

总线接口部件<BIU>主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或者I/O 端口读取操作数参加E U 运算或者存放运算结果等。

2.8086CPU 预取指令队列有什么好处? 8086CPU 内部的并行操作体现在哪里?答: 8086CPU 的预取指令队列由6个字节组成,按照8086CPU 的设计要求, 指令执行部件〔EU 在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在C PU 内部,EU 从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU 内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086 系统中物理地址的形成过程。

8086 系统中的物理地址最多有多少个?逻辑地址呢?答: 8086 系统中的物理地址是由20 根地址总线形成的。

8086 系统采用分段并附以地址偏移量办法形成20 位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部份构成,都是16 位二进制数。

通过一个20 位的地址加法器将这两个地址相加形成物理地址。

具体做法是16 位的段基址左移4位<相当于在段基址最低位后添4个"0">,然后与偏移地址相加获得物理地址。

第1章基础知识部分1.1 计算机中常用的计数制有哪些?解:二进制、八进制、十进制(BCD)、十六进制。

1.2 什么是机器码?什么是真值?解:把符号数值化的数码称为机器数或机器码,原来的数值叫做机器数的真值。

1.3 完成下列数制的转换。

微型计算机的基本工作原理汇编语言程序设计微型计算机接口技术建立微型计算机系统的整体概念,形成微机系统软硬件开发的初步能力。

解:(1)166,A6H(2)0.75(3)11111101.01B, FD.4H(4 ) 5B.AH, (10010001.011000100101)BCD1.4 8位和16位二进制数的原码、补码和反码可表示的数的范围分别是多少?解:原码(-127~+127)、(-32767~+32767)补码(-128~+127)、(-32768~+32767)反码(-127~+127)、(-32767~+32767)1.5 写出下列真值对应的原码和补码的形式。

(1)X= -1110011B(2)X= -71D(3)X= +1001001B解:(1)原码:11110011 补码:10001101(2)原码:11000111 补码:10111001(3)原码:01001001 补码:010010011.6 写出符号数10110101B的反码和补码。

解:11001010,110010111.7 已知X和Y的真值,求[X+Y]的补码。

(1)X=-1110111B Y=+1011010B(2)X=56D Y= -21D解:(1)11100011(2)001000111.8 已知X= -1101001B,Y= -1010110B,用补码求X-Y的值。

解:111011011.9 请写出下列字符的ASCII码。

4A3-!解:34H,41H,33H,3DH,21H1.10 若给字符4和9的ASCII码加奇校验,应是多少?解:34H,B9H1.11 上题中若加偶校验,结果如何?解:B4H,39H1.12 计算下列表达式。

《微机原理与接口技术》(第三版)简介《微机原理与接口技术》是一本介绍微机原理以及接口技术的教材。

本书主要内容包括微机系统、计算机的组成与结构、内部总线结构、存储器系统、微机的中央处理器、系统总线与接口技术等。

本书旨在帮助读者全面了解微机原理和接口技术,为读者提供深入学习和研究微机原理与接口技术的基础知识。

第一章微机系统1.1 微机系统的概念和组成在本章中,我们将介绍微机系统的概念和组成。

微机系统由中央处理器(CPU)、存储器(Memory)和输入输出(I/O)设备组成。

我们将详细介绍每个组件的功能和作用,以及它们之间的关系和通信方式。

1.2 微机系统的发展历程本节将回顾微机系统的发展历程。

我们将从早期的微处理器发展到如今的微机系统,探讨微机系统在不同时期的发展和应用。

1.3 微机系统的分类微机系统可以根据不同的分类标准进行分类。

在本节中,我们将介绍微机系统的几种常见分类方式,并讨论各种分类方式的优缺点。

第二章计算机的组成与结构2.1 计算机的基本组成本章将介绍计算机的基本组成。

计算机由硬件和软件两部分组成,硬件包括中央处理器、存储器和输入输出设备,软件包括操作系统和应用软件。

2.2 计算机的结构计算机的结构是指计算机系统中各个组成部分之间的关系和交互方式。

在本节中,我们将介绍计算机的结构,并详细讨论计算机中各个组成部分之间的关系和通信方式。

第三章内部总线结构3.1 内部总线的概念和作用内部总线是计算机中各个组件之间进行数据传输的通道。

本章将介绍内部总线的概念和作用,并详细探讨内部总线在计算机系统中的重要性和应用。

3.2 内部总线的分类内部总线可以根据不同的分类标准进行分类。

在本节中,我们将介绍内部总线的几种常见分类方式,并讨论各种分类方式的优缺点。

3.3 内部总线的设计本节将介绍内部总线的设计原理和方法。

我们将讨论内部总线的带宽、传输速率、传输方式等设计参数,并详细介绍内部总线的设计流程和方法。

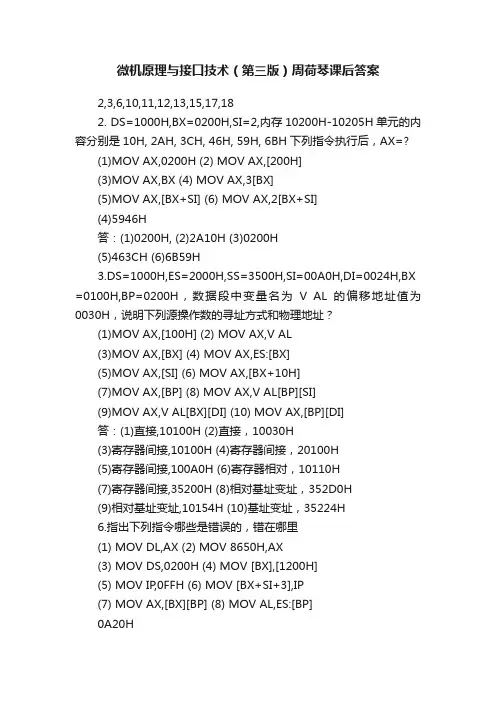

微机原理与接口技术(第三版)周荷琴课后答案2,3,6,10,11,12,13,15,17,182. DS=1000H,BX=0200H,SI=2,内存10200H-10205H单元的内容分别是10H, 2AH, 3CH, 46H, 59H, 6BH下列指令执行后,AX=?(1)MOV AX,0200H (2) MOV AX,[200H](3)MOV AX,BX (4) MOV AX,3[BX](5)MOV AX,[BX+SI] (6) MOV AX,2[BX+SI](4)5946H答:(1)0200H, (2)2A10H (3)0200H(5)463CH (6)6B59H3.DS=1000H,ES=2000H,SS=3500H,SI=00A0H,DI=0024H,BX =0100H,BP=0200H,数据段中变量名为V AL的偏移地址值为0030H,说明下列源操作数的寻址方式和物理地址?(1)MOV AX,[100H] (2) MOV AX,V AL(3)MOV AX,[BX] (4) MOV AX,ES:[BX](5)MOV AX,[SI] (6) MOV AX,[BX+10H](7)MOV AX,[BP] (8) MOV AX,V AL[BP][SI](9)MOV AX,V AL[BX][DI] (10) MOV AX,[BP][DI]答:(1)直接,10100H (2)直接,10030H(3)寄存器间接,10100H (4)寄存器间接,20100H(5)寄存器间接,100A0H (6)寄存器相对,10110H(7)寄存器间接,35200H (8)相对基址变址,352D0H(9)相对基址变址,10154H (10)基址变址,35224H6.指出下列指令哪些是错误的,错在哪里(1) MOV DL,AX (2) MOV 8650H,AX(3) MOV DS,0200H (4) MOV [BX],[1200H](5) MOV IP,0FFH (6) MOV [BX+SI+3],IP(7) MOV AX,[BX][BP] (8) MOV AL,ES:[BP]0A20H(9) MOV DL,[SI][DI] (10)MOV AX,OFFSET(11) MOV AL,OFFSET TABLE (12)XCHG AL,50HOUT AL,0FFEH(13)(14)IN BL,05H答:(1)长度不匹配(2)立即数不能做目的操作数(3)段寄存器不能用立即数赋值(4)不能两个内存(5)IP不能用指令直接修改(6)指令中不能出现IP(7)BX/BP应与SI/DI搭配(8)对(9)SI/DI 应与BX/BP搭配(10)OFFSET后应该内存(11)应用AX (12)不能立即数(13)IN必须用AL/AX (14)操作数反;地址应为8位10. 某班有7个同学英语成绩低于80分,分数存在字节类型ARRAY数组中,编程完成:(1)给每人加5分,结果存到NEW数组中(2)把加分后的总分存到字类型SUM单元中(3)把加分后的平均分存到字节类型A VERAGE单元中答:ARRAY DB 79,78,77,76,77,78,79NEW DB 7 DUP(?)SUM DW 1 DUP(?)A VERAGE DB 1 DUP(?)MOV DS, AXMOV ES, AXLEA SI,ARRAYLEA DI,NEWMOV CX,7CLDREP MOVSBMOV CX,7MOV AX,0LEA SI,NEWADD5: ADD BYTE PTR[SI],5ADD AL,[SI]ADC AH,0SIINCLOOP ADD5MOV SUM,AXMOV BL,7DIV BLMOV A VERAGE,AL11.AX=2508H,BX=0F36H,CX=0004H,DX=1864H,下列指令执行后结果是多少,标志位CF=?(1) AND AH,CL (2) OR BL,30HXOR CX,0FFF0H(4)(3)NOT AX(5) TEST DH,0FH (6) CMP CX,00H(7) SHR D X,CL (8) SAR A L,1(9) SHL BH,CL (10) SAL AX,1B X,1 (12)ROR DX,CLRCL(11)答:(1)AX=0408H,CF=0 (2)BX=0F36H,CF=0(3)AX=0DAF7H,CF不变(4)CX=0FFF4H,CF=0(5) DX=01864H,CF=0 (6)CX=0004H,CF=0(7)DX=0186H,CF=0 (8)AX=2504H,CF=0(9)BX=0F036H,CF=0 (10)AX=4A10H,CF=0(11)BX=1E6C/1E6DH,CF=0 (12)DX=4186H,CF=012.数据段定义如下:DATA SEGMENTComputer&PersonalTV’DB‘TheSTRINGDATA ENDS用字符串操作等指令完成以下功能:(1)把该字符串传送到附加段中偏移量为GET_CHAR开始的内存单元中(2)比较该字符串是否与’The computer’相同,若相同则将AL寄存器的内容置1,否则置0,并将比较次数送到BL寄存器(3)检查该字符串是否有’&’符,若有则用空格符替换(4)把大写字母传送到附加段中以CAPS开始的单元中,其余字符传送到以CHART 开始的单元,然后将数据段中存储上述字符串的单元清零。

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成它们的主要功能是什么答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处8086CPU内部的并行操作体现在哪里答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个逻辑地址呢答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

&电子工业出版社&第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

微机原理与接口技术第三版要点填空题:第一章1,微处理器是指包含有运算器、控制器、寄存器组以及总线接口等部件的一块大规模集成电路芯片,负责对计算机系统各部件进行统一协调和控制;微型计算机以微处理器为核心,配置存储器、输入/输出设备、接口电路和总线等器特点是功能强、体积小、质量轻、价格低、可靠性高、结构灵活、适应性强、应用面广、维护方便2,主存容量是指主存储器中RAM和ROM的总和,他是衡量卫星计算机处理数据能力的一个重要指标;构成主存的器件通常采用半导体存储器RAM和ROM6,ASCII码可以表示128种字符,其中起控制作用的称为功能码,供书写程序和描述命令使用的成为信息码。

第二章1,8086的内部结构由执行部件EU和总线接口部件组成,前者功能是从BIU指令队列中取出指令代码,经指令译码后执行指令规定的全部功能,后者的功能是根据EU请求,完成CPU与存储器或I/O 设备间数据传送。

2,8086取指令时,会选取CS 作为段基值,再加上那个由IP提供的偏移地址形成20位物理地址。

3,8086有两种外部中断请求,他们分别是可屏蔽中断请求信号INTR 和非屏蔽中断请求信号NMI。

7,时钟周期是指cpu基本时间计量单位,由主频来决定总线周期是指执行总线操作所需时间,总线操作是指经外部总线对存储器或I/O端口进行一次信息输入或输出的过程。

8,8086工作在最大方式时CPU引脚MN/MX应接 +5V高电平,最大和最小工作方式的应用场合分别是多处理器系统和单处理器系统。

第三章1,计算机指令通常由操作码字段和操作数字段两部分组成,指令对数据操作时,按照数据的存放位置可分为立即数、寄存器操作数和存储器操作数。

2,寻址的含义是指寻找操作数的过程;8086指令系统的寻址方式按照大类可分为操作数寻址和I/O 端口寻址;其中寻址速度最快的是立即数寻址。

3,指令MOV AX,ES:[BX+0100H]中,源操作数位于内存单元中;读取的是附加段数据段的存储单元内容。

第1章基础知识部分1.1 计算机中常用的计数制有哪些?解:二进制、八进制、十进制(BCD)、十六进制。

1.2 什么是机器码?什么是真值?解:把符号数值化的数码称为机器数或机器码,原来的数值叫做机器数的真值。

1.3 完成下列数制的转换。

微型计算机的基本工作原理汇编语言程序设计微型计算机接口技术建立微型计算机系统的整体概念,形成微机系统软硬件开发的初步能力。

解:(1)166,A6H(2)0.75(3)11111101.01B, FD.4H(4 ) 5B.AH, (10010001.011000100101)BCD1.4 8位和16位二进制数的原码、补码和反码可表示的数的范围分别是多少?解:原码(-127~+127)、(-32767~+32767)补码(-128~+127)、(-32768~+32767)反码(-127~+127)、(-32767~+32767)1.5 写出下列真值对应的原码和补码的形式。

(1)X= -1110011B(2)X= -71D(3)X= +1001001B解:(1)原码:11110011 补码:10001101(2)原码:11000111 补码:10111001(3)原码:01001001 补码:010010011.6 写出符号数10110101B的反码和补码。

解:11001010,110010111.7 已知X和Y的真值,求[X+Y]的补码。

(1)X=-1110111B Y=+1011010B(2)X=56D Y= -21D解:(1)11100011(2)001000111.8 已知X= -1101001B,Y= -1010110B,用补码求X-Y的值。

解:111011011.9 请写出下列字符的ASCII码。

4A3-!解:34H,41H,33H,3DH,21H1.10 若给字符4和9的ASCII码加奇校验,应是多少?解:34H,B9H1.11 上题中若加偶校验,结果如何?解:B4H,39H1.12 计算下列表达式。