FPGA的USB模块实现

- 格式:pdf

- 大小:853.29 KB

- 文档页数:36

基于FPGA的USB接口IP核设计USB(通用串行总线)作为一种外设连接技术,是计算机外设连接技术的重大变革,USB具有速度快、通用性好、扩展性强、功耗低、稳定、易开发等众多优点,在实践中获得了广泛的应用,逐步成为PC机的一种标准接口。

USB接口控制芯片是实现USB设备与主机建立通信所必须的芯片,目前国内的USB开发者所采用的芯片都是由国外的芯片商所提供,如Cypress、NEC、Motorola等大的IC设计公司,价格较贵。

由于USB的广泛应用,国内外众多科研机构和集成电路设计公司都把目光投向USB这项具有广阔市场前景的技术。

USB内核(USB Core)是USB接口控制芯片的关键模块,设计一个稳定、高速的USB内核更是芯片成功推向市场的前提。

1 USB通信原理USB通信逻辑上分成了3层:信号层、协议层和数据层。

信号层用来实现在USB 设备和主机的物理连接之间传输位信息流的信息。

逻辑层用来实现在USB设备和USB主机端的协议软件之间传输包字节流的信息,它们在信号层被编码成NRZI位信息后传送出去。

数据传输层用来实现在USB主机端的客户端驱动程序和设备端的功能接口之间传输有一定意义的信息,这些信息在协议层被打包成包格式。

1.1 传输的基本单元包(Packet)是USB系统中信息传输的基本单元。

结构,如图1所示,根据USB 规范,包的类型有:令牌包、数据包、握手包和专用包。

USB总线操作(通讯过程)都可以归结为3种包的传输:令牌包、数据包和应答包。

任何操作都是从主机开始的,主机以预先排好的时序,发出一个描述操作类型、方向、外设地址以及端点号,称之为令牌包Foken Packet。

然后由在令牌中指定的数据发送者发出一个数据包Data Packet或者报告它没有数据可以传输。

而数据的目的地一般要以一个应答包Handshake Packet做出响应表明传输是否成功。

1.2 事务处理事务处理(Transaction)是指USB总线上数据信息的一次接收或发送的处理过程。

基于Verilog的FPGA与USB 2.0高速接口设计2009-04-28 14:41:36 来源:与非网关键字:Verilog FPGA USB2.0高速接口设计0 引言USB(通用串行总线)是英特尔、微软、IBM、康柏等公司1994年联合制定的一种通用串行总线规范,它具有数据传输速度快,成本低,可靠性高,支持即插即用和热插拔等优点,迅速得到广泛应用。

在高速的数据采集或传输中,目前使用较多的都是采用USB 2.0接口控制器和FPGA或DSP实现的,本设计在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作为外部主控制器实现对FX2 USB内部的FIFO进行控制,以实现数据的高速传输。

该模块可普遍适用于基于USB 2.0接口的高速数据传输或采集中。

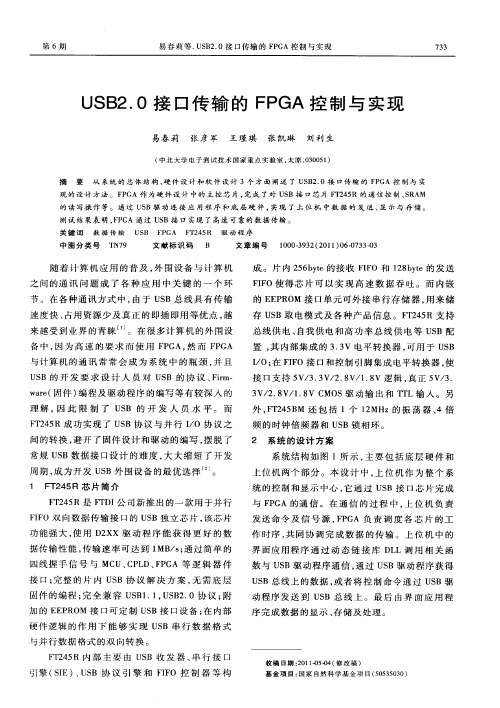

l 系统硬件模块设计1.1 系统硬件框图图1中展示了Slave FIFO方式下FX2 USB和FPGA的典型连接。

其中,FD[7..O]为8位双向数据总线FLAGA~FLAGC 为FX2内FIFO的标志管脚,映射FIFO的当前状态;SLCS为Slave FIFO的片选信号;SLOE用于使能数据总线FD的输出;FIFOADR[1..0]用于选择和FD连接的端点缓冲区(00代表端点2,01代表端点4,10代表端点6,11代表端点8);SLRD和SLWR可分别作为FIFO的读写选通信号。

1.2 USB 2.0接口芯片CY7C680131.2.1 CY7C68013的结构特点Cypress公司的USB FX2是第一个包含USB 2.0的集成微控制器,它内部集成了1个增强型的8051,1个智能USB 串行接口引擎,1个USB数据收发器,3个8位I/O口,16位地址线,8.5 KB RAM和4 KBFIFO等。

增强性8051内核完全与标准8051兼容,而性能可达到标准8051的3倍以上。

其框图如图2所示。

1.2.2 CY7C68013的工作模式CY7C68013有Ports模式、Slave FIFO和GPIF三种接口方式。

㊀㊀文章编号:1009-2552(2019)02-0116-05㊀㊀DOI:10 13274/j cnki hdzj 2019 02 026基于FPGA的USBPD控制器设计与实现张烨晨ꎬ刘有耀ꎬ崔㊀盼(西安邮电大学电子工程学院ꎬ西安710061)摘㊀要:USBPD是目前市场上主流的快充技术ꎬ在嵌入式系统中集成USBType ̄C接口与USBPD技术是必然的发展趋势ꎬ文中采用自顶向下的模块化方法设计一种基于PIC微处理器的USBPD控制器ꎬ详细介绍了USBPD控制器发送机㊁接收机和状态机的设计ꎮ使用FPGA仿真器㊁USBPD协议测试仪和示波器作为验证平台ꎬ经实测ꎬ表明控制器发送和接收数据过程均符合USBPD数据传输标准ꎮ该USBPD控制器减小了硬件电路面积ꎬ具有成本低㊁易扩展的优点ꎬ可广泛应用于USBPD快速充电系统设计中ꎮ关键词:USBType ̄CꎻUSBPD控制器ꎻPIC微处理器ꎻFPGA中图分类号:TN492㊀㊀文献标识码:ADesignandimplementationofUSBPDcontrollerbasedonFPGAZHANGYe ̄chenꎬLIUYou ̄yaoꎬCUIPan(SchoolofElectronicEngineeringꎬXi anUniversityofPostsandTelecommunicationꎬXi an710061ꎬChina)Abstract:USBPDisthemainstreamfast ̄chargingtechnologyonthemarket.IntegratingUSBType ̄CinterfaceandUSBPDtechnologyinembeddedsystemsistheinevitabletrend.Atop ̄downmodularapproachisusedtodesignaPIC ̄basedmicroprocessor.ThisarticlepresentsdetailsofthedesignoftheUSBPDcontrollertransmitterꎬreceiverandstatemachine.UsingtheFPGAemulatorꎬUSBPDprotocoltesterandoscilloscopeastheverificationplatformꎬtheresultsoftestsshowthatallthesendingandreceivingofdataisinaccordancewiththeUSBPDdatatransmissionstandard.TheUSBPDcontrollerreducescircuitareaofhardwareꎬwiththeadvantagesoflowcostandeasyexpansionꎬwhichcanbewidelyusedinthedesignoftheUSBPDfast ̄chargingsystem.Keywords:USBType ̄CꎻUSBPDControllerꎻPICMicroprocessorꎻFPGA收稿日期:2018-10-10作者简介:张烨晨(1993-)ꎬ男ꎬ硕士研究生ꎬ研究方向为电路与系统ꎮ0㊀引言USBType ̄C[1]接口具有体积更小㊁正反可插㊁供电更强㊁快速高效和兼容性佳等优点ꎬ在消费类电子产品接口市场中得到了广泛应用[2]ꎮ与传统的USB接口相比ꎬ最大的吸引点在于USBType ̄C接口重新定义了一条CC线ꎬUSB电力传输(UniversalSerialBusPowerDeliveryꎬUSBPD)协议就是基于CC线实现的ꎬ与Type ̄C接口的结合可通过单根线缆提供更灵活的电力和数据传输ꎬ实现USB功能的最大化[3]ꎬ因此USBPD是USBType ̄C接口的灵魂所在ꎮ随着智能手机的飞速发展ꎬ设备的续航能力已成为用户使用体验上的最大痛点[4]ꎮ在锂电池技术没有太大的突破下ꎬ通过增加手机充电功率ꎬ减少手机充电所需等待的时间ꎬ就是一种改善续航的 曲线救国 方案ꎮUSBType ̄C接口和USBPD的结合很好地契合了这一方案的需求ꎮ自从Cypress推出了全球首款USBPD控制器芯片以来ꎬ各大芯片公司纷纷抢夺市场ꎮ目前国内能够自主研发USBPD控制器芯片的公司屈指可数ꎬ因此研究USBPD控制器不仅可以掌握核心的技术ꎬ还可以创造可观的经济效益ꎮ本文的USBPD控制器基于PIC微处611理器实现ꎬ并利用FPGA平台进行验证ꎮ1㊀USBPD控制器架构USBPD控制器主要包括PD发送机㊁PD接收机和发送接收波特率控制单元ꎮUSBPD控制器架构如图1所示ꎬ本设计中采用自顶向下模块化的设计方法ꎬ使用Verilog硬件描述语言建立模型ꎬUSBPD控制器主要是负责数据的发送㊁接收以及协议处理ꎮ图1㊀USBPD控制器架构PD发送机的任务是接收来自协议层的初始数据包ꎬ然后在物理层按照USBPD协议规定的消息格式给初始数据包添加前导码㊁SOP㊁CRC32计算和EOPꎬ对数据包各部分(除前导码之外)进行4B5B编码ꎬ最后对数据包进行BMC编码ꎬ组成一组完整的数据包经CC信道发送到外部接收端[5]ꎮPD接收机的任务是接收CC信道上来自外部发送端的数据包ꎬ对其进行BMC解码ꎬ检测SOP包ꎬ进行5B4B译码接收到的数据包(包括CRC32)ꎬ最后检测EOP并进行CRC32校验ꎮ如果CRC32校验有效ꎬ向协议层发送数据ꎻ如果CRC32校验无效ꎬ丢失接收到的数据包[6]ꎮ在PD波特率控制单元中对发送和接收时间分别设定不同波特率进行数据发送和接收ꎮ2㊀USBPD控制器硬件设计2.1㊀波特率控制单元设计数据发送和接收波特率示意图如图2所示ꎮ本设计中采用MCT0和MCPR0作为发送和接收波特率控制ꎬ分别设定不同波特率进行数据发送和接收ꎮCC信道上的标准位速率为300kHzꎮ波特率由MCPR0决定ꎬ如系统时钟为20MHzꎬMCPR0=20MHz/300kHz-1=66ꎮ采样波特率由MCTCON寄存器中MSAMPLE[5ʒ0]决定ꎬ其计算公式为20MHz/300kHz/4=16ꎮ采样波特率是由MCT0S计数ꎬ当MCT0S与MSAMPLE[5ʒ0]相等时ꎬ标志位SCNT_SYNC置1说明第一次采样完成ꎬ并且BMCR_SCNT自加1ꎬ重复此过程ꎬ直至MCT0与MCPR0相等时ꎬBMCR_SCNT会从3重置为0ꎬ说明对一个位采样完成ꎮ图2㊀波特率示意图2.2㊀发送机模块设计发送机的设计总体框图如图3所示ꎬPDTX_STATE和MC_STATE分别是发射状态机和BMC编码状态机ꎬ前者主要是对数据进行组包ꎬ后者是对组包的数据进行BMC编码ꎮ图3㊀发送机总体框图首先ꎬ物理层接收来自协议层的初始数据包(Header和Data)ꎬ为其添加前导码㊁SOP㊁CRC32计算和EOP部分ꎮ将完整的数据包发送至DATA_TRANS模块ꎬ将数据包中的Header和Data依次传入CRC32模块中进行CRC32计算ꎬ将计算出的结果又返回至DATA_TRANS模块ꎮ其次ꎬSOP㊁Head ̄er㊁Data㊁CRC32计算值和EOP都进入4B5B模块进行编码ꎮ同时PDTX_STATE状态机模块对输入的数据选择性的处理组成完整的数据包并输出ꎮ最后ꎬ将数据包中的所有比特依次传入MC_STATE状态机模块进行BMC编码ꎬ编码后的数据会回传至PDTX_STATE状态机模块中ꎬ最后的数据包从PDTX_DATA输出至CC信道ꎮ①CRC32计算模块为了防止协议层的数据包(Header和Data)在传递过程中受到损坏或者丢失ꎬ因此对数据包的Header以及Data部分进行了CRC32计算ꎬ起到了711保护数据的作用ꎮ②4B5B编码模块本设计中对整个数据包(除了前导码之外)进行4B5B编码ꎬ将数据包以8比特为一组传至4B5B编码模块ꎬ编码后的数据存放在BMC_THBUF[4ʒ0]和BMC_TLBUF[4ʒ0]寄存器中ꎮ③发送状态机模块如图4所示ꎬ发送机在没有使能的情况下一直处于TX_IDLE状态ꎬ一旦使能打开ꎬ说明协议层有数据传入ꎮ当LOADEN0和LOADEN1同时为1时ꎬ发送状态机处于TX_WAIT状态ꎬ等待数据到来ꎮTX_SYNC是同步状态ꎬ用来判断是否存在延迟0的个数ꎬ如果没有延迟0的个数ꎬ将进入TX_OK状态说明发送完成ꎻ如果有延迟0的个数ꎬ将进入TX_DLY状态ꎬ若DLY_OK为0时ꎬDLY_CNT就会递减ꎬ直至DLY_CNT的值为0ꎬDLY_OK标志位会自动置1ꎬ此刻进入TX_OK状态说明数据发送完成ꎮ图4㊀PD发送状态机TXBUF[9ʒ0]寄存器中存放的数据高位在前低位在后ꎬ逐位发送且低位在前高位在后ꎬTXBUF[9ʒ0]在发送数据过程中时ꎬPDTXIF会置0ꎬ且BM ̄CTH[4ʒ0]和BMCTL[4ʒ0]寄存器被锁存ꎬ无法写入数据ꎮ当TXBUF[9ʒ0]数据发送完成ꎬPDTXIF会自动置1ꎮTXBUF[9ʒ0]发送数据时处于TX_BUF状态ꎬ当数据在发送过程中TX_CNT会递减且TX_OK标志位为0ꎬ直至TX_CNT减到1时ꎬ说明数据发送完成ꎬTX_OK标志位自动置1并进入TX_OK状态ꎮ若发送缓冲区标志位PDTXBF为1ꎬ说明发送缓冲区正在发送且处于TX_BUF状态ꎬ若发送缓冲区标志位PDTXBF为0ꎬ说明发送缓冲区发送完成且处于TX_OK状态ꎮ④BMC编码模块双向符号编码(BiphaseMarkCodingꎬBMC)是用于传递USBPD信息的一种编码方式ꎮ这种方式采用专用DC连接ꎬ通过CC线来标识[6]ꎮ在BMC中ꎬ每个位时间开始(UI)都有一次转换ꎬ并且在发送1时在UI的中间会有第二个转换ꎮBMC能进行有效的DC平衡(每个1都是DC平衡的ꎬ并且2个连续的0也是DC平衡的ꎬ不考虑1的反转次数)ꎮBMC的编码方式原理图如图5所示ꎮ图5㊀BMC编码原理如图6所示ꎬMC_00和MC_11表示0对应的BMC编码状态ꎬMC_01和MC_10表示1对应的BMC编码状态ꎮ本设计中是通过对TX_BUF状态下每一位数据进行BMC编码ꎬ状态机初始状态是MC_00ꎬ是因为发送端初始为低电平ꎮBMC编码后的信号必须满足CC信道传输的要求ꎬ会在发送每位数据中间进行一次检测ꎮ处于MC_00状态ꎬPDTX_DATA发送0ꎻ处于MC_11状态ꎬPDTX_DA ̄TA发送1ꎻ处于MC_01状态ꎬ当BMCR_SCNT为00时ꎬPDTX_DATA发送0ꎬ当BMCR_SCNT为10时ꎬPDTX_DATA发送1ꎻ处于MC_10状态ꎬ当BMCR_SCNT为00时ꎬPDTX_DATA发送1ꎬ当BMCR_SCNT为10时ꎬPDTX_DATA发送0ꎮ当MCT0与MCPR0相等且BMCR_SCNT为11时ꎬ说明一个数据BMC编码且发送完成ꎮ2.3㊀接收机模块设计接收机的设计总体框图如图7所示ꎮ图中PDRX_STATE是接收状态机ꎬ主要是对接收到的数据包进行解包ꎮ首先ꎬ对来自CC信道的输入数据进行了BMC解码ꎬ对解码后的数据进行倒序高位在前低位在后ꎬ同时根据来自状态机PDRX_STATE以及PD接收标811图6㊀BMC编码状态机图7㊀接收机总体框图志状态位ꎬ接收并解码各个部分的数据ꎮ其次ꎬ对数据进行5B4B解码ꎮ最后将5B4B解码后的数据发送到CRC32中计算新的CRC32计算值ꎬ将新旧CRC32计算值对比ꎬ若相同ꎬ说明数据包正确ꎬ将其传输至接收机的协议层ꎬ若不同ꎬ说明数据包错误ꎬ将其丢弃掉ꎮ①BMC解码模块接收机通过Type ̄C接口的CC信道接收来自发射机的编码数据ꎬ因为在CC信道上传递的数据都需要BMC编码ꎬ所以接收机要对接收到的数据进行BMC解码[6]ꎮ本设计中我们对CC信道上接收到的数据BMCR_CCDAT进行采样ꎬ当BMCR_SCNT为01且SCNT_SYNC为1时ꎬ将BMCR_CCDAT的数据传给BMCR_SDAT[0]ꎬ当BMCR_SCNT为11且SCNT_SYNC为1时ꎬ将BMCR_CCDAT的数据传给BMCR_SDAT[1]ꎬ根据采样波特率对接收到的每一比特进行两次采样ꎬ然后两次采样的结果进行异或运算ꎬ异或的结果即就是BMC解码的数据ꎬ每接收完1比特ꎬ用MCTSYN_EN作为结束标志位ꎮ这样就对前导码㊁SOP㊁Header㊁Data以及EOP解码完成ꎮ②5B4B解码模块将经过BMC解码后的Header㊁Data和CRC32数据存入BMC_RLBUF[4ʒ0]和BMC_RHBUF[4ʒ0]进行5B4B解码ꎬ最后的原始数据以8比特一组从BMCR5T4寄存器输出ꎮ③接收状态机模块图8㊀接收机状态图如图8所示ꎬ接收机在没有使能的情况下一直处于IDLE状态ꎬ一旦使能打开ꎬ说明外部有数据传入ꎮ首先进入WAIT状态ꎬ等待接收数据ꎬ当BMCR_SYNC[0]为0且BMCR_SYNC[1]为1时进入SFIRST状态ꎮ当BMCR_SYNC[0]为1且BMCR_SYNC[1]为0时进入接收前导码状态ꎬ同时Pream ̄ble_cnt[5ʒ0]作为前导码的计数器ꎬ为了准确无误的接收到前导码ꎬ对BMC解码后的前导码进行检测ꎬ当满足条件后Preamble_cnt[5ʒ0]会自加1ꎬ并且在Preamble_cnt[5ʒ0]计数到63时说明前导码接收完成ꎬSYNC64_FLAG标志位会置1ꎮ然后进入SYN1状态ꎬ检测并接收完SOP中第一个SYNC时SYNC1_FLAG标志位会置1ꎬ必须用软件对SYNC1_FLAG标志位清零ꎮ为了简化接收机的设计ꎬ其余三个SYNC或RST代码都在DATA状态中ꎬ并且用BMCRCNT[2ʒ0]作为计数器ꎬ当检测到SOP中第二个SYNC时SYNC1_FLAG会置1ꎬ然后再用软件清零ꎮ直到检测并接收完SOP中第四个SYNC时才对SOP检测完成ꎮ在Header和Data接收完成之911后ꎬDATA_FLAG标志位会置1ꎬ并且会用软件对其清零ꎮ最后ꎬEOP_FLAG标志位为1时说明EOP接收完成ꎬ跳转至IDLE状态ꎮ当接收数据发生错误时ꎬ也会返回到IDLE状态ꎮ④CRC32计算模块在数据进行5B4B解码之后ꎬ将得到的4比特输出数据传输至CRC32计算模块中进行CRC32计算ꎬ计算得到的结果与接收到的CRC32进行对比ꎬ若两者值相等ꎬ把接收到的数据包传输至协议层ꎬ若两者值不相等ꎬ丢掉接收到的数据包ꎮ3㊀结果验证USBPD控制器挂接在嵌入式系统中ꎬ采用Al ̄terQuartusII工具综合出门级网表电路ꎬ选用AlterCycloneIVEP4CE6E22C8NFPGA仿真器以及USBPD(POWER ̄Z)协议测试仪和示波器作为验证平台ꎮUSBPD控制器模块采用PIC系统时钟20MHzꎬ确保CC信道上位速率的正确性ꎬ数据来自协议层ꎬ本文中数据由软件产生并且生成HEX文件烧录至仿真器中ꎮ验证平台如图9所示ꎮ图9㊀FPGA验证平台为检验USBPD控制器的数据传输是否符合USBPD协议标准ꎬ使用数字示波器采样CC传输信道的波形进行验证ꎮPD协议测试仪可作为用户端(吸端)ꎬ将其设置为Monitor模式ꎬ在系统上电之后ꎬ仿真器(源端)检测到有设备插入ꎬ会将自身的供电能力传输给用户端(吸端)ꎮ通过示波器对Type ̄C的CC线进行捕获ꎬ如图10所示ꎮ第一个数据包是源端提供给接吸端的5V/3A供电能力包(Source_Capability命令)ꎬ是来自协议层的数据(Header和Data) 111a0001912c 进入物理层后ꎬ添加前导码㊁SOP㊁CRC32计算和EOP形成一组完整的数据包ꎮ第二个数据包是吸端成功接收到源端的数据后判定其符合USBPD协议规范ꎬ并且返回GoodCRC控制命令ꎬ在源端成功接收到GoodCRC命令之后会将PC0的电平拉高ꎬ此通信过程说明USBPD控制器设计满足要求ꎮ图10㊀CC通道数据包采样4㊀结束语本文研究了USBPD协议中的消息格式与消息类型以及通信交互机制ꎮ基于此设计并实现了一种基于PIC微处理器的USBPD控制器ꎬ对各个模块的设计进行VCS+Verdi的功能仿真ꎬ并且经过FP ̄GA平台验证ꎬ验证结果表明PIC微处理器加载USBPD驱动程序可以实现PD数据正确收发ꎮUSBPD控制器硬件电路实现简单ꎬ在提升系统性能的同时降低了成本ꎬ且具有极大的扩展性ꎬ可根据后期的需求对软件进行修改ꎮ为了进一步研究ꎬ后期工作将实现USBPD快速充电智能管理系统ꎮ参考文献:[1]俞德军.基于USBTYPE ̄C协议的大功率智能电源技术研究[D].成都:电子科技大学ꎬ2018.[2]阮颐ꎬ宋清亮ꎬ王甲ꎬ等.USBType ̄C与PD技术概述与应用[J].集成电路应用ꎬ2017ꎬ34(4):31-36.[3]李勇.USBPD在移动设备快速充电中的新兴应用[J].电子产品世界ꎬ2018ꎬ25(9):27-30.[4]惠惠.支持快充协议的充电接口芯片XD9523的研究与设计[D].西安:西安电子科技大学ꎬ2017.[5]黄勇华.USBPD协议中VDM消息的实现[D].大连:大连理工大学ꎬ2016.[6]李生晖.基于Type_C接口的USB_PD协议的设计与实现[D].西安:西安电子科技大学ꎬ2017.责任编辑:梁毅菲021。

收稿日期:2019年11月16日,修回日期:2019年12月19日作者简介:牛雨萌,女,硕士研究生,研究方向:集成电路系统设计。

焦继业,男,高级工程师,研究方向:集成电路系统设计。

李晨,女,硕士研究生,研究方向:嵌入式系统开发。

∗1引言目前市场上新发布的主流手机机型,已全面开始使用USB Type-C [1]接口,且飞利浦、乐视等厂商已经推出USB Type-C 接口的数字耳机,USB Type-C 在消费类电子市场中得到了广泛应用[2]。

相比于传统USB 接口[3],最大的不同在于USB Type-C 接口中新定义了一条CC 线,USB PD [4]协议就是基于USB Type-C 接口中的CC 线实现的,它是一种主从单线通讯协议,不仅是用于实现快速充电的协议,实际上,USB PD 是USB Type-C 的灵魂所在。

它与USB Type-C 接口的结合可支持高达20V/5A 的标准电能传输,利用协议中的VDM [5]消息建立Type-C 替代模式的连接,可实现DisplayPort [6~7]、HDMI [8]等高速数据传输,具有良好的应用前景[9]。

本文设计并实现了一种USB PD 控制器,完成了PD 数据包的正确发送、接收及校验,并利用FP ⁃GA 进行验证[10]。

FPGA (Field-Programmable Gate Array ),即现场可编程门阵列,具有丰富的可编程逻辑单元、嵌入式块RAM 、可编程输入输出单元等硬件资源,可以在其内部灵活实现各种数字电路设计。

因此,采用FPGA 技术进行验证,可以快速修改代码中的错误,为后续的IC 设计提供正确保障。

基于FPGA 的USB PD 控制器的设计与实现∗牛雨萌焦继业李晨(西安邮电大学电子工程学院西安710121)摘要USB PD 协议可以使USB Type-C 接口集数据、电能、视频传输于一体,其核心点是通过PD 控制器来控制USBType-C 接口中CC 线上的数据通信。

可编程器件应用 电 子 测 量 技 术 ELECTRONIC MEASUREMENT TECHNOLOGY第34卷第10期2011年10月 基于FPGA的USB数字I/O设备设计王晓利 龙 兵 李 力(电子科技大学自动化工程学院 成都 611731)摘 要:从系统硬件设计和软件设计2个方面阐述了USB数字I/O设备的设计方法。

本次设计依据USB 2.0通信协议,以FPGA逻辑为核心控制器件,实现与USB接口芯片CY7C68013的通信控制,多通道数据的存储、读取、发送和采集。

较为详细的论述了该设备的软硬件设计及实现,介绍了整体设计思路、硬件总体架构和软件流程,并且对程序进行了仿真。

关键词:USB;FPGA;CY7C68013;中图分类号:TP202 文献标识码:AUSB digital I/O device design based On FPGAWang Xiaoli Long Bing LI Li(School of Automation Engineer,UESTC,Chengdu 611731)Abstract:This article from the hardware design and software design two aspects the USB digital I/O device designmethod.USB 2.0communication protocol,according to the FPGA logic control as the core control devices,realize theUSB interface chip CY7C68013communication control,multi-channel data storage,read,send and acquisition.Moredetailed describes the design and realization of the software and hardware equipment,this paper programs.Keywords:USB;FPGA;CY7C68013 本文于2011年7月收到。

苏州经贸职业技术学院机电系电信专业毕业设计论文基于FPGA算法的USB设备接口的设计学生姓名:崔娣指导教师: 徐进2010年1月目录摘要............................................................... I I 第1章绪论 (1)1.1USB技术研究现状 (1)1.1.1 USB速度快 (1)1.1.2 USB设备安装和配置容易 (1)1.1.3 USB易于扩展 (1)1.1.4 USB独立供电 (1)1.1.5 USB支持多媒体 (1)1.2FPGA的概念 (1)1.2.1 FPGA的概念 (1)1.2.2 Altera的APEX系列器件 (2)1.3实现FPGA技术需要的硬件描述语言VHDL (2)1.3.1 VHDL的特点 (2)第2章 USB2.0协议介绍及USB设备控制器结构原理 (3)2.2传输速率 (3)2.3端点 (4)2.4数据解码/编码 (4)2.5USB传输 (4)2.6与外部微型控制器接口 (5)2.7USB协议控制器的模块划分 (5)2.8控制器顶层引脚定义 (7)第3章USB设备控制器设计 (8)3.1USB接口控制器功能设计 (8)3.2VHDL实现 (8)3.2.1存储器接口及存储器仲裁器 (8)3.2.2应用程序的WishBone接口 (9)3.3USB协议处理层 (10)第4章USB设备控制器的FPGA实现 (14)4.1器件的选择 (14)4.2编译和仿真 (14)结论 (15)参考文献 (15)致谢 (15)附录 (16)摘要通用串行总线(USB)是PC体系中比较新的一套工业标准。

它是为了解决日益增加的PC外设与有限的主板插槽、端口之间的矛盾.提高设备的传输速度和简化PC与外设的连接过程而出现的。

自从2000年提出USB2.0协议,短短几年间。

USB不光成为了微机主板上的标准端口,而目还成为了所有微机外设(包括键盘、鼠标、显示器、打印机、数码相机、扫描仪等等)与主机相连的标准协议之一。