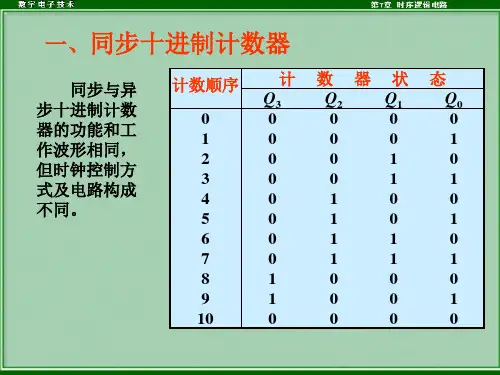

集成十进制同步计数器

- 格式:ppt

- 大小:315.00 KB

- 文档页数:9

同步和异步十进制加法计数器的设计全文共四篇示例,供读者参考第一篇示例:同步和异步是计算机系统中常用的两种通信机制,它们在十进制加法计数器设计中起到了至关重要的作用。

在这篇文章中,我们将深入探讨同步和异步十进制加法计数器的设计原理及应用。

让我们来了解一下十进制加法计数器的基本概念。

十进制加法计数器是一种用于执行十进制数字相加的数字电路。

它通常包含多个十进制加法器单元,每个单元用于对应一个十进制数位的运算。

在进行加法操作时,每个数位上的数字相加后,可能会产生进位,这就需要进位传递的机制来满足计数器的正确操作。

在同步十进制加法计数器中,每个十进制加法器单元都与一个时钟信号同步,所有的操作都按照时钟信号的节拍来进行。

具体来说,当一个数位的加法计算完成后,会将结果通过进位端口传递给下一个数位的加法器单元,这样就能确保每个数位的计算都是按照特定的顺序来进行的。

同步十进制加法计数器的设计较为简单,在时序控制方面有很好的可控性,但由于需要受限于时钟信号的频率,其速度受到了一定的限制。

在实际应用中,根据不同的需求可以选择同步或异步十进制加法计数器。

如果对计数器的速度要求较高,并且能够承受一定的设计复杂度,那么可以选择异步设计。

如果对计数器的稳定性和可控性要求较高,而速度不是首要考虑因素,那么同步设计可能更为适合。

无论是同步还是异步,十进制加法计数器的设计都需要考虑诸多因素,如延迟、数据传输、进位控制等。

通过合理的设计和优化,可以实现一个高性能和稳定的十进制加法计数器,在数字电路、计算机硬件等领域中有着广泛的应用。

同步和异步十进制加法计数器的设计都有其各自的优势和劣势,需要根据具体的需求来选择合适的设计方案。

通过不断的研究和实践,我们可以进一步完善十进制加法计数器的设计,为计算机系统的性能提升和应用拓展做出贡献。

希望这篇文章能够为大家提供一些启发和帮助,让我们共同探索数字电路设计的奥秘,开拓计算机科学的新境界。

第二篇示例:同步和异步计数器都是数字电路中常见的设计,用于实现特定的计数功能。

二进制十进制同步加法计数器逻辑ic芯片二进制十进制同步加法计数器是一种逻辑集成电路(IC)芯片,可用于进行二进制的加法和计数操作。

它主要由逻辑门和触发器构成,能够实现数字计数与加法运算的功能。

在本文中,我将详细介绍二进制十进制同步加法计数器的工作原理、设计流程以及应用场景。

首先,让我们了解一下二进制和十进制的概念。

二进制是一种由0和1组成的数制,用来表示数字和进行计算。

而十进制是指以10为基数的数制,由0至9的数字组成。

二进制数字的加法和十进制数字的加法有着类似的原理,但操作方法稍有不同。

二进制十进制同步加法计数器的主要功能是进行加法和计数操作。

它能够将输入的二进制数值与当前内部存储的数值相加,并将结果输出。

在进行计数操作时,只需要连续输入0、1的脉冲信号即可完成对二进制数值的计数。

二进制十进制同步加法计数器的实现主要依赖于逻辑门和触发器。

逻辑门用来实现不同输入信号的逻辑运算,而触发器则用于存储并传递逻辑运算的结果。

常见的逻辑门有AND门、OR门、NOT门等,触发器常用的有RS触发器、D触发器等。

在设计二进制十进制同步加法计数器时,需要根据具体的需求来选择适当的逻辑门和触发器,并将它们按照一定的电路连接方式进行组合,以实现所需的功能。

以下是一个简单的设计流程供参考:1.确定计数器的位数:根据需求确定计数器需要的位数,决定计数范围和精度。

2.选择逻辑门和触发器:根据计数器的位数和功能需求选择适当的逻辑门和触发器。

3.连接逻辑门和触发器:按照设计需求将选择好的逻辑门和触发器进行连接,形成计数器的核心电路。

4.确定输入和输出信号:确定计数器的输入信号和输出信号,并设计合适的接口电路进行连接。

5.进行测试和调试:将设计好的电路进行实物搭建,并通过信号发生器等设备产生输入信号进行测试和调试。

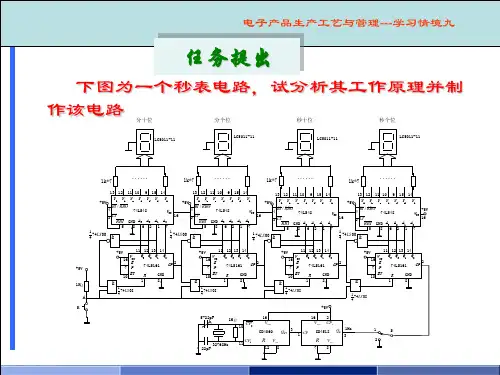

二进制十进制同步加法计数器的应用场景非常广泛。

例如,在数字电路和计算机体系结构中,计数器被广泛用于时序控制、频率分频等功能的实现。

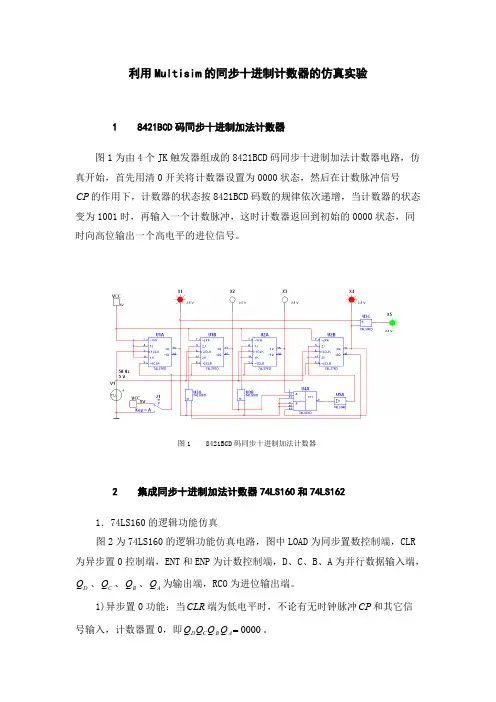

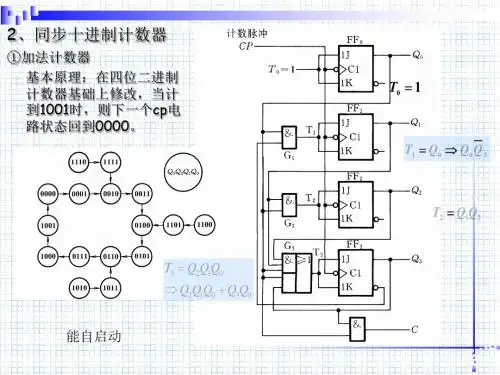

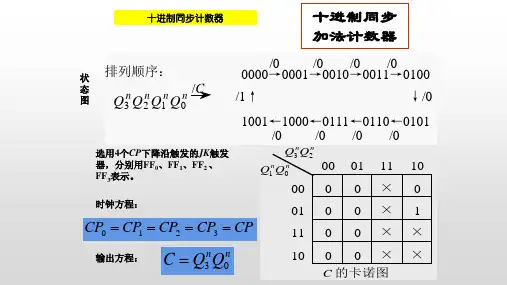

利用Multisim 的同步十进制计数器的仿真实验1 8421BCD 码同步十进制加法计数器图1为由4个JK 触发器组成的8421BCD 码同步十进制加法计数器电路,仿真开始,首先用清0开关将计数器设置为0000状态,然后在计数脉冲信号的作用下,计数器的状态按8421BCD 码数的规律依次递增,当计数器的状态CP 变为1001时,再输入一个计数脉冲,这时计数器返回到初始的0000状态,同时向高位输出一个高电平的进位信号。

2 集成同步十进制加法计数器74LS160和74LS1621.74LS160的逻辑功能仿真图2为74LS160的逻辑功能仿真电路,图中LOAD 为同步置数控制端,CLR 为异步置0控制端,ENT 和ENP 为计数控制端,D 、C 、B 、A 为并行数据输入端,、、、为输出端,RCO 为进位输出端。

D Q C Q B Q A Q 1)异步置0功能:当端为低电平时,不论有无时钟脉冲和其它信CLR CP 号输入,计数器置0,即。

0000 A B C D Q Q QQ 图1 8421BCD 码同步十进制加法计数器2)同步并行置数功能:当时,在输入计数脉冲的作01==LOAD CLR ,CP 用下,并行数据被置入计数器,即,本仿真电路中并DCBA DCBA Q Q Q Q A B C D =行置数仅为0000和1111两种。

3)计数功能:当,端输入计数脉冲1====ENP ENT CLR LOAD CLK 时,计数器按8421BCD 的规律进行十进制加法计数。

CP 4)保持功能:当,且中有0时,则计数器保持1==CLR LOAD ENP ENT 和原来的状态不变。

2.利用74LS160的“异步置0”获得N 进制计数器由74LS160设有“异步置0”控制端,可以采用“反馈复位法”,使复CLR 位输入端为0,迫使正在计数的计数器跳过无效状态,实现所需要进制的CLR 计数器。

图3为用74LS160的“异步置0”功能获得的七进制计数器电路,设计数器从状态开始计数,“7”的二进制代码为0111,反馈归零函0000=A B C D Q Q Q Q 数,根据该函数式用3输入与非门将它们连接起来。

74LS161和74LS290集成计数器功能说明1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。

目前生产的同步计数器芯片分为二进制和十进制两种。

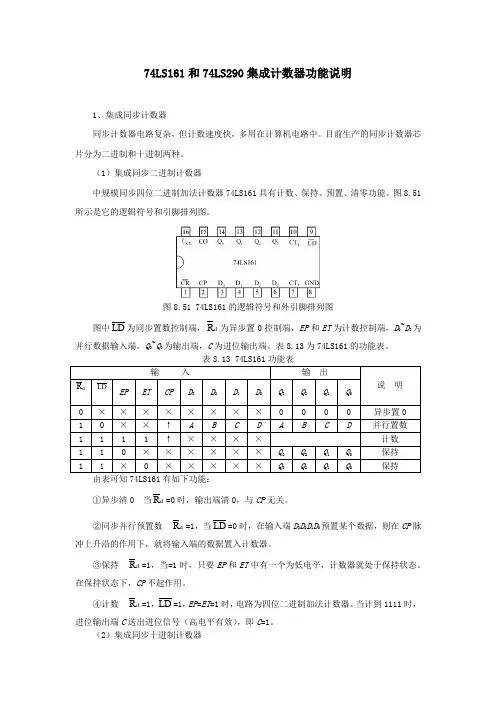

(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。

图8.51所示是它的逻辑符号和引脚排列图。

图8.51 74LS161的逻辑符号和外引脚排列图图中LD为同步置数控制端,d R为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。

表8.13为74LS161的功能表。

R=0时,输出端清0,与CP无关。

①异步清0 当dR=1,当LD=0时,在输入端D3D2D1D0预置某个数据,则在CP脉②同步并行预置数d冲上升沿的作用下,就将输入端的数据置入计数器。

R=1,当=1时,只要EP和ET中有一个为低电平,计数器就处于保持状态。

③保持d在保持状态下,CP不起作用。

R=1,LD=1,EP=ET=1时,电路为四位二进制加法计数器。

当计到1111时,④计数d进位输出端C送出进位信号(高电平有效),即C=1。

(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。

2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。

(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。

它兼有二进制、五进制和十进制三种计数功能。

当十进制计数时,又有8421BCD 和5421BCD 码选用功能,表8.14是它的功能表。

95481213131011CP 0CP 1Q 0Q 1Q 3Q 2R O(1)R O(2)S 9(1)S 9(2)图8.52 74LS290的逻辑结构图由表可知,74LS290具有如下功能:①异步置0 当R 0(1)=R 0(2)=1且S 9(1)或S 9(2)中任一端为0,则计数器清零,即Q D Q C Q B Q A =0000。

第一章引言数字电子技术的应用一直在向着广度和深度扩展。

时至今日,“数字化”的浪潮几乎席卷了电子技术应用的一切领域。

由于电子产品的更新周期日益缩短,新产品开发速度日益加快,因而对电子设计自动化(EDA)提出了更高的要求,也有力地促进了EDA技术的发展和普及。

在数字集成电路方面,电路的集成度如摩尔定律(Moore’s Law)所预言的那样,以每1-2年翻一番的速度增长,使电路的复杂程度越来越高、规模越来越大。

同时,在基本技能方面,对使用EDA工具的能力也提出了更高的要求。

因此,学好EDA课程设计至关重要。

第二章 设计说明1.器件介绍-集成十进制加法计数器74160集成同步十进制加法计数器74160。

图2-1给出了74160的引脚排列图和逻辑符号图。

除了具有十进制加法计数功能外,还具有异步复位、同步预置数和计数状态保持、对输入的时钟信号进行分频等功能。

CLRN 为异步复位端,LDN 为预置数控制端,A-D 为预置状态输入端,RCO 为进位输出端,ENT 和ENP 为工作状态控制端(双使能端)。

图2-1 74160逻辑符号图 表2-1 74160功能特性 表2-2是74160的功能表,它给出了各种控制信号作用下计数器的工作状态,具体如下。

序号 CLK CLRN LDN ENP ENT 工作状态 1 × 0 × × × 复位 2 ↑ 1 0 × × 预置数 3 ↑ 1 1 1 1 正常计数 4 × 1 1 × 0 保持,且C=0 5×110 1保持表2-2 74160的功能表⑴当CLRN=0时,无论其他功能端为何状态,计数器都将复位,有QD ~QA=0000(注:QD 为状态端最高位)。

⑵当CLRN=1、LDN=0时,计数器处于预置数状态。

在出现此情况后的第一个CLK 上升沿,将预置输入端加载的数据送入计数器,即有QD ~QA=D ~A(注:D 为置入端最高位)。

实验三使用74161构成十进制计数器实验三使用74161构成十进制计数器实验三使用74161构成一个同步十进制计数器一、实验目的1.掌握74161的功能2.掌控意见反馈登位法、意见反馈预置法二、实验内容使用74161及必要的逻辑门构成一个同步十进制计数器。

建议使用意见反馈登位法、意见反馈预置法两种方法。

三、分析过程1.反馈复位法:下面的第一个图是反馈复位法。

反馈复位发是当遇到1010时,会立即进行清零。

即从0000开始到1010的时候会进行清零。

qb与qd想与在进行非门,最后的引脚给了clrn,即给它清零。

从0000开始计时,当遇到第一个时冲的时候,qdqcqbqa变成0001,挡在遇到下一个clock时钟的时候,变成0010,就这样每当遇到一个上升的时钟的上升沿的时候,qdqcqbqa就会自动的加一,到了第十个时钟脉冲的时候,它会自动的立即清零。

2.意见反馈预置法:下面的第一个图就是意见反馈混凝土法。

混凝土的dcba的值0000,意见反馈混凝土就是当碰到1001时,不能立即展开清零,而是要到下一个时冲的到来的时候可以立即清零,既当碰到1010的时候可以立即清零。

即为从0000已经开始至1010的时候可以展开清零。

qb与qd想要与在展开非门,最后的插槽给了clrn,即为给它清零。

从0000已经开始计时,当碰到第一个时冲的时候,qdqcqbqa变成0001,挡在遇到下一个clock时钟的时候,变成0010,就这样每当遇到一个上升的时钟的上升沿的时候,qdqcqbqa就会自动的加一,到了第十个时钟脉冲的时候,它会自动的立即清零四、原理图(粘贴quartus中绘制的原理图)下面这个是反馈复位:下面这个就是意见反馈预置五、功能仿真的波形图及说明这就是一个意见反馈登位的74161十进制的计数器,clock的频率为5纳秒,刚开始的时候,qdqcqbqa的值0000;在第一个clock始终到来的时候,即为在第五纳秒的时候,qdqcqbqa可以自己提1=0001;在第二个时钟的下降沿的到来的时候,即为在第十纳秒的时候,qdqcqbqa=0010;在第三个时钟的下降沿的下降沿的时候,即为在第十五纳秒的时候qdqcqbqa=0011;在第四个时钟的下降沿的下降沿的时候,即为在第二十纳秒的时候qdqcqbqa=0100……当在第十个时钟的上升沿到来的时候,会马上清零,即当在了1010的时候,在时钟的上升沿的到来的时候,qdqcqbqa=,马上又变成了0000;即又开始了了下一个的轮回。

十进制计数器级联方法verilog在Verilog中,你可以使用一个简单的模块来创建一个十进制计数器。

以下是一个简单的4位十进制计数器的例子:```verilogmodule counter4bit(input wire clk,input wire reset,output reg [3:0] count);always (posedge clk or posedge reset) beginif (reset) begincount <= 4'b0000;end else begincount <= count + 4'b0001;endendendmodule```在这个模块中,我们定义了一个4位宽的输出`count`,它表示当前的计数值。

`clk`是时钟输入,`reset`是复位输入。

在每个时钟上升沿,如果没有复位信号,计数器就会加1。

如果复位信号为高,计数器就会被清零。

级联多个这样的计数器,你可以通过将一个计数器的输出连接到下一个计数器的时钟输入来实现。

例如,如果你想创建一个16位的十进制计数器,你可以将两个4位计数器级联在一起:```verilogmodule counter16bit(input wire clk,input wire reset,output reg [15:0] count);counter4bit counter1(.clk(clk),.reset(reset),.count(count[3:0]));counter4bit counter2(.clk(count[3]),.reset(reset),.count(count[7:4]));endmodule```在这个例子中,我们创建了一个16位的计数器,它由两个4位计数器组成。

第一个计数器的输出连接到第二个计数器的时钟输入。

这样,当第一个计数器的计数值达到9(即二进制1001)时,第二个计数器就会开始计数。

集成计数器功能描述及说明一、计数器概述集成计数器具有功能完善、通用性强、功耗低、工作速度快、功能可扩展等许多优点,应用非常广泛。

目前用得最多、性能较好的是高速CMOS集成计数器,其次是TTL计数器。

由于定型产品的种类毕竟有限,就计数进制而言,在集成计数器中,只有二进制和十进制计数两大系列。

因此,学习集成计数器,必须掌握用已有的计数器芯片构成其它任意进制计数器的连接方法。

1、集成同步计数器同步计数器电路复杂,但计数速度快,多用在计算机电路中。

目前生产的同步计数器芯片分为二进制和十进制两种。

(1)集成同步二进制计数器中规模同步四位二进制加法计数器74LS161具有计数、保持、预置、清零功能。

图8.51所示是它的逻辑符号和引脚排列图。

图8.51 74LS161的逻辑符号和外引脚排列图图中LD为同步置数控制端,d R为异步置0控制端,EP和ET为计数控制端,D0~D3为并行数据输入端,Q0~Q3为输出端,C为进位输出端。

表8.13为74LS161的功能表。

R=0时,输出端清0,与CP无关。

①异步清0 当d②同步并行预置数 d R =1,当LD =0时,在输入端D 3D 2D 1D 0预置某个数据,则在CP 脉冲上升沿的作用下,就将输入端的数据置入计数器。

③保持 d R =1,当=1时,只要EP 和ET 中有一个为低电平,计数器就处于保持状态。

在保持状态下,CP 不起作用。

④计数 d R =1,LD =1,EP =ET =1时,电路为四位二进制加法计数器。

当计到1111时,进位输出端C 送出进位信号(高电平有效),即C =1。

(2)集成同步十进制计数器集成同步十进制加法计数器74LS160的管脚图和功能表与74LS161基本相同,唯一不同的是74LS160是十进制计数器,而74LS161是二进制计数器。

2、集成异步计数器异步计数电路简单,但计数速度慢,多用于仪器、仪表中。

(1)集成计数器74LS290图8.52是二-五-十进制集成计数器74LS290的逻辑结构图。