《现代计算机组成原理》附录

- 格式:pdf

- 大小:176.32 KB

- 文档页数:7

计算机组成原理第1章计算机系统概论一.填空题1. 计算机系统是由硬件和软件两大部分组成的,前者是计算机系统的物质基础,而后者则是计算机系统解题的灵魂,两者缺一不可。

2. 存储程序是指解题之前预先把程序存入存储器;程序控制是指控制器依据所存储的程序控制计算机自动协调地完成解题的任务,这两者合称为存储程序控制,它是冯·诺依曼型计算机的重要工作方式。

3.通常将控制器和运算器合称为中央处理器(CPU) ;而将控制器、运算器和内存储器合称为计算机的主机。

4.计算机系统的硬件包括控制器、运算器、存储器、I/O接口和I/O设备等五大部分。

二.选择题1. 指令周期是指( C )。

A.CPU从主存取出一条指令的时间B.CPU执行一条指令的时间C. CPU从主存取出一条指令加上执行该指令的时间三.问答题1.存储程序控制是冯•诺依曼型计算机重要的工作方式,请解释何谓存储程序、程序控制?答:存储程序是指将解题程序(连同原始数据)预先存入存储器;程序控制是指控制器依据存储的程序,控制全机自动、协调的完成解题任务。

2.计算机系统按功能通常可划分为哪五个层次?画出其结构示意图加以说明。

答:.五级组成的计算机系统如图1.7 (课本P18)1)微程序设计级:微指令直接由硬件执行。

2)一般机器级(机器语言级):由微程序解释机器指令系统,属硬件级。

3)操作系统级:由操作系统程序实现。

4)汇编语言级:由汇编程序支持执行。

5)高级语言级:由高级语言编译程序支持执行。

这五级的共同特点是各级均可编程。

四.计算题1.设某计算机指令系统有4种基本类型的指令A、B、C和D,它们在程序中出现的频度(概率)分别为0.3、0.2、0.15和0.35,指令周期分别为5ns、5.5ns、8ns和10ns,求该计算机的平均运算速度是多少MIPS(百万条指令每秒)?解:指令平均运算时间:T=5×0.3+5.5×0.2+8×0.15+10×0.35=7.3 (ns)平均运算速度:V=1/T=1/(7.3×10-3)=137(MIPS)第2章运算方法与运算器一.填空题1.若某计算机的字长是8位,已知二进制整数x=10100,y=–10100,则在补码的表示中,[x]补=00010100 ,[y]补=11101100 。

基于手写键盘的的发展第一章键盘的发展历史 (2)1.1 键盘的产生 (2)1.2 键盘两次革新 (3)第二章键盘的分类 (4)2.1 薄膜键盘 (4)2.2 机械键盘 (5)第三章手写键盘 (9)3.1 智能手机的工作原理 (9)3.2 手写板的工作原理 (10)3.3 手写键盘的实现 (10)第一章键盘的发展历史键盘作为我们日常工作、生活和游戏娱乐必不可少的设备,我们每天都要和接触,但是很多人对键盘的了解又有多少呢?1.1 键盘的产生1873年美国人克里斯托弗·拉思兰·肖尔斯发明了第一款商用打字机键盘起源:第一款商用打字机发明者肖尔斯将键盘完全按字母顺序排列,发现只要打字速度稍快,键盘就会卡住。

肖尔斯请他那当数学老师的弟弟帮忙,弟弟解决方案是:将连用的字母在键盘上错开排列,使打字速度减慢,卡键问题迎刃而解。

当然对外不能这样说,于是肖尔斯就像本山大叔一样忽悠开了,声称这样排列是经过科学计算的,目的是使打折速度更快。

他太有才了,将那些不按这种方式排列键盘的打字机公司一个一个打倒,独霸天下,其地位至今不可动摇。

所以肖尔斯发明的键盘是现代键盘的真正鼻祖,又可以说键盘是由打字机演变而成的。

键盘非常悠久,早在1714年,就开始相继有英、美、法、意、瑞士等国家的人发明了各种形式的打字机,最早的键盘就是那个时候用在那些技术还不成熟的打字机上的。

直到1868年,“打字机之父”——美国人克里斯托夫·拉森尔斯(Christopher Latham Sholes)获打字机模型专利并取得经营权经营,又于几年后设计出现代打字机的实用形式和首次规范了键盘,即现在的“QWERTY”键盘。

为什么要将键盘规范成现在这样的“QWERTY”键盘按键布局呢?这是因为最初,打字机的键盘是按照字母顺序排列的,而打字机是全机械结构的打字工具,因此如果打字速度过快,某些键的组合很容易出现卡键问题,于是克里斯托夫·拉森·肖尔斯(Christopher Latham Sholes)发明了QWERTY键盘布局,他将最常用的几个字母安置在相反方向,最大限度放慢敲键速度以避免卡键。

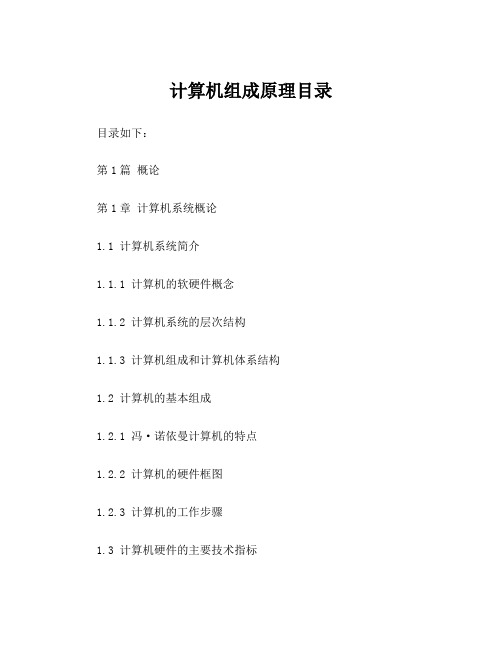

计算机组成原理目录目录如下:第1篇概论第1章计算机系统概论1.1 计算机系统简介1.1.1 计算机的软硬件概念1.1.2 计算机系统的层次结构1.1.3 计算机组成和计算机体系结构1.2 计算机的基本组成1.2.1 冯·诺依曼计算机的特点1.2.2 计算机的硬件框图1.2.3 计算机的工作步骤1.3 计算机硬件的主要技术指标1.3.1 机器字长1.3.2 存储容量1.3.3 运算速度1.4 本书结构思考题与习题第2章计算机的发展及应用2.1 计算机的发展史2.1.1 计算机的产生和发展2.1.2 微型计算机的出现和发展2.1.3 软件技术的兴起和发展2.2 计算机的应用2.2.1 科学计算和数据处理2.2.2 工业控制和实时控制2.2.3 网络技术的应用2.2.4 虚拟现实2.2.5 办公自动化和管理信息系统2.2.6 CAD/CAM/CIMS2.2.7 多媒体技术2.2.8 人工智能2.3 计算机的展望思考题与习题第2篇计算机系统的硬件结构第3章系统总线3.1 总线的基本概念3.2 总线的分类3.2.1 片内总线3.2.2 系统总线3.2.3 通信总线3.3 总线特性及性能指标3.3.1 总线特性3.3.2 总线性能指标3.3.3 总线标准3.4 总线结构3.4.1 单总线结构3.4.2 多总线结构3.4.3 总线结构举例3.5 总线控制3.5.1 总线判优控制3.5.2 总线通信控制思考题与习题第4章存储器4.1 概述4.1.2 存储器的层次结构4.2 主存储器4.2.1 概述4.2.2 半导体存储芯片简介4.2.3 随机存取存储器4.2.4 只读存储器4.2.5 存储器与CPU的连接4.2.6 存储器的校验4.2.7 提高访存速度的措施4.3 高速缓冲存储器4.3.1 概述4.3.2 Cache—主存地址映射4.3.3 替换策略4.4.1 概述4.4.2 磁记录原理和记录方式4.4.3 硬磁盘存储器4.4.4 软磁盘存储器4.4.5 磁带存储器4.4.6 循环冗余校验码4.4.7 光盘存储器思考题与习题附录4A 相联存储器第5章输入输出系统5.1 概述5.1.1 输入输出系统的发展概况5.1.2 输入输出系统的组成5.1.3 I/O设备与主机的联系方式5.1.4 I/O设备与主机信息传送的控制方式5.2 I/O设备5.2.1 概述5.2.2 输入设备5.2.3 输出设备5.2.4 其他I/O设备5.2.5 多媒体技术5.3 I/O接口5.3.1 概述5.3.2 接口的功能和组成5.3.3 接口类型5.4 程序查询方式5.4.1 程序查询流程5.4.2 程序查询方式的接口电路5.5 程序中断方式5.5.1 中断的概念5.5.2 I/O中断的产生5.5.3 程序中断方式的接口电路5.5.4 I/O中断处理过程5.5.5 中断服务程序的流程5.6 DMA方式5.6.1 DMA方式的特点5.6.2 DMA接口的功能和组成5.6.3 DMA的工作过程5.6.4 DMA接口的类型思考题与习题附录5A ASCⅡ码附录5B BCD码附录5C 奇偶校检码第3篇中央处理器第6章计算机的运算方法6.1 无符号数和有符号数6.1.1 无符号数6.1.2 有符号数6.2 数的定点表示和浮点表示6.2.1 定点表示6.2.2 浮点表示6.2.3 定点数和浮点数的比较6.2.4 举例6.2.5 IEEE754标准6.3 定点运算6.3.1 移位运算6.3.2 加法与减法运算6.3.3 乘法运算6.3.4 除法运算6.4 浮点四则运算6.4.1 浮点加减运算6.4.2 浮点乘除法运算6.4.3 浮点运算所需的硬件配置6.5 算术逻辑单元6.5.1 ALU电路6.5.2 快速进位链思考题与习题附录6A 各种进位制6A.1 各种进位制的对应关系6A.2 各种进位制的转换附录6B 阵列乘法器和阵列除法器附录6C 74181逻辑电路第7章指令系统7.1 机器指令7.1.1 指令的一般格式7.1.2 指令字长7.2 操作数类型和操作类型7.2.1 操作数类型7.2.2 数据在存储器中的存放方式7.2.3 操作类型7.3 寻址方式7.3.1 指令寻址7.3.2 数据寻址7.4 指令格式举例7.4.1 设计指令格式应考虑的各种因素7.4.2 指令格式举例7.4.3 指令格式设计举例7.5 RISC技术7.5.1 RISC的产生和发展7.5.2 RISC的主要特征7.5.3 RISC和CISC的比较思考题与习题第8章 CPU的结构和功能8.1 CPU的结构8.1.1 CPU的功能8.1.2 CPU结构框图8.1.3 CPU的寄存器8.1.4 控制单元和中断系统8.2 指令周期8.2.1 指令周期的基本概念8.2.2 指令周期的数据流8.3 指令流水8.3.1 指令流水原理8.3.2 影响流水线性能的因素8.3.3 流水线性能8.3.4 流水线中的多发技术8.3.5 流水线结构8.4 中断系统8.4.1 概述8.4.2 中断请求标记和中断判优逻辑8.4.3 中断服务程序入口地址的寻找8.4.4 中断响应8.4.5 保护现场和恢复现场8.4.6 中断屏蔽技术思考题与习题第4篇控制单元第9章控制单元的功能9.1 微操作命令的分析9.1.1 取指周期9.1.2 间址周期9.1.3 执行周期9.1.4 中断周期9.2 控制单元的功能9.2.1 控制单元的外特性9.2.2 控制信号举例9.2.3 多级时序系统9.2.4 控制方式9.2.5 多级时序系统实例分析思考题与习题第10章控制单元的设计10.1 组合逻辑设计10.1.1 组合逻辑控制单元框图10.1.2 微操作的节拍安排10.1.3 组合逻辑设计步骤10.2 微程序设计10.2.1 微程序设计思想的产生10.2.2 微程序控制单元框图及工作原理10.2.3 微指令的编码方式10.2.4 微指令序列地址的形成10.2.5 微指令格式10.2.6 静态微程序设计和动态微程序程序设计10.2.7 毫微程序设计10.2.8 串行微程序控制和并行微程序控制10.2.9 微程序设计举例思考题与习题附录10A PC整机介绍10A.1 主板10A.1.1 主板的主要组成部件10A.1.2 CPU芯片及插座(插槽)10A.1.3 内存条插槽10A.1.4 扩展插10A.1.5 配套芯片和器件10A.1.6 主板结构的改进10A.2 芯片组10A.2.1 芯片组的功能10A.2.2 芯片组的组成《计算机组成原理》是2008年1月1日高等教育出版社出版的图书,作者是唐朔飞。

《计算机组成原理》实验1寄存器试验,2运算器试验实验指导书课程:计算机组成原理实验教师:班级:第⼀章系统概述1.1 实验系统组成第⼆章基础模块实验实验⼀寄存器实验实验⽬的:熟悉试验仪各部分功能。

掌握寄存器结构、⼯作原理及其控制⽅法。

实验内容:利⽤实验仪开关区上的开关sk23-sk16提供数据,其它开关做为控制信号,将数据通过DBUS写⼊OUT 寄存器,并将OUT寄存器的内容送往扩展区通过数码管和发光⼆极管显⽰。

实验原理:实验箱⽤74HC273 来构成寄存器。

(1)74HC273的功能如下:(2)实验箱中74HC273的连接⽅式:(3)实验逻辑框图12、打开实验仪电源,按CON单元的nRST按键,系统复位;如果EXEC键上⽅指⽰灯不亮,请按⼀次EXEC键,点亮指⽰灯,表⽰实验仪在运⾏状态。

3、利⽤开关和控制信号将数据通过DBUS写⼊OUT寄存器,并将OUT寄存器的内容送往扩展区通过数码管和发光⼆极管显⽰。

并写出将数据5FH写⼊OUT寄存器的操作过程。

实验⼆运算器实验实验⽬的:了解运算器的组成结构;掌握运算器的⼯作原理和控制⽅法。

实验内容:利⽤实验仪提供的运算器,通过开关提供数据信号,将数据写⼊寄存器A和寄存器B,并⽤开关控制ALU的运算⽅式,验证运算器的功能。

实验原理:(1)实验逻辑框图:信号说明:IN0~IN7:ALU数据输⼊信号ALU_D0~ALU_D7:ALU数据输出信号:寄存器A写信号,低电平有效。

当T1节拍信号到来,该信号有效时,IN0~IN7数据可以写⼊寄存器A。

:寄存器B写信号,低电平有效。

当T2节拍信号到来,该信号有效时,IN0~IN7数据可以写⼊寄存器B。

:ALU计算结果读出信号,当T3节拍信号到来,该信号有效时,ALU计算结果送往ALU_D0~ALU_D7。

S3~S0,CN_I:ALU运算控制信号,控制ALU的运算⽅法。

T1,T2,T3:三个节拍信号,⾼电平有效,由con区的uSTEP按键控制,在运⾏状态时,依次按下uSTEP 键会依次发出T1、T2、T3节拍。

现代计算机组成原理潘明潘松编著科学出版社第6 章16位CISC CPU设计6.1 顶层系统设计6.1.1 16位CPU的组成结构图6-1 16位CPU结构框图6.1 顶层系统设计6.1.2指令系统设计1.指令格式(1)单字指令表6-1 单字节指令格式6.1 顶层系统设计(2)双字指令表6-2 双字指令格式表6-3 双字节指令2.指令操作码表6-4 操作码功能表6.1 顶层系统设计6.1.2指令系统设计6.1 顶层系统设计6.1.2指令系统设计2.指令操作码表6-5 常用指令举例6.1 顶层系统设计6.1.3 顶层结构的VHDL设计1. CPU元件的VHDL描述【例6-1】CPU_LIB.VHDlibrary IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;package cpu_lib istype t_shift is (shftpass,shl,shr,rotl,rotr);subtype t_alu is unsigned(3downto0);(接下页)6.1 顶层系统设计6.1.3 顶层结构的VHDL设计1. CPU元件的VHDL描述constant alupass : unsigned(3downto 0) := "0000";constant andOp : unsigned(3downto 0) := "0001";constant orOp : unsigned(3downto 0) := "0010";constant notOp : unsigned(3downto 0) := "0011";constant xorOp : unsigned(3downto 0) := "0100";constant plus : unsigned(3downto 0) := "0101";constant alusub : unsigned(3downto 0) := "0110";constant inc : unsigned(3downto 0) := "0111";constant dec : unsigned(3downto 0) := "1000";constant zero : unsigned(3downto 0) := "1001";type t_comp is (eq,neq,gt,gte,lt,lte);subtype t_reg is std_logic_vector(2downto 0);type state is (reset1, reset2, reset3, reset4, reset5,reset6, execute,nop, load, store, move,load2, load3, load4, store2, store3,store4, move2, move3, move4,incPc, incPc2,incPc3, incPc4, incPc5, incPc6,loadPc,loadPc2,loadPc3, loadPc4, bgtI2, bgtI3,bgtI4, bgtI5, bgtI6, bgtI7,bgtI8, bgtI9,bgtI10, braI2, braI3, braI4, braI5, braI6,loadI2,loadI3, loadI4, loadI5, loadI6,inc2, inc3, inc4);subtype bit16 is std_logic_vector(15downto 0);end cpu_lib;6.1 顶层系统设计6.1.3 顶层结构的VHDL设计1. CPU元件的VHDL描述【例6-2】top.vhdlibrary IEEE;use IEEE.std_logic_1164.all;use work.cpu_lib.all;entity top isend top;architecture behave of top iscomponent mem port (addr : in bit16;sel,rw : in std_logic ;ready : out std_logic ;data :inout bit16);end component;component cpuport(clock, reset, ready : in std_logic ;addr : out bit16;rw,vma : out std_logic ;data :inout bit16);end component;signal addr, data : bit16 ;signal vma,rw, ready : std_logic ;signal clock, reset : std_logic := '0';beginclock <= not clock after 50 ns ;reset <= '1', '0' after 100 ns ;m1 :mem port map (addr,vma,rw, ready, data);u1 :cpu port map(clock, reset, ready,addr,rw,vma,data);end behave;2. 顶层文件的原理图设计6.1 顶层系统设计6.1.3 顶层结构的VHDL设计(接下页)图6-2CPU顶层结构图6.1 顶层系统设计6.1.3 顶层结构的VHDL设计3.CPU与LCD显示模块的接口图6-3 显示模块dsp的实体结构图6.1 顶层系统设计6.1.3 顶层结构的VHDL设计3.CPU与LCD显示模块的接口图6-4 LCD显示屏的数据显示6.1 顶层系统设计6.1.4 软件设计实例表6-6 示例程序6.2.1 运算器ALU6.2 CPU基本部件设计6.2.1 运算器ALU图6-5 运算器ALU 结构图【例6-3】alu.vhd library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;use work.cpu_lib.all;entity alu is port( a, b : in bit16;sel : in t_alu; c : out bit16 );end alu;architecture rtl of alu is beginaluproc: process(a, b,sel)begin case sel iswhen alupass=> c<=a after 1 ns; when andOp => c<=a and b after 1 ns;when orOp => c<= a or b after 1 ns; when xorOp => c<= a xor b after 1 ns;when notOp => c<= not a after 1 ns; when plus => c<= a + b after 1 ns;when alusub => c<= a -b after 1 ns;when inc => c<= a + "0000000000000001" after 1 ns;when dec => c<= a -"0000000000000001" after 1 ns;when zero => c<= "0000000000000000" after 1 ns;when others => c<= "0000000000000000" after 1 ns;end case;end process;end rtl;6.2.1 运算器ALU6.2.1 运算器ALUC=00006.2.2 比较器COMP6.2.2 比较器COMP6.2 CPU基本部件设计6.2.2 比较器COMP【例6-4】COMP.VHD library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;use work.cpu_lib.all;entity comp isport( a, b : in bit16;sel : in t_comp ;compout : out std_logic);end comp;architecture rtl of comp is begincompproc: process(a, b,sel)begin case sel iswhen eq => if a = b then compout <= '1' after 1 ns ;else compout <='0' after 1 ns ;end if ;when neq => if a /= b then compout <= '1' after 1 ns;else compout <= '0' after 1 ns ;end if ;when gt => if a > b then compout <= '1' after 1 ns;else compout <= '0' after 1 ns ;end if ;when gte => if a >= b then compout <= '1'after 1 ns ;else compout <= '0' after 1 ns ;end if;when lt => if a < b then compout <= '1' after 1 ns ;else compout <= '0' after 1 ns ;end if;when lte => if a <= b then compout <= '1' after 1 ns ;else compout <= '0' after 1 ns ;end if;end case ;end process ;end rtl ;6.2.2 比较器COMP6.2 CPU基本部件设计6.2.3 控制器CONTROL图6-9 控制器CONTROL的实体结构图【例6-5】control.vhdlibrary IEEE;use IEEE.std_logic_1164.all;use work.cpu_lib.all;entity control isport( clock,reset ,ready,compout: in std_logic;instrReg: in bit16; progCntrWr,progCntrRd,addrRegWr,addrRegRd,outRegWr,outRegRd: out std_logic;shiftSel: out t_shift;aluSel: out t_alu;compSel: out t_comp;opRegRd,opRegWr,instrWr,regRd,regWr,rw,vma: out std_logic; regSel: out t_reg);end control;architecture rtl of control issignal current_state, next_state : state;beginnxtstateproc: process( current_state,instrReg,compout,ready)beginprogCntrWr<= '0';progCntrRd<= '0';addrRegWr<= '0';outRegWr<= '0'; outRegRd<= '0';shiftSel<=shftpass;aluSel<=alupass;compSel<=eq; opRegRd<= '0';opRegWr<= '0';instrWr<= '0';regSel<= "000";regRd<= '0';regWr<= '0';rw<= '0';vma<= '0';case current_state iswhen reset1=>aluSel<=zero after 1 ns;shiftSel<=shftpass; next_state<=reset2; when reset2 =>aluSel<=zero;shiftSel<=shftpass;outRegWr<='1'; (接下页)next_state<=reset3;when reset3 =>outRegRd<='1'; next_state<=reset4;when reset4 =>outRegRd<='1';addrRegRd<='1';progCntrWr<='1';addrRegWr<='1'; next_state<=reset5;when reset5 =>vma<='1';rw<= '0'; next_state <= reset6;when reset6 =>vma<='1';rw<='0';if ready = '1' then instrWr<='1'; next_state<=execute;else next_state <= reset6; end if;when execute => case instrReg(15downto11) iswhen "00000" => next_state <=incPc;--nopwhen "00001" =>regSel<=instrReg(5downto3);regRd<='1'; next_state<=load2;when "00010" =>regSel<=instrReg(2downto0);regRd<='1';next_state<=store2;--storewhen "00011" =>regSel<=instrReg(5downto3);regRd<='1';aluSel<=alupass;shiftSel<=shftpass; next_state<=move2;when "00100" =>progcntrRd<='1';alusel<=inc;shiftsel<=shftpass;next_state<=loadI2;when "00101" =>progcntrRd<='1';alusel<=inc;shiftsel<=shftpass;next_state<=braI2;when "00110" =>regSel<=instrReg(5downto3);regRd<='1';next_state<=bgtI2;--BranchGTImmwhen "00111" =>regSel<=instrReg(2downto0);regRd<='1';alusel<=inc;(接下页)shiftsel<=shftpass; next_state<=inc2;when others =>next state <=incPc;end case;when load2 =>regSel<=instrReg(5downto3);regRd<= '1';addrregWr<= '1'; next_state <= load3;when load3 =>vma<= '1';rw<= '0'; next_state <= load4;when load4 =>vma<= '1';rw<= '0';regSel<=instrReg(2downto0);regWr<= '1'; next_state <=incPc;when store2 =>regSel<=instrReg(2downto0);regRd<= '1';addrregWr<= '1'; next_state <= store3;when store3 =>regSel<=instrReg(5downto3);regRd<= '1';next_state <= store4;when store4 =>regSel<=instrReg(5downto3);regRd<= '1';vma<= '1';rw<= '1'; next_state <=incPc;when move2 =>regSel<=instrReg(5downto3);regRd<= '1';aluSel<= alupass;shiftsel<=shftpass;outRegWr<= '1'; next_state <= move3;when move3 =>outRegRd<= '1'; next_state <= move4;when move4 =>outRegRd<= '1';regSel<=instrReg(2downto0);regWr<= '1'; next_state <=incPc;when loadI2 =>progcntrRd<= '1';alusel<= inc;shiftsel<=shftpass;outregWr<= '1'; next_state <= loadI3;when loadI3 =>outregRd<= '1'; next_state <= loadI4;when loadI4 =>outregRd<= '1';progcntrWr<='1';addrregWr<='1';next_state<=loadI5;(接下页)when loadI5 =>vma<= '1';rw<= '0'; next_state <= loadI6;when loadI6 =>vma<= '1';rw<= '0';if ready = '1' then regSel<=instrReg(2downto0);regWr<= '1'; next_state <=incPc;else next_state <= loadI6; end if;when braI2 =>progcntrRd<= '1';alusel<= inc;shiftsel<=shftpass; outregWr<= '1'; next_state <= braI3;when braI3 =>outregRd<= '1'; next_state <= braI4;when braI4 =>outregRd<='1';progcntrWr<='1';addrregWr<='1';next_state<=braI5;when braI5 =>vma<='1';rw<='0'; next_state <= braI6;when braI6 =>vma<= '1';rw<= '0';if ready = '1' then progcntrWr<= '1'; next_state <=loadPc;else next_state <= braI6; end if;when bgtI2 =>regSel<=instrReg(5downto3);regRd<= '1';opRegWr<= '1'; next_state <= bgtI3;when bgtI3 =>opRegRd<= '1';regSel<=instrReg(2downto0);regRd<= '1';compsel<=gt; next_state <= bgtI4;when bgtI4 =>opRegRd<= '1' after 1 ns;regSel<=instrReg(2downto0);regRd<= '1';compsel<=gt;if compout= '1' then next_state <= bgtI5;else next_state <=incPc; end if;when bgtI5 =>progcntrRd<='1';alusel<=inc;shiftSel<=shftpass;next_state<=bgtI6;when bgtI6 =>progcntrRd<= '1';alusel<= inc;shiftsel<=shftpass; outregWr<= '1'; next_state <= bgtI7;(接下页)when bgtI7 =>outregRd<= '1'; next_state <= bgtI8;when bgtI8 =>outregRd<= '1';progcntrWr<= '1';addrregWr<= '1'; next_state <= bgtI9;when bgtI9 =>vma<= '1';rw<= '0'; next_state <= bgtI10;when bgtI10 =>vma<= '1';rw<= '0';if ready = '1' then progcntrWr<= '1'; next_state <=loadPc;else next_state <= bgtI10; end if;when inc2 =>regSel<=instrReg(2downto0);regRd<= '1';alusel<= inc; shiftsel<=shftpass;outregWr<= '1'; next_state <= inc3;when inc3 =>outregRd<= '1'; next_state <= inc4;when inc4 =>outregRd<= '1';regsel<=instrReg(2downto0);regWr<= '1'; next_state <=incPc;when loadPc=>progcntrRd<= '1'; next_state <= loadPc2;when loadPc2 =>progcntrRd<= '1';addrRegWr<= '1'; next_state <= loadPc3; when loadPc3 =>vma<= '1';rw<= '0'; next_state <= loadPc4;when loadPc4 =>vma<= '1';rw<= '0';if ready = '1' then instrWr<= '1'; next_state <= execute;else next_state <= loadPc4; end if;when incPc=>progcntrRd<='1';alusel<=inc;shiftsel<=shftpass;next_state<=incPc2;when incPc2 =>progcntrRd<= '1';alusel<= inc;shiftsel<=shftpass; outregWr<= '1'; next_state <= incPc3;when incPc3 =>outregRd<= '1'; next_state <= incPc4;when incPc4 =>outregRd<='1';progcntrWr<='1';(接下页)addrregWr<='1'; next_state<=incPc5;when incPc5 =>vma<= '1';rw<= '0'; next_state <= incPc6; when incPc6 =>vma<= '1';rw<= '0';if ready = '1' then instrWr<= '1'; next_state <= execute; else next_state <= incPc6; end if;when others => next_state <=incPc;end case;end process;controlffProc:process(clock, reset)beginif reset = '1' then current_state <= reset1 after 1 ns;elsif clock'event and clock = '1'then current_state <= next_state after 1 ns; end if;end process;end rtl;6.2.4 寄存器与寄存器阵列6.2 CPU基本部件设计6.2.4 寄存器与寄存器阵列1.寄存器REG【例6-6】reg.vhdlibrary IEEE;use IEEE.std_logic_1164.all;use work.cpu_lib.all;entity reg isport( a : in bit16;clk: in std_logic; q : out bit16);end reg;architecture rtl of reg isbeginregproc: processbeginwait until clk' event and clk= '1';q <= a after 1 ns;end process;end rtl;6.2 CPU基本部件设计2.寄存器阵列RegArray 【例6-7】regarray.vhdlibrary IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;use work.cpu_lib.all;entity regarray isport( data : in bit16;sel : in t_reg; en ,clk : in std_logic;q : out bit16);end regarray;architecture rtl of regarray istype t_ram is array (0 to 7) of bit16;signal temp_data : bit16;beginprocess(clk,sel)variable ramdata : t_ram;beginif clk'event and clk = '1' then ramdata(conv_integer(sel)) := data;end if;temp_data <=ramdata(conv_integer(sel)) after 1 ns;end process;process(en, temp_data)beginif en = '1' then q <= temp_data after 1 ns;else q <="ZZZZZZZZZZZZZZZZ" after 1 ns; end if;end process;end rtl;6.2.4 寄存器与寄存器阵列6.2.4 寄存器与寄存器阵列6.2.5 移位寄存器SHIFT【例6-8】sheft.VHDlibrary IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use work.cpu_lib.all;entity shift isport ( a : in bit16;sel: in t_shift ; y : out bit16);end shift;architecture rtl of shift isbeginshftproc: process(a,sel)begincase sel iswhen shftpass=>y <= a after 1 ns;when sftl=>y <= a(14downto0) & '0' after 1 ns;when sftr=>y <= '0' & a(15downto1) after 1 ns;when rotl=>y <= a(14downto0) & a(15) after 1 ns;when rotr=>y <= a(0) & a(15downto1) after 1 ns;when others =>y <= "0000000000000000" after 1 ns;end case;end process;end rtl;6.2 CPU基本部件设计6.2.5 移位寄存器SHIFT表6-12 SHIFT移位运算类型说明6.2.5 移位寄存器SHIFT6.2.5 移位寄存器SHIFT6.2.6 三态寄存器TRIREG6.2 CPU基本部件设计6.2.6 三态寄存器TRIREG 【例6-9】triReg.vhdlibrary IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;use work.cpu_lib.all;entity trireg is port( a : in bit16; en ,clk : in std_logic; q : out bit16);end trireg;architecture rtl of trireg issignal val : bit16;begintriregdata: processbeginwait until clk'event and clk = '1';val <= a;end process;trireg3st: process(en,val)beginif en = '1' then q <=val after 1 ns;elsif en = '0' then q <= "ZZZZZZZZZZZZZZZZ" after 1 ns;else q <= "XXXXXXXXXXXXXXXX" after 1 ns; --exemplar_translate_on end if;end process;end rtl;6.3 CPU的时序仿真与实现6.3.1 编辑仿真波形文件1.建立仿真波形VWF文件通过仿真波形分析,可以了解CPU在执行指令过程中,各信号的工作时序是否符合设计要求。