Fixed vs. dynamic sub-transfer in reinforcement learning

- 格式:pdf

- 大小:90.53 KB

- 文档页数:6

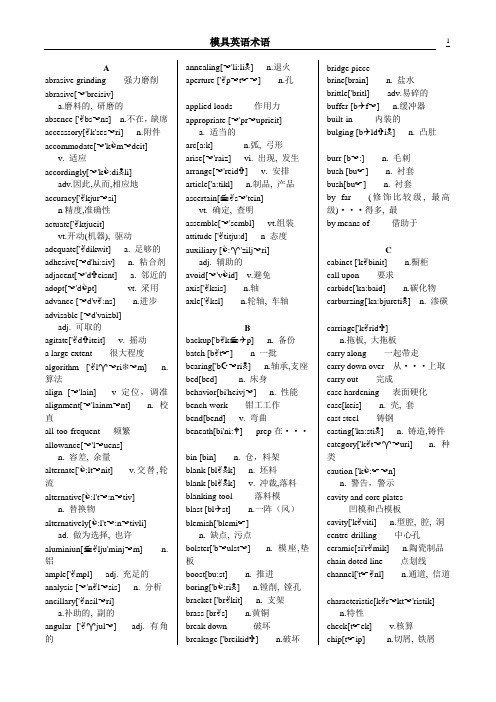

Aabrasive grinding 强力磨削abrasive[☜'breisiv]a.磨料的, 研磨的absence ['✌bs☜ns] n.不在,缺席accesssory[✌k'ses☜ri] n.附件accommodate[☜'k m☜deit]v. 适应accordingly[☜'k :di☠li]adv.因此,从而,相应地accuracy['✌kjur☜si]n精度,准确性actuate['✌ktjueit]vt.开动(机器), 驱动adequate['✌dikwit] a. 足够的adhesive[☜d'hi:siv] n. 粘合剂adjacent[☜'d✞eisnt] a. 邻近的adopt[☜'d pt] vt. 采用advance [☜d'v✌:ns] n.进步advisable [☜d'vaizbl]adj. 可取的agitate['✌d✞iteit] v. 摇动a large extent 很大程度algorithm ['✌l♈☜ri❆☜m] n. 算法align [☜'lain] v 定位,调准alignment[☜'lainm☜nt] n. 校直all-too-frequent 频繁allowance[☜'l☜uens]n. 容差, 余量alternate[' :lt☜nit] v.交替,轮流alternative[ :l't☜:n☜tiv]n. 替换物alternatively[ :l't☜:n☜tivli]ad. 做为选择, 也许aluminiun[ ✌lju'minj☜m] n.铝ample['✌mpl] adj. 充足的analysis [☜'n✌l☜sis] n. 分析ancillary['✌nsil☜ri]a.补助的, 副的angular ['✌♈jul☜] adj. 有角的annealing[☜'li:li☠] n.退火aperture ['✌p☜t☞☜] n.孔applied loads 作用力appropriate [☜'pr☜uprieit]a. 适当的arc[a:k] n.弧, 弓形arise[☜'raiz] vi. 出现, 发生arrange[☜'reid✞] v. 安排article['a:tikl] n.制品, 产品ascertain[ ✌s☜'tein]vt. 确定, 查明assemble[☜'sembl] vt.组装attitude ['✌titju:d] n 态度auxiliary [ :♈'zilj☜ri]adj. 辅助的avoid[☜'v id] v.避免axis['✌ksis] n.轴axle['✌ksl] n.轮轴, 车轴Bbackup['b✌k ✈p] n. 备份batch [b✌t☞] n 一批bearing['b☪☜ri☠] n.轴承,支座bed[bed] n. 床身behavior[bi'heivj☜] n. 性能bench-work 钳工工作bend[bend] v. 弯曲beneath[bi'ni: ] prep在···bin [bin] n. 仓,料架blank [bl✌☠k] n. 坯料blank [bl✌☠k] v. 冲裁,落料blanking tool 落料模blast [bl✈st] n.一阵(风)blemish['blemi☞]n. 缺点, 污点bolster['b☜ulst☜] n. 模座,垫板boost[bu:st] n. 推进boring['b :ri☠] n.镗削, 镗孔bracket ['br✌kit] n. 支架brass [br✌s] n.黄铜break down 破坏breakage ['breikid✞] n.破坏bridge piecebrine[brain] n. 盐水brittle['britl] adv.易碎的buffer [b✈f☜] n.缓冲器built-in 内装的bulging [b✈ld✞i☠] n. 凸肚burr [b☜:] n. 毛刺bush [bu☞] n. 衬套bush[bu☞] n. 衬套by far (修饰比较级, 最高级)···得多, 最by means of 借助于Ccabinet ['k✌binit] n.橱柜call upon 要求carbide['ka:baid] n.碳化物carburzing['ka:bjureti☠] n. 渗碳carriage['k✌rid✞]n.拖板, 大拖板carry along 一起带走carry down over 从···上取carry out 完成case hardening 表面硬化case[keis] n. 壳, 套cast steel 铸钢casting['ka:sti☠] n. 铸造,铸件category['k✌t☜♈☜uri] n. 种类caution ['k :☞☜n]n. 警告,警示cavity and core plates凹模和凸模板cavity['k✌viti] n.型腔, 腔, 洞centre-drilling 中心孔ceramic[si'r✌mik] n.陶瓷制品chain doted line 点划线channel['t☞✌nl] n.通道, 信道characteristic[k✌r☜kt☜'ristik]n.特性check[t☞ek] v.核算chip[t☞ip] n.切屑, 铁屑chuck [t☞✈k] n.卡盘chute [☞u:t] n. 斜道circa ['s☜k☜:] adv. 大约circlip['s☜:klip] n.(开口)簧环circuit['s☜:kit] n. 回路, 环路circular supoport block circulate['s☜:kjuleid]v.(使)循环clamp [kl✌mp] vt 夹紧clamp[kl✌mp] n.压板clay[klei] n. 泥土clearance ['kli☜r☜ns] n. 间隙clip [klip] vt. 切断,夹住cold hobbing 冷挤压cold slug well 冷料井collapse[k☜'l✌ps]vi. 崩塌, 瓦解collapsible[k☜'l✌ps☜bl]adj. 可分解的combination [k mbi'nei☞☜n] n. 组合commence[k☜'mens]v. 开始, 着手commence[k☜'mens] v. 开始commercial [k☜'m☜:☞☜l]adj. 商业的competitive[k☜m'petitiv]a. 竞争的complementary[ k mpli'ment☜ri]a. 互补的complexity [kem'pleksiti]n. 复杂性complicated['k mpl☜keitid]adj. 复杂的complication [k mpli'kei☞☜n] n. 复杂化compression [k☜m'pre☞☜n] n.压缩comprise[k☜m'prais] vt.包含compromise['k mpr☜maiz]n. 妥协, 折衷concern with 关于concise[k☜n'sais]a. 简明的, 简练的confront[k☜n'fr✈nt] vt. 使面临connector[k☜'nekt☜]n. 连接口, 接头consequent['k nsikw☜nt]a. 随之发生的, 必然的console ['k nsoul] n.控制台consume [k☜n'sjum]vt. 消耗, 占用consummate [k☜n's✈meit]vt. 使完善container[k☜n'tein☜] n. 容器contingent[ken'tind✞☜nt]a.可能发生的contour['k☜ntu☜] n.轮廓conventional[k☜n'ven☞☜nl]a. 常规的converge[k☜n'v☜:d✞]v. 集中于一点conversant[k n'v☜:s☜nt]a. 熟悉的conversion[k☜n'v☜:☞☜n]n 换算, 转换conveyer[ken'vei☜]n. 运送装置coolant['ku:l☜nt] n. 冷却液coordinate [k☜u' :dnit]vt. (使)协调copy machine 仿形(加工)机床core[k :] n. 型芯, 核心corresponding [ka:ri'sp di☠]n.相应的counteract [kaunt☜'r✌kt]vt. 反作用,抵抗couple with 伴随CPU (central processing unit)中央处理器crack[kr✌k ] v.(使)破裂,裂纹critical['kritikl] adj.临界的cross-hatching 剖面线cross-section drawn 剖面图cross-slide 横向滑板CRT (cathoder-ray tube)阴极射线管crush[kr✈☞] vt.压碎cryogenic[ krai☜'d✞enik ]a. 低温学的crystal['kristl] adj.结晶状的cubic['kju:bik]a. 立方的, 立方体的cup [k✈p]vt (使)成杯状, 引伸curable ['kjur☜bl]adj. 可矫正的curvature['k☜:v☜t☞☜] n.弧线curve [k☜:v] vt. 使弯曲cutter bit 刀头, 刀片cyanide['sai☜naid] n.氰化物Ddash [d✌☞] n. 破折号daylight ['deilait] n. 板距decline[di'klain]v. 下落,下降,减少, ,deform[di'f :m] v. (使)变形demonstrate['dem☜streit ]v 证明depict[di'pikt ] vt 描述deposite [di'p zit] vt. 放置depression[di'pre☞☜n] n. 凹穴descend [di'sent] v. 下降desirable[di'zair☜bl] a. 合适的detail ['diteil] n.细节,详情deterioration[diti☜ri:☜'rei☞☜n]n. 退化, 恶化determine[di't☜:min] v.决定diagrammmatic[ dai☜gr☜'m✌tik] a. 图解的,图表的dictate['dikteit] v. 支配die[dai] n.模具, 冲模, 凹模dielectric[daii'lektrik]n. 电介质die-set 模架digital ['did✞itl ]n. 数字式数字, a.数字的dimensional[dddi'men☞☜nl]a. 尺寸的, 空间的discharge[dis't☞a:d✞]n.v. 放电, 卸下, 排出discharge[dis't☞a:d✞] v.卸下discrete [dis'cri:t]adj. 离散的,分立的dislodge[dis'l d✞]v. 拉出, 取出dissolution[dis☜'lu:☞☜n] n.结束distinct [dis'ti☠kt]a.不同的,显著的distort [dis'd :t] vt. 扭曲distort[dis't :t]vt. (使)变形, 扭曲distributed system分布式系统dowel ['dau☜l] n. 销子dramaticlly [dr☜'m✌tikli]adv. 显著地drastic ['dr✌stik] a.激烈的draughting[dra:fti☠] n. 绘图draughtsman['dr✌ftsm☜n]n. 起草人drawing['dr :i☠] n. 制图drill press 钻床drum [dr✈m] n.鼓轮dual ['dju:☜l]adv. 双的,双重的ductility [d✈k'tiliti ] n.延展性dynamic [dai'n✌mik ]adj 动力的Eedge [ed✞] n .边缘e.g.(exempli gratia) [拉] 例如ejector [i'd✞ekt☜] n.排出器,ejector plate 顶出板ejector rob 顶杆elasticity[il✌'stisiti] n.弹性electric dicharge machining电火花加工electrochemical machining电化学加工electrode[i'lektr☜ud] n. 电极electro-deposition 电铸elementary [el☜'ment☜ri]adj.基本的eliminate[i'limineit]vt. 消除, 除去elongate[i'l ☠♈et]vt. (使)伸长, 延长emerge [i'm☜:d✞]vi. 形成, 显现emphasise['emf☜saiz]vt. 强调endeavour[en'dev☜] n. 尽力engagement[in'♈eid✞ment]n. 约束, 接合enhance[in'h✌ns]vt. 提高, 增强ensure [in'☞u☜] vt. 确保,保证envisage[in'vizid✞] vt.设想erase[i'reis] vt. 抹去, 擦掉evaluation[i'v✌lju ei☞☜n]n. 评价, 估价eventually[i'v☜nt☞u☜li ]adv. 终于evolution[ev☜'lu:☞☜n] n.进展excecution[eksi'kju:☞☜n]n. 执行, 完成execute ['ekskju:t] v. 执行exerte [i♈'z☜:t] vt. 施加experience[iks'piri☜ns] n. 经验explosive[iks'pl☜usiv]adj.爆炸(性)的extend[eks'tend] v. 伸展external[eks't☜:nl] a. 外部的extract[eks'tr✌kt] v. 拔出extreme[iks'tri:m] n. 极端extremely[iks'tri:mli]adv. 非常地extremity[iks'tmiti] n. 极端extrusion[eks'tru:✞☜n]n. 挤压, 挤出FF (Fahrenheit)['f✌r☜nhait]n. 华氏温度fabricate ['f✌brikeit]vt. 制作,制造facilitate [f☜'siliteit] vt. 帮助facility[f☜'siliti] n. 设备facing[feisi☠] n. 端面车削fall within 属于, 适合于fan[f✌n] n.风扇far from 毫不, 一点不, 远非fatigue[f☜'ti♈] n.疲劳feasible ['fi:z☜bl] a 可行的feature ['fi:t☞☜] n.特色, 特征feed[fi:d] n.. 进给feedback ['fi:db✌k] n. 反馈female['fi:meil]a. 阴的, 凹形的ferrule['fer☜l] n. 套管file system 文件系统fitter['fit☜] n.装配工, 钳工fix[fiks]vt. 使固定, 安装, vi. 固定fixed half and moving half定模和动模flat-panel technology平面(显示)技术flexibility[fleksi'biliti]n. 适应性, 柔性flexible['fleks☜bl] a. 柔韧的flow mark 流动斑点follow-on tool 连续模foregoing ['f :'♈☜ui☠]adj.在前的,前面的foretell[f :'tell]vt. 预测, 预示, 预言forge[f :d✞] n. v. 锻造forming[f :mi☠] n. 成型four screen quadrants四屏幕象限fracture['fr✌kt☞☜] n.破裂free from 免于Ggap[♈✌p] n. 裂口, 间隙gearbox['♈i☜b ks] n.齿轮箱general arrangementgovern['♈✈v☜n]v. 统治, 支配, 管理grain [♈rein] n. 纹理graphic ['♈r✌fik] adj. 图解的grasp [♈r✌sp] vt. 抓住grid[♈rid] n. 格子, 网格grind[♈raind]v. 磨, 磨削, 研磨grinding ['♈raindi☠]n. 磨光,磨削grinding machine 磨床gripper[♈rip☜] n. 抓爪, 夹具groove[♈ru:v] n. 凹槽guide bush 导套guide pillar 导柱guide pillars and bushes导柱和导套Hhandset['h✌ndset] n. 电话听筒hardness['ha:dnis] n.硬度hardware ['ha:dw☪☜] n. 硬件headstock['hedst k] n.床头箱, 主轴箱hexagonal[hek's✌♈☜nl]a. 六角形的, 六角的hindrance['hindr☜ns]n.障碍, 障碍物hob[h b] n. 滚刀, 冲头hollow-ware 空心件horizontal[h ri'z ntl]a. 水平的hose[h☜uz] n. 软管, 水管hyperbolic [haip☜'b lik]adj. 双曲线的Ii.e. (id est) [拉] 也就是identical[ai'dentikl] a同样的identify [ai'dentifai] v. 确定,识别idle ['aidl] adj.空闲的immediately[i'mi:dj☜tli] adv.正好, 恰好impact['imp✌kt] n.冲击impart [im'pa:t] v.给予implement ['implim☜nt]vt 实现impossibility[imp s☜'biliti]n.不可能impression[im'pre☞☜n] n. 型腔in contact with 接触in terms of 依据inasmuch (as)[in☜z'm✈t☞]conj. 因为, 由于inch-to-metric conversions英公制转换inclinable [in'klain☜bl]adj. 可倾斜的inclusion [in'klu☞☜n]n. 内含物inconspicuous[ink☜n'spikju☜s]a. 不显眼的incorporate [in'k :p☜reit]v 合并,混合indentation[ inden'tei☞☜n ]n. 压痕indenter[in'dent☜] n. 压头independently[indi'pein☜ntli]a. 独自地, 独立地inevitably[in'evit☜bli]ad. 不可避免地inexpensive[inik'spensiv]adj. 便宜的inherently [in'hi☜r☜ntli]adv. 固有的injection mould 注塑模injection[in'd✞ek☞☜n] n. 注射in-line-of-draw 直接脱模insert[in's☜:t] n. 嵌件inserted die 嵌入式凹模inspection[in'spek☞☜n]n. 检查,监督installation[inst☜'lei☞☜n]n. 安装integration [inti'♈rei☞☜n]n.集成intelligent[in'telid✞☜nt]a. 智能的intentinonally [in'ten☞☜n☜li]adv 加强地,集中地interface ['int☜feis] n.. 界面internal[in't☜:nl] a. 内部的interpolation [int☜p☜'lei☞☜n]n.插值法investment casting 熔模铸造irregular [i'regjul☜]adj. 不规则的,无规律irrespective of 不论, 不管irrespective[iri'spektiv]a. 不顾的, 不考虑的issue ['isju] vt. 发布,发出Jjoint line 结合线Kkerosene['ker☜si:n] n.煤油keyboard ['ki:b :d ] n. 健盘knock [n k] v 敲,敲打Llance [la:ns] v. 切缝lathe[lei❆] n. 车床latitude ['l✌titju:d] n. 自由lay out 布置limitation[limi'tei☞☜n]n. 限度,限制,局限(性)local intelligence 局部智能locate [l☜u'keit] vt. 定位logic ['l d✞ik] n. 逻辑longitudinal['l nd✞☜'tju:dinl]a. 纵向的longitudinally['l nd✞☜'tju:dinl]a. 纵向的look upon 视作, 看待lubrication[lju:bri'kei☞☜n ]n. 润滑Mmachine shop 车间machine table 工作台machining[m☜'☞i:ni☠] n. 加工made-to-measure 定做maintenance['meintin☜ns]n.维护,维修majority[m☜'d✞a:riti] n.多数make use of 利用male[meil] a. 阳的, 凸形的malfunction['m✌l'f✈☠☞☜n]n. 故障mandrel['m✌dtil] n.心轴manifestation[m✌nif☜s'tei☞☜n] n. 表现, 显示massiveness ['m✌sivnis ]厚实,大块measure['me✞☜] n. 大小, 度量microcomputer 微型计算机microns['maikr n] n.微米microprocessor 微处理器mild steel 低碳钢milling machine 铣床mineral['min☜r☜l] n.矿物, 矿产minimise['minimaiz]v.把···减到最少, 最小化minute['minit] a.微小的mirror image 镜像mirror['mir☜] n. 镜子MIT (Massachusetts Institute ofTechnology) 麻省理工学院moderate['m d☜rit]adj. 适度的modification [m difi'kei☞☜n ]n. 修改, 修正modulus['m djul☜s] n.系数mold[m☜uld]n. 模, 铸模, v. 制模, 造型monitor ['m nit☜ ] v. 监控monograph['m n☜♈ra:f]n. 专著more often than not 常常motivation[m☜uti'vei☞☜n]n. 动机mould split line 模具分型线moulding['m☜udi☠] n. 注塑件move away from 抛弃multi-imprssion mould多型腔模Nnarrow['n✌r☜u] a. 狭窄的NC (numerical control ) 数控nevertheless[ nev☜❆☜'les]conj.,adv.然而,不过nonferrous['n n'fer☜s]adj.不含铁的, 非铁的normally['n :mli] adv.通常地novice['n vis]n. 新手, 初学者nozzle['n zl] n. 喷嘴, 注口numerical [nju'merikl]n. 数字的Oobjectionable [☜b'd✞ek☞☜bl]adj. 有异议的,讨厌的observe[☜b'z☜:v] vt. 观察obviously [' bvi☜sli]adv 明显地off-line 脱机的on-line 联机operational [ p☜'rei☞☜nl]adj. 操作的, 运作的opportunity[ p☜'tju:niti]n. 时机, 机会opposing[☜'p☜uzi☠]a. 对立的, 对面的opposite[' p☜zit]n. 反面a.对立的,对面的optimization [ ptimai'zei☞☜n]n. 最优化orient [' :ri☜nt] vt. 确定方向orthodox [' : ☜d ks]adj. 正统的,正规的overall['☜uv☜r :l]a. 全面的,全部的overbend v.过度弯曲overcome[☜uv☜'k✈m]vt. 克服, 战胜overlaping['☜uv☜'l✌pi☠]n. 重叠overriding[☜uv☜'raidi☠]a. 主要的, 占优势的Ppack[p✌k] v. 包装package ['p✌kid✞] vt.包装pallet ['p✌lit] n.货盘panel ['p✌nl] n.面板paraffin['p✌r☜fin] n. 石蜡parallel[p✌r☜lel] a.平行的penetration[peni'trei☞☜n ]n.穿透peripheral [p☜'rif☜r☜l] adj外围的periphery [p☜'rif☜ri] n. 外围permit[p☜'mit] v. 许可, 允许pessure casting 压力铸造pillar['pil☜] n. 柱子, 导柱pin[pin] n. 销, 栓, 钉pin-point gate 针点式浇口piston ['pist☜n] n.活塞plan view 主视图plasma['pl✌zm☜] n. 等离子plastic['pl✌stik] n. 塑料platen['pl✌t☜n] n. 压板plotter[pl t☜] n. 绘图机plunge [pl✈nd✞] v翻孔plunge[pl✈nd✞] v.投入plunger ['pl✈nd✞☜ ] n. 柱塞pocket-size 袖珍portray[p :'trei] v.描绘pot[p t] n.壶pour[p :] vt. 灌, 注practicable['pr✌ktik☜b]a. 行得通的preferable['pref☜r☜bl]a.更好的, 更可取的preliminary [pri'limin☜ri]adj 初步的,预备的press setter 装模工press[pres]n. 压,压床,冲床,压力机, prevent [pri'vent] v. 妨碍primarily['praim☜rili]adv. 主要地procedure[pr☜'si:d✞☜]n. 步骤, 方法, 程序productivity.[pr☜ud✈k'tiviti] n. 生产力profile ['pr☜ufail] n. 轮廓progressively[pr☜'♈resiv]ad. 渐进地project[pr☜'d✞ekt] n.项目project[pr☜'d✞ekt] v. 凸出projection[pr☜'d✞ek☞☜n]n. 突出部分proper['pr p☜] a. 本身的property['pr p☜ti] n.特性prototype ['pr☜ut☜taip] n. 原形proximity[pr k'simiti] n.接近prudent['pru:d☜nt] a. 谨慎的punch [p✈nt☞] v. 冲孔punch shapper tool 刨模机punch-cum-blanking die凹凸模punched tape 穿孔带purchase ['p☜:t☞☜s] vt. 买,购买push back pin 回程杆pyrometer[pai'n mit☜] n. 高温计Qquality['kwaliti] n. 质量quandrant['kw dr☜nt] n. 象限quantity ['kw ntiti] n. 量,数量quench[kwent☞] vt. 淬火Rradial['reidi☜l] adv.放射状的ram [r✌m] n 撞锤.rapid['r✌pid]adj. 迅速的rapidly['r✌pidli] adv. 迅速地raster['r✌st☜] n. 光栅raw [r :] adj. 未加工的raw material 原材料ream [ri:m] v 铰大reaming[ri:mi☠]n. 扩孔, 铰孔recall[ri'k :l] vt. 记起, 想起recede [ri'si:d] v. 收回, 后退recess [ri'ses]n. 凹槽,凹座,凹进处redundancy[ri'd✈nd☜nsi]n. 过多re-entrant 凹入的refer[ri'f☜:]v. 指, 涉及, 谈及,reference['ref☜r☜ns]n.参照,参考refresh display 刷新显示register ring 定位环register['red✞st☜]v. 记录, 显示, 记数regrind[ri:'♈aind](reground[ri:'gru:nd]) vt. 再磨研relative['rel☜tiv]a. 相当的, 比较的relay ['ri:lei] n. 继电器release[ri'li:s] vt. 释放relegate['rel☜geit] vt.把··降低到reliability [rilai☜'biliti] n. 可靠性relief valves 安全阀relief[ri'li:f] n. 解除relieve[ri'li:v ] vt.减轻, 解除remainder[ri'meind☜]n. 剩余物, 其余部分removal[ri'mu:vl] n. 取出remove[ri'mu:v] v. 切除, 切削reposition [rip☜'zi☞☜n]n. 重新安排represent[ repri'zent☜]v 代表,象征reputable['repjut☜bl]a. 有名的, 受尊敬的reservoir['rez☜vwa: ]n.容器, 储存器resident['rezid☜nt] a. 驻存的resist[ri'zist] vt. 抵抗resistance[ri'zist☜ns]n.阻力, 抵抗resolution[ rez☜'lu:☞☜n] n.分辨率respective[ri'spektiv]a. 分别的,各自的respond[ris'p nd]v. 响应, 作出反应responsibility[risp ns☜'biliti]n. 责任restrain[ris'trein] v. 抑制restrict [ris'trikt] vt 限制,限定restriction[ris'trik☞☜n] n. 限制retain[ri'tein] vt.保持, 保留retaining plate 顶出固定板reveal [ri'vil] vt.显示,展现reversal [ri'v☜sl] n. 反向right-angled 成直角的rigidity[ri'd✞iditi] n. 刚度rod[r d] n. 杆, 棒rotate['r☜uteit] vt.(使)旋转rough machining 粗加工rough[r✈f] a. 粗略的routine [ru:'ti:n] n. 程序rubber['r✈b☜] n.橡胶runner and gate systems 流道和浇口系统Ssand casting 砂型铸造satisfactorily[ s✌tis'f✌ktrili] adv. 满意地saw[a :] n. 锯子scale[skeil] n. 硬壳score[sk :] v. 刻划scrap[skr✌p]n. 废料, 边角料, 切屑, screwcutting 切螺纹seal[si:l] vt.密封secondary storagesection cutting plane 剖切面secure[si'kju☜] v. 固定secure[si'kju☜]vt. 紧固,夹紧,固定segment['se♈m☜nt] v. 分割sensitive['sensitiv] a. 敏感的sequence ['si:kw☜ns] n. 次序sequential[si'kwen☞☜l]a. 相继的seriously['si☜ri☜sli] adv.严重地servomechanism['s☜:v☜'mek☜nizm] n.伺服机构Servomechanism aboratoies 伺服机构实验室servomotor ['s☜:v☜m☜ut☜] n. 伺服马达setter ['set☜] n 安装者set-up 机构sever ['sev☜] v 切断severity [si'veriti] n. 严重shaded[☞✌did] adj. 阴影的shank [☞✌☠k] n. 柄.shear[☞i☜] n.剪,切shot[☞t] n. 注射shrink[☞ri☠k] vi. 收缩side sectional view 侧视图signal ['si♈nl] n. 信号similarity[simi'l✌riti] n.类似simplicity[sim'plisiti] n. 简单single-point cutting tool 单刃刀具situate['sitjueit] vt. 使位于, 使处于slide [slaid] vi. 滑动, 滑落slideway['slaidwei] n. 导轨slot[sl t] n. 槽slug[sl✈♈] n. 嵌条soak[s☜uk] v. 浸, 泡, 均热software ['s ftw☪☜] n. 软件solid['s lid] n.立体, 固体solidify[s☜'lidifai] vt.vi. (使)凝固, (使)固solution[s☜'lu:☞☜n] n.溶液sophisiticated [s☜'fistikeitid]adj.尖端的,完善的sound[saund] a. 结实的, 坚固的)spark erosion 火花蚀刻spindle['spindl] n. 主轴spline[splain] n.花键split[split] n. 侧向分型, 分型spool[spu:l] n. 线轴springback n.反弹spring-loaded 装弹簧的sprue bush 主流道衬套sprue puller 浇道拉杆square[skw☪☜] v. 使成方形stage [steid✞] n. 阶段standardisation[ st✌nd☜dai'zei☞☜n] n. 标准化startling['sta:tli☠]a. 令人吃惊的steadily['sted☜li ] adv. 稳定地step-by-step 逐步stickiness['stikinis] n.粘性stiffness['stifnis] n. 刚度stock[st k] n.毛坯, 坯料storage tube display储存管显示storage['st :rid✞] n. 储存器straightforward[streit'f :w☜d]a.直接的strain[strein] n. 应变strength[stre☠] n.强度stress[stres] n. 压力,应力stress-strain 应力--应变stretch[stret☞] v.伸展strike [straik] vt. 冲击stringent['strind✞☜nt ] a.严厉的stripper[strip☜] n. 推板stroke[strouk] n. 冲程, 行程structrural build-up 结构上形成的sub-base 垫板subject['s✈bd✞ikt] vt.使受到submerge[s☜b'm☜:d✞] v.淹没subsequent ['s✈bsikwent] adj.后来的subsequently ['s✈bsikwentli]adv. 后来, 随后substantial[s☜b'st✌n☞☜l] a.实质的substitute ['s✈bstitju:t] vt. 代替,.替换subtract[s☜b'tr✌kt] v.减, 减去suitable['su:t☜bl]a. 合适的, 适当的suitably['su:t☜bli] ad.合适地sunk[s✈☠k](sink的过去分词)v. 下沉, 下陷superior[s☜'pi☜ri☜] adj.上好的susceptible[s☜'sept☜bl]adj.易受影响的sweep away 扫过symmetrical[si'metrikl]a. 对称的synchronize ['si☠kr☜naiz]v. 同步,同时发生Ttactile['t✌ktail] a. 触觉的, 有触觉的tailstock['teilst k] n.尾架tapered['teip☜d] a. 锥形的tapping['t✌pi☠] n. 攻丝technique[tek'ni:k] n. 技术tempering['temp☜r☠] n.回火tendency['tend☜nsi]n. 趋向, 倾向tensile['tensail]a. 拉力的, 可拉伸的拉紧的, 张紧的tension ['ten☞☜n] n.拉紧,张紧terminal ['t☜:m☜nl ] n. 终端机terminology[t☜:mi'n l☜d✞i ] n. 术语, 用辞theoretically [ i:☜'retikli ] adv.理论地thereby['❆☪☜bai] ad. 因此, 从而thermoplastic[' ☜:m☜u'pl✌stik] a. 热塑性的,n. 热塑性塑料thermoset[' ☜:m☜set] n.热固性thoroughly[' ✈r☜uli] adv.十分地, 彻底地thread pitch 螺距thread[ red] n. 螺纹thrown up 推上tilt [tilt] n. 倾斜, 翘起tolerance ['t l☜r☜ns] n..公差tong[t ☠] n. 火钳tonnage['t✈nid✞]n. 吨位, 总吨数tool point 刀锋tool room 工具车间toolholder['tu:lh☜uld☜]n. 刀夹,工具柄toolmaker ['tu:l'meik☜]n 模具制造者toolpost grinder 工具磨床toolpost['tu:l'p☜ust] n. 刀架torsional ['t :☞☜nl] a扭转的.toughness['t fnis] n. 韧性trace [treis] vt.追踪tracer-controlled milling machine仿形铣床transverse[tr✌ns'v☜:s]a. 横向的tray [trei] n. 盘,盘子,蝶treatment['tri:tm☜nt] n.处理tremendous[tri'mend☜s]a. 惊人的, 巨大的trend [trend] n.趋势trigger stop 始用挡料销tungsten['t✈☠st☜n] n.钨turning['t☜:ni☠] n.车削twist[twist ] v.扭曲,扭转two-plate mould双板式注射模Uultimately['✈ltimitli] adv终于.undercut moulding侧向分型模undercut['✈nd☜k✈t]n. 侧向分型undercut['✈nd☜k✈t] n. 底切underfeed['✈nd☜'fi:d]a 底部进料的undergo[✈nd☜'♈☜u] vt. 经受underside['✈nd☜said]n 下面,下侧undue[✈n'dju:]a.不适当的, 过度的uniform['ju:nif :m]a. 统一的, 一致的utilize ['ju:tilaiz] v 利用Utopian[ju't☜upi☜n]adj. 乌托邦的, 理想化的Vvalve[v✌lv] n. 阀vaporize['veip☜raiz]vt.vi. 汽化, (使)蒸发variation [v☪☜ri'ei☞☜n] n.变化various ['v☪☜ri☜s]a. 不同的,各种的,vector feedrate computation向量进刀速率计算vee [vi:] n. v字形velocity[vi'l siti] n.速度versatile['v☜s☜tail]a. 多才多艺的,万用的vertical['v☜:tikl] a. 垂直的via [vai☜] prep.经,通过vicinity[v☜'siniti] n. 附近viewpoint['vju:p int] n. 观点Wwander['w nd☜] v. 偏离方向warp[w :p] v. 翘曲washer ['w ☞☜] n. 垫圈wear [w☪☜] v. 磨损well line 结合线whereupon [hw☪☜r☜'p n]adv. 于是winding ['waindi☠] n. 绕, 卷with respect to 相对于withstand[wi❆'st✌nd]vt. 经受,经得起work[w☜:k] n. 工件workstage 工序wrinkle['ri☠kl] n.皱纹vt.使皱Yyield[ji:ld] v. 生产Zzoom[zu:] n. 图象电子放大。

★专业英語★XiaoYingLiu121GLOSSARY GLOSSARY((术语术语表表)Aabrasive grinding 强力磨削abrasive[E 'breisiv]a.磨料的,研磨的absence ['A bs E ns]n..不在,缺席accesssory[A k'ses E ri]n.附件accommodate[E 'k C m E deit]v.适应accordingly[E 'k C :di N li]adv.因此,从而,相应地accuracy['A kjur E si]n 精度,准确性actuate['A ktjueit]vt.开动(机器),驱动adequate['A dikwit]a.足够的adhesive[E d'hi:siv]n.粘合剂adjacent[E 'd V eisnt]a.邻近的adopt[E 'd C pt]vt.采用advance [E d'v A :ns]n.进步advisable [E d'vaizbl]adj.可取的agitate['A d V iteit]v.摇动a large extent 很大程度algorithm ['A l ^E ri T E m]n.算法align [E 'lain]v 定位,调准alignment[E 'lainm E nt]n.校直all-too-frequent 频繁allowance[E 'l E uens]n.容差,余量alternate['C :lt E nit]v.交替,轮流alternative[C :l't E :n E tiv]n.替换物alternatively[C :l't E :n E tivli]ad.做为选择,也许aluminiun[7A lju'minj E m]n.铝ample['A mpl]adj.充足的analysis [E 'n A l E sis]n.分析ancillary['A nsil E ri]a.补助的,副的angular ['A ^jul E ]adj.有角的annealing[E 'li:li N ]n.退火aperture ['A p E t F E ]n.孔applied loads 作用力appropriate [E 'pr E uprieit]a.适当的arc[a:k]n.弧,弓形arise[E 'raiz]vi.出现,发生arrange[E 'reid V ]v.安排article['a:tikl]n.制品,产品ascertain[7A s E 'tein]vt.确定,查明assemble[E 'sembl]vt.组装attitude ['A titju:d]n 态度auxiliary [C :^'zilj E ri]adj.辅助的avoid[E 'v C id]v.避免axis['A ksis]n.轴axle['A ksl]n.轮轴,车轴Bbackup['b A k 7Q p]n.备份batch [b A t F ]n 一批bearing['b Z E ri N ]n.轴承,支座bed[bed]n.床身behavior[bi'heivj E ]n.性能bench-work 钳工工作bend[bend]v.弯曲beneath[bi'ni:W ]prep 在···下bin [bin]n.仓,料架blank [bl A N k]n.坯料blank [bl A N k]v.冲裁,落料blanking tool 落料模blast [bl Q st]n.一阵(风)blemish['blemi F ]n.缺点,污点bo l s t e r ['b E ul s t E ]n.模座,垫板★专业英語★boost[bu:st]n.推进boring['b C:ri N]n.镗削,镗孔bracket['br A kit]n.支架brass[br A s]n.黄铜break down破坏breakage['breikid V]n.破坏bridge piecebrine[brain]n.盐水brittle['britl]adv.易碎的buffer[b Q f E]n.缓冲器built-in内装的bulging[b Q ld V i N]n.凸肚burr[b E:]n.毛刺bush[bu F]n.衬套bush[bu F]n.衬套by far(修饰比较级,最高级)··得多,最by means of借助于Ccabinet['k A binit]n.橱柜call upon要求carbide['ka:baid]n.碳化物carburzing['ka:bjureti N]n.渗碳carry along一起带走carry down over从···上取下carry out完成case hardening表面硬化case[keis]n.壳,套cast steel铸钢casting['ka:sti N]n.铸造,铸件category['k A t E^E uri]n.种类caution['k C:F E n]n.警告,警cavity and core plates凹模和凸模板cavity['k A viti]n.型腔,腔,洞centre-drilling中心孔ceramic[si'r A mik]n.陶瓷制品complexity[kem'pleksiti]n.复杂性complicated['k C mpl E keitid]adj.复杂的complication[k C mpli'kei F E n]n.复杂化compression[k E m'pre F E n]n.压缩corresponding[ka:ri'sp C di N]n.相应的counteract[kaunt E'r A kt]vt.反作用,抵抗couple with伴随CPU(central processing unit)中央处理器crack[kr A k]v.(使)破裂,裂纹critical['kritikl]adj.临界的cross-hatching剖面线cross-section drawn剖面图cross-slide横向滑板CRT(cathoder-ray tube)阴极射线管crush[kr Q F]vt.压碎cryogenic[7krai E'd V enik]a.低温学的crystal['kristl]adj.结晶状的cubic['kju:bik]a.立方的,立方体的cup[k Q p]vt(使)成杯状,引伸curable['kjur E bl]adj.可矫正的curvature['k E:v E t F E]n.弧线curve[k E:v]vt.使弯曲cutter bit刀头,刀片cyanide['sai E naid]n.氰化物Ddash[d A F]n.破折号daylight['deilait]n.板距decline[di'klain]v.下落,下降,减少, deform[di'f C:m]v.(使)变形★专业英語★demonstrate['dem E streit]v证明depict[di'pikt]vt描述deposite[di'p C zit]vt.放置depression[di'pre F E n]n.凹穴descend[di'sent]v.下降desirable[di'zair E bl]a.合适的de ta il['di t ei l]n.细节,详情deterioration[diti E ri:E'rei F E n]n.退化,恶化determine[di't E:min]v.决定diagrammmatic[7dai E gr E'm A tik] .a.图解的,图表的dictate['dikteit]v.支配die[dai]n.模具,冲模,凹模dielectric[daii'lektrik]n.电介质die-set模架digital['did V itl]n.数字式数字,a.数字的dimensional[dddi'men F E nl]a.尺寸的,空间的discharge[dis't F a:d V]n.v.放电,卸下,排出discharge[dis't F a:d V]v.卸下discrete[dis'cri:t]adj.离散的,分立的dislodge[dis'l C d V]v.拉出,取出dissolution[dis E'lu:F E n]n.结束distinct[dis'ti N kt]a.不同的,显著的distort[dis'd C:t]vt.扭曲distort[dis't C:t]vt.(使)变形,扭曲distributed system分布式系统dowel['dau E l]n.销子dramaticlly[dr E'm A tikli]adv.显著地drastic['dr A stik]a.激烈的draughting[dra:fti N]n.绘图draughtsman['dr A ftsm E n]n.起草人drawing['dr C:i N]n.制图drill press钻床drum[dr Q m]n.鼓轮dual['dju:E l]adv.双的,双重的ductility[d Q k'tiliti]n.延展性dynamic[dai'n A mik]adj动力的Eedge[ed V]n.边缘e.g.(exempli gratia)[拉]例如ejector[i'd V ekt E]n.排出器,ejector plate顶出板ejector rob顶杆elasticity[il A'stisiti]n.弹性electric dicharge machining电火花加工electrical discharge machining电火花加工electrochemical machining电化学加工electrode[i'lektr E ud]n.电极electro-deposition电铸elementary[el E'ment E ri]adj.基本的eliminate[i'limineit]vt.消除,除去elongate[i'l C N^et]vt.(使)伸长,延长emphasise['emf E saiz]vt.强调endeavour[en'dev E]n.尽力engagement[in'^eid V ment]n.约束,接合enhance[in'h A ns]vt.提高,增强ensure[in'F u E]vt.确保,保证envisage[in'vizid V]vt.设想erase[i'reis]vt.抹去,擦掉evaluation[i'v A lju7ei F E n]n.评价,估价eventually[i'v E nt F u E li]adv.终于evolution[ev E'lu:F E n]n.进展★专业英語★excecution[eksi'kju:F E n]n.执行,完成execute['ekskju:t]v.执行exerte[i^'z E:t]vt.施加experience[iks'piri E ns]n.经验explosive[iks'pl E usiv]adj.爆炸(性)的extend[eks'tend]v.伸展external[eks't E:nl]a.外部的extract[eks'tr A kt]v.拔出extreme[iks'tri:m]n.极端extremely[iks'tri:mli]adv.非常地extremity[iks'tmiti]n.极端extrusion[eks'tru:V E n]n.挤压,挤出FF(Fahrenheit)['f A r E nhait]n.华氏温度fabricate['f A brikeit]vt.制作,制造facilitate[f E'siliteit]vt.帮助facility[f E'siliti]n.设备facing[feisi N]n.端面车削fall within属于,适合于fan[f A n]n.风扇far from毫不,一点不,远非fatigue[f E'ti^]n.疲劳feasible['fi:z E bl]a可行的feature['fi:t F E]n.特色,特征feed[fi:d]n..进给feedback['fi:db A k]n.反馈female['fi:meil]a.阴的,凹形的ferrule['fer E l]n.套管file system文件系统fitter['fit E]n.装配工,钳工fix[fiks]vt.使固定,安装,vi.固定fixed half and moving half定模和动模flat-panel technology平面(显示)技术flexibility[fleksi'biliti]n.适应性,柔性flexible['fleks E bl]a.柔韧的flow mark流动斑点follow-on tool连续模foregoing['f C:'^E ui N]adj.在前的,前面的foretell[f C:'tell]vt.预测,预示,预言forge[f C:d V]n.v.锻造forming[f C:mi N]n.成型four screen quadrants四屏幕象限fracture['fr A kt F E]n.破裂free from免于Ggap[^A p]n.裂口,间隙gearbox['^i E b C ks]n.齿轮箱general arrangementgovern['^Q v E n]v.统治,支配,管理grain[^rein]n.纹理graphic['^r A fik]adj.图解的grasp[^r A sp]vt.抓住grid[^rid]n.格子,网格grind[^raind]v.磨,磨削,研磨grinding['^raindi N]n.磨光,磨削grinding machine磨床gripper[^rip E]n.抓爪,夹具groove[^ru:v]n.凹槽guide bush导套guide pillar导柱guide pillars and bushes导柱和导套Hhandset['h A ndset]n.电话听筒hardness['ha:dnis]n.硬度hardware['ha:dw Z E]n.硬件headstock['hedst C k]n.床头箱,★专业英語★主轴箱hexagonal[hek's A^E nl]a.六角形的,六角的hindrance['hindr E ns]n.障碍,障碍物hob[h C b]n.滚刀,冲头hollow-ware空心件horizontal[h C ri'z C ntl]a.水平的hose[h E uz]n.软管,水管hyperbolic[haip E'b C lik]adj.双曲线的Ii.e.(id est)[拉]也就是identical[ai'dentikl]a同样的identify[ai'dentifai]v.确定,识别idle['aidl]adj.空闲的immediately[i'mi:dj E tli]adv.正好,恰好impact['imp A kt]n.冲击impart[im'pa:t]v.给予implement['implim E nt]vt实现impossibility[imp C s E'biliti]n.不可能impression[im'pre F E n]n.型腔in contact with接触in terms of依据inasmuch(as)[in E z'm Q t F]conj.因为,由于inch-to-metric conversions英公制转换inclinable[in'klain E bl]adj.可倾斜的inclusion[in'klu F E n]n.内含物inconspicuous[ink E n'spikju E s]a.不显眼的incorporate[in'k C:p E reit]v合并,混合indentation[7inden'tei F E n]n.压痕indenter[in'dent E]n.压头independently[indi'pein E ntli]a.独自地,独立地inevitably[in'evit E bli]ad.不可避免地inexpensive[inik'spensiv]adj.便宜的inherently[in'hi E r E ntli]adv.固有的injection mould注塑模injection[in'd V ek F E n]n.注射in-line-of-draw直接脱模insert[in's E:t]n.嵌件inserted die嵌入式凹模inspection[in'spek F E n]n.检查,监督installation[inst E'lei F E n]n.安装integration[inti'^rei F E n]n.集成intelligent[in'telid V E nt]a.智能的intentinonally[in'ten F E n E li] adv加强地,集中地interface['int E feis]n..界面internal[in't E:nl]a.内部的interpolation[int E p E'lei F E n]n.插值法investment casting熔模铸造irregular[i'regjul E]adj.不规则的,无规律irrespective of不论,不管irrespective[iri'spektiv]a.不顾的,不考虑的issue['isju]vt.发布,发出Jjoint line结合线Kkerosene['ker E si:n]n.煤油keyboard['ki:b C:d]n.健盘knock[n R k]v敲,敲打L★专业英語★lance[la:ns]v.切缝lathe[lei T]n.车床latitude['l A titju:d]n.自由lay out布置limitation[limi'tei F E n]n.限度,限制,局限(性)local intelligence局部智能locate[l E u'keit]vt.定位logic['l C d V ik]n.逻辑longitudinal['l C nd V E'tju:dinl]a.纵向的longitudinally['l C nd V E'tju:dinl]a.纵向的look upon视作,看待lubrication[lju:bri'kei F E n]n.润滑Mmachine shop车间machine table工作台machining[m E'F i:ni N]n.加工made-to-measure定做maintenance['meintin E ns]n.维护,维修majority[m E'd V a:riti]n.多数make use of利用male[meil]a.阳的,凸形的malfunction['m A l'f Q N F E n]n.故障mandrel['m A dtil]n.心轴manifestation[m A nif E s'tei F E n]n.表现,显示massiveness['m A sivnis]厚实,大块measure['me V E]n.大小,度量microcomputer微型计算机microns['maikr C n]n.微米microprocessor微处理器mild steel低碳钢milling machine铣床mineral['min E r E l]n.矿物,矿产minimise['minimaiz]v.把···减到最少,最小化minute['minit]a.微小的mirror image镜像mirror['mir E]n.镜子MIT(Massachusetts Institute of Technology)麻省理工学院moderate['m C d E rit]adj.适度的modification[m R difi'kei F E n]n.修改,修正modulus['m C djul E s]n.系数mold[m E uld]n.模,铸模,v.制模,造型monitor['m C nit E]v.监控monograph['m C n E^ra:f]n.专著more often than not常常motivation[m E uti'vei F E n]n.动机mould split line模具分型线moulding['m E udi N]n.注塑件move away from抛弃multi-imprssion mould多型腔模Nnarrow['n A r E u]a.狭窄的NC(numerical control)数控nevertheless[7nev E T E'les]conj.,adv.然而,不过nonferrous['n C n'fer E s]adj.不含铁的,非铁的normally['n C:mli]adv.通常地novice['n C vis]n.新手,初学者nozzle['n C zl]n.喷嘴,注口numerical[nju'merikl]n.数字的O objectionable[E b'd V ek F E bl]adj.有异议的,讨厌的★专业英語★observe[E b'z E:v]vt.观察obviously['C bvi E sli]adv明显地off-line脱机的on-line联机operational[C p E'rei F E nl]adj.操作的,运作的opportunity[C p E'tju:niti]n.时机,机会opposing[E'p E uzi N]a.对立的,对面的opposite['C p E zit]n.反面a.对立的,对面的optimization[R ptimai'zei F E n]n.最优化orient['C:ri E nt]vt.确定方向orthodox['C:W E d C ks]adj.正统的,正规的overall['E uv E r C:l]a.全面的,全部的overbend v.过度弯曲overcome[E uv E'k Q m]vt.克服,战胜overlaping['E uv E'l A pi N]n.重叠overriding[E uv E'raidi N]a.主要的,占优势的Ppack[p A k]v.包装package['p A kid V]vt.包装pallet['p A lit]n.货盘panel['p A nl]n.面板paraffin['p A r E fin]n.石蜡parallel[p A r E lel]a.平行的penetration[peni'trei F E n]n.穿透peripheral[p E'rif E r E l]adj外围的periphery[p E'rif E ri]n.外围permit[p E'mit]v.许可,允许pessure casting压力铸造pillar['pil E]n.柱子,导柱pin[pin]n.销,栓,钉pin-point gate针点式浇口piston['pist E n]n.活塞plan view主视图plasma['pl A zm E]n.等离子plastic['pl A stik]n.塑料platen['pl A t E n]n.压板plotter[pl C t E]n.绘图机plunge[pl Q nd V]v翻孔plunge[pl Q nd V]v.投入plunger['pl Q nd V E]n.柱塞pocket-size袖珍portray[p C:'trei]v.描绘pot[p C t]n.壶pour[p C:]vt.灌,注practicable['pr A ktik E b]a.行得通的preferable['pref E r E bl]a.更好的,更可取preliminary[pri'limin E ri]adj初步的,预备的press setter装模工press[pres]n.压,压床,冲床,压力机prevent[pri'vent]v.妨碍primarily['praim E rili]adv.主要地procedure[pr E'si:d V E]n.步骤,方法,程序productivity.[pr E ud Q k'tiviti]n.生产力profile['pr E ufail]n.轮廓progressively[pr E'^resiv]ad.渐进地project[pr E'd V ekt]n.项目project[pr E'd V ekt]v.凸出projection[pr E'd V ek F E n]n.突出部分proper['pr C p E]a.本身的property['pr C p E ti]n.特性prototype['pr E ut E taip]n.原★专业英語★形proximity[pr C k'simiti]n.接近prudent['pru:d E nt]a.谨慎的punch[p Q nt F]v.冲孔punch shapper tool刨模机punch-cum-blanking die凹凸模punched tape穿孔带purchase['p E:t F E s]vt.买,购买push back pin回程杆pyrometer[pai'n C mit E]n.高温计Qquality['kwaliti]n.质量quandrant['kw C dr E nt]n.象限quantity['kw C ntiti]n.量,数量quench[kwent F]vt.淬火Rradial['reidi E l]adv.放射状的ram[r A m]n撞锤.rapid['r A pid]adj.迅速的rapidly['r A pidli]adv.迅速地raster['r A st E]n.光栅raw[r C:]adj.未加工的raw material原材料ream[ri:m]v铰大reaming[ri:mi N]n.扩孔,铰孔recall[ri'k C:l]vt.记起,想起recede[ri'si:d]v.收回,后退recess[ri'ses]n.凹槽,凹座,凹进处redundancy[ri'd Q nd E nsi]n.过多re-entrant凹入的r e f e r[r i'f E:]v.指,涉及,谈及reference['ref E r E ns]n.参照,参考refresh display刷新显示register['red V st E]v.记录,显示,记数regrind[ri:'^aind](reground[ri:'gru:nd]) vt.再磨研relative['rel E tiv]a.相当的,比较的relay['ri:lei]n.继电器release[ri'li:s]vt.释放relegate['rel E7geit]vt.把··降低到reliability[rilai E'biliti]n.可靠性relief valves安全阀relief[ri'li:f]n.解除relieve[ri'li:v]vt.减轻,解除remainder[ri'meind E]n.剩余物,其余部分removal[ri'mu:vl]n.取出remove[ri'mu:v]v.切除,切削reposition[rip E'zi F E n]n.重新安排represent[7repri'zent E]v代表,象征reputable['repjut E bl]a.有名的,受尊敬的reservoir['rez E vwa:]n.容器,储存器resident['rezid E nt]a.驻存的resist[ri'zist]vt.抵抗resistance[ri'zist E ns]n.阻力,抵抗resolution[7rez E'lu:F E n]n.分辨率respective[ri'spektiv]a.分别的,各自的respond[ris'p C nd]v.响应,作出反应responsibility[risp C ns E'biliti]n.责任restrain[ris'trein]v.抑制restrict[ris'trikt]vt限制,限定restriction[ris'trik F E n]n.限制retain[ri'tein]vt.保持,保留retaining plate顶出固定板reveal[ri'vil]vt.显示,展现★专业英語★reversal[ri'v E sl]n.反向right-angled成直角的rigidity[ri'd V iditi]n.刚度rod[r C d]n.杆,棒rotate['r E uteit]vt.(使)旋转rough machining粗加工rough[r Q f]a.粗略的routine[ru:'ti:n]n.程序rubber['r Q b E]n.橡胶runner and gate systems流道和浇口系统Ssand casting砂型铸造satisfactorily[7s A tis'f A ktrili]adv.满意地saw[a C:]n.锯子scale[skeil]n.硬壳score[sk C:]v.刻划scrap[skr A p]n.废料,边角料,切屑screwcutting切螺纹seal[si:l]vt.密封secondary storagesection cutting plane剖切面secure[si'kju E]v.固定secure[si'kju E]vt.紧固,夹紧,固定segment['se^m E nt]v.分割sensitive['sensitiv]a.敏感的sequence['si:kw E ns]n.次序sequential[si'kwen F E l]a.相继的seriously['si E ri E sli]adv.严重地servomechanism['s E:v E'mek E nizm] n.伺服机构Servomechanism Laboratoies伺服机构实验室servomotor['s E:v E m E ut E]n.伺服马达setter['set E]n安装者set-up机构sever['sev E]v切断severity[si'veriti]n.严重shaded[F A did]adj.阴影的shank[F A N k]n.柄.shear[F i E]n.剪,切shot[F C t]n.注射shrink[F ri N k]vi.收缩side sectional view侧视图signal['si^nl]n.信号similarity[simi'l A riti]n.类似simplicity[sim'plisiti]n.简单single-point cutting tool单刃刀具situate['sitjueit]vt.使位于,使处于slide[slaid]vi.滑动,滑落slideway['slaidwei]n.导轨slot[sl C t]n.槽slug[sl Q^]n.嵌条soak[s E uk]v.浸,泡,均热software['s C ftw Z E]n.软件solid['s C lid]n.立体,固体solidify[s E'lidifai]vt.vi.(使)凝固,(使)固化solution[s E'lu:F E n]n.溶液sophisiticated[s E'fistikeitid]adj.尖端的,完善的sound[saund]a.结实的,坚固的)s p a r k e r o s i o n火花蚀刻spindle['spindl]n.主轴spline[splain]n.花键split[split]n.侧向分型,分型spool[spu:l]n.线轴springback n.反弹spring-loaded装弹簧的sprue bush主流道衬套sprue puller浇道拉杆★专业英語★square[skw Z E]v.使成方形stage[steid V]n.阶段standardisation[7st A nd E dai'zei F E n] n.标准化startling['sta:tli N]a.令人吃惊的steadily['sted E li]adv.稳定地step-by-step逐步stickiness['stikinis]n.粘性stiffness['stifnis]n.刚度stock[st C k]n.毛坯,坯料storage tube display储存管显示storage['st C:rid V]n.储存器straightforward[streit'f C:w E d]a.直接的strain[strein]n.应变strength[stre N W]n.强度stress[stres]n.压力,应力stress-strain应力--应变stretch[stret F]v.伸展strike[straik]vt.冲击stringent['strind V E nt]a.严厉的stripper[strip E]n.推板stroke[strouk]n.冲程,行程structrural build-up结构上形成的sub-base垫板subject['s Q bd V ikt]vt.使受到submerge[s E b'm E:d V]v.淹没subsequent['s Q bsikwent]adj.后来的subsequently['s Q bsikwentli]adv.后来,随后substantial[s E b'st A n F E l]a.实质的substitute['s Q bstitju:t]vt.代替,.替换subtract[s E b'tr A kt]v.减,减去suitable['su:t E bl]a.合适的,适当的suitably['su:t E bli]ad.合适地sunk[s Q N k](sink的过去分词)v.下沉,下陷superior[s E'pi E ri E]adj.上好的susceptible[s E'sept E bl]adj.易受影响的sweep away扫过symmetrical[si'metrikl]a.对称的synchronize['si N kr E naiz]v.同步,同时发生Ttactile['t A ktail]a.触觉的,有触觉的tailstock['teilst C k]n.尾架tapered['teip E d]a.锥形的tapping['t A pi N]n.攻丝technique[tek'ni:k]n.技术tempering['temp E r N]n.回火tendency['tend E nsi]n.趋向,倾向tensile['tensail]a.拉力的,可拉伸的L2拉紧的,张紧的tension['ten F E n]n.拉紧,张紧terminal['t E:m E nl]n.终端机terminology[t E:mi'n C l E d V i]n.术语,用辞theoretically[W i:E'retikli]adv.理论地thereby['T Z E bai]ad.因此,从而thermoplastic['W E:m E u'pl A stik] a.热塑性的,n.热塑性塑料thermoset['W E:m E set]n.热固性thoroughly['W Q r E uli] adv.十分地,彻底地thread pitch螺距thread[W red]n.螺纹thrown up推上tilt[tilt]n.倾斜,翘起tolerance['t C l E r E ns]n..公差tong[t CN]n.火钳tonnage['t Q nid V]n.吨位,总吨数tool point刀锋tool room工具车间★专业英語★XiaoYingLiu131toolholder['tu:lh E uld E ]n.刀夹,工具柄toolmaker ['tu:l'meik E ]n 模具制造者toolpost grinder 工具磨床toolpost['tu:l'p E ust]n.刀架torsional ['t C :F E nl]a 扭转的.toughness['t C fnis]n.韧性trace [treis]vt.追踪tracer-controlled milling machine 仿形铣床transverse[tr A ns'v E :s]a.横向的tray [trei]n.盘,盘子,蝶treatment['tri:tm E nt]n.处理tremendous[tri'mend E s]a.惊人的,巨大的trend [trend]n.趋势trigger stop 始用挡料销tungsten['t Q N st E n]n.钨turning['t E :ni N ]n.车削twist[twist ]v.扭曲,扭转two-plate mould 双板式注射模Uultimately['Q ltimitli]adv 终于.un de r c ut mou l d i ng 侧向分型模undercut['Q nd E k Q t]n.侧向分型undercut['Q nd E k Q t]n.底切underfeed['Q nd E 'fi:d]a,底部进料的undergo[Q nd E '^E u]vt.经受underside['Q nd E said]n 下面,下侧undue[Q n'dju:]a.不适当的,过度的uniform['ju:nif C :m]a.统一的,一致的utilize ['ju:tilaiz]v 利用Utopian[ju't E upi E n]adj.乌托邦的,理想化的Vvalve[v A lv]n.阀vaporize['veip E raiz]vt.vi.汽化,(使)蒸发variation [v Z E ri'ei F E n]n.变化various ['v Z E ri E s]a.不同的,各种的vector feedrate computation 向量进刀速率计算vee [vi:]n.v 字形velocity[vi'l C siti]n.速度versatile['v E s E tail]a.多才多艺的,万用的vertical['v E :tikl]a.垂直的via [vai E ]prep.经,通过vicinity[v E 'siniti]n.附近viewpoint['vju:p C int]n.观点Wwander['w C nd E ]v.偏离方向warp[w C :p]v.翘曲washer ['w CF E ]n.垫圈wear [w Z E ]v.磨损well line 结合线whereupon [hw Z E r E 'p C n]adv.于是winding ['waindi N ]n.绕,卷with respect to 相对于withstand[wi T 'st A nd]vt.经受,经得起work[w E :k]n.工件workstage 工序wrinkle['ri N kl]n.皱纹vt.使皱Yyield[ji:ld]v.生产Zzoom[zu:]n.图象电子放大。

fix协议 resend(最新版)目录1.Fix 协议概述2.Resend 的作用和原理3.Fix 协议与 Resend 的结合应用4.Fix 协议与 Resend 在证券市场的重要性正文1.Fix 协议概述Fix(Financial Information eXchange)协议是一种用于证券市场信息传输的国际标准协议,主要用于实时报价、交易指令、交易确认等信息的传输。

Fix 协议采用统一的数据格式和传输方式,能够确保信息在各个系统间的准确传输,从而提高了证券市场的效率和安全性。

2.Resend 的作用和原理Resend(重传)是 Fix 协议中的一种机制,用于处理在传输过程中可能出现的数据丢失或损坏问题。

当发送方发现接收方未收到数据或接收方反馈错误信息时,发送方会重新发送数据,以确保信息的完整性和准确性。

Resend 机制的原理是在发送方维护一个待重传数据列表,当发现数据未到达接收方时,将该数据加入待重传列表并发送。

接收方收到重传数据后,将数据与本地存储的数据进行比对,如数据一致则更新本地数据,如不一致则反馈错误信息。

3.Fix 协议与 Resend 的结合应用Fix 协议与 Resend 机制的结合应用在证券市场中具有重要意义。

首先,Fix 协议统一了证券市场信息传输的标准,使得各个系统间的信息传输更加高效、准确。

而 Resend 机制则保证了在传输过程中可能出现的数据丢失或损坏问题得到及时解决,从而提高了证券市场的稳定性和可靠性。

4.Fix 协议与 Resend 在证券市场的重要性Fix 协议与 Resend 机制在证券市场中具有举足轻重的地位。

它们为证券市场的参与者提供了一个高效、稳定、安全的信息传输平台,使得市场参与者能够及时获取市场信息,进行投资决策。

同时,它们也为证券市场的监管者提供了有力的监管手段,有助于维护市场的公平、公正、公开。

TMS320VC5416Fixed-Point Digital Signal Processor Data ManualPRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.Literature Number:SPRS095PMarch1999–Revised October2008Revision HistoryTMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH 1999–REVISED OCTOBER 2008NOTE:Page numbers for previous revisions may differ from page numbers in the current version.This data sheet revision history highlights the technical changes made to the SPRS095O device-specific data sheet to make it an SPRS095P revision.Scope:This document has been reviewed for technical accuracy;the technical content is up-to-date as of the specified release date with the following corrections.2Revision History Submit Documentation FeedbackContentsTMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH 1999–REVISED OCTOBER 2008Revision History ...........................................................................................................................1TMS320VC5416Features.......................................................................................................2Introduction.......................................................................................................................2.1Description ..................................................................................................................2.2PinAssignments............................................................................................................2.2.1TerminalAssignments forthe GGUPackage...............................................................2.2.2Pin AssignmentsforthePGEPackage......................................................................2.2.3Signal Descriptions ..............................................................................................3Functional Overview ...........................................................................................................3.1Memory ......................................................................................................................3.1.1Data Memory .....................................................................................................3.1.2Program Memory ................................................................................................3.1.3Extended Program Memory ...................................................................................3.2On-Chip ROM With Bootloader ...........................................................................................3.3On-Chip RAM ...............................................................................................................3.4On-Chip Memory Security .................................................................................................3.5Memory Map ................................................................................................................3.5.1Relocatable Interrupt Vector Table ............................................................................3.6On-Chip Peripherals .......................................................................................................3.6.1Software-Programmable Wait-State Generator .............................................................3.6.2Programmable Bank-Switching ................................................................................3.6.3Bus Holders ......................................................................................................3.7Parallel I/O Ports ...........................................................................................................3.7.1Enhanced 8-/16-Bit Host-Port Interface (HPI8/16)..........................................................3.7.2HPI Nonmultiplexed Mode ......................................................................................3.8Multichannel Buffered Serial Ports (McBSPs)..........................................................................3.9Hardware Timer ............................................................................................................3.10Clock Generator ............................................................................................................3.11Enhanced External Parallel Interface (XIO2)...........................................................................3.12DMA Controller .............................................................................................................3.12.1Features ..........................................................................................................3.12.2DMA External Access ...........................................................................................3.12.3DMA Memory Maps .............................................................................................3.12.4DMA Priority Level ...............................................................................................3.12.5DMA Source/Destination Address Modification .............................................................3.12.6DMA in Autoinitialization Mode ................................................................................3.12.7DMA Transfer Counting .........................................................................................3.12.8DMA Transfer in Doubleword Mode ..........................................................................3.12.9DMA Channel Index Registers .................................................................................3.12.10DMA Interrupts ..................................................................................................3.12.11DMA Controller Synchronization Events .....................................................................3.13General-Purpose I/O Pins .................................................................................................3.13.1McBSP Pins as General-Purpose I/O .........................................................................3.13.2HPI Data Pins as General-Purpose I/O ......................................................................3.14Device ID Register .........................................................................................................3.15Memory-Mapped Registers ...............................................................................................3.16McBSP Control Registers and Subaddresses ..........................................................................3.17DMA Subbank Addressed Registers ....................................................................................3.18Interrupts ....................................................................................................................4Support .............................................................................................................................Contents3TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 4.1Documentation Support...................................................................................................4.2Device and Development-Support Tool Nomenclature................................................................5Electrical Specifications......................................................................................................5.1Absolute Maximum Ratings...............................................................................................5.2Recommended Operating Conditions...................................................................................5.3Electrical Characteristics.................................................................................................5.3.1Test Loading.....................................................................................................5.3.2Timing Parameter Symbology............................................................................................5.3.3Internal Oscillator With External Crystal.................................................................................5.4Clock Options...............................................................................................................5.4.1Divide-By-Two and Divide-By-Four Clock Options..........................................................5.4.2Multiply-By-N Clock Option(PLL Enabled)...................................................................5.5Memory and Parallel I/O Interface Timing..............................................................................5.5.1Memory Read....................................................................................................5.5.2Memory Write....................................................................................................5.5.3I/O Read..........................................................................................................5.5.4I/O Write..........................................................................................................5.5.5Ready Timing for Externally Generated Wait States..................................................................5.5.6and Timings...............................................................................................5.5.7Reset,BIO,Interrupt,and MP/MC Timings.............................................................................5.5.8Instruction Acquisition and Interrupt Acknowledge Timings..........................................5.5.9External Flag(XF)and TOUT Timings..................................................................................5.5.10Multichannel Buffered Serial Port(McBSP)Timing...................................................................5.5.10.1McBSP Transmit and Receive Timings....................................................................5.5.10.2McBSP General-Purpose I/O Timing.......................................................................5.5.10.3McBSP as SPI Master or Slave Timing....................................................................5.5.11Host-Port Interface Timing...............................................................................................5.5.11.1HPI8Mode.....................................................................................................5.5.11.2HPI16Mode....................................................................................................6Mechanical Data.................................................................................................................6.1Package Thermal Resistance Characteristics..........................................................................4Contents Submit Documentation FeedbackTMS320VC5416Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008List of Figures2-1144-Ball GGU MicroStar BGA™(Bottom View).............................................................................2-2144-Pin PGE Low-Profile Quad Flatpack(Top View).......................................................................3-1TMS320VC5416Functional Block Diagram..................................................................................3-2Program and Data Memory Map................................................................................................3-3Extended Program Memory Map...............................................................................................3-4Process Mode Status Register..................................................................................................3-5Software Wait-State Register(SWWSR)[Memory-Mapped Register(MMR)Address0028h].........................3-6Software Wait-State Register(SWWSR)[Memory-Mapped Register(MMR)Address0028h].........................3-7Bank-Switching Control Register BSCR)[MMR Address0029h]...........................................................3-8Host-Port Interface—Nonmulltiplexed Mode.................................................................................3-9HPI Memory Map.................................................................................................................3-10Multichannel Control Register(MCR1).........................................................................................3-11Multichannel Control Register(MCR2).........................................................................................3-12Pin Control Register(PCR)......................................................................................................3-13Nonconsecutive Memory Read and I/O Read Bus Sequence.............................................................3-14Consecutive Memory Read Bus Sequence(n=3reads)..................................................................3-15Memory Write and I/O Write Bus Sequence.................................................................................3-16DMA Transfer Mode Control Register(DMMCRn)...........................................................................3-17On-Chip DMA Memory Map for Program Space(DLAXS=0and SLAXS=0).........................................3-18On-Chip DMA Memory Map for Data and IO Space(DLAXS=0and SLAXS=0)....................................3-19DMPREC Register................................................................................................................3-20General-Purpose I/O Control Register(GPIOCR)[MMR Address003Ch]................................................3-21General-Purpose I/O Status Register(GPIOSR)[MMR Address003Dh].................................................3-22Device ID Register(CSIDR)[MMR Address003Eh].........................................................................3-23IFR and IMR Registers...........................................................................................................5-1Tester Pin Electronics............................................................................................................5-2Internal Divide-By-Two Clock Option With External Crystal...............................................................5-3External Divide-By-Two Clock Timing.........................................................................................5-4Multiply-By-One Clock Timing..................................................................................................5-5Nonconsecutive Mode Memory Reads.......................................................................................5-6Consecutive Mode Memory Reads............................................................................................5-7Memory Write(MSTRB=0)....................................................................................................5-8Parallel I/O Port Read(IOSTRB=0).........................................................................................5-9Parallel I/O Port Write(IOSTRB=0)..........................................................................................5-10Memory Read With Externally Generated Wait States.....................................................................5-11Memory Write With Externally Generated Wait States.....................................................................5-12I/O Read With Externally Generated Wait States...........................................................................5-13I/O Write With Externally Generated Wait States...........................................................................5-14HOLD and HOLDA Timings(HM=1).........................................................................................List of Figures5TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 5-15Reset and BIO Timings.........................................................................................................5-16Interrupt Timing..................................................................................................................5-17MP/MC Timing...................................................................................................................5-18Instruction Acquisition(IAQ)and Interrupt Acknowledge(IACK)Timings................................................5-19External Flag(XF)Timing......................................................................................................5-20TOUT Timing.....................................................................................................................5-21McBSP Receive Timings.......................................................................................................5-22McBSP Transmit Timings.......................................................................................................5-23McBSP General-Purpose I/O Timings........................................................................................5-24McBSP Timing as SPI Master or Slave:CLKSTP=10b,CLKXP=0....................................................5-25McBSP Timing as SPI Master or Slave:CLKSTP=11b,CLKXP=0....................................................5-26McBSP Timing as SPI Master or Slave:CLKSTP=10b,CLKXP=1....................................................5-27McBSP Timing as SPI Master or Slave:CLKSTP=11b,CLKXP=1....................................................5-28Using HDS to Control Accesses(HCS Always Low)........................................................................5-29Using HCS to Control Accesses...............................................................................................5-30HINT Timing......................................................................................................................5-31GPIOx Timings...................................................................................................................5-32Nonmultiplexed Read Timings.................................................................................................5-33Nonmultiplexed Write Timings.................................................................................................5-34HRDY Relative to CLKOUT....................................................................................................6List of Figures Submit Documentation FeedbackTMS320VC5416Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008List of Tables2-1Terminal Assignments for the TMS320VC5416GGU(144-Pin BGA Package).........................................2-2Signal Descriptions...............................................................................................................3-1Standard On-Chip ROM Layout...............................................................................................3-2Processor Mode Status(PMST)Register Bit Fields........................................................................3-3Software Wait-State Register(SWWSR)Bit Fields.........................................................................3-4Software Wait-State Control Register(SWCR)Bit Fields..................................................................3-5Bank-Switching Control Register(BSCR)Fields..............................................................................3-6Bus Holder Control Bits..........................................................................................................3-7Sample Rate Input Clock Selection...........................................................................................3-8Clock Mode Settings at Reset.................................................................................................3-9DMD Section of the DMMCRn Register......................................................................................3-10DMA Reload Register Selection...............................................................................................3-11DMA Interrupts...................................................................................................................3-12DMA Synchronization Events..................................................................................................3-13DMA Channel Interrupt Selection..............................................................................................3-14Device ID Register(CSIDR)Bits................................................................................................3-15CPU Memory-Mapped Registers................................................................................................3-16Peripheral Memory-Mapped Registers for Each DSP Subsystem........................................................3-17McBSP Control Registers and Subaddresses.................................................................................3-18DMA Subbank Addressed Registers...........................................................................................3-19Interrupt Locations and Priorities................................................................................................5-1Input Clock Frequency Characteristics.........................................................................................5-2Clock Mode Pin Settings for the Divide-By-2and By Divide-By-4Clock Options.......................................5-3Divide-By-2and Divide-By-4Clock Options Timing Requirements.......................................................5-4Divide-By-2and Divide-By-4Clock Options Switching Characteristics...................................................5-5Multiply-By-N Clock Option Timing Requirements..........................................................................5-6Multiply-By-N Clock Option Switching Characteristics......................................................................5-7Memory Read Timing Requirements..........................................................................................5-8Memory Read Switching Characteristics.....................................................................................5-9Memory Write Switching Characteristics.....................................................................................5-10I/O Read Timing Requirements................................................................................................5-11I/O Read Switching Characteristics...........................................................................................5-12I/O Write Switching Characteristics............................................................................................5-13Ready Timing Requirements for Externally Generated Wait States......................................................5-14Ready Switching Characteristics for Externally Generated Wait States..................................................5-15HOLD and HOLDA Timing Requirements....................................................................................5-16HOLD and HOLDA Switching Characteristics...............................................................................5-17Reset,BIO,Interrupt,and MP/MC Timing Requirements..................................................................5-18Instruction Acquisition(IAQ)and Interrupt Acknowledge(IACK)Switching Characteristics...........................List of Tables7TMS320VC5416Fixed-Point Digital Signal ProcessorSPRS095P–MARCH1999–REVISED 5-19External Flag(XF)and TOUT Switching Characteristics...................................................................5-20McBSP Transmit and Receive Timing Requirements.......................................................................5-21McBSP Transmit and Receive Switching Characteristics..................................................................5-22McBSP General-Purpose I/O Timing Requirements........................................................................5-23McBSP General-Purpose I/O Switching Characteristics...................................................................5-24McBSP as SPI Master or Slave Timing Requirements(CLKSTP=10b,CLKXP=0).................................5-25McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=10b,CLKXP=0).............................5-26McBSP as SPI Master or Slave Timing Requirements(CLKSTP=11b,CLKXP=0).................................5-27McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=11b,CLKXP=0).............................5-28McBSP as SPI Master or Slave Timing Requirements(CLKSTP=10b,CLKXP=1).................................5-29McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=10b,CLKXP=1).............................5-30McBSP as SPI Master or Slave Timing Requirements(CLKSTP=11b,CLKXP=1).................................5-31McBSP as SPI Master or Slave Switching Characteristics(CLKSTP=11b,CLKXP=1).............................5-32HPI8Mode Timing Requirements.............................................................................................5-33HPI8Mode Switching Characteristics..........................................................................................5-34HPI16Mode Timing Requirements............................................................................................5-35HPI16Mode Switching Characteristics.......................................................................................6-1Thermal Resistance Characteristics............................................................................................8Submit Documentation Feedback List of Tables1TMS320VC5416FeaturesTMS320VC5416 Fixed-Point Digital Signal Processor SPRS095P–MARCH1999–REVISED OCTOBER2008Reads•Advanced Multibus Architecture With ThreeSeparate16-Bit Data Memory Buses and One•Arithmetic Instructions With Parallel Store and Program Memory Bus Parallel Load•40-Bit Arithmetic Logic Unit(ALU)Including a•Conditional Store Instructions40-Bit Barrel Shifter and Two Independent•Fast Return From Interrupt 40-Bit Accumulators•On-Chip Peripherals•17-×17-Bit Parallel Multiplier Coupled to a–Software-Programmable Wait-State 40-Bit Dedicated Adder for Non-Pipelined Generator and ProgrammableSingle-Cycle Multiply/Accumulate(MAC)Bank-SwitchingOperation–On-Chip Programmable Phase-Locked •Compare,Select,and Store Unit(CSSU)for the Loop(PLL)Clock Generator With External Add/Compare Selection of the Viterbi Operator Clock Source–One16-Bit Timer•Exponent Encoder to Compute an Exponent–Six-Channel Direct Memory Access(DMA) Value of a40-Bit Accumulator Value in aControllerSingle Cycle–Three Multichannel Buffered Serial Ports •Two Address Generators With Eight Auxiliary(McBSPs)Registers and Two Auxiliary Register–8/16-Bit Enhanced Parallel Host-Port Arithmetic Units(ARAUs)Interface(HPI8/16)•Data Bus With a Bus Holder Feature•Power Consumption Control With IDLE1,•Extended Addressing Mode for8M×16-Bit IDLE2,and IDLE3Instructions With Maximum Addressable External ProgramPower-Down ModesSpace•CLKOUT Off Control to Disable CLKOUT •128K×16-Bit On-Chip RAM Composed of:•On-Chip Scan-Based Emulation Logic,IEEE –Eight Blocks of8K×16-Bit On-ChipStd1149.1(JTAG)Boundary Scan Logic(1) Dual-Access Program/Data RAM•144-Pin Ball Grid Array(BGA)(GGU Suffix)–Eight Blocks of8K×16-Bit On-ChipSingle-Access Program RAM•144-Pin Low-Profile Quad Flatpack(LQFP)(PGE Suffix)•16K×16-Bit On-Chip ROM Configured forProgram Memory• 6.25-ns Single-Cycle Fixed-Point InstructionExecution Time(160MIPS)•Enhanced External Parallel Interface(XIO2)•8.33-ns Single-Cycle Fixed-Point Instruction •Single-Instruction-Repeat and Block-RepeatExecution Time(120MIPS) Operations for Program Code• 3.3-V I/O Supply Voltage(160and120MIPS)•Block-Memory-Move Instructions for BetterProgram and Data Management• 1.6-V Core Supply Voltage(160MIPS)•Instructions With a32-Bit Long Word Operand• 1.5-V Core Supply Voltage(120MIPS)(1)IEEE Standard1149.1-1990Standard-Test-Access Port and •Instructions With Two-or Three-OperandBoundary Scan ArchitectureTMS320C54x,TMS320are trademarks of Texas Instruments.All other trademarks are the property of their respective owners.PRODUCTION DATA information is current as of publication date.Copyright©1999–2008,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasInstruments standard warranty.Production processing does notnecessarily include testing of all parameters.。

国内图书分类号:F830.91国际图书分类号:339.743管理学硕士学位论文黑龙江省固定资产投资结构优化研究硕士研究生:张学发导师:胡珑瑛教授申请学位:管理学硕士学科、专业:技术经济及管理所在单位:黑龙江省财政厅答辩日期:2007年3月授予学位单位:哈尔滨工业大学Classified Index:F830.91U.D.C.: 339.743Dissertation for the Master Degree in ManagementHEILONGJIANG FIXED ASSETSCAPITAL CONSTRUCTION INVESTMENT CONSTRUCTION IS EXCELLENT TO TURN THE RESEARCHCandidate:Zhang XuefaSupervisor: Prof. Hu LongyingAcademic Degree Applied for: Master Degree of Management Specialty: Technical Economy and Management Affiliation:Heilongjiang Province Treasure Bureau Defense: March, 2007ofDateDegree-Offering-Institution: Harbin Institute of Technology哈尔滨工业大学管理学硕士学位论文摘要投资是经济增长和经济发展必不可少的重要手段,从经济学的角度看,投资增长与经济增长为互相联动的关系。

改革开放以来,固定资产投资一直在我国的经济增长中发挥着十分重要的作用,投资调控始终是政府宏观调控中一个非常重要的组成部分,无论是抑制经济过热还是扩大国内需求,投资结构调整都首当其冲。

研究固定资产投资结构优化不仅可以促进产业结构调整、能最大限度的利用各种资源,实现资源的优化配置,而且对保持整个国民经济稳定、协调、快速发展具有十分重要的意义。

使⽤SSIS对DynamicsCRM系统进⾏数据迁移嗨,各位。

近期项⽬⼀直都⾮常忙,⽽且⾃⼰也⼀直在思考职业发展的问题,所以有⾮常长⼀段时间没静下⼼写⼏篇Blog 了。

近期我參与的项⽬是Dynamics CRM 2011 到 Dynamics CRM 2013 Online的数据迁移,刚好接着今天这个机会和⼤家分析⼀下数据迁移的⼼得吧。

读过我之前⽂章的朋友肯定记得我把Dynamics CRM的接⼝分为了两⼤类:1)功能接⼝,2)数据接⼝。

今天要说的数据迁移能够理解为数据接⼝,实现数据接⼝的⽅式有⾮常多种,⽐⽅C#制作的程序,数据库层的SQL 脚本,以及今天我要和给⼤家介绍的主⾓SQL Server Integration Service(SSIS)。

为什么要使⽤SSIS呢?肯定是简单了,SSIS提供了功能丰富的控件给我们使⽤,⽐⽅:FTP控件,Excel控件,以及⼤量五花⼋门的控件以及第三⽅组件。

回到今天我们的话题,怎样使⽤SSIS实现Dynamics CRM 2011 与 Dynamics CRM 2013之前的数据迁移呢?我们有两种⽅案可选:1)使⽤Script Component编写Proxy来处理Dynamics CRM数据的CRUD操作,2)使⽤第三⽅的Dynamics CRM Component实现Dynamics CRM数据的CRUD操作。

这⾥就要依据项⽬情况来进⾏把控了,假设数据量不是⾮常多,且数据结构简单,当然是⽤ScriptComponent了,反之则是第三反的收费组件,⽐如:Cozyroc, SSIS Integration Toolkit for Dynamics CRM。

顺便提下,第⼆个组件是⼜咱们的Denical Cai开发的。

在数据迁移的过程中,最⿇烦的事情还是处理特殊结构的实体,⽐如活动类型的实体Service Appointment,以及包括Party List 控件的Opportunity实体。