CMOS逻辑门电路图形符号

- 格式:pdf

- 大小:56.16 KB

- 文档页数:2

两P增强型并联,两N增强型串联.-----与非门两P增强型串联,两N增强型并联------或非门PMOS门:低电平导通,高电平截止。

NMOS门:低电平截止,高电平导通。

带缓冲级的COMS门电路其输出电阻、输出高低电平均不受输入端状态的影响,电压传输特性更陡。

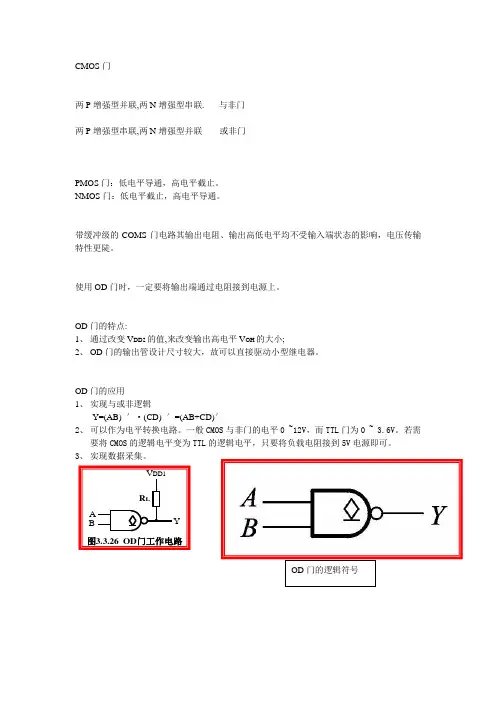

使用OD门时,一定要将输出端通过电阻接到电源上。

OD门的特点:1、通过改变V DD2的值,来改变输出高电平V OH的大小;2、OD门的输出管设计尺寸较大,故可以直接驱动小型继电器。

OD门的应用1、实现与或非逻辑Y=(AB)′·(CD)′=(AB+CD)′2、可以作为电平转换电路。

一般CMOS与非门的电平0 ~12V,而TTL门为0 ~ 3.6V。

若需要将CMOS的逻辑电平变为TTL的逻辑电平,只要将负载电阻接到5V电源即可。

3、实现数据采集。

V DD1R LAB Y图3.3.26 OD门工作电路OD门的逻辑符号1、 C=0,C ˊ=1输出V O =0.输入输出之间高阻态,传输门截至。

2、 C=1,C ˊ=0输出V O =V I 。

输入输出之间低阻态,传输门导通。

特点:1、 其输出端和输入端也可以互换使用2、 利用CMOS 传输门可以组成双向模拟开关,用来传输连续变化的模拟电压信号CMOS 双向模拟开关电路是由CMOS 传输门和反相器组成,其工作原理为:当C =1,开关闭合,Vo = V I ;当C =0 ,开关断开,Vo =0,输出高阻态。

CMOS 双向模拟开关:当C =1时,开关接通,输出电压为当C=0时,开关截止,V O =0.为得到尽量大且稳定的典雅传输系数,应使R L >>R TG三态输出的CMOS 逻辑门输出状态有三态:高电平,低电平,高阻态。

EN ˊ=0时,Y=A ˊ ITG ILTG L o vK v R R R v =+=ENˊ=1时,Y=Z(高阻态)ENˊ为使能端(控制端),为低电平有效。

另一种三态门:(注意简化图)当EN=1时,T'2导通,Y =A;当EN=0时,T'2、T1截止,输出为Y =Z(高阻态)。

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用C MOS工艺制成的。

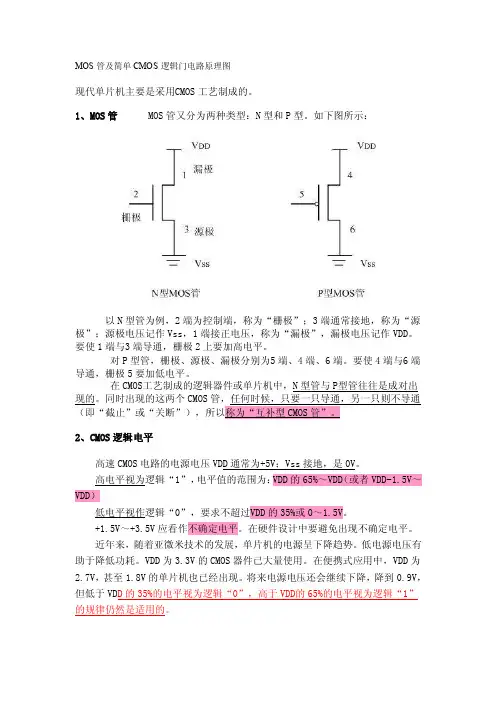

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMO S2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过V DD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMO S器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMO S管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与VDD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

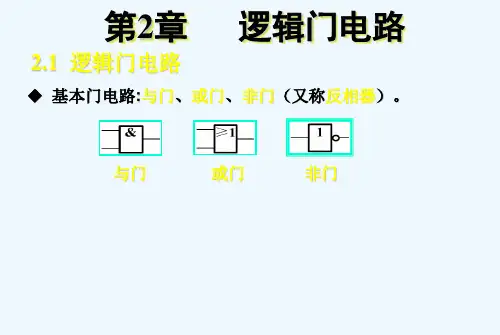

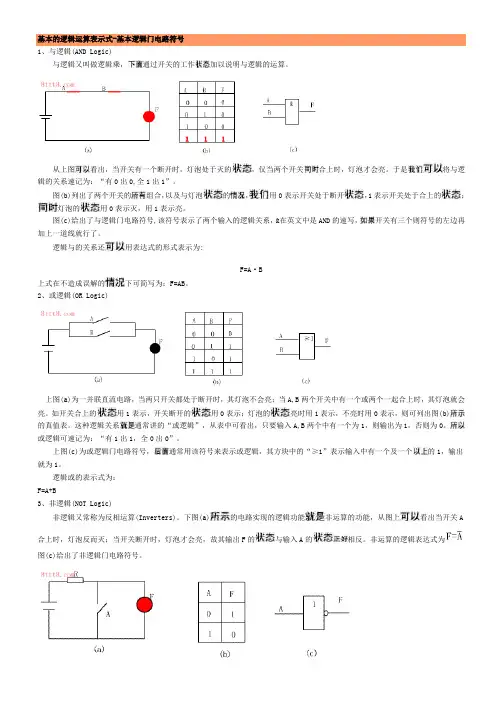

基本的逻辑运算表示式-基本逻辑门电路符号1、与逻辑(AND Logic)与逻辑又叫做逻辑乘,通过开关的工作加以说明与逻辑的运算。

从上图看出,当开关有一个断开时,灯泡处于灭的,仅当两个开关合上时,灯泡才会亮。

于是将与逻辑的关系速记为:“有0出0,全1出1”。

图(b)列出了两个开关的组合,以及与灯泡的,用0表示开关处于断开,1表示开关处于合上的;灯泡的用0表示灭,用1表示亮。

图(c)给出了与逻辑门电路符号,该符号表示了两个输入的逻辑关系,&在英文中是AND的速写,开关有三个则符号的左边再加上一道线就行了。

逻辑与的关系还用表达式的形式表示为:F=A·B上式在不造成误解的下可简写为:F=AB。

2、或逻辑(OR Logic)上图(a)为一并联直流电路,当两只开关都处于断开时,其灯泡不会亮;当A,B两个开关中有一个或两个一起合上时,其灯泡就会亮。

如开关合上的用1表示,开关断开的用0表示;灯泡的亮时用1表示,不亮时用0表示,则可列出图(b)的真值表。

这种逻辑关系通常讲的“或逻辑”,从表中可看出,只要输入A,B两个中有一个为1,则输出为1,否则为0。

或逻辑可速记为:“有1出1,全0出0”。

上图(c)为或逻辑门电路符号,通常用该符号来表示或逻辑,其方块中的“≥1”表示输入中有一个及一个的1,输出就为1。

逻辑或的表示式为:F=A+B3、非逻辑(NOT Logic)非逻辑又常称为反相运算(Inverters)。

下图(a)的电路实现的逻辑功能非运算的功能,从图上看出当开关A 合上时,灯泡反而灭;当开关断开时,灯泡才会亮,故其输出F的与输入A的相反。

非运算的逻辑表达式为图(c)给出了非逻辑门电路符号。

复合逻辑运算在数字系统中,除了与运算、或运算、非运算之外,使用的逻辑运算还有是通过这三种运算派生出来的运算,这种运算通常称为复合运算,的复合运算有:与非、或非、与或非、同或及异或等。

4、与非逻辑(NAND Logic)与非逻辑是由与、非逻辑复合而成的。

CMOS逻辑门电路CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件。

CMOS电路的工作速度可与TTL 相比较,而它的功耗和抗干扰能力则远优于TTL。

此外,几乎所有的超大规模存储器件,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,随后发展为4000B系列。

当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。

下面首先讨论CMOS反相器,然后介绍其他CMO逻辑门电路。

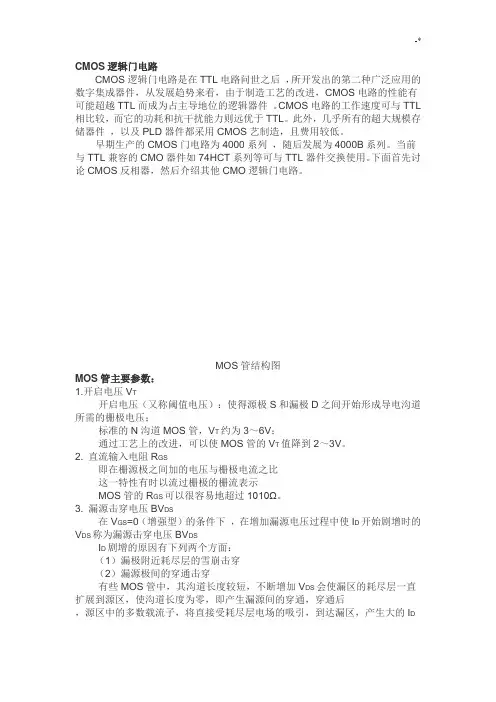

MOS管结构图MOS管主要参数:1.开启电压V T·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,V T约为3~6V;·通过工艺上的改进,可以使MOS管的V T值降到2~3V。

2. 直流输入电阻R GS·即在栅源极之间加的电压与栅极电流之比·这一特性有时以流过栅极的栅流表示·MOS管的R GS可以很容易地超过1010Ω。

3. 漏源击穿电压BV DS·在V GS=0(增强型)的条件下,在增加漏源电压过程中使I D开始剧增时的V DS称为漏源击穿电压BV DS·I D剧增的原因有下列两个方面:(1)漏极附近耗尽层的雪崩击穿(2)漏源极间的穿通击穿·有些MOS管中,其沟道长度较短,不断增加V DS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的I D4. 栅源击穿电压BV GS·在增加栅源电压过程中,使栅极电流I G由零开始剧增时的V GS,称为栅源击穿电压BV GS。

5. 低频跨导g m·在V DS为某一固定数值的条件下,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导·g m反映了栅源电压对漏极电流的控制能力·是表征MOS管放大能力的一个重要参数·一般在十分之几至几mA/V的范围内6. 导通电阻R ON·导通电阻R ON说明了V DS对I D的影响,是漏极特性某一点切线的斜率的倒数·在饱和区,I D几乎不随V DS改变,R ON的数值很大,一般在几十千欧到几百千欧之间·由于在数字电路中,MOS管导通时经常工作在V DS=0的状态下,所以这时的导通电阻R ON可用原点的R ON来近似·对一般的MOS管而言,R ON的数值在几百欧以内7. 极间电容·三个电极之间都存在着极间电容:栅源电容C GS 、栅漏电容C GD和漏源电容CDS·C GS和C GD约为1~3pF·C DS约在0.1~1pF之间8. 低频噪声系数NF·噪声是由管子内部载流子运动的不规则性所引起的·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)·这个数值越小,代表管子所产生的噪声越小·低频噪声系数是在低频范围内测出的噪声系数·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小一、CMOS反相器由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。

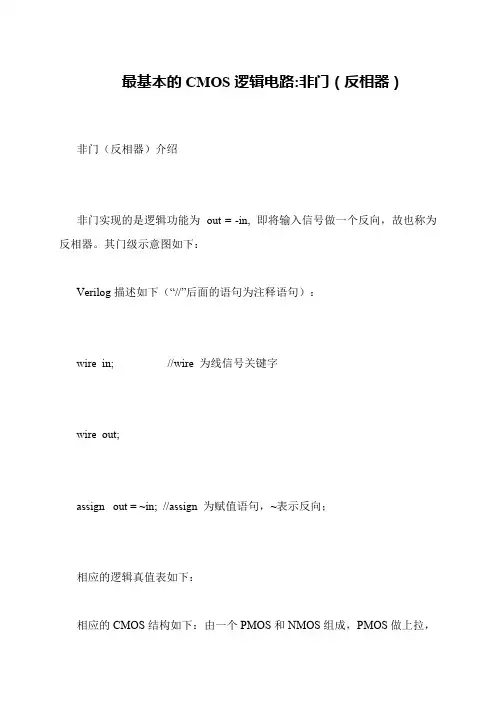

最基本的CMOS逻辑电路:非门(反相器)

非门(反相器)介绍

非门实现的是逻辑功能为 out = -in, 即将输入信号做一个反向,故也称为反相器。

其门级示意图如下:

Verilog描述如下(“//”后面的语句为注释语句):

wire in; //wire 为线信号关键字

wire out;

assign out = ~in; //assign 为赋值语句,~表示反向;

相应的逻辑真值表如下:

相应的CMOS结构如下:由一个PMOS和NMOS组成,PMOS做上拉,

与VDD相连;NMOS做下拉,与GND相连。

简单分析一下我们要实现的功能,无非就是当in 为0 (低电平)时,out输出为1(高电平),即out跟电源VDD相连;当in 为1(高电平)时,out输出为0(低电平),即out要跟GND(地)相连。

故上面的非门CMOS电路的等效电路如下:当in 为0时开关k1闭合,k2打开,即out与VDD相连,输出为1;当in 为1时开关k1打开,k2闭合,即out与GND相连,输出为0。

故PMOS相当于一个开关,如下当G端为低电平时,D端与S端才连通;

故NMOS相当于一个开关,如下当G端为高电平时,D端与S端才连通;

拓展:现在常见的数字集成电路其底层的基本逻辑电路都是由CMOS结构构成。

上拉逻辑部分由PMOS组成,下拉逻辑部分由NMOS组成。

反相器就是一个最基本的CMOS逻辑电路,上拉部分只有一个PMOS,下拉部分只有一个NMOS。

后面还会讲到其它逻辑门电路,到时候大家对CMOS逻辑的了解就更深入了。

MOS管及简单CMOS逻辑门电路原理图现代单片机主要是采用CMOS工艺制成的。

1、MOS管 MOS管又分为两种类型:N型和P型。

如下图所示:以N型管为例,2端为控制端,称为“栅极”;3端通常接地,称为“源极”;源极电压记作Vss,1端接正电压,称为“漏极”,漏极电压记作VDD。

要使1端与3端导通,栅极2上要加高电平。

对P型管,栅极、源极、漏极分别为5端、4端、6端。

要使4端与6端导通,栅极5要加低电平。

在CMOS工艺制成的逻辑器件或单片机中,N型管与P型管往往是成对出现的。

同时出现的这两个CMOS2、CMOS逻辑电平高速CMOS电路的电源电压VDD通常为+5V;Vss接地,是0V。

高电平视为逻辑“1”,电平值的范围为:VDD的65%~VDD(或者VDD-1.5V~VDD)低电平视作逻辑“0”,要求不超过VDD的35%或0~1.5V。

+1.5V~+3.5V应看作不确定电平。

在硬件设计中要避免出现不确定电平。

近年来,随着亚微米技术的发展,单片机的电源呈下降趋势。

低电源电压有助于降低功耗。

VDD为3.3V的CMOS器件已大量使用。

在便携式应用中,VDD为2.7V,甚至1.8V的单片机也已经出现。

将来电源电压还会继续下降,降到0.9V,但低于VDD的35%的电平视为逻辑“0”,高于VDD的65%的电平视为逻辑“1”的规律仍然是适用的。

3、非门非门(反向器)是最简单的门电路,由一对CMOS管组成。

其工作原理如下:A端为高电平时,P型管截止,N型管导通,输出端C的电平与Vss保持一致,输出低电平;A端为低电平时,P型管导通,N型管截止,输出端C的电平与V DD一致,输出高电平。

4、与非门与非门工作原理:①、A、B输入均为低电平时,1、2管导通,3、4管截止,C端电压与V DD 一致,输出高电平。

②、A输入高电平,B输入低电平时,1、3管导通,2、4管截止,C端电位与1管的漏极保持一致,输出高电平。

③、A输入低电平,B输入高电平时,情况与②类似,亦输出高电平。

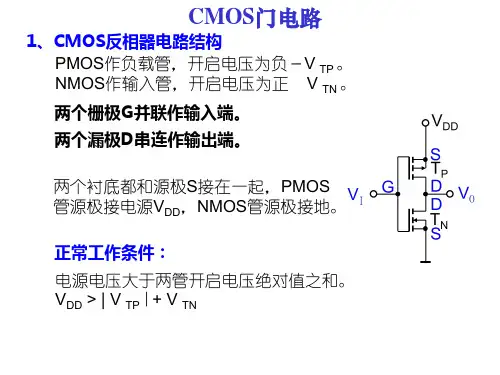

CMOS 逻辑门电路CMOS 是互补对称MOS 电路的简称(Complementary Metal-Oxide-Semiconductor ),其电路结构都采用增强型PMOS 管和增强型NMOS 管按互补对称形式连接而成,由于CMOS 集成电路具有功耗低、工作电流电压范围宽、抗干扰能力强、输入阻抗高、扇出系数大、集成度高,成本低等一系列优点,其应用领域十分广泛,尤其在大规模集成电路中更显示出它的优越性,是目前得到广泛应用的器件。

一、CMOS 反相器CMOS 反相器是CMOS 集成电路最基本的逻辑元件之一,其电路如图11-36所示,它是由一个增强型NMOS 管T N 和一个PMOS 管T P 按互补对称形式连接而成。

两管的栅极相连作为反相器的输入端,漏极相连作为输出端,T P 管的衬底和源极相连接电源U DD ,T N 管的衬底与源极相连后接地,一般地U DD >(U TN +|U TP |),(U TN和|U TP |是T N 和T P 的开启电压)。

当输入电压u i =“0”(低电平)时,NMOS 管T N 截止,而PMOS 管T P 导通,这时T N 管的阻抗比T P 管的阻抗高的多,(两阻抗比值可高达106以上),电源电压主要降在T N 上,输出电压为“1”(约为U DD )。

当输入电压u i =“1”(高电平)时,T N 导通,T P 截止,电源电压主要降在T P 上,输出u o =“0”,可见此电路实现了逻辑“非”功能。

通过CMOS 反相器电路原理分析,可发现CMOS 门电路相比NMOS 、PMOS 门电路具有如下优点:①无论输入是高电平还是低电平,T N 和T P 两管中总是一个管子截止,另一个导通,流过电源的电流仅是截止管的沟道泄漏电流,因此,静态功耗很小。

②两管总是一个管子充分导通,这使得输出端的等效电容C L 能通过低阻抗充放电,改善了输出波形,同时提高了工作速度。

③由于输出低电平约为0V ,输出高电平为U DD ,因此,输出的逻辑幅度大。