数字频率计电路原理图

- 格式:pdf

- 大小:75.19 KB

- 文档页数:2

课题三数字频率计逻辑电路设计一﹑简述在进行模拟﹑数字电路的设计﹑安装和调试过程中,经常要用到数字频率计。

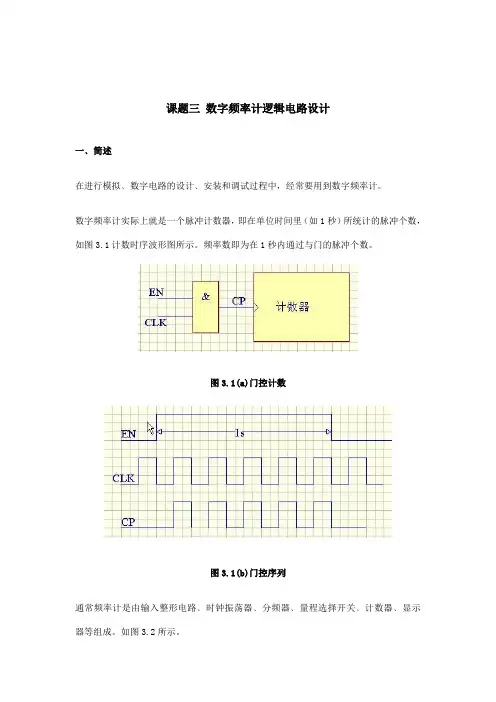

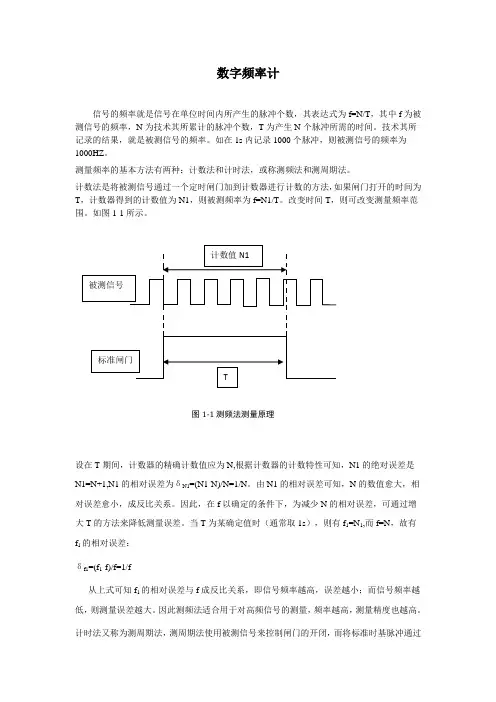

数字频率计实际上就是一个脉冲计数器,即在单位时间里(如1秒)所统计的脉冲个数,如图3.1计数时序波形图所示。

频率数即为在1秒内通过与门的脉冲个数。

图3.1(a)门控计数图3.1(b)门控序列通常频率计是由输入整形电路﹑时钟振荡器﹑分频器﹑量程选择开关﹑计数器﹑显示器等组成。

如图3.2所示。

图3.2 方框图图3.2中,由于计数信号必须为方波信号,所以要用史密特触发器对输入波形进行整形,分频器输出的信号必须为1Hz,即脉冲宽度为1秒,这个秒脉冲加到与门上,就能检测到待测信号在1秒内通过与门的个数。

脉冲个数由计数器计数,结果由七段显示器显示。

二﹑设计任务和要求设计一个八位的频率计数器逻辑控制线路,具体任务和要求如下:1. 八位十进制数字显示。

2. 测显范围为1Hz~10MHz。

3. 量程分为四档,分别为*1000﹑*100﹑*10﹑*1。

三﹑可选用器材1. NET系列数字电子技术实验系统2. 直流稳压电源3. 集成电路:频率计数器专用芯片ICM7216B,74LS93,74LS123,74LS390,7555及门电路4. 晶振:8MHz,10MHz5. 数显:CL102,CL002,LC5011—116. 电阻﹑电容等四﹑设计方案提示数字频率计可分为三部分进行考虑:1. 计数﹑译码﹑显示这一部分是频率计数器不可少的。

即外部整形后的脉冲。

通过计数器在单位时间里进行计数﹑译码和显示。

计数器选用十进制的中规模(TTL/CMOS)集成计数器均可,译码显示可采用共阴或共阳的配套器件。

例如计数器选用74LS161,译码器为74LS248,数显器为LC5011—11。

也可选用四合一计数﹑寄存﹑译码﹑显示CL102或专用大规模频率计数器ICM7216芯片等。

中规模组成的计数﹑译码显示和四合一的数显。

我们在基本实验和前几个课题中都已使用过,使用时,可参阅有关章节。

频率计的设计内容介绍:数字频率计是用来测量信号频率的装置。

它可以测量正弦波、方波、三角波和尖脉冲信号的频率。

在进行模拟、数字电路的设计、安装、调试的过程中,经常要用到频率计。

由于其用十进制数显示,测量速度快、精度高、显示直观,因此频率计得到广泛的应用。

一、设计内容及技术指标设计内容:设计用四只数码管显示结果的数字频率计。

技术指标:1、测量信号:正弦波、方波、三角波2、被测量信号频率范围:1HZ—9999HZ3、显示方式:4位十进制数显示4、时基电路由555定时器组成多谐振荡器产生的时基信号,其脉冲宽度分别为:正脉冲 1S,负脉冲0.25S二、电路原理及框图数字频率计测频率的基本原理:所谓频率,就是周期性信号在单位时间(1s)内变化的次数。

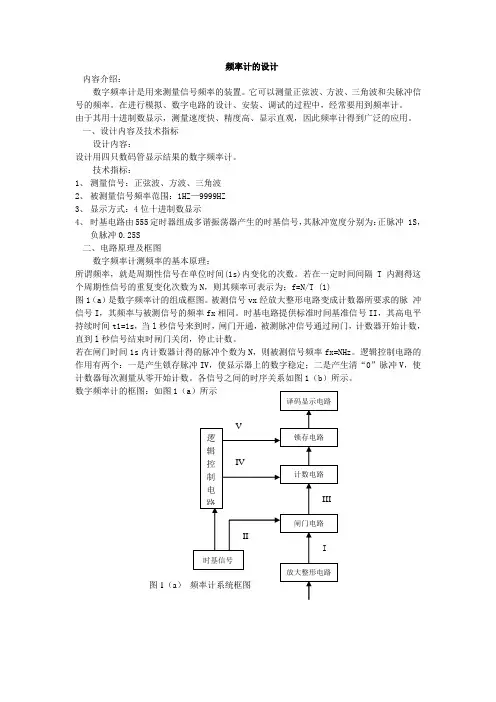

若在一定时间间隔T 内测得这个周期性信号的重复变化次数为N,则其频率可表示为:f=N/T (1)图1(a)是数字频率计的组成框图。

被测信号vx经放大整形电路变成计数器所要求的脉冲信号I,其频率与被测信号的频率fx相同。

时基电路提供标准时间基准信号II,其高电平持续时间t1=1s,当l秒信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到l秒信号结束时闸门关闭,停止计数。

若在闸门时间1s内计数器计得的脉冲个数为N,则被测信号频率fx=NHz。

逻辑控制电路的作用有两个:一是产生锁存脉冲IV,使显示器上的数字稳定;二是产生清“0”脉冲V,使计数器每次测量从零开始计数。

各信号之间的时序关系如图1(b)所示。

I所谓频率,就是周期性信号的在单位时间(1s )内变化的次数,若在一定时间间隔T 内测得这个周期性信号的重复变化次数为N ,则其频率可表示为:T N f = (2.2.1)上图是数字频率计的结构框图。

被测信号X V 经放大整形电路变成计数器所要求的脉冲信号I ,其频率与被测信号的频率x f 相同。

时基电路提供标准时间基准信号II ,其高电平持续的时间s t 11=,当s 1信号来到时,闸门开通,被测脉冲信号通过闸门,计数器开始计数,直到s 1信号结束时闸门关闭,停止计数。

数字频率计信号的频率就是信号在单位时间内所产生的脉冲个数,其表达式为f=N/T,其中f为被测信号的频率,N为技术其所累计的脉冲个数,T为产生N个脉冲所需的时间。

技术其所记录的结果,就是被测信号的频率。

如在1s内记录1000个脉冲,则被测信号的频率为1000HZ。

测量频率的基本方法有两种:计数法和计时法,或称测频法和测周期法。

计数法是将被测信号通过一个定时闸门加到计数器进行计数的方法,如果闸门打开的时间为T,计数器得到的计数值为N1,则被测频率为f=N1/T。

改变时间T,则可改变测量频率范围。

如图1-1所示。

设在T期间,计数器的精确计数值应为N,根据计数器的计数特性可知,N1的绝对误差是N1=N+1,N1的相对误差为δN1=(N1-N)/N=1/N。

由N1的相对误差可知,N的数值愈大,相对误差愈小,成反比关系。

因此,在f以确定的条件下,为减少N的相对误差,可通过增大T的方法来降低测量误差。

当T为某确定值时(通常取1s),则有f1=N1,而f=N,故有f1的相对误差:δf1=(f1-f)/f=1/f从上式可知f1的相对误差与f成反比关系,即信号频率越高,误差越小;而信号频率越低,则测量误差越大。

因此测频法适合用于对高频信号的测量,频率越高,测量精度也越高。

计时法又称为测周期法,测周期法使用被测信号来控制闸门的开闭,而将标准时基脉冲通过闸门加到计数器,闸门在外信号的一个周期内打开,这样计数器得到的计数值就是标准时基脉冲外信号的周期值,然后求周期值的倒数,就得到所测频率值。

首先把被测信号通过二分频,获得一个高电平时间是一个信号周期T的方波信号;然后用一个一直周期T1的高频方波信号作为计数脉冲,在一个信号周期T的时间内对T1信号进行计数,如图1-2所示。

图2-2计时法测量原理图1-2计时法测量原理若在T时间内的计数值为N2,则有:T2=N2*T1f2=1/T2=1/(N2*T1)=f1/N2N2的绝对误差为N2=N+1。

数字频率计的基来源根基理之宇文皓月创作设计并制作出一种数字频率计,其技术指标如下:1.频率丈量范围: 10 ~ 9999Hz 。

2.输入信号波形:任意周期信号。

输入电压幅度 >300mV 。

3.电源: 220V 、 50Hz4. 系统框图从数字频率计的基来源根基理出发,根据设计要求,得到如图1所示的电路框图。

图1 数字频率计框图下面介绍框图中各部分的功能及实现方法(1)电源与整流稳压电路框图中的电源采取50Hz的交流市电。

市电被降压、整流、稳压后为整个系统提供直流电源。

系统对电源的要求不高,可以采取串联式稳压电源电路来实现。

(2)全波整流与波形整形电路本频率计采取市电频率作为尺度频率,以获得稳定的基准时间。

按国家尺度,市电的频率漂移不克不及超出0.5Hz,即在1%的范围内。

用它作普通频率计的基准信号完全能满足系统的要求。

全波整流电路首先对50Hz交流市电进行全波整流,得到如图2(a)所示100Hz的全波整流波形。

波形整形电路对100Hz信号进行整形,使之成为如图2(b)所示100Hz的矩形波。

波形整形可以采取过零触发电路将全波整流波形变成矩形波,也可采取施密特触发器进行整形。

图2 全波整流与波形整形电路的输出波形(3)分频器分频器的作用是为了获得1S的尺度时间。

电路首先对图2所示的100Hz信号进行100分频得到如图3(a)所示周期为1S 的脉冲信号。

然后再进行二分频得到如图3(b)所示占空比为50%脉冲宽度为1S的方波信号,由此获得丈量频率的基准时间。

利用此信号去打开与关闭控制门,可以获得在1S时间内通过控制门的被测脉冲的数目。

图3 分频器的输出波形分频器可以采取教材中介绍过的方法,由计数器通过计数获得。

二分频可以采取触发器来实现。

(4)信号放大、波形整形电路为了能丈量分歧电平值与波形的周期信号的频率,必须对被测信号进行放大与整形处理,使之成为能被计数器有效识此外脉冲信号。

信号放大与波形整形电路的作用即在于此。

资料范本本资料为word版本,可以直接编辑和打印,感谢您的下载数字频率计电路地点:__________________时间:__________________说明:本资料适用于约定双方经过谈判,协商而共同承认,共同遵守的责任与义务,仅供参考,文档可直接下载或修改,不需要的部分可直接删除,使用时请详细阅读内容第二章电路的总体设计方案2.1方案论证与选择2.1.1方案的提出方案一电路整体框架如图一所示。

被测信号经过放大,整形电路将其转换成同频率的脉动信号,送入计数器进行计数,闸门的一个输入信号是秒脉冲发出的标准脉冲信号,秒脉冲信号源含有个高稳定的石英振荡器和一个多级分频器共同决定,其时间是相当精确的,计数器显示电路采用七段共阴极LED数码管。

图 2-1 方案一框架图方案二:本方案采用单片机程序处理输入信号并且将结果直接送往LED显示,为了提高系统的稳定性,输入信号前进行放大整形,在通过A/D转换器输入单片机系统,采用这种方法可大大提高测试频率的精度和灵活性,并且能极大的减少外部干扰,采用VDHL编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA芯片上实现,整个系统非常精简,而且具有灵活的现场可更改性。

但采用这种方案相对设计复杂度将会大大提高并且采用单片机系统成本也会大大提高。

图2-2 方案二框架图方案三:采用频率计专用模块,即大规模集成电路将计数器、锁存器、译码、位和段驱动,量程及小数点选择等电路集成在一块芯片中,该方案在技术上是可行的,可以简化电路的设计,当对于设计要求中的某些指标,采用专用模块来完成比较困难,即扩展极为不便。

图2-3 方案三框架图2.1.2方案的的比较方案一:具有设计复杂度小、电路简洁、功能实用且成本低廉等特点,其稳定性较好基本能满足设计要求。

方案二:采用单片机处理能较高要求,但成本提高且设计复杂,虽然可以达到很高的精度要求,但是,VHDL编程语言是我们在学习过程中没有接触过的,短期内也很难掌握并且熟练运用。

数字频率计设计报告一内容提要:数字频率计是一种用十进制数字显示被测信号频率的数字测量仪器.它的基本功能是测量正弦信号.方波信号,尖脉冲信号及其他各种单位时间内变化的物理量.本文粗略讲述了我在本次实习中的整个设计过程及收获。

二设计内容及要求:要求设计一个简易的数字频率计,其信号是给定的脉冲信号,是比较稳定的。

1.测量信号:方波;2.测量频率范围: 1Hz~999Hz ;3.显示方式: 3位十进制数显示;4.时基电路由 555 定时器产生;三设计思路及原理:数字频率计由四部分组成:时基电路、闸门电路、逻辑控制电路以及可控制的计数、译码、显示电路。

由555 定时器,分级分频系统及门控制电路得到具有固定宽度T的方波脉冲做门控制信号,时间基准T称为闸门时间.宽度为T的方波脉冲控制闸门的一个输入端B.被测信号频率为fx,周期Tx.到闸门另一输入端A.当门控制电路的信号到来后,闸门开启,周期为Tx的信号脉冲和周期为T的门控制信号结束时过闸门,于输出端 C 产生脉冲信号到计数器,计数器开始工作,直到门控信号结束,闸门关闭.单稳1的暂态送入锁存器的使能端,锁存器将计数结果锁存,计数器停止计数并被单稳2暂态清零. (简单地说就是:在时基电路脉冲的上升沿到来时闸门开启,计数器开始计数,在同一脉冲的下降沿到来时,闸门关闭,计数器停止计数.同时,锁存器产生一个锁存信号输送到锁存器的使能端将结果锁存,并把锁存结果输送到译码器来控制七段显示器,这样就可以得到被测信号的数字显示的频率.而在锁存信号的下降沿到来时逻辑控制电路产生一个清零信号将计数器清零,为下一次测量做准备,实现了可重复使用,避免两次测量结果相加使结果产生错误.) 若T=1s,计数器显示fx=N(T时间内的通过闸门信号脉冲个数) 若T=0.1s,通过闸门脉冲个数位N时,fx=10N,(闸门时间为0.1s时通过闸门的脉冲个数).也就是说,被测信号的频率计算公式是fx=N/T.由此可见,闸门时间决定量程,可以通过闸门时基选择开关,选择T大一些,测量准确度就高一些,T小一些,则测量准确度就低.根据被测频率选择闸门时间来控制量程.被测信号频率通过计数锁存可直接从计数显示器上读出.在整个电路中,时基电路是关键,闸门信号脉冲宽度是否精确直接决定了测量结果是否精确.因此,可得出数字频率计的原理框图如下:四:设计分析1.时基电路其基本电路图如左:I555定时器组成的振荡器(即脉冲产生电路),要求其产生1S高电平的脉冲.振荡器的频率计算公式为:T1=(R30+R31)*C*ln2,因此,我们可以计算出各个参数通过计算确定了R30取30k欧姆,R31取10k欧姆,电容取47uF.这样我们得到了比较稳定的一秒时基信号。

电路CAD课程设计报告设计题目:简易数字频率计专业班级:电子信息0701学号:学生姓名:同组学生:简易数字频率计摘要在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分紧密的联系,因此频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是测量频率的重要手段之一。

电子计数器测频有两种方式:一是直接测频法;二是间接测频法,如周期测频法。

本文阐述了基于通用集成电路设计了一个简单的数字频率计的过程。

AbstractBe one of the most fundamnetal parameter in electron technology medium frequency, parameter measurement scheme,measurement result all have very close something to do with a lot of electricity and,the frequency measurement looks like being more important therefore right away.The method measuring frequency has various,among them the electronic counter measures frequency having accuracy height,usage is conveient, measurement is prompt,easy to realize measurement process automation waits for merit and,is one of the important means that frequency measures.The electronic counter frequency having two kinds way:Measure frequency law first directly;Two is indirect measure frequency law,if the period measure frequency law.目录一、设计任务与要求 (3)二、方案设计与论证 (3)三、单元电路设计与参数计算 (4)1. 我所设计的电路单元 (4)2.各部分单元电路原理图 (5)3. 计频电路部分 (6)4. 计频电路部分电路原理图 (7)5. 单元电路总结 (8)四、总原理图及元器件清单 (9)1.总原理 (9)2.说明 (10)3.元器件清单 (10)五、结论与心得 (10)六、设计后思考 (10)参考文献 (11)一、设计任务与要求设计一个简易数字频率,该频率计测量频率小于10kHz。

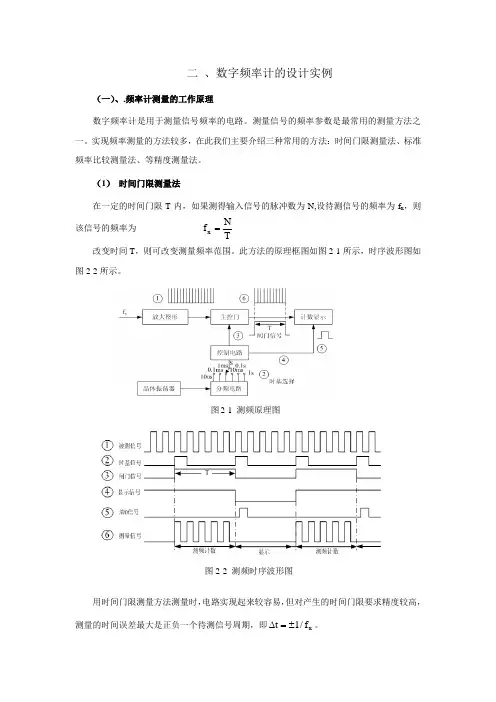

二 、数字频率计的设计实例(一)、.频率计测量的工作原理数字频率计是用于测量信号频率的电路。

测量信号的频率参数是最常用的测量方法之一。

实现频率测量的方法较多,在此我们主要介绍三种常用的方法:时间门限测量法、标准频率比较测量法、等精度测量法。

(1) 时间门限测量法在一定的时间门限T 内,如果测得输入信号的脉冲数为N,设待测信号的频率为f x ,则该信号的频率为 TNf x =改变时间T ,则可改变测量频率范围。

此方法的原理框图如图2-1所示,时序波形图如图2-2所示。

用时间门限测量方法测量时,电路实现起来较容易,但对产生的时间门限要求精度较高,测量的时间误差最大是正负一个待测信号周期,即x f /1t ±=∆。

图2-1 测频原理图图2-2 测频时序波形图(2)标准频率比较测量法用两组计数器在相同的时间门限内同时计数,测得待测信号的脉冲个数为N 1、已知的标准频率信号的脉冲个数为N 2,设待测信号的频率为f x ,已知的标准频率信号的频率为f 0;由于测量时间相同,则可得到如下等式:21N f N f x = 从上式可得出待测信号的频率公式为: 021f N N f x =标准频率比较测量法对测量产生的时间门限的精度要求不高,对标准频率信号的频率准确度和稳定度要求较高,标准信号的频率越高,测量的精度就越高。

该方法的测量时间误差与时间门限测量法的相同,可能的最大误差为正负一个待测信号周期,即x f /1t ±=∆。

测量时可能产生的误差时序波形如图2-3所示。

(3)等精度测量法以上介绍的两种测量频率的方法实现电路容易,但是,测量的精度与待测信号的频率有关,待测信号频率越高,测量的精度就越高,反之,测量精度越低。

为了提高测量低频时的精度,使得测量的高、低频率精度都一样,一般采用等精度测量法。

上面介绍的两种方法都是在闸门门限的控制下来实现计数器的计数开始和结束的。

当闸门门限的上升沿到来时,计数器计数开始,当闸门门限的下降沿到来时,计数器计数结束。

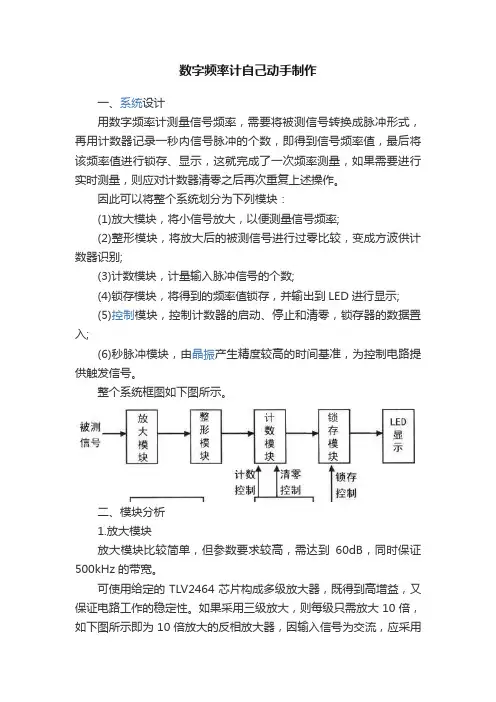

数字频率计自己动手制作一、系统设计用数字频率计测量信号频率,需要将被测信号转换成脉冲形式,再用计数器记录一秒内信号脉冲的个数,即得到信号频率值,最后将该频率值进行锁存、显示,这就完成了一次频率测量,如果需要进行实时测量,则应对计数器清零之后再次重复上述操作。

因此可以将整个系统划分为下列模块:(1)放大模块,将小信号放大,以便测量信号频率;(2)整形模块,将放大后的被测信号进行过零比较,变成方波供计数器识别;(3)计数模块,计量输入脉冲信号的个数;(4)锁存模块,将得到的频率值锁存,并输出到LED进行显示;(5)控制模块,控制计数器的启动、停止和清零,锁存器的数据置入;(6)秒脉冲模块,由晶振产生精度较高的时间基准,为控制电路提供触发信号。

整个系统框图如下图所示。

二、模块分析1.放大模块放大模块比较简单,但参数要求较高,需达到60dB,同时保证500kHz的带宽。

可使用给定的TLV2464芯片构成多级放大器,既得到高增益,又保证电路工作的稳定性。

如果采用三级放大,则每级只需放大10倍,如下图所示即为10倍放大的反相放大器,因输入信号为交流,应采用±3V双电源供电。

由于输入信号幅度很小,而且频率最低达10Hz,所以应采用直接耦合的方式级联。

2.整形模块整形模块应使用给定的TLC372芯片构成过零电压比较器,将放大信号转换成TTL电平,因此采用+5v单电源供电即可,如下图所示。

3.计数模块计数模块使用给定的CC4518芯片构成,EN端作为时钟输入端以便级联使用,CLK作为计数控制端,MR接清零信号,即实现十进制计数,如下图所示。

其最高位输出Q3直接连接次级EN,即可实现级联,每个CC4518包含两个计数器,因此至少需要3片CC4518才能完成lOOk计数。

4.锁存模块锁存模块使用给定的SN74LS175芯片构成,由于测量精度为lOHz~lOOkHz,因此至少需要显示4个数据。

每个锁存器存储4位BCD二进制码,DO—D3接计数器的数据输出,CLK接锁存控制信号,MR接高电平禁止清零,输出接LED显示,如下图所示。

毕业设计(论文)设计(论文)题目简易数字频率计的设计---电路仿真分析与PCB板图绘制学院电信工程学院教学系通信技术系班级原理图和PCB图我剪了。

要的加QQ 姓名不要图就直接下吧 QQ 1300400058。

指导教师我花了200买的图。

2012 年 4 月简易数字频率计的设计—电路仿真分析与PCB板图绘制摘要数字频率计是一种专门对被测信号频率进行测量的电子测量仪器。

被测信号可以是正弦波、方波或其它周期性变化的信号。

数字频率计主要由放大整形电路、闸门电路、计数器电路、锁存器、时基电路、逻辑控制、译码显示电路几部分组成。

随着微电子技术和计算机技术的不断发展,信号完整性分析的应用已经成为解决高速系统设计的唯一有效途径。

借助功能强大的Protel99SE仿真软件,利用IBIS模型,对高速信号线进行布局布线前信号完整性仿真分析是一种简单可行的分析方法,可以发现信号完整性问题,根据仿真结果在信号完整性相关问题上做出优化的设计,从而缩短设计周期。

讨论了基Protel99SE仿真软件模型的建立并对仿真结果进行了分析。

研究结果表明在高速电路设计中采用基于信号完整性的仿真设计是可行的, 也是必要的。

关键词:数计频率设计方案优化设计 PCB目录1 绪论 (1)2数字频率计功能及要求 (2)2.1频率计功能 (2)2.2 元器件数量 (2)2.3整体电路设计图及原理 (3)3 Multisim8电路仿真分析 (5)3.1直流工作点分析 (5)3.2瞬态分析 (5)3.3交流分析 (6)3.4傅里叶分析 (7)4.Protel99SE简介 (8)5 pcb板图绘制 (9)5.1 PCB设计的一般原则 (9)5.1.1 布局 (9)5.1.2 布线 (10)5.2 元器件的自动和手工布局 (11)6.原理图和PCB板图 (13)7 结论 (14)谢辞 (15)参考文献 (16)1 绪论随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。