基于fpga的adc采样控制电路设计

- 格式:docx

- 大小:36.83 KB

- 文档页数:2

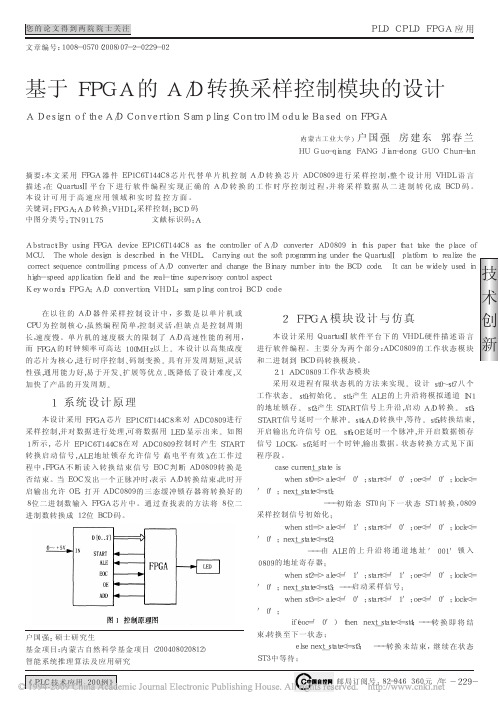

技术创新PLDCPLDFPGA应用您的论文得到两院院士关注基于FPGA的A/D转换采样控制模块的设计ADesignoftheA/DConvertionSamplingControlModuleBasedonFPGA(内蒙古工业大学)户国强房建东郭春兰HUGuo-qiangFANGJian-dongGUOChun-lan摘要:本文采用FPGA器件EP1C6T144C8芯片代替单片机控制A/D转换芯片ADC0809进行采样控制,整个设计用VHDL语言描述,在QuartusⅡ平台下进行软件编程实现正确的A/D转换的工作时序控制过程,并将采样数据从二进制转化成BCD码。

本设计可用于高速应用领域和实时监控方面。

关键词:FPGA;A/D转换;VHDL;采样控制;BCD码中图分类号:TN911.75文献标识码:AAbstract:ByusingFPGAdeviceEP1C6T144C8asthecontrollerofA/DconverterAD0809inthispaperthattaketheplaceofMCU.ThewholedesignisdescribedintheVHDL.CarryingoutthesoftprogrammingundertheQuartusⅡplatformtorealizethecorrectsequencecontrollingprocessofA/DconverterandchangetheBinarynumberintotheBCDcode.Itcanbewidelyusedinhigh-speedapplicationfieldandthereal-timesupervisorycontrolaspect.Keywords:FPGA;A/Dconvertion;VHDL;samplingcontrol;BCDcode文章编号:1008-0570(2008)07-2-0229-02在以往的A/D器件采样控制设计中,多数是以单片机或CPU为控制核心,虽然编程简单,控制灵活,但缺点是控制周期长,速度慢。

基于FPGA多路A/D自动采集采集系统设计摘要:在以往AD采集中,通过微控制器控制A/D芯片复杂的逻辑,不仅增加了微控制器干预,从而影响处理器运行速度,同时由于微控制器不断介入A/D控制会影响程序正常运行。

本文概述了基于FPGA的多路数据自动采集系统的设计和实现过程。

该系统采用高速A/D转换器将多路模拟信号转换成数字信号,以FPGA为控制核心产生各种控制时序,控制A/D和模拟量开关切换,并对转换结果进行数据读取保存在双口RAM中,通过试验验证表明该系统工作稳定,能够实现对多路采集信号实时采集处理,检测效果良好。

关键词:FPGA A/D转换自动采集Design of automatic acquisition and acquisition system based on FPGA multi A/DAbstract: In the past, A/D acquisition through the micro controller to control the complexity of the A/D chip logic. That not only increased the micro controller intervention, so that affecting the operating speed of the processor, but also affected the normal operation of the program when the micro controller continuous intervention the A/D conversion. This paper Summary the design and implementation of high speed multi channel data acquisition system based on FPGA, The system uses high speed A/D converter to convert multiple analog signals into digital signals. The FPGA is used as control core to generate various control timing, which is used to control A/D and analog switch, at the same time, the data that is converted is stored in dual port RAM. Through the experiment, the system is proved to can stably real-time process for multi-channel signal acquired system, and the examination effect is good. Key words: A/D FPGA Automatic Acquisition1 引言在高速多路数据采集系统中,通常采用数字信号处理器DSP或单片机作为微控制器,控制模数转换器AD及其他外围设备的工作。

基于FPGA的高精度AD采样实现摘要:研究了基于FPGA的高精度A/D采样实现,FPGA选用altera公司cycloneII 系列芯片,AD转换器采用AD7606-4,该转换器具有4通道16位精度。

关键词:FPGA 仿真芯片1 系统原理FPGA可以根据用户的需要将多种芯片的功能集中实现,在可靠性要求较高,电路板要求越来越小的趋势下,FPGA的应用越来越广。

在设计完后,设计者可以对芯片的功能进行仿真验证,在线修改,大大减少了设计的复杂性。

AD7606-4是ADI公司推出的新一代16位、4通道同步采样的模拟数字转换器。

它采用5V单电源供电,不再需要正负双电源,并支持真正10V或5V的双极性信号输入。

所有的通道均能以高达200kSPS的速率进行采样。

本文研究了基于FPGA的A/D转换控制,图1是A/D与FPGA 的连接框图。

A/D的转换时间最快是5us。

由FPGA发出转换控制信号AD_CONVST,A/D复位信号AD_RESET,A/D读信号AD_RD,读使能信号AD_CS。

采用并行字节方式将A/D转换的信号通过数据线DA0-DA7读到FPGA中。

AD7606-4先发高字节,再发低字节;先对通道1进行转换,再对通道2,最后对通道3进行转换。

AD_RESET为高电平时A/D复位,AD_CONVST出现上升沿时,A/D开始模拟信号转换,转换时间最快为5us,设计者可以根据应用设计转换时间,在本程序中转换时间设置为10us。

模拟信号转换完的时间是2us,本程序中设计转换开始5us后,FPGA发出AD_RD信号,可以把转换完的数字信号读到FPGA中。

图2是采用并行字节读模式的时序图。

2 VHDL实现及仿真在Quartus II 集成开发环境中,采用VHDL实现FPGA对A/D 的采集,系统时钟选用24Mhz,以下程序实现转换控制信号AD_CONVST和读使能信号AD_CS:if clk_global&acute;event and clk_global=&acute;1&acute; thencount<=count+1;if count=2 then------------------实现转换信号AD_convst<=&acute;0&acute;;elsif count>=3 and count<=239 thenAD_convst<=&acute;1&acute;;end if;if count>=120 and count<=134 then -----实现CS信号CS<=&acute;0&acute;;elseCS<=&acute;1&acute;;end if;if count>=239 then --计数器回零count<=0;end if;end if;仿真结果如图3所示,其中AD_data_in是送给FPGA的AD转换后的数字信号,AD1_data_out,AD2_data_out,AD3_data_out,表示三路通道输出的16位数字信号,在本程序中只使用3路通道。

基于FPGA的ADC采集系统的设计摘要基于FPGA在高速数据采集方面有单片机和DSP无法比拟的优势,FPGA具有时钟频率高,内部延时小,全部控制逻辑由硬件完成,速度快,效率高,组成形式灵活等特点。

因此,本文研究并开发了一个基于FPGA的数据采集系统。

FPGA的IO口可以自由定义,没有固定总线限制更加灵活变通。

本文中所提出的数据采集系统设计方案,就是利用FPGA作为整个数据采集系统的核心来对系统时序和各逻辑模块进行控制。

依靠FPGA强大的功能基础,以FPGA作为桥梁合理的连接了ADC、显示器件以及其他外围电路,最终实现了课题的要求,达到了数据采集的目的。

关键词FPGA A/D转换AbstractFPGA is better than microcontroller and DSP in high speed data acquisition, FPGA has higher internal clock frequency, smaller delay than DSP,and all the control logic of FPGA is completed by hardware, FPGA has fast speed, high efficiency, and so on. Therefore, this paper introduces and develops a data acquisition system which is based on FPGA.The I/O pin of FPGA can be defined yourself without fixed limit,it’s very flexible. This design of data acquisition system use FPGA as the data acquisition system core to control the timing and the logic control module. Relying on the powerful function of FPGA, FPGA can connect ADC, display devices and other peripheral circuits, finally we can achieve the requirements of the subject, and the purpose of the data collection。

FPGA课程设计题目:基于FPGA的多通道采样系统设计院(系):电气工程及其自动化学院专业:电子信息工程12-01摘要本论文介绍了基于FPGA的多通道采样系统的设计。

用FPGA设计一个多通道采样控制器,利用VHDL语言设计有限状态机来实现对AD7892的控制。

由于FPGA器件的特性是可以实现高速工作,为此模拟信号选用音频信号。

由于音频信号的频率是20Hz-20KHz,这样就对AD转换的速率有很高的要求.因为FPGA的功能很强大,所以我们把系统的许多功能都集成到FPGA器件中,例如AD通道选择部分,串并输出控制模块,这样使得整个系统的外围电路简单、系统的稳定性强。

FPGA的配置模式选用被动串行模式,这样就增强了系统的可扩展性。

输出模式可选择性使得系统的应用相当广泛,串行输出可以用于通信信号的采集,方便调制后发射到远程接受端,远程接收端对采集的数据进行解调;而并行输出模式则可以通过高速存储器将采集的信号放到微机或者其他的处理器上,根据采集的数据进行相应的控制。

此系统的缺点是由于FPGA器件配置是基于SRAM查找表单元,编程的信息是保持在SRAM中,但SRAM在掉电后编程信息立即丢失,所以每次系统上电都需要重新配置芯片,这对在野外作业的工作人员很不方便,解决的方法是专用的配置器件来配置FPGA,在每次系统上电的时候会自动把编程信息配置到FPGA芯片中。

但设计中没有采用到这种配置方案主要是考虑到专用配置器件的价格问题。

本文开始介绍了多通道系统的组成部分,然后分别介绍了各个组成部分的原理和设计方法,其中重点介绍了FPGA软件设计部分。

还对当前十分流行的基于FPGA的设计技术作了简单的阐述,最后对系统的调试和应用作了简短的说明。

关键词:音频放大;滤波器;FPGA;VHDL;AD7892;有限状态机;目录摘要 (2)引言 (3)1题目来源 (3)2研究意义 (3)3多通道采样系统的组成 (3)4方案设计 (4)5 单元电路的设计 (4)5.1音频放大、滤波部分 (4)(1)音频放大部分 (4)(2)有源滤波器的设计 (4)5.2 AD采样电路 (5)5.3 FPGA控制部分 (5)(1)通道选择模块 (6)(2)延时模块的设计 (6)(3)串并输出选择控制 (7)5.4 FPGA的硬件设计 (8)6 软件介绍 (8)7 整机调试 (8)7.1 硬件电路的调试步骤 (8)(1)音频放大部分调试 (8)(2)滤波部分调试 (8)(3)FPGA硬件电路调试 (9)(4)AD采样模块调试 (9)(5) 联机调试 (9)8 结论 (9)参考文献 (10)附录 (11)引言FPGA(Field-Programmable Gate Array 现场可编程门阵列)是近年来广泛应用的超大规模、超高速的可编程逻辑器件,由于其具有高集成度(单片集成的系统门数达上千万门)、高速(200MHz 以上)、在线系统可编程等优点,为数字系统的设计带来了突破性变革,大大推动了数字系统设计的单片化、自动化,提高了单片数字系统的设计周期、设计灵活性和可靠性。

基于FPGA的A/D转换采集控制模块设计黄容兰1,万德焕21. 桂林电子科技大学电子工程学院,广西桂林(541001)2.桂林空军学院,广西桂林(541003)摘要:本文采用FPGA器件EP1C3T144C8N处理器,对A/D转换芯片AD7714进行采样控制。

整个设计在QuartusⅡ平台下进行软件编程,采用Verilog语言描述,实现正确的AD7714转换的工作时序控制过程,并将采样的数据存储起来进行处理。

本设计可用于微弱信号采集和实时监控方面,仿真结果显示该模块工作性能稳定、可靠性高、使用方便。

关键词:FPGA;Verilog;A/D转换;采样控制中图分类号:TN1.引言对于微弱信号的采集和处理,多数是以单片机或CPU为控制核心,虽然编程简单,控制灵活,但缺点是速度慢,控制周期长。

单片机的速度极大地限制了A/D高速性能的利用。

而FPGA的时钟频率可高达100MHz以上【1】。

本设计以高集成度的芯片为核心,进行数据采集控制、数据时序控制、数据存储等。

具有开发周期短、灵活性强、通用能力好、易于开发、扩展等优点【2】。

既降低了设计难度,又加快了产品的开发周期。

2.系统设计本设计采用FPGA芯片EP1C3T144C8N来对AD7714进行采样控制,并对数据进行存储,然后进行处理。

2.1 AD7714芯片介绍AD7714是AD公司生产的16/24位可编程串行模数转换器,能直接从传感器接收低电平信号并输出串行数字。

它具有低噪声(140nV)、低功耗和±0.0015%的精度,片内含可编程低通滤波寄存器和可读写系统校准寄存器等8个可编程的片内寄存器等特点。

AD7714对于微控制器非常理想,主要应用于低频小信号的测量。

FPGA对AD7714的控制,主要通过对它的片内8个寄存器进行设置,如表1所示。

表1 AD7714内部功能结构表寄存器寄存器位数通信寄存器8位模式寄存器8位高位滤波寄存器8位低位滤波寄存器8位测试寄存器8位数据寄存器 16位或者24位0刻度校准寄存器 24位全刻度校准寄存器 24位而对每个寄存器的设置都要通过对通信寄存器的写操作开始。

基于FPGA的高速ADC同步采集电路的设计与实现秦艳召*明蕾**庄东曙***摘要在无线通信领域,实时分析及处理的信号带宽越来越大,要求射频前端ADC 的采样率也越来越高,对采样系统的SNR、SFDR以及同步性有着较高的要求。

本文描述了一种基于FPGA的两路高速ADC同步电路,该电路保证了两路宽带信号高速采集,提高了宽带通信的分析处理带宽,同时保证了采集电路的同步性及SNR和SFDR性能。

本设计在无线通信、信号采集、信号处理领域,有着较强的实用性,可广泛用于宽带无线通信、数字仪表、电子对抗等领域。

关键词:无线通信同步采集高速ADCDesign and Implementation of a High-speed ADC Synchronous Acquisition Circuit Based on FPGAQin Yanzhao Ming Lei Zhuang DongshuAbstractIn the field of wireless communication,the signal bandwidth of real-time analysis and pro-cessing is getting larger,which requires high sampling rate of RF front-end,high demand of SNR,SFDR and the synchronization of the sampling system.This paper describes a two -way high-speed ADC synchronous acquisition circuit based on FPGA,which improves the analysis and processing bandwidth of broadband communication,and guarantees the high-speed acquisition of the two-way broadband signal,the synchronization of acquisition circuit,as well as the performance of SNR and SFDR.The design has strong practicability in wireless communication,signal acquisition and processing.It can be widely used in the fields of broadband wireless communication,digital instruments and e-lectronic countermeasures.Key words:Wireless communication Synchronous acquisition High-speed ADC*作者系南京熊猫汉达科技有限公司工程师**作者系南京熊猫汉达科技有限公司工程师***作者系南京熊猫通信科技有限公司高级工程师12019年第3期通信与广播电视一、引言在无线通信中,实时分析及处理的信号带宽越来越大,要求ADC 的采样率也越来越高,同时对采样系统的SNR 、SFDR 以及同步性有着较高的要求,而传统的采集系统不能满足当前需求。

以FPGA 为核心控制A/D 转换器来完成的数据采集系统设计详解弹丸飞行速度的测量是武器系统各种运动参数中一项至关重要的内容,它是衡量火炮特性,弹药特性和弹道特性的一个重要指标。

在众多的弹丸速度测量系统中.激光光幕区截测速靶以其精度高而独具优势。

但采用现成的数据采集卡进行数据采集。

不仅成本高,而且易受机箱等环境的限制。

介绍了一种以咏为核心的数据采集系统.当子弹穿过光幕靶时,光电探测器获得弹丸过靶信号.FPGA 控制A /D 转换器进行信号采集并存储。

以供后续分析和处理。

1激光测速靶原理简介激光测速靶就是一种利用光测法测量弹丸速度的测试装置。

它由初速靶和存速靶组成,初速靶和存速靶又分别由启动靶和停止靶组成。

激光测速靶的光源为半导体激光器,激光束经准直、柱面反射镜的扩柬形成人射光幕.弹丸依次过靶时.先后遮挡部分入射光线。

经原向反射屏反射后由光电探测器获取弹丸过靶时的交变信号。

信号调理后,由数据采集电路进行采集.最后传输到上位机做数据处理和运算得出子弹的飞行速度。

≡≡自动脉冲信K p T=11"1—"ffiι谶光测速品卜'./咨示盘视2数据采集方案为记录子弹在启动靶和停止靶的过靶信号,以启动靶信号为触发源,负延时触发FPGA 控制2个A/D 转换器同步进行数据采集,将采集到的数据分别存储至IJS 幽中,然后通过USB 依次将SRAM 中的数据传输到上位机进行信号的分析和处理。

单通道数据采集方案如图2所示。

子弹 停止Ie一中…光电:短][)电转慢I 光电转帙放大电路放大电路I 放大电路放大电路3器件选型及依据3.1FPGA的选择FPGA是英文Fie1dProgrammab1eGateArray的缩写,即现场可编程门阵列,它是在PA1、GA1>迺等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA直接控制ADC0809对模拟信号进行采样设计方案第二章总体方案设计2.1 系统方案设计在以往的A/D器件采样控制设计中,多数是以单片机或CPU为控制核心,虽然编程简单,控制灵活,但缺点是控制周期长,速度慢。

单片机的速度极大的限制了A/D高速性能的利用,而FPGA的时钟频率可高达100MHz以上。

本设计以高集成度的芯片为核心,进行时序控制、码制变换。

具有开发周期短,灵活性强,通用能力好,易于开发、扩展等优点。

既降低了设计难度,又加快了产品的开发周期。

基于FPGA的信号采集系统主要有:A/D转换器,FPGA,RS232通信,PC机组成。

A/D 转换器对信号进行会采集,A/D 部集成了采样、保持电路,可有效的降低误差,减少外围电路的设计,降低系统的功耗。

A/D在接受到指令后进行采集,FPGA采集控制模块首先将采集到的通过A/D 转换城的数字信号引入FPGA,而后对数字信号送往算法实现单元进行处理,并存于FPGA部RAM中,再将数据由RS232传送到PC上做FFT,实现对采集信号的时域和频域的显示。

图2.1.1系统的总体框图:FPGA的设计结构如图2.1.2所示。

数字倍频器的倍频输出提供ADC控制器的采样触发脉冲。

根据ADC0809操作时序,ADC控制器来实现ADC0809的数据采集操作,采样的时机由倍频器来控制。

控制器每控制完成一次采样操作,则停止等待下一个触发脉冲的到来。

倍频器每输出一个低电平脉冲,ADC采样控制器的状态机进行一次采样操作。

在倍频器的触发控制下,完成被测信号一个基波周期N个点的等间隔采样,同时数字倍频器跟踪输入信号的频率的变化,尽可能地保持N个点的采样宽度正好为被测信号一个周波的宽度。

-时钟分配及各模块的控制:在协调模块工作时,起到很重要的作用。

引进晶振产的时钟信号,根据实际需要对起进行倍频或分频,使A/D的采样频率,RAM的读写频率,信号处理实现的核心模块的工作频率一致。

图2.1.2系统具体流程框图2.2 各功能模块的设计方案2.2.1 FPGA最小系统板方案设计FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物[4]。

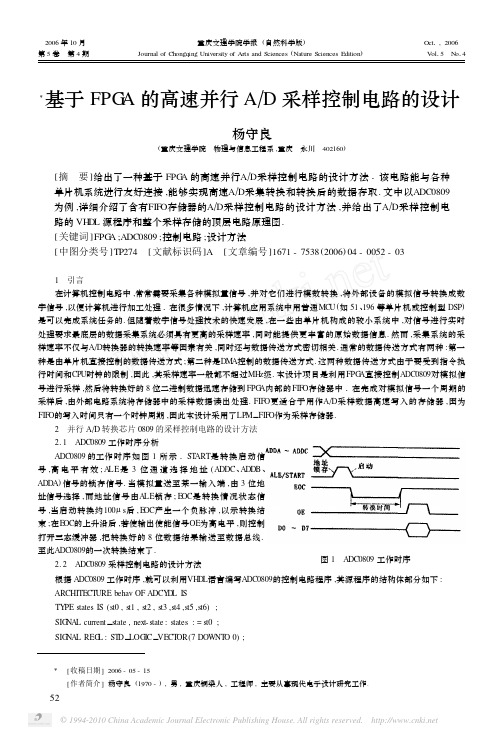

2006年10月重庆文理学院学报(自然科学版)Oct 1,2006 第5卷 第4期Journal of Chongqing University of Arts and Sciences (Nature Sciences Edition )V ol 15 N o 14Ξ基于FPG A 的高速并行A ΠD 采样控制电路的设计杨守良(重庆文理学院 物理与信息工程系,重庆 永川 402160)[摘 要]给出了一种基于FPG A 的高速并行A ΠD 采样控制电路的设计方法1该电路能与各种单片机系统进行友好连接,能够实现高速A ΠD 采集转换和转换后的数据存取.文中以ADC0809为例,详细介绍了含有FIFO 存储器的A ΠD 采样控制电路的设计方法,并给出了A ΠD 采样控制电路的VH D L 源程序和整个采样存储的顶层电路原理图.[关键词]FPG A ;ADC0809;控制电路;设计方法[中图分类号]TP274 [文献标识码]A [文章编号]1671-7538(2006)04-0052-031 引言在计算机控制电路中,常常需要采集各种模拟量信号,并对它们进行模数转换,将外部设备的模拟信号转换成数字信号,以便计算机进行加工处理1在很多情况下,计算机应用系统中用普通MC U (如51、196等单片机或控制型DSP )是可以完成系统任务的.但随着数字信号处理技术的快速发展,在一些由单片机构成的较小系统中,对信号进行实时处理要求最底层的数据采集系统必须具有更高的采样速率,同时能提供更丰富的原始数据信息.然而,采集系统的采样速率不仅与A ΠD 转换器的转换速率等因素有关,同时还与数据传送方式密切相关.通常的数据传送方式有两种:第一种是由单片机直接控制的数据传送方式;第二种是DM A 控制的数据传送方式.这两种数据传送方式由于要受到指令执行时间和CPU 时钟的限制,因此,其采样速率一般都不超过MH z 级.本设计项目是利用FPG A 直接控制ADC0809对模拟信号进行采样,然后将转换好的8位二进制数据迅速存储到FPG A 内部的FIFO 存储器中1在完成对模拟信号一个周期的采样后,由外部电路系统将存储器中的采样数据读出处理.FIFO 更适合于用作A ΠD 采样数据高速写入的存储器,因为FIFO 的写入时间只有一个时钟周期,因此本设计采用了LP M —FIFO 作为采样存储器.2 并行A ΠD 转换芯片0809的采样控制电路的设计方法图1 ADC0809工作时序2.1 ADC0809工作时序分析ADC0809的工作时序如图1所示1ST ART 是转换启动信号,高电平有效;A LE 是3位通道选择地址(ADDC 、ADDB 、ADDA )信号的锁存信号.当模拟量送至某一输入端,由3位地址信号选择,而地址信号由A LE 锁存;E OC 是转换情况状态信号,当启动转换约100μs 后,E OC 产生一个负脉冲,以示转换结束;在E OC 的上升沿后,若使输出使能信号OE 为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输送至数据总线.至此ADC0809的一次转换结束了.2.2 ADC0809采样控制电路的设计方法根据ADC0809工作时序,就可以利用VH D L 语言编写ADC0809的控制电路程序,其源程序的结构体部分如下:ARCHITECT URE behav OF ADCY D L ISTY PE states IS (st0,st1,st2,st3,st4,st5,st6);SIG NA L current —state ,next-state :states :=st0;SIG NA L REG L :ST D —LOGIC —VECT OR (7DOW NT O 0);25Ξ[收稿日期]2006-05-15[作者简介]杨守良(1970-),男,重庆铜梁人,工程师,主要从事现代电子设计研究工作.SIG NA L LOCK:ST D—LOGIC;BEGI NADDA<=‘1’;LOCK1<=LOCK;PRO:PROCESS(current—state,E OC)BEGI NC ASE current—state ISWHE N st0=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;next—state<=st1;WHE N st1=>A LE<=‘1’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;next—state<=st2;WHE N st2=>A LE<=‘0’;ST ART<=‘1’;OE<=‘0’;LOCK<=‘0’;next—state<=st3;WHE N st3=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;IF(E OC=‘1’)THE N next—state<=st3;E LSE next—state<=st4;E ND IF;WHE N st4=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;IF(E OC=‘0’)THE N next-state<=st4;E LSE next—state<=st5;E ND IF;WHE N st5=>A LE<=‘0’;ST ART<=‘0’;OE<=‘1’;LOCK<=‘0’;next—state<=st6;WHE N st6=>A LE<=‘0’;ST ART<=‘0’;OE<=‘1’;LOCK<=‘1’;next—state<=st0;WHE N OTHERS=>A LE<=‘0’;ST ART<=‘0’;OE<=‘0’;LOCK<=‘0’;next—state<=st0;E ND C ASE;E ND PROCESS PRO;PROCESS(C LK)BEGI NIF(C LK’E VE NT AND C LK=‘1’)THE Ncurrent—state<=next—state;E ND IF;E ND PROCESS;PROCESS(LOCK)BEGI NIF LOCK=‘1’AND LOCK’E VE NT THE N REG L<=D;E ND IF;E ND PROCESS;Q<=REG L;E ND behav;2.3 对设计电路进行仿真测试利用QuartusII对其进行文本编辑输入、编译和仿真测试,得到ADC0809芯片控制电路的仿真波形,其仿真波形如图2所示1由此可见,设计已满足ADC0809各控制信号的要求.最后进行引脚锁定并下载到FPG A目标器件中进行测试,以验证设计的电路对ADC0809的控制功能.图2 ADC0809仿真波形图3 采样存储电路的设计方法采样存储电路采用lpm—FIFO参数化宏功能块,它有一个输入和一个输出共用端口,其输入端口连接ADC0809采样输出端.它的输出端连接在CPU的数据总线上,用于CPU需要读取数据时使用.其设计的顶层电路图如图3所示.AD—35FIFO的工作分两个阶段,即采样阶段和数据读取阶段.在前一阶段,输入控制信号WR—E N为高电平,C LK使能,读请求rdreq禁止.在某一采样周期中,当转换结束后,ADC0809的8位数据出现在数据总线D[7..0]上时,由ADCI NT发出的LOCK信号的上升沿将总线上的数据锁存进FIFO2中.在完成一个或数个输入模拟信号周期采样后进入数据读取阶段.在数据读取阶段中,WR—E N被置为低电平,FIFO2的读写时钟C LOCK通过M UX由RD—E N控制,在它的每一个上升沿, FIFO2中的数据将一一出现在端口Q[7..0]上.图3 ADC采样控制存储电路顶层电路图4 结语在整个系统设计过程中,数据采集与数据传送独立于CPU,选用FPG A作为采样控制电路和采样后的数据存储电路.因此,这种方式摆脱了CPU时钟的限制,这样数据采集、数据传送可以同时进行,从而大大提高了采集与传送的速度.[参考文献][1]S tefan S joholm,Lennart Lindh.边计年,薛宏熙,译.VH D L设计电子线路[M].北京:清华大学出版社,2000.[2]潘松,黄继业,王国栋.现代DSP技术[M].西安:西安电子科技大学出版社,2003.[3]潘松,黄继业.E DA技术实用教程[M].北京:科学出版社,2002.[4]徐志军,徐光辉.CP LDΠFPG A的开发与应用[M].北京:电子工业出版社,2002.[5]包明,赵明富,陈渝光.E DA技术与数字系统设计[M].北京:北京航空航天大学出版社,2002.[6]褚振勇,翁木云.FPG A设计及应用[M].西安:西安电子科技大学出版社,2002.[7]林明权.VH D L数字控制系统设计范例(第1版)[M].北京:电子工业出版社,2003.[8]侯伯亨,顾新.VH D L硬件描述语言与数字逻辑电路设计(第1版)[M].西安:西安电子科技大学出版社,1999.The Design of the AΠD Sampling Control Circuit B asing on the H igh Speed Simultaneous FPGAY ANG Shou-liang(Dept.of Physics and Information Engineering,Chongqing University of Arts and Science s,Y ongchuan Chongqing402160,China) Abstract:The author introduces a kind of designing method of the AΠD Sam pling C ontrol Circuit basing on the high speed simultaneous FPG A.The circuit can be joined well with all kinds of single-chip com puter systems, which can gather and trans form the data of AΠD at a speed and perform the data access after the conversion as well.T aking ADC0809as an exam ple in the article,the author explained the designing method of the AΠD Sam pling C ontrol circuit which includes FIFO mem orizer particularly.And the author als o presents the VH D L s ource program of the AΠD Sam pling C ontrol Circuit and the top level circuit schematic drawing of the entire sam pling mem orizer.K ey w ords:FPG A;ADC0809;controling circuit;Designing method45。

电子技术• Electronic Technology92 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】现场可编程门阵列 多通道采样系统 系统硬件电路 时序程序高性能模数转换器主要应用于通信、仪器仪表及医疗设备等多个领域。

他对我国国防建设及科研工作的开展有着积极的促进意义。

现场可编程门阵列具有着运行速度快、抗干扰能力强等优势,与之相关的FPGA 系统可以让采集系统更好地满足人们的需求。

FPGA 和AD 设备采样系统之间的有效连接,可以让人们对系统的AD 转换模块的性能进行分析与验证。

1 基于FPGA的高速多通道AD采样系统的总体设计霍尔传感器、滤波电路、AD 采样芯片和FPGA 是基于FPGA 的多通道数据采样系统主要组成部分。

以现场可编程门阵列为核心的数据采集系统可以根据上位机的指令配置和实际需求,对实时采样方式和高速采样方式进行转换,与之相关的硬件电路具有数据采集、自动电桥平衡和状态反馈功能等多种功能。

在AD 采样系统的设计环节,系统硬件电路的搭建方式建立在其整体结构基础之上。

在需要被检测的电流电压进入滤波电路以后,滤波电路会将电流电压转换为模拟量信号,AD 芯片会将经由电路处理的模拟量信号传入FPGA 之中。

2 基于FPGA的高速多通道AD采样系统的实现2.1 AD采样系统的硬件电路设计AD7606是基于FPGA 的高速多通道AD 采样系统中所常用的一种高速模数转换芯片。

这一设备具有着分辨率高、双极性输入效果好和具有多通道同步采样能力的特点。

芯片内部的数字滤波器所具有的过采样功能可以为信号的并行输出及串行输出提供保障。

在AD 采样基于FPGA 的高速多通道AD 采样系统的设计与实现文/刘雨聪系统的硬件电路设计方面,状态机编程方式是实现AD7606的时序控制的有效方式。

根据一些学者的研究结果,系统的工作电压可以被设定为3.3V ,内核电压可以控制为1.2V 。

fpga控制adc采样原理随着电子科技的不断发展,现在的仪器和设备越来越复杂,所需要的精度和速度也越来越高,为了满足人们对于高精度和高速度的需求,FPGA控制ADC采样便应运而生。

本文将从FPGA、ADC、采样原理三个方面来详细解析FPGA控制ADC采样原理。

一、什么是FPGA控制ADC采样?FPGA(Field-Programmable Gate Array)是可编程门阵列,是一种灵活性最强的集成电路芯片,其功能是可由用户进行调整和设计,从而实现所需功能。

而ADC (Analog-to-Digital Converter)是一种模拟信号转数字信号的装置,将模拟信号转换为数字信号,以便于数字电子设备的处理和存储。

FPGA控制ADC采样,就是将ADC采集到的数据传输给FPGA进行处理,从而实现各种功能。

二、关于FPGAFPGA作为一种可编程门阵列芯片,其结构包括可编程逻辑单元(LUT)、存储单元、I/O(输入输出)单元、时钟链和ALU(算术逻辑单元)等部分。

其中,LUT是FPGA 主要的几何单元之一,它通过组合逻辑电路实现复杂的数字信号处理和运算、状态控制等功能,LUT中的每一个存储单元可以存储逻辑电路中的一个常量。

三、关于ADCADC是模拟信号转数字信号的一种设备,其主要功能是将模拟信号转换为数字信号,以便数字电子设备进行处理。

在ADC中,模拟信号被采集,并被离散化为一系列数字样品,再由采集软件对其进行处理,从而得到所需的数据。

ADC还可以将模拟信号进行滤波、增益调整等处理。

四、采样原理ADC的采样原理是将模拟信号离散化为一系列数字信号,而采样率则是指每秒采样的次数,采样率越高,所得数字信号的精度就越高。

在FPGA控制ADC采样中,由于FPGA的可编程性,它可以通过编写程序从ADC中获取采样数据,并进行处理,从而实现各种功能。

特别的,FPGA还可以通过内置的簇片和DSP单元等部分来实现高精度运算以及并行化数据处理,从而提高处理速度和效率。

fpga adc电压采集参考电路下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!FPGA ADC 电压采集参考电路在设计数字信号处理系统时,常常需要使用模数转换器(ADC)来将模拟信号转换为数字信号。

基于fpga的adc采样控制电路设计

FPGA(现场可编程门阵列)是一种高度可编程的数字电路设

计工具,可用于实现各种应用。

ADC(模拟数字转换器)是

一种电子设备,用于将模拟信号转换为数字信号。

在本文中,我们将设计一个基于FPGA的ADC采样控制电路。

首先,我们需要选择一个合适的ADC芯片,以满足我们的需求。

ADC芯片通常具有不同的分辨率(以位为单位)和采样

速率(以样本/秒为单位)。

选择适当的芯片将取决于被测信

号的频率范围和精度要求。

一旦我们选择了ADC芯片,我们

可以开始设计采样控制电路。

ADC采样控制电路的主要任务是控制ADC芯片的采样频率和

采样精度。

首先,我们需要使用FPGA来生成一个时序信号,用于控制ADC芯片的采样。

此时序信号应具有适当的频率,

以保证ADC芯片的采样和转换过程正常运行。

然后,我们需要将ADC芯片的采样结果传递给FPGA。

为此,我们可以使用串行通信接口(如SPI或I2C),在ADC芯片

和FPGA之间建立一个数据通道。

通过该通道,ADC芯片的

采样结果将传输到FPGA中进行后续处理。

一旦ADC芯片的采样结果进入FPGA,我们可以进行进一步

的数字信号处理。

我们可以使用FPGA内部的逻辑电路和存

储器来实现数字滤波、数字滤波等功能。

这些功能可以根据特定应用的需求进行定制。

最后,我们可以将FPGA处理后的数字信号输出到外部设备(如计算机)或其他电路中。

这些输出信号可以用于进一步分析、控制或存储。

总之,基于FPGA的ADC采样控制电路是一种常见的电路设计方法,可用于实现各种实时信号处理和控制应用。

通过适当选择ADC芯片和设计有效的采样控制电路,我们可以在FPGA上实现高性能、低功耗的ADC系统。

这种设计方法具有灵活性和可扩展性,适用于各种应用领域,如通信、医疗、工业控制等。