自上而下原理图设计

- 格式:doc

- 大小:309.50 KB

- 文档页数:2

多通道设计介绍在电路设计中,对于规模较大的原理图,虽然可以利用Altium Designer绘制在一张图纸中,但是会产生图面过大,层次性不分明的问题使图面可读性变差,查看不便。

Altium Desinger为此提供了多通道设计的解决方案。

设计者可以按功能将电路分别绘制在不同的图面中。

复杂的电路就会变成相对较简单的几个模块,便于检查和修改,复用性也得到提升。

Altium Designer提供了“自上而下”和“自下而上”的两种层次化原理图设计的方法。

下面我们简单介绍这两种层次原理图设计的方法。

自上而下的设计方法所谓“自上而下”的设计方法是指用户根据系统结构,将系统划分成不同功能的子模块,再根据划分,将系统的层次原理母图画出,最终完成整个系统原理图的设计。

常用命令在这种设计方法中常用的命令如下,下列命令可以从Design菜单下进入:Create Sheet from Symbol:使用这个命令,可将方块电路生成原理图,方块电路图中的端口会在生成原理图的过程中自动加载到原理图中。

Create VHDL file from Symbol:使用这个命令可以产生一个VHDL文件,这个VHDL 文件的实体声明部分包含与指定的方块电路中相匹配的端口的定义。

Create Verilog file from Symbol:使用这个命令可以产生一个Verilog文件,这个Verilog 文件的模块声明部分包括与指定的方块电路中相匹配的端口的定义。

Push Part to Sheet:使用这个命令可以将一个已经放置好的元件“推”到一个新原理图的子图中,代替原理图母图中的已有元件。

而原理图母图是以方块电路的形式存在,每一个方块电路对应一个子图。

相匹配的端口自动加到子图中。

右键单击元件可以进入这个命令。

操作方法下面以Create Sheet from Symbol的方式来介绍自上而下设计方法的具体操作放法。

1、利用方块电路绘制电路层次母图。

![Altium Designer 14原理图与PCB设计第4章 层次化原理图绘制[精]](https://uimg.taocdn.com/7b5c4c30a6c30c2259019e74.webp)

Concept HDL原理图设计(二)层次原理图的设计在本章前面章节中,主要讲述了原理图的绘制方法,这一节主要讲述层次原理图的设计方法。

由前面所讲内容可以看出,层次原理图的设计使得原理图的设计更加清晰明了,各模块功能一目了然。

下面将详细讲述层次原理图的设计方法。

一、层次化设计的特点层次化设计技术使用符号代表功能,大大地减少了冗余的信息,并且功能模块能够重复调用,加强了团队合作性。

Design Entry HDL支持两种层次化的设计方法:自上而下的设计(TOP-DOWN)和自下而上的设计方法(DOWN-TOP)。

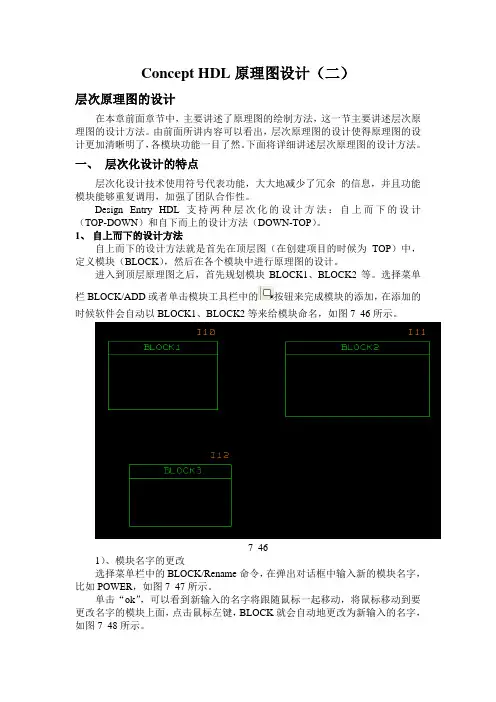

1、自上而下的设计方法自上而下的设计方法就是首先在顶层图(在创建项目的时候为TOP)中,定义模块(BLOCK),然后在各个模块中进行原理图的设计。

进入到顶层原理图之后,首先规划模块BLOCK1、BLOCK2等。

选择菜单栏BLOCK/ADD或者单击模块工具栏中的按钮来完成模块的添加,在添加的时候软件会自动以BLOCK1、BLOCK2等来给模块命名,如图7_46所示。

7_461)、模块名字的更改选择菜单栏中的BLOCK/Rename命令,在弹出对话框中输入新的模块名字,比如POWER,如图7_47所示。

单击“ok”,可以看到新输入的名字将跟随鼠标一起移动,将鼠标移动到要更改名字的模块上面,点击鼠标左键,BLOCK就会自动地更改为新输入的名字,如图7_48所示。

7_477_482)、模块的移动模块的移动和元件的移动是一样的,此处不再赘述。

3)、模块大小的调整选择菜单栏中的BLOCK/Stretch命令或者选择模块工具栏中的按钮,然后左键单击模块的边沿,松开鼠标左键后,拖动鼠标即可改变模块的大小,达到合适尺寸后再次单击鼠标左键即可完成调整。

4)模块管脚的添加选择菜单栏中的BLOCK/Add Pin/Input Pin(或者Output Pin、Inout Pin)命令,也可以直接选择模块工具栏中的按钮,弹出如图7_49所示对话框,在弹出的对话框中依次添加信号名(输完网络名后,回车输入下一个网络名),如图7_50所示。

第一步绘制总图

(1)建立一个空项目文件,并命名为“层次原理图.prjpcb”,保存在桌面上的新建文件夹内。

(2)File----new----schematic,命名为“总图.schdoc”,保存在桌面上的新建文件夹内。

(3)Wiring----place sheet symbol,点击tab键,弹出属性对话框,designator----总图,filename----first.schdoc,画出第一个框图。

(4)根据(3)画出第二个框图second.schdoc

(5)Place sheet entry----tab,name----in1,i/o type----input,放在第一个框图内部靠左侧的地方。

(6)根据(5),分别在第一框图内部右侧、第二框图内部左侧、第二框图内部右侧分别放置out1、in2、out2。

(7)Place port----tab,name----in,i/o type----input,放在第一框图的左侧;在第二框图的右侧放置out,然后将他们用导线连接。

绘制子图

(1)design----creat sheet from symble,点击第一个框图,点no,生成first.schdoc文件,画出它的原理图,保存。

(2)根据(1)画出second.schdoc的原理图并保存。

电子技术的日新月异,不断地改变着人们的生活方式。

而世界电子技术及设计方法的发展,正在给中国的电子设计工程师们以新的挑战和压力。

不能否认,目前中国电子设计技术仍远远落后于发达国家水平,尤其是在电子技术的基础产业,即IC/ASIC方面。

当国人以国产计算机,电视,VCD,影碟机等产业欣欣向荣,飞速发展而沾沾自喜的时候,却不能不看到,几乎所有的核心技术和几乎所有的内部关键集成电路,仍然印着国外半导体厂家的商标。

单从时间上看,国内技术可能只落后一、二十年,但是我们更应该看到:一方面,这一产业的发展是以非线性速度向前推进的,另一方面,当发达国家“全民皆兵”,整体发展水平平均较高时,国内仍局限在为数不多的几个国家重点投资企业或合资/独资企业里。

然而,我们有幸的看到,FPGA/EPLD的发展正逐步取代越来越多的ASIC市场。

可重复使用,小批量,低投入,高性能,高密度,开发周期短等诸多优点,使国内更多的工程师们乐于采用。

由于不需要任何投片费用,也不需要建立任何生产线,因此,采用FPGA/EPLD所需的投资远远低于ASIC的投资。

据估计,引进一套先进的FPGA Top-Down设计工具所需费用还不到ASIC所需的十分之一,而大力推广先进的FPGA设计方法,既可以降低诸多产业投资成本,也可培养一大批国内的Top-Down的设计人才,从而提高国内Top-Down设计的整体水平,为将来国内ASIC产业的快速、健康发展打下坚实的基础。

FPGA/EPLD的自上而下(Top-Down)设计方法:传统的设计手段是采用原理图输入的方式进行的,如图1所示。

通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特定FPGA/EPLD厂商布局布线器所需网表,通过布局布线,完成设计。

原理图绘制完成后可采用门级仿真器进行功能验证。

图1:传统的设计手段与Top-Down设计工具的比较然而,工程师的最初设计思想不是一开始就考虑采用某一FPGA/EPLD厂商的某一特定型号器件,而是从功能描述开始的。

第一步绘制总图

(1)建立一个空项目文件,并命名为“层次原理图.prjpcb”,保存在桌面上的新建文件夹内。

(2)File----new----schematic,命名为“总图.schdoc”,保存在桌面上的新建文件夹内。

(3)Wiring----place sheet symbol,点击tab键,弹出属性对话框,designator----总图,filename----first.schdoc,画出第一个框图。

(4)根据(3)画出第二个框图second.schdoc

(5)Place sheet entry----tab,name----in1,i/o type----input,放在第一个框图内部靠左侧的地方。

(6)根据(5),分别在第一框图内部右侧、第二框图内部左侧、第二框图内部右侧分别放置out1、in2、out2。

(7)Place port----tab,name----in,i/o type----input,放在第一框图的左侧;在第二框图的右侧放置out,然后将他们用导线连接。

绘制子图

(1)design----creat sheet from symble,点击第一个框图,点no,生成first.schdoc文件,画出它的原理图,保存。

(2)根据(1)画出second.schdoc的原理图并保存。