LVDS编码

- 格式:docx

- 大小:628.92 KB

- 文档页数:4

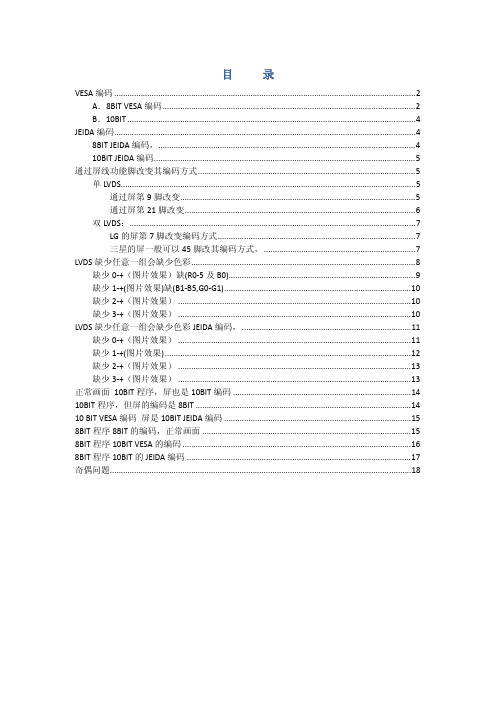

目 录VESA编码 (2)A.8BIT VESA编码 (2)B.10BIT (4)JEIDA编码 (4)8BIT JEIDA编码, (4)10BIT JEIDA编码 (5)通过屏线功能脚改变其编码方式 (5)单LVDS (5)通过屏第9脚改变 (5)通过屏第21脚改变 (6)双LVDS: (7)LG的屏第7脚改变编码方式 (7)三星的屏一般可以45脚改其编码方式, (7)LVDS缺少任意一组会缺少色彩 (8)缺少0‐+(图片效果)缺(R0‐5及B0) (9)缺少1‐+(图片效果)缺(B1‐B5,G0‐G1) (10)缺少2‐+(图片效果) (10)缺少3‐+(图片效果) (10)LVDS缺少任意一组会缺少色彩JEIDA编码, (11)缺少0‐+(图片效果) (11)缺少1‐+(图片效果) (12)缺少2‐+(图片效果) (13)缺少3‐+(图片效果) (13)正常画面 10BIT程序,屏也是10BIT编码 (14)10BIT程序,但屏的编码是8BIT (14)10 BIT VESA编码 屏是10BIT JEIDA编码 (15)8BIT程序8BIT的编码,正常画面 (15)8BIT程序10BIT VESA的编码 (16)8BIT程序10BIT的JEIDA编码 (17)奇偶问题 (18)LVDS编码方式VESA编码A.8BIT VESA编码定义一般式为0‐+,1‐+,2‐+,CLK‐+,3‐+共5组其中数据为4组时钟1组编码图示:一般奇美AU,编码标识图A一般三星屏LVDS VESA编码标识图图片效果:B.10BITJEIDA编码8BIT JEIDA编码,10BIT JEIDA编码LVDS缺少任意一组都出问题(体现色颜色不正常),而且程序输出编码与屏的编码方式要相对应,可以通规格书查看,并可以屏的功能脚改变其编码方式通过屏线功能脚改变其编码方式单LVDS通过屏第9脚改变A.(OPEN或3。

3为VESA,GND为JEIDA)其定义如下:通过屏第21脚改变B.双LVDS:LG的屏第7脚改变编码方式一般可以27脚改变10BIT与8BIT,三星的屏一般可以45脚改其编码方式,不能改其10BIT与8BIT选择LVDS缺少任意一组会缺少色彩VESA编码,程序是VESA屏VESA缺少0+(图片效果)缺(R05及B0)缺少1+(图片效果)缺(B1B5,G0G1)缺少2+(图片效果)a.缺(G2‐G5,DE HS VS)由于没有DE HS VS信号所以屏没法显示缺少3+(图片效果)b.缺(R6‐7,G6‐7,B6‐7)LVDS缺少任意一组会缺少色彩JEIDA编码, 程序JEIDA屏JEIDA缺少0+(图片效果)c.缺(R2‐R7,G2)缺少1+(图片效果)d.(G3‐G7,B2‐B3)缺少2+(图片效果)e.(B4‐B7,DE,HS,VS)由屏没有DE HS VS没法显示缺少3+(图片效果)f.(R0‐R1,G0‐G1,B0‐B1)正常画面 10BIT程序,屏也是10BIT编码10BIT程序,但屏的编码是8BIT10 BIT VESA编码 屏是10BIT JEIDA编码8BIT程序8BIT的编码,正常画面小结对于编码方式,24寸以下的屏LVDS编码方式是固定的,一般是VESA 编码,三星屏的为JIEDA编码,26寸以上的屏LVDS编码方式可以通过某个功能脚改变其编码方式,A单LVDS 9脚21脚视屏的定义来定,如上所说,B双LVDS通过7脚45脚,视屏的定义来定,如上所说,120HZ屏的编码与双LVDS编码相同,控制脚在51PIN的第7脚或45脚视定义来定LG 10BIT屏为了兼容8BIT模式,通过27脚可以选择,奇偶问题另外对屏的奇偶问题,一般看屏规格书,对我们屏线来讲主板端靠近电源近的为第一组(奇),另一组为第二组(偶),单LVDS只接第一组,有时视客户而定大尺寸屏线LG与奇美FHD屏大尺寸奇偶互反请看一下图,但小尺寸屏相同LG定义奇美定义(ODD奇,EVEN偶)奇偶反请看现象:120HZ屏LG与三星的屏的定义不同,接线也不相同,但是一般来讲接线请看下表,非一般情况要求特别注明ST6M20/ST6M30 屏接口PIN数对接1 36PIN 41PIN对接2 40PIN 51PINLG定义41PIN(第三、四像素)和51PIN(第一、二像素)三星定义51PIN(第一、三像素)和 41PIN(第二、四像素)120HZ两组线反了。

DS90C387B(双像素LVDS接口编码器)一、简介DS90C387B支持在主机和显示格式为QXGA的平板显示器之间数据的双线传输,它将48位CMOS/TTL信号和3位控制信号转换成8位LVDS(低压差分信号)数据流,在双像素最大频率112MHz的情况下,若总数据量为5.7Gbit/s,LVDS 数据线速度可达784Mbit/s。

LDI芯片集是FPD-Link驱动的改良一代产品,它可以支持更高的带宽和更长时间的双线驱动。

为了增加带宽,将最大的像素时钟频率增加112MHz,并提供了8个LVDS输出端口。

双线驱动通过可供用户选择的预加强特征信号,在跃变阶段以提供附加电流输出的方式抵消线负载效应。

DS90C387A提供了第二个LVDS输出时钟,两个LVDS时钟是一样的,这个特点使得它可以兼容FPD-Link。

第二时钟使得它能够与采用24位或18位双像素结构的FPD-Link对接。

二、特点z支持SVGA、QXGA;z时钟频率为32.5~112/170MHz;z可驱动低成本的长线;z具有高达5.7 Gbit/s的带宽;z双像素结构支持与GUI、时间控制器对接,单像素结构仅支持GUI 接口;z可抑制嵌套循环的抖动;z数据与控制输入脚电压阈值:5V;z可编程数据传送及控制门锁选择;z符合ANSI/TIA/EIA-644-1995 LVDS标准。

三、内部框图60四、引脚功能61续表名称类型数量功能2PLLVCC IPLL电路电源电压3PLLGND IPLL电路接地端LVDSVCC I 3LVDS输出电源电压LVDSGND I 4LVDS输出接地端CLK2P/NC O 1LVDS附加正极差分时钟输出CLK2M/NC O 1LVDS附加负极差分时钟输出62。

转载什么是LVDS及LVDS针脚定义[转载]什么是LVDS及LVDS针脚定义2010年06月01日 什么是LVDS? 现在的液晶显示屏普遍采用LVDS接口,那么什么是LVDS呢? LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。

由于其可使系统供电电压低至 2V,因此它还能满足未来应用的需要。

此技术基于 ANSI/TIA/EIA-644 LVDS 接口标准。

LVDS 技术拥有 330mV 的低压差分信号 (250mV MIN and 450mV MAX)和快速过渡时间。

这可以让产品达到自 100 Mbps 至超过 1 Gbps的高数据速率。

此外,这种低压摆幅可以降低功耗消散,同时具备差分传输的优点。

LVDS技术用于简单的线路驱动器和接收器物理层器件以及比较复杂的接口通信芯片组。

通道链路芯片组多路复用和解多路复用慢速 TTL信号线路以提供窄式高速低功耗 LVDS 接口。

这些芯片组可以大幅节省系统的电缆和连接器成本,并且可以减少连接器所占面积所需的物理空间。

LVDS 解决方案为设计人员解决高速 I/O 接口问题提供了新选择。

LVDS 为当今和未来的高带宽数据传输应用提供毫瓦每千兆位的方案。

更先进的总线 LVDS (BLVDS)是在LVDS 基础上面发展起来的,总线 LVDS (BLVDS) 是基于 LVDS技术的总线接口电路的一个新系列,专门用于实现多点电缆或背板应用。

它不同于标准的LVDS,提供增强的驱动电流,以处理多点应用中所需的双重传输。

BLVDS 具备大约 250mV 的低压差分信号以及快速的过渡时间。

这可以让产品达到自 100 Mbps 至超过 1Gbps 的高数据传输速率。

此外,低电压摆幅可以降低功耗和噪声至最小化。

差分数据传输配置提供有源总线的 +/-1V 共模范围和热插拔器件。

BLVDS 产品有两种类型,可以为所有总线配置提供最优化的接口器件。

LVDS信号原理和设计:LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

LVDS信号介绍:LVDS:Low V oltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

LVDS信号传输组成:LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE规定,电阻为100欧。

我们通常选择为100,120欧。

LVDS信号电平特性:LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS 接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

由于LVDS信号物理电平变化在0。

LVDS原理及设计指南LVDS全称为Low Voltage Differential Signaling,即低压差分信号传输技术,它是一种高速、低功耗的数字信号传输技术,广泛用于各种数字通信和数据传输系统中。

LVDS通过传输差分信号来实现高速、可靠的数据传输,具有抗干扰性强、抗噪声能力好等优点,因此在现代电子设备中得到了广泛应用。

LVDS的工作原理主要是利用差分信号传输来传输数据。

差分信号是指由两个信号线构成的信号对,在信号线上分别传输正向和反向的信号,两个信号之间的电压差被接收端检测和解码,从而实现数据传输。

LVDS的发送端会对输入的数字信号进行编码,生成差分信号,并通过差分传输线传输到接收端,接收端再对差分信号进行解码还原成数字信号。

LVDS的设计主要包括发送端和接收端两个部分。

在发送端,需要对输入的数字信号进行编码,生成差分信号。

一般采用的编码方式包括常见的3态编码和4态编码,通过控制电压的变化来实现数据的传输。

发送端的差分信号经过一定的调整和驱动电路之后,通过传输线传输到接收端。

在接收端,需要对接收到的差分信号进行解码,将其还原成数字信号。

接收端会对差分信号进行增益放大和滤波处理,然后通过解码电路将其转换成数字信号。

接收端还会对接收到的信号进行校验和误码纠正,以确保数据传输的可靠性和稳定性。

在LVDS的设计中,需要考虑以下几个方面:1.差分传输线的设计:差分信号传输需要一对信号线,信号线要保持相同长度,阻抗匹配,以确保信号的高速传输和抗干扰能力。

2.发送端和接收端的电路设计:发送端需要设计合适的驱动电路和编码电路,以确保差分信号的稳定输出;接收端需要设计合适的放大电路和解码电路,以确保差分信号的准确解码和数据还原。

3.时序和信号完整性设计:在设计LVDS系统时需要考虑时序和信号完整性,确保信号的传输速度和数据的准确性。

4.抗干扰设计:LVDS的差分信号传输具有较好的抗干扰能力,但在实际应用中可能会受到外部干扰的影响,因此需要设计合适的抗干扰措施,如屏蔽、滤波等。

TS48V 高清LVDS 编码板接线图V0.61. 接口定义说明:2. FH3接口(LVDS ,接EH6300接口,USL00-30L-C)FH330,29 … 2, 1FH2 1,2 … 23,243.FH2接球机解码器接口(24P FPC)Pin NO. 名称说明备注1 PWFBOUT 电源反馈输出系统测试2 TPRX- 网络接收数据负接RJ45口3 TPRX+ 网络接收数据正接RJ45口4 GND 接地接RJ45口5 TPTX+ 网络发送数据正接RJ45口6 TPTX- 网络发送数据负接RJ45口7 LED_LINK# 网络连接指示灯接RJ45口8 LED3/PHYADD3 网络应答指示灯接RJ45口9 GND10 TX_33 232串行数据输出(3.3伏)连接云台解码器,控制一体机11 RX_33 232串行数据输入(3.3伏)连接云台解码器,控制一体机12 GND13 485+ 485串行数据正连接云台解码器,控制云台14 485- 485串行数据负连接云台解码器,控制云台15 GND 地连接CRT监视器16 CVBS 模拟视频输出连接CRT监视器17 AGND_VOP18 USB_DM USB数据正接USB口(注:USB设备电源外供)19 USB_DP USB数据负接USB口(注:USB设备电源外供)20 DRESET21 GND 地22 12V 电源12伏23 12V 电源12伏24 12V 电源12伏4.应用原理说明:备注:变焦是由解码板直接控制一体机。

5.使用连接说明准备内容:1.TSTS48V视频编码板1块。

2.EH6300一体机1台。

3.30Pin细同轴数据线1条。

4.24 Pin FPC数据排线1条。

5.“SC110_CONNECTOR_V1.0”测试接口板1块。

6.PC(XP)1台,装UC客户端。

备注:1.30Pin的管脚的顺序从左到右。

24Pin的管脚的从顺序从右到左。

在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(Wo rd Aligner)。

一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。

另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。

FPGA对上述两种方案都可以进行正确处理。

对于标准协议,FPGA通常都会有知识产权(IP)模块提供。

本文主要讨论在FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐的设计方法及步骤。

LVDS已经成为业界高速传输最普遍应用的差分标准。

LVDS的优势包括:由于采用差分信号带来的对共模噪声的免疫能力,进而提高了抗噪声能力;功率消耗较小,噪声较小等。

由于LVDS有比较好的抗躁声特性,它可以采用低至几百毫伏的信号摆幅,进而可以支持更高的数据速率。

LVDS串行器/解串器(SERDES)可以完成多位宽度的并行信号到LVDS串行信号的转换以及反方向操作,如图1所示。

有些器件提供图1中的随路时钟,但有些器件可能并不提供,这时LVDS解串器还必须具有时钟恢复(CDR)功能。

市面上有各种规格的LVDS SER DES器件,此外FPGA或其它一些器件也都能集成LVDS SERDES模块。

图1:LVDS串行器/解串器的功能示意图。

为确保正确的数据传送,通过LVDS接收器后必须能恢复字顺序,即输入到LVDS串行器的最高比特能够正确地出现在解串器恢复输出数据的最高比特位置上,至少是需要预先知道出现在哪个比特位置上后再进行调整。

图2和图3分别给出了4位宽度下字顺序得到保留和没有得到保留的例子。

对于图3的情况,需要采用一种方法找把字顺序调整过来。

图2:字顺序得到保留。

图3:字顺序没有得到保留。

字顺序的调整通常采用寻找训练码来进行。

一些标准的协议通常会定义特殊的码型来进行字对齐处理,比如8B/10B编码中K28.5码型的主要功能就是字对齐处理。

LVDS信号的工作原理和特点引言概述:LVDS(Low Voltage Differential Signaling)是一种数字信号传输技术,它通过差分信号传输数据,具有高速传输、抗干扰能力强等特点,被广泛应用在各种数字通信系统中。

本文将详细介绍LVDS信号的工作原理和特点。

一、LVDS信号的工作原理1.1 LVDS信号的差分传输LVDS信号是通过差分传输方式传输数据的,即同时传输正向和反向的信号。

在发送端,正向信号和反向信号的电压大小相等,但正负相反;在接收端,通过比较正向和反向信号的差值来恢复原始数据。

1.2 LVDS信号的编码方式LVDS信号采用的是非归零编码方式,即逻辑“1”和逻辑“0”分别用高电平和低电平表示,不会出现直流分量,有利于减小传输中的干扰和功耗。

1.3 LVDS信号的传输速率LVDS信号的传输速率通常较高,可以达到几百兆赫兹甚至更高的速率,适用于对传输速率要求较高的应用场景,如高清视频传输、数据通信等。

二、LVDS信号的特点2.1 高速传输LVDS信号采用差分传输方式,传输速率高,抗干扰能力强,适用于高速数据传输的场景。

2.2 低功耗由于LVDS信号采用非归零编码方式,不会产生直流分量,因此功耗相对较低,适用于对功耗要求较高的应用场景。

2.3 抗干扰能力强LVDS信号在传输过程中采用差分传输方式,能够有效抵抗来自外部干扰的影响,保证数据传输的稳定性和可靠性。

三、LVDS信号的应用领域3.1 高清视频传输LVDS信号可以实现高速数据传输,适用于高清视频传输领域,如数字电视、监控系统等。

3.2 数据通信LVDS信号在数据通信领域也有广泛应用,如计算机内部总线、网络设备等,能够满足对传输速率和稳定性要求较高的场景。

3.3 工业控制领域在工业控制领域,LVDS信号的高速传输和抗干扰能力使其成为理想的通信方式,可以应用于PLC、仪器仪表等设备中。

四、LVDS信号与其他传输方式的比较4.1 LVDS与CMOS的比较与CMOS传输方式相比,LVDS信号具有更高的传输速率和抗干扰能力,适用于对数据传输速率和稳定性要求较高的场景。

LVDS屏的测量

LVDS屏的接口描述:

LVDS(低差分信号)其工作原理是:把输入的TTL信号,通过一片专用的芯片编码差分为LVDS信号。

单6位屏为4组差分,(3组数据、1组时钟)单8屏为5组差分(4组数据、1组时钟)。

信号定义为:D0-、D0+ | D1-、D1+ | D2-、D2+ | CK-、CK+ | D3-、D3+,如果是单6位的屏就没有D3-、D3+这一组数据了。

LVDS的屏归根结底也是TTL的屏,因为LVDS的信号电平是1V左右,而且—线和+线之间的干扰可以相互抵消,抗干扰能力强,很适合用在高分辩率的屏上。

由于一些高分屏的分辩率实在是太高,单靠一路LVDS传输已不堪重负,所以都采用双路LVDS接口,降低每一路LVDS的速率,提高信号的稳定度,双6位屏就是为8组差分,(6组数据、2组时钟),双8屏为10组差分(8组数据、2组时钟)。

通常在LVDS接口屏中,多为扁平插头。

14P、20P、30P,也有双排21P的。

14P的理论上支持(单6、单8)位的屏,20P、21P的理论上支持(单6、单8、双6)位的屏,30P 的就都有可能了。

和TTL的屏比较,LVDS的屏要单一的多。

测量和估计要容易很多,LVDS的接口可以用万用表测屏,先找出地,再找到电源,电源是和保险在一起的,接着就是信号,LVDS屏的信号是成对的,没对之间的电阻是100欧,一般来说是(-、+、GND)难的是要识别时钟在数据之前还是在后。

21P双。

目 录VESA编码 (2)A.8BIT VESA编码 (2)B.10BIT (4)JEIDA编码 (4)8BIT JEIDA编码, (4)10BIT JEIDA编码 (5)通过屏线功能脚改变其编码方式 (5)单LVDS (5)通过屏第9脚改变 (5)通过屏第21脚改变 (6)双LVDS: (7)LG的屏第7脚改变编码方式 (7)三星的屏一般可以45脚改其编码方式, (7)LVDS缺少任意一组会缺少色彩 (8)缺少0‐+(图片效果)缺(R0‐5及B0) (9)缺少1‐+(图片效果)缺(B1‐B5,G0‐G1) (10)缺少2‐+(图片效果) (10)缺少3‐+(图片效果) (10)LVDS缺少任意一组会缺少色彩JEIDA编码, (11)缺少0‐+(图片效果) (11)缺少1‐+(图片效果) (12)缺少2‐+(图片效果) (13)缺少3‐+(图片效果) (13)正常画面 10BIT程序,屏也是10BIT编码 (14)10BIT程序,但屏的编码是8BIT (14)10 BIT VESA编码 屏是10BIT JEIDA编码 (15)8BIT程序8BIT的编码,正常画面 (15)8BIT程序10BIT VESA的编码 (15)8BIT程序10BIT的JEIDA编码 (15)奇偶问题 (16)LVDS编码方式VESA编码A.8BIT VESA编码定义一般式为0‐+,1‐+,2‐+,CLK‐+,3‐+共5组其中数据为4组时钟1组编码图示:一般奇美AU,编码标识图A一般三星屏LVDS VESA编码标识图图片效果:B.10BITJEIDA编码8BIT JEIDA编码,10BIT JEIDA编码LVDS缺少任意一组都出问题(体现色颜色不正常),而且程序输出编码与屏的编码方式要相对应,可以通规格书查看,并可以屏的功能脚改变其编码方式通过屏线功能脚改变其编码方式单LVDS通过屏第9脚改变A.(OPEN或3。

3为VESA,GND为JEIDA)其定义如下:通过屏第21脚改变B.双LVDS:LG的屏第7脚改变编码方式一般可以27脚改变10BIT与8BIT,三星的屏一般可以45脚改其编码方式,不能改其10BIT与8BIT选择LVDS缺少任意一组会缺少色彩VESA编码,程序是VESA屏VESA缺少0+(图片效果)缺(R05及B0)缺少1+(图片效果)缺(B1B5,G0G1)缺少2+(图片效果)a.缺(G2‐G5,DE HS VS)由于没有DE HS VS信号所以屏没法显示缺少3+(图片效果)b.缺(R6‐7,G6‐7,B6‐7)LVDS缺少任意一组会缺少色彩JEIDA编码, 程序JEIDA屏JEIDA缺少0+(图片效果)c.缺(R2‐R7,G2)缺少1+(图片效果)d.(G3‐G7,B2‐B3)缺少2+(图片效果)e.(B4‐B7,DE,HS,VS)由屏没有DE HS VS没法显示缺少3+(图片效果)f.(R0‐R1,G0‐G1,B0‐B1)正常画面 10BIT程序,屏也是10BIT编码10BIT程序,但屏的编码是8BIT10 BIT VESA编码 屏是10BIT JEIDA编码8BIT程序8BIT的编码,正常画面8BIT程序10BIT VESA的编码8BIT程序10BIT的JEIDA编码小结对于编码方式,24寸以下的屏LVDS编码方式是固定的,一般是VESA 编码,三星屏的为JIEDA编码,26寸以上的屏LVDS编码方式可以通过某个功能脚改变其编码方式,A单LVDS 9脚21脚视屏的定义来定,如上所说,B双LVDS通过7脚45脚,视屏的定义来定,如上所说,120HZ屏的编码与双LVDS编码相同,控制脚在51PIN的第7脚或45脚视定义来定LG 10BIT屏为了兼容8BIT模式,通过27脚可以选择,奇偶问题另外对屏的奇偶问题,一般看屏规格书,对我们屏线来讲主板端靠近电源近的为第一组(奇),另一组为第二组(偶),单LVDS只接第一组,有时视客户而定大尺寸屏线LG与奇美FHD屏大尺寸奇偶互反请看一下图,但小尺寸屏相同LG定义奇美定义(ODD奇,EVEN偶)奇偶反请看现象:120HZ屏LG与三星的屏的定义不同,接线也不相同,但是一般来讲接线请看下表,非一般情况要求特别注明ST6M20/ST6M30 屏接口PIN数对接1 36PIN 41PIN对接2 40PIN 51PINLG定义41PIN(第三、四像素)和51PIN(第一、二像素)三星定义51PIN(第一、三像素)和 41PIN(第二、四像素)120HZ两组线反了。

➢LVDS接口介绍

LVDS 是英文Low-Voltage Differential Signaling 的缩写,即低压差分信号。

LVDS 因其具有低噪声,低EMI,低功耗,高比特率,连接简单等特点,是当前液晶体电视中图像信号从信号处理板到显示屏的主要连接方式。

一、LVDS LVDS 电路原理电路原理电路原理及电气特性及电气特性及电气特性

LVDS 的规范由TIA/EIA-644 标准定义,其驱动和接受电路如下:

LVDS 的规范由TIA/EIA-644 标准定义,其驱动和接受电路如下:

LVDS 的电气特性如下表所示:

因为LVDS 接口采用低摆幅的差分信号来传输数据,对应的功耗极低,噪声很小,因而可以有很高的传输速率和比较远的传输距离。

标准中推荐的最大传输比特率655Mbps,而理论上的最大传输比特率可以达到1.923Gbsp,传输距离可以达到10M。

➢LVDS 数据发送方式

在液晶体电视中,需要输出到显示屏的信号是并行的图像信号和控制信号,而LVDS信号是串行传输的,所以在发

送端需要将并行数据转换为串行数据。

以8bit RGB 显示屏接口为例,每个显示周期需要传输8bit 的R信号,8bit 的G 信号,8bit 的B信号,及VS,HS,DE信号,总共为27 BIT。

而每对LVDS 信号线在一个TX 周期里只能传输7 BIT 数据,所以需要4 对数据线,外加一对时钟线。

LVDS 并串转换如下图所示:

上图中的每一组对线称为一个Pair,4 组数据线加一对时钟线称为一个

Channel ,LVDS 发送器总是将一个像素数据映射到(remapping)一个Channel 的一个发送周期(TX CLK)中。

如果是6BIT 显示屏,则并行数据有21 位(18位RGB 加3位控制信号),因此LVDS 接口每个Channel只需要3对数据线和一对时钟线。

如果是10BIT 显示屏,则并行数据有33位(30位RGB 加3位控制信号),因此LVDS 接口每个Channel需要5对数据线和一对时钟线。

通常,LVDS 接口的时钟为20MHz 到85MHz,因此对于输出像素时钟低于85MHz的信号,只需一个Channel 就可以;而对于输出像素时钟高于85MHZ的信号,比如1080P/60HZ的输出,像素显示时钟为148.5MHz,就不能直接用一个Channel传输,而是将输出的像素按顺序分为奇像素和偶像素,将所有的奇像素用一组LVDS 传输,所有的偶像素用另外一组LVDS 传输。

也就是说,需要两个Channel来传输1080P/60HZ 的信号。

对于像素显示时钟更高的信号,比如1080P/120HZ显示,则需要4个Channel来传输。

两Channel、4 Channel的像素分配分别如图4、图5所示:

➢LVDS 数据映射(MappingMapping)标准

LVDS接口电路中,将像素的并行数据转换为串行数据的格式主要有两种标准:VESA和JEIDA。

VSEA标准如下图所示:

JEIDA 标准是由日本电子行业开发协会(JAPAN ELECTRONIC INDUSTRY DEVELOPMENT ASSOCIATION)制定的标准,其格式如下

对于JEIDA格式,需要注意的是,如果像素为6bit RGB,则每个通道只需要最上面的 3 对数据线,其中的R9...R4, G9...G4, B9...B4 对应实际的R5...R0, G5...G0, B5...B0;同样,如果像素是8 bit RGB,则每个通道只需要靠上面的 4 对数据线,其中的R9...R2, G9...G2, B9...B2 对应实际的R7...R0, G7...G0, B7 0

另外,COLOR MAPPING 也可以采用自定义格式,只要LVDS 发送端和接受端采用相同的映射顺序,就可以显示正确的色彩。