嵌入式习题

- 格式:doc

- 大小:63.16 KB

- 文档页数:7

嵌入式系统期末考试试卷习题1.下面哪一种工作模式不属于ARM特权模式(A)。

A.用户模式B.系统模式C.软中断模式D.FIQ模式2.ARM7TDMI的工作状态包括(D)。

A.测试状态和运行状态B.挂起状态和就绪状态C.就绪状态和运行状态D.ARM状态和Thumb状态3.下面哪个Linux操作系统是嵌入式操作系统(B)。

A.Red-XXX Linux4.使用Host-Target联合开发嵌入式应用,(B)不是必须的。

A.宿主机B.银河麒麟操作系统C.目标机D.交叉编译器5.下面哪个不属于Linux下的一个进程在内存里的三部分的数据之一(A)。

A.寄存器段B.代码段C.堆栈段D.数据段选择题(共5小题,每题2分,共10分)1.下面哪一个系统属于嵌入式系统(D)。

A.“河汉一号”计较机系统B.IBMX200条记本电脑C.遐想S10上彀本D.Iphone手机2.在Makefile中的命令必必要以(A)键开始。

A.Tab键B.#号键C.空格键D.&键3.Linux支持多种文件系统,下面哪种不属于Linux的文件系统格式(B)。

A.ExtB.FAT32C.NFSD.Ext34.下面哪类不属于VI三种事情形式之一(D)。

A.命令行模式B.插入模式C.底行模式D.工作模式5.下面哪一项不属于Linux内核的配置系统的三个组成部分之一(C)。

A.MakefileB.配置文件(config.in)XXX.配置工具1.人们糊口中经常使用的嵌入式设备有哪些?罗列4个以上(1)手机,(2)机顶盒,(3)MP3,(4)GPS。

(交流机、打印机、投影仪、无线路由器、车载媒体、PDA、GPS、智能家电等等。

)2.ARM9处理器使用了五级流水线,五级流水具体指哪五级:(5)取指,(6)译码,(7)执行,(8)缓冲/数据,(9)回写。

3.在Makefile中的命令必须要以(10)Tab键开始。

4.Linux支持多种文件系统,主要包括哪些(写出其中4中就行)(11)Ext,(12)VFAT,(13)JFS,(14)NFS。

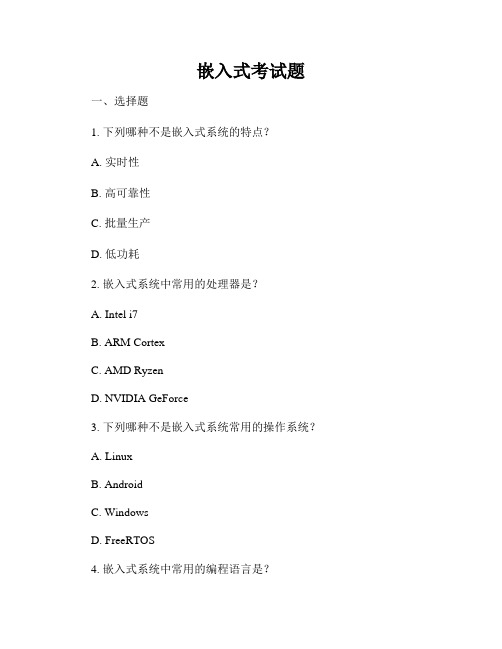

嵌入式考试题

一、选择题

1. 下列哪种不是嵌入式系统的特点?

A. 实时性

B. 高可靠性

C. 批量生产

D. 低功耗

2. 嵌入式系统中常用的处理器是?

A. Intel i7

B. ARM Cortex

C. AMD Ryzen

D. NVIDIA GeForce

3. 下列哪种不是嵌入式系统常用的操作系统?

A. Linux

B. Android

C. Windows

D. FreeRTOS

4. 嵌入式系统中常用的编程语言是?

A. Java

B. C++

C. Python

D. HTML

5. 以下哪种外设不能算作嵌入式系统的外设?

A. LCD显示屏

B. 小键盘

C. 摄像头

D. 鼠标

二、简答题

1. 什么是嵌入式系统?举例说明。

2. 嵌入式系统的设计流程包括哪些步骤?简要描述。

3. 什么是实时系统?嵌入式系统中为什么需要实时性?

4. 解释嵌入式系统中的中断处理机制。

5. 介绍一种常用的嵌入式系统开发工具及其功能。

三、计算题

1. 假设嵌入式系统中有一个定时器中断,中断间隔为10ms,如果在中断服务程序中运行一个函数需要5ms,问系统能否满足实时性要求?

2. 假设一个嵌入式系统的主频为50MHz,要求其通过串口发送一个100字节的数据包,波特率为9600bps,计算发送该数据包需要多长时间?

3. 假设一个嵌入式系统的Flash存储器容量为512MB,每个数据包大小为1KB,存储器可擦写次数为10000次,计算该存储器的寿命能够支持多少次数据包的写入操作?

以上为嵌入式考试题,请根据题目要求完成题目。

选择题1.W3C制定了同步多媒体集成语言规范,称为____规范。

A. XMLB. SMILC. VRMLD. SGML##2.________完全把系统软件和硬件部分隔离开来,从而大大提高了系统的可移植性。

A. 硬件抽象层B. 驱动映射层C. 硬件交互层D. 中间层##A3.在C语言中,设有数组定义:char array[]="China"; 则数据array 所占用的空间为______。

A. 4个字节B. 5个字节C. 6个字节D. 7个字节##C4.对某一寄存器某几位清零,可用一条指令_______来实现。

A. ANDB. ORC. NOTD. AOR##A5.实时操作系统(RTOS)内核与应用程序之间的接口称为________。

A. 输入/输出接口B. 文件系统C. APID. 图形用户接口##C6.在操作系统中,Spooling技术是用一类物理设备模拟另一类物理设备的技术,实现这种技术的功能模块称做____。

A. 可林斯系统B. 斯普林系统C. 图灵机系统D. 虚拟存储系统##7.文件系统的主要功能是______。

A. 实现对文件按名称存取B. 实现虚拟存储器C. 提高外村的读写速度D. 用于保护系统文档##8.在CPU和物理内存之间进行地址转换时,________将地址从虚拟(逻辑)地址空间映射到物理地址空间。

A. TCBB. MMUC. CacheD. DMA##9.以下叙述中,不符合RISC指令系统特点的是______。

A. 指令长度固定,指令种类少B. 寻址方式种类丰富,指令功能尽量增强C. 设置大量通用寄存器,访问存储器指令简单D. 选取使用频率较高的一些简单指令##10.在操作系统中,除赋初值外,对信号量仅能操作的两种原语是____。

A. 存操作、取操作B. 读操作、写操作C. P操作、V操作D. 输入操作、输出操作11.在面向对象系统中,用______关系表示一个较大的“整体”包含一个或多个较小“部分”的类。

嵌入式习题第一章(1)嵌入式系统的定义是什么?请问:以应用领域为中心,以计算机技术为基础,软件、硬件可以剪裁,适应环境应用领域系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

(2)详述嵌入式的发展历程和发展阶段。

答:历程:简单操作系统阶段,实时操作系统阶段,面向internet阶段。

发展阶段:第一阶段是scm(单片微型计算机)阶段,第二阶段是mcu(微控制器)阶段,第三阶段是soc阶段,第四阶段是以internet为标志的嵌入式系统。

(3)简述嵌入式系统的特点。

请问:低成本、低实时性、使用嵌入式系统或实时系统、高可靠性、低功耗、环境适应性不好、挤占系统资源太少、rom程序存储、多处理器体系结构、特定工具和方法研发、软件切割。

(4)嵌入式系统的分类:答:1单个微处理器、2不带计时功能的微处理器装置、3带计时器功能的组件、4在制造或控制过程中使用的计算机系统。

(5)基本构成:请问:嵌入式微处理器、外围硬件设备、嵌入式操作系统以及用户应用程序。

(6)嵌入式的应用领域:答:工业、交通、信息家电、家庭智能管理系统、pos网络及电子商务、环境工程与自然、机器人。

(7)嵌入式的发展趋势:请问:1高可靠性、低稳定性2运转速度快、研发周期短3强悍的拓展功能和网络运输功能。

(8)自学嵌入式系统技术的目的:答;第二章1请描述单片机系统和嵌入式处理器系统在开发流程上的异同各自复杂程度相同,具体内容设计过程略有不同。

单片机系统主要用作同时实现相对直观的掌控,系统核心内置在一块芯片―单片机上,再在外围重新加入USB电路即可。

软件部分不须要嵌入式操作系统的积极支持,只需使用汇编语言撰写针对特定应用领域的程序即可。

嵌入式微处理器的基本研发流程:1用户市场需求、2挑选微处理器及硬件平台、3挑选操作系统、4基于操作系统研发应用程序、5测试应用程序、6整个系统测试、7完结。

2恳请叙述传统的嵌入式系统设计方法及其缺点经过需求分析和总体设计,系统划分为硬件子系统和软件子系统两个独立部分,随后硬件工程师和软件工程师分别对两部分进行设计,调试和测试,最后软硬件集成并对集成的系统进行测试。

选择题1、嵌入式系统有硬件和软件部分构成,以下(C)不属于嵌入式系统软件.A。

系统软件 B. 驱动 C. ADS软件 D。

嵌入式中间件2、ARM处理器的工作模式有( C )种.A. 5 B。

6 C. 7 D。

83、ARM寄存器组有(D )个寄存器。

A、7B、32C、6D、374、下列CPSR寄存器标志位的作用说法错误的是(D)。

A。

N:负数 B. Z:零 C. C: 进位 D. V: 借位5、ARM复位异常的入口地址是( A ).A、0x00000000B、0x00000008C、0x00000018D、0x000000146、下列描述不属于RISC计算机的特点的是(C)。

A.流水线每周期前进一步. B.更多通用寄存器。

C.指令长度不固定,执行需要多个周期.D.独立的Load和Store指令完成数据在寄存器和外部存储器之间的传输。

7、关于μCOS-II应用,以下说法不正确的是(B )。

A、任务可以有类型说明B、任务可以返回一个数值C、任务可以有形参变量D、任务是一个无限循环8、μCOS-II操作系统不属于( C).A、RTOSB、占先式实时操作系统C、非占先式实时操作系统D、嵌入式实时操作系统9、实时操作系统中,两个任务并发执行,一个任务要等待其合作伙伴发来信息,或建立某个条件后再向前执行,这种制约性合作关系被成为(A).A。

同步 B。

互斥 C。

调度 D. 执行10、每种嵌入式操作系统都有自身的特点以吸引相关用户,下列说法错误的是(D)。

A. 嵌入式Linux提供了完善的网络技术支持;B. μCLinux是专门为没有MMU的ARM芯片开发的;C. μC/OS—Ⅱ操作系统是一种实时操作系统(RTOS);D. WinCE提供完全开放的源代码。

11、存储一个32位数0x12345678到2000H~2003H四个字节单元中,若以大端模式存储,则2000H存储单元的内容为( D).A、0x21B、0x68C、0x65D、0x0212、ARM指令集和Thumb指令集分别是(D )位的。

1.以下哪项不属于精简指令集(RISC)架构:A.ARMB.X86C.MIPSD.PPC2.以下关于SOC的描述,正确的是?A.S3C2410是基于ARM7的SOCB.微处理器内核与外设整合在一个芯片C.ARM系列全部是SOCD.Intel PCA架构不属于SOC3.以下关于嵌入式操作系统的描述,不正确的是A.VxWorks属于不可剥夺型内核的操作系统B.IOS与Android均属于UNIX-Like系统C.操作系统是屏蔽硬件的中间件D.uC/OS-II任务调度为抢占式4.以下关于编译的描述,不正确的是?A.预处理是指处理C文件的Include以及define指令等B..elf经反汇编后转换为.c文件C.ld指令的操作对象是.o文件,操作结果为.elf文件D..c文件经汇编后形成.o文件5.以下关于RAM,ROM,Flash的描述,正确的是?A.全部为非易失性存储器B.RAM存取速度最快C.全部为并行随机存储器D.Flash不可以片内执行程序6.以下关于Nor Flash与Nand Flash的描述,错误的是?A.容量相同的情况下,Nand Flash体积更大,价格更高B.Nor Flash地址总线与数据总线分开,Nand Flash地址与数据串行传输。

C.Nor Flash不但可以存储数据,还可以执行程序D.一般情况下,Boot Loader存放在Nor Flash,而OS存放于Nand Flash.7.以下S3C2410与ROM的接线方案([A]为ROM地址线,[ADDR]为CPU地址线),正确的是?A.一片8BIT ROM,[A0]-[ADDR0],依次类推B.两片8BIT ROM,[A0]-[ADDR0],依次类推C.两片16BIT ROM,[A0]-[ADDR0],依次类推D.一片32BIT ROM,[A0]-[ADDR1],依次类推8.以下存储器K9F1208U0M的存储结构,描述错误的是:A.四个Plane,每个Plane 1024个块B.Plane中的块连续存放C.每页分3次读取D.每个块32页,每页526字节9.以下哪项是运行于WINDOWS系统下的ARM开源编译工具链?A.Arm-linux-gccB.IARC.Arm-none-eabi-gccD.ARM ADS10.以下关于驻留仿真调试的描述,错误的是?A.Boot Loader作为Server, 运行与目标机器B.Boot Loader可通过串口线接受调试指令C.Boot Loader可通过TCP/IP协议接受目标程序,并将其放到目标内存执行D.程序每次更新都要重新进行烧录11.以下哪种仿真调试方案不宜用于实时性要求高的应用?A.IAR + JLINKB.ECLIPSE+GUN GCC+GDB CLIENT+OPENOCD+OPENGTAGC.Eclipse+GNU GCC+GDB+JlinkD.ECLIPSE+GNU GCC+BOOTLOADER+LINUX KENEL(NFS)12.以下哪项指令实现连接GDB SERVER的作用A.Monitor goB.Target remote localhost:2331C.Monitor haltD.Continue13.以下S3C2440的定时器描述错误的是?A.所有定时器均具备PWM功能B.两级预分频可取的更宽的定时范围C.基本时钟输入单位是PCLKD.核心是比较器和计数器14.以下关于I2C的描述,错误的是?A.只有两条线,SDA为数据线,SCL为时钟线B.SDA在SCL高电平状态下,下降沿开始传输,上升沿结束传输C.接收方SDA第九个周期拉低表示ACKD.SCL高电平期间读取数据,低电平期间发送数据15.以下关于字节顺序的描述,不正确的是A.小端模式是指LSB在前,大端模式反之B.大端模式是指LSB在前,小端模式反之C.X86为小端模式,PPC为大端模式D.ARM可设置为大端或小端模式16.关于RISC的描述,以下哪个是正确的?A.Intel X86属于RISCB.ARM不属于RISCC.RISC代表复杂指令集D.20%的指令承担80%的工作17.以下关于BSP的描述正确的是?A.BSP依赖于具体的硬件B.U-BOOT不属于BSPC.相同的ARM硬件电路设计,搭载linux和uCosII的BSP相同D.同样搭载Linux系统,基于ARM9与ARM11硬件电路的BSP相同18.以下关于ARM920T的描述,不正确的是?A.支持JA V A加速B.支持Thumb指令集C.支持MMC,CacheD.体系架构为ARM4T19.以下关于GPIO的描述,错误的是?A.共有117个多功能I/O端口B.包含GPxCON,GPxDAT,GPxUP共3个寄存器C.GPxCON配置端口复用功能D.GPA没有上拉电阻配置功能20.SDRAM,Nor Flash以及Nand Flash的存取速度由慢到快的速度排序是A.SDRAM,Nor Flash, Nand FlashB.SDRAM,Nand Flash,Nor FlashC.Nand Flash, Nor Flash, SDRAMD.Nor Flash, Nand Flash,SDRAM21.以下关于S3C2410的存储控制器,以下描述错误的是?A.设计中,可将SDRAM连接到BANK0B.共27位地址总线,容量为1G,分8个BANKC.通过steptone 技术,可实现Nand Flash启动D.可通过OM1,OM0选择16位或32位数据宽度22.以下关于存储器K9F1208U0M的地址结构的描述,错误的是A.A9 ~ A13为块内页地址B.A14 ~ A25为Plane内块地址C.A14 ~ A15为Plane地址D.A0 ~ A8为Plane列地址23.以下关于ARM920T在ARM状态下的寄存器的描述,正确的是A.R14 = R15 + 4B.R1~ R15在所有模式下定义均相同C.CPSR 为当前状态寄存器,头五位用于决定处理器工作模式D.R13为程序计数器,R14为堆栈指针寄存器24.以下关于JTAG仿真的说法,正确的是?A.JTAG仿真需要网线或串口线的支持才能进行B.JLink 是实现串口(通常为USB)转换JTAG协议的工具。

第1章嵌入式体系基本【1 】1.什么是嵌入式体系?它由哪几部分构成?有何特点?写出你所想到的嵌入式体系.答:(1)界说:国内对嵌入式体系的一般界说是:以运用为中间,以盘算机技巧为基本,软硬件可裁剪,从而可以或许顺应现实运用中对功效.靠得住性.成本.体积.功耗等严厉请求的专用盘算机体系.(2)构成:嵌入式处理器.外围装备.嵌入式操纵体系和运用软件等几部分构成.(3)特点:a.软硬件一体化,集盘算机技巧.微电子技巧.行业技巧于一体;b.须要操纵体系支撑,代码小,履行速度快;c.专用紧凑,用处固定,成本迟钝;d.靠得住性请求高;e.多样性,运用普遍,种类繁多.(4)嵌入式体系:小我数字助理(PDA).机顶盒(STB).IP德律风.2.嵌入式处理器分为哪几类?答:(1)低端的微控制器(MicroController Unit,MCU);(2)中高端的嵌入式微处理器(Embeded MicroProcessor Unit,EMPU);(3)通讯范畴的DSP处理器(Digital Signal Processor,DSP);(4)高度集成的片上体系(System on Chip,SoC).3.ARM英文原意是什么?它是一个如何的公司?其处理器有何特点?答:(1)英文原意:Advanced RISC Machines.高等精简指令集机械.(2)公司简介:该公司是全球领先的16/32位RISC微处理器常识产权设计供给商,经由过程将其高机能.低成本.低功耗的RISC微处理器.外围和体系芯片设计技巧让渡给合作伙伴来临盆各具特点的芯片.ARM公司已成为移动通讯.手持装备.多媒体数字花费嵌入式解决计划的RISC尺度.(3)其处理器特点:a.小体积.低功耗.低成本而高机能;b.16/32位双指令集;c.全球的合作伙伴浩瀚.4.什么是及时体系?它有哪些特点?若何分类?答:(1)及时体系的界说:及时体系(Real Time System)是指产生体系输出的时光对体系至关重要的体系.(2)特点:及时性.并行性.多路性.自力性.可猜测性.靠得住性.(3)分类:依据响应时光的不合,及时体系可分为3种类型:强及时体系.弱及时体系.一般及时体系.依据肯定性的不合,及时体系可分为2种类型:硬及时.软及时.5.RTOS由哪几部分构成?它有哪些特点?与一般操纵体系比拟有何不合?答:(1)构成:及时内核.收集组件.文件体系.图形用户界面.(2)特点:a.支撑异步事宜的响应;b.中止和调剂义务的优先级机制;c.支撑抢占式调剂;d.肯定的义务切换时光和中止延迟时光;e.支撑同步.(3)与一般OS的不合:a.及时性:响应速度快,只有几微秒;履行时光肯定,可猜测;b.代码尺寸小:只有10~100KB,节俭内存空间,下降成本;c.运用程序开辟较难;d.须要专用开辟对象:仿真器.编译器和调试器等.6.单片机体系.嵌入式体系和SOC体系三者有何差别和接洽?答:(1)今朝嵌入式体系的主流是以32位嵌入式微处理器为焦点的硬件设计和基于及时操纵体系(RTOS)的软件设计;(2)单片机体系多为4位.8位.16位机,不合适运行操纵体系,难以进行庞杂的运算及处理功效;(3)嵌入式体系强调基于平台的设计.软硬件协同设计,单片机大多采取软硬件流水设计;(4)嵌入式体系设计的焦点是软件设计(占70%阁下的工作量),单片机体系软硬件设计所占比例基底细同.(5)SoC是嵌入式体系的最高实现情势,它集成了很多功效模块,它的焦点技巧是IP(Intellectual Property Core,常识产权核)核.7. 无第2章嵌入式体系开辟进程1.嵌入式体系开辟进程分为哪几个阶段?每个阶段的特点是什么?答:(1)需求剖析阶段:a.对问题的辨认和剖析;b.制订例格解释文档;c.需求评审.(2)设计阶段:a.数据流剖析;b.划分义务;c.界说义务间的接口.(3)生成代码阶段:a.代码编程;b.交叉编译和链接;c.交叉调试;d.测试.(4)固化阶段2.嵌入式体系有哪几种调试方法?如今最风行的是哪种?运用什么接口?答:(1)调试方法:源程序模仿器方法.监控器方法.仿真器方法.(2)如今最风行的是仿真器方法,运用JTAG(Joint Test Action Group,结合测试行为组)接口.3.什么是板级支撑包?它一般应完成哪些工作?答:(1)界说:有些嵌入式操纵体系的内核明白分为两层,上层一般称为“内核”,而底层则称为“硬件抽象层”或“硬件适配层”,缩写为HAL,有的厂商将硬件抽象层称为BSP,即板级支撑包(BoardSupport Package).(2)重要完成工作:a.在体系启动时,对硬件进行初始化.B.为驱动程序供给拜访硬件的手腕.(3)重要感化:清除硬件差别.第3章 ARM体系构造1.ARM的英文全名是什么?ARM处理器有什么特点?答:见第1章课后习题第3题.2.ARM7和ARM9在流水线方面有何不合?答:ARM7是3级流水线构造,ARM9是5级流水线构造.AR]M9把3级流水线中的履行阶段的操纵进行再分派,即把履行阶段中的“存放器读”插在译码阶段中完成,把“存放器写”安插在另一级(即第5级)完成,同时,在该级之前,再安插一级(存储拜访).3.ARM处理器支撑的数据类型有哪些?答:(1)Byte 字节,8位;(2)Halfword 半字,16位;(3)Word 字,32位;4.写出ARM运用的各类工作模式和工作状况.答:(1)工作模式:详见下表:(2)工作状况:a.ARM:32位,这种状况下履行字对齐的ARM指令;b.Thumb:16位,这种状况下履行半字对齐的Thumb指令.5.ARM处理器总共有若干个存放器?个中哪个用做PC?哪个用做LR?答:(1)ARM处理器总共有37个存放器:31个通用存放器,6个状况存放器. (2)R15用做程序计数器PC,R14用做子程序链接存放器LR.6.假设R0=0x12345678,运用将R0存储到0x4000的指令存到存储器中,若存储器为大端组织,写出从存储器0x4000处加载一个字节到R2的指令履行后R2的值.答:因为0x4000是大端组织,所以R0存进后,0x4000中稀有0x56781234,从0x4000加载一个字节到R2后(由地位到高位加载),R2的值为0x34. 7.ARM920T处理器参加了哪两个协处理器?各自的重要功效是什么?答:ARM920T处理器参加了两个协处理器:(1)CP14,许可软件拜访调试通讯通道;(2)体系控制协处理器CP15,供给了一些附加存放器用于设置装备摆设和控制Caches.MMU.呵护体系.时钟模式和其他体系选项.8.ARM920T支撑哪些时钟模式?答:快速总线模式.同步模式.异步模式.9.什么是写直达和写回Cache操纵,各有何特点?答:(1)写直达:当CPU对Cache写射中时,Cache与主存同时产生写修正.长处:一致性好;缺陷:耗时.(2)写回:当CPU对Cache写射中时,只修正Cache的内容而不立刻写入主存,只当此履行被换出时才写回主存.长处:削减拜访主存次数,进步效力.缺陷:一致性差点.10.ARM为何集成了32位的ARM指令集和16位的Thumb指令集?(即它的利益)答:可供给长的转移规模.壮大的算术运算才能和大的寻址空间.11.什么是big-endian和little-endian,编写一段程序测试你所用的盘算机体系构造采取哪种存储机制?答:(1)大端存储体系(big-endian):低地址存放高字节,高地址存放低字节.小端存储体系(little-endian): 低地址存放低字节,高地址存放高字节.(2)int x=0x12345678;int *p=&x;if(*(char*)p=0x78)…little endianelse…big endian第4章 ARM体系硬件设计基本1.一个典范的可履行映像由哪几部分构成?答:2.汇编和C说话的互相挪用办法.答:(1)汇编程序挪用C程序的办法为:起首在汇编程序中运用IMPORT伪指令事先声明将要挪用的C说话函数;然后经由过程BL指令来挪用C函数.(2)C程序挪用汇编子程序的办法为:起首在汇编程序中运用EXPORT伪指令声明被挪用的子程序,暗示该子程序将在其他文件中被挪用;然后在C程序中运用extern症结字声明要挪用的汇编子程序为外部函数. (填补)3.基于ARM的硬件启动流程?答:(1)分派中止向量表;(2)初始化存储器体系;(3)初始化各工作模式下的客栈;(4)初始化有特别请求的硬件模块;(5)初始化用户程序的履行情况;(6)切换处理器的工作模式;(7)挪用主运用程序.第5章基于S3C2410的体系硬件设计1.温习控制:P230 I/O口编程实例.填补:2.中止的处理流程?答:(1)保管现场;(2)模式切换;(3)获取中止源;(4)中止处理;(5)中端返回,恢复现场.3.中止存放器的感化及相干的操纵?P235-237.。

1.什么是冯诺依曼结构?什么是哈佛结构?STM32采用的是什么结构?为何要采用这种结构?答:哈佛结构是一种将程序指令存储和数据存储分开的存储器结构。

中央处理器首先到程序指令存储器中读取程序指令内容,解码后得到数据地址,再到相应的数据存储器中读取数据,并进行下一步的操作(通常是执行)。

冯·诺伊曼结构也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构。

程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置,因此程序指令和数据的宽度相同。

STM32采用的是哈弗结构。

原因是哈弗结构在一个机器周期内处理器可以并行获得执行字和操作数,提高了执行速度。

1.STM32采用的是32位处理器核Cortex-M3,各种寄存器是主要的编程对象。

2.Cortex-M3的CPU是司令部,是大脑。

3.总线矩阵具有仲裁功能,,由4个主动部件和4个被动部件组构成4.闪存FLASH通过FLASH端口连接CPU,FLASH有两条路到CPU,一条是传送指令的ICODE总线,另一条是传送数据的DCODE总线。

5.RCC全称是复位和时钟控制(RESET and CLOCK CONTROL),它是高速设备,连接在AHB总线上。

6.低速APB1外设的速度上限是36Mbit/s,APB2的速度上限是72Mbit/s,(注意bit和BYTE的区别)。

7.嵌套向量中断控制器(NVIC)负责中断控制,提供可屏蔽、可嵌套、动态优先级的中断管理。

8.闪存地址重载及断点(FPB),实现硬件断点以及代码空间到系统空间的映射。

9.28.STM32系列ARM Cortex-M3芯片支持三种复位形式,分别为系统复位、电源复位和备份区域复位。

10.STM32的所有端口都有外部中断能力。

当使用外部中断线时,相应的引脚必须配置成输入模式。

11.STM32具有单独的位设置或位清除能力。

这是通过GPIOX_BSRR 和GPIOX_BRR 寄存器来实现的。

第一章(1)嵌入式系统的定义是什么?答:以应用为中心,以计算机技术为基础,软件、硬件可剪裁,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

(2)简述嵌入式的发展历程和发展阶段。

答:历程:简单操作系统阶段, 实时操作系统阶段, 面向Internet阶段。

发展阶段:第一阶段是SCM (单片微型计算机)阶段,第二阶段是MCU(微控制器)阶段,第三阶段是SoC阶段,第四阶段是以Internet 为标志的嵌入式系统。

(3)简述嵌入式系统的特点。

答:低成本、高实时性、采用嵌入式系统或实时系统、高可靠性、低功耗、环境适应性好、占用系统资源少、ROM程序存储、多处理器体系结构、特定工具和方法开发、软件固化。

(4)嵌入式系统的分类:答:1单个微处理器、2不带计时功能的微处理器装置、3带计时器功能的组件、4在制造或控制过程中使用的计算机系统。

(5)基本构成:答:嵌入式微处理器、外围硬件设备、嵌入式操作系统以及用户应用程序。

(6)嵌入式的应用:答:工业、交通、信息家电、家庭智能管理系统、pos网络及电子商务、环境工程与自然、机器人。

(7)嵌入式的发展趋势:答:1高可靠性、高稳定性 2运行速度快、开发周期短 3强大的扩展功能和网络运输功能。

(8)学习嵌入式系统技术的目的:答;第二章1请描述单片机系统和嵌入式处理器系统在开发流程上的异同各自复杂程度不同,具体设计过程略有不同。

单片机系统主要用于实现相对简单的控制,系统核心集成在一块芯片—单片机上,再在外围加入接口电路即可。

软件部分不需要嵌入式操作系统的支持,只需采用汇编语言编写针对特定应用的程序即可。

嵌入式微处理器的基本开发流程:1用户需求、2选择微处理器及硬件平台、3选择操作系统、4基于操作系统开发应用程序、5测试应用程序、6整个系统测试、7结束。

2 请描述传统的嵌入式系统设计方法及其缺点经过需求分析和总体设计,系统划分为硬件子系统和软件子系统两个独立部分,随后硬件工程师和软件工程师分别对两部分进行设计,调试和测试,最后软硬件集成并对集成的系统进行测试。

缺点:1设计方法缺乏统一的软硬件协同表示方法;2设计周期很长;3硬件设计有一定盲目性;4难以充分利用软硬件资源。

3请描述软硬件协同设计的基本过程,他与传统的嵌入式系统设计方法有何不同?系统描述,软硬件划分,协同综合,协同仿真与验证,最后系统集成;与传统嵌入式系统设计方法相比,软硬件协同设计强调软件与硬件设计的并行性与相互反馈,提高了设计抽象的层次,拓展了设计覆盖范围,同时还强调利用现有资源,即重用构件和IP核,缩短系统卡发周期,降低系统成本,提高系统性能,保证系统开发质量。

4请描述嵌入式软件的测试技术嵌入式软件的测试主要分模块测试,集成测试,系统测试,硬件/软件集成测试4个阶段精心。

1白盒测试与黑盒测试白盒测试主要检查程序内部设计,根据源代码组织结构查找软件缺陷。

黑盒测试根据软件用途和外部特征查找缺陷2目标环境产生和宿主环境测试在宿主环境中,可进行逻辑或界面的测试以及与硬件无关的测试。

在目标环境中,进行与定时问题有关的白盒测试,中断测试,硬件接口测试等。

第三章选择题(1)一个完整的计算机系统包括硬件系统和软件系统。

(2)目前大部分的微处理器使用的半导体技术称为CMOS(3)在嵌入式系统的存储器结构中,存储速度最快的是寄存器组。

(4)嵌入式系统的特点:实时、技术密集、专用紧凑、安全可靠、微型化、(5)嵌入式应用软件一般在宿主机上开发,在目标机运行,因此需要一个交互编译环境。

简答题1、什么是嵌入式系统?答:嵌入式系统是以应用为中心,以计算机技术为基础,软件,硬件可剪裁,适应应用系统对功能,可靠性,成本,体积,功耗严格要求的专用计算机系统。

2.简述嵌入式处理器分类。

答:嵌入式微处理器,嵌入式微控制器,数字信号处理器,嵌入式片上系统。

3.简述ARM处理器的工作状态。

答:ARM状态:此时处理器执行32位的字对齐的ARM指令。

Thumb状态:此时处理器执行16位的、半字对齐的Thumb指令当ARM微处理器执行32位的ARM指令集时,工作在ARM状态;当ARM微处理器执行16位的Thumb 指令集时,工作在Thumb状态。

在程序的执行过程中,微处理器可以随时在两种工作状态之间切换,并且,处理器工作状态的转变并不影响处理器的工作模式和相应寄存器中的内容。

4.可以从那几个方面来理解PowerPC处理器体系结构,并简述之。

答:可以从三个层次来理解powerpc的体系结构,即指令集体结构,虚环境体系结构和操作系统体系结构,指令集体系结构是最底层程序员可见的的指令集他定义了基本的用户指令集,用户级寄存器,数据类型以及寻址方式,详细说明了什么样的寄存器可以应用以及如何进行按地址访问,在这一层次定义的成分构成了任何软件程序的基本组成部分。

虚环境体系结构属于第二层描述了软件程序必须遵守的存储器模型的语义以及定义了一些附加指令从应用程序员的角度解释了定时控制装置,并涵盖了存储器的cache模型,操作系统体系结构属于第三层即描述存储器管理结构。

监控级寄存器和异常模型。

详细说明了应用程序员接触不到的特权设施,包括中断和异常处理机制。

5.简述FPGA的结构资源。

答:FPGA的结构资源包括:硬件资源,软件资源,IP核资源。

硬件资源包括:输入输出引脚资源,内部资源;软件资源包括:设计输入工具,编译和综合工具,仿真工具。

6.简述SoC设计方法学。

答:软硬件协同设计,IP核生成及复用技术,超声亚微米设计。

7.简述使用多处理器结构需要考虑的几个问题。

答:节点间通信方式,任务调度策略,Cache一致性问题,系统的异构性问题。

第四章选择题(1)存储元件:1位二进制信息。

存储单元指:由若干存储元件组成,存放一个字节的所有存储元集合。

(2)存储周期是指存储器进行连续读或写操作所允许的最短时间间隔。

(3)和外存储器相比,内存的特点是容量小、速度快、成本高。

(4)某存储器容量位32x16位,则地址线为15根、数据线为16根。

容量表示:字节数如128MB 、字数x 字长如128kx16(5)(6)主存和CPU 间增加高速缓冲存储器的目的是解决CPU 和主存间的速度匹配问题。

填空题(1)SRAM 靠双稳态触发器存储信息,DRAM 靠MOS 电容存储电荷存储信息。

(2)DRAM 的刷新一般有集中、分散和异步刷新方式,刷新的原因是电容存在漏电。

(读写保持状态和刷新状态)。

三级结构:高速缓冲存储器——主存(内存)——辅存(外存)(3)主存可和CPU 、缓存和外存交换信息,外存可以和辅存交换信息,高速缓存可以和CPU 、主存交换信息。

(4)缓存是设在CPU 和主存之间的一种存储器,速度快、容量和价格有关。

(5)存储时间由快到慢排列:通用寄存器组、高速缓存、主存、磁盘、磁带。

简答题1、解释下列概念:RAM 、ROM 、PROM 、EPROM 、EEPROM 及Flash 存储器。

答:RAM :顺序存储器(RAM )是可读可写的存储器,CPU 可以对ROM 单元的内容随机地进行读写访问。

ROM :只读存储器(ROM )是一种半导体存储器,其特性是一旦存储数据就无法再将之改变或删除,且内容不会因为电源关闭而消失。

PROM :可编程只读存储器(PROM )其内部有行列式的镕丝,可依用户(厂商)的需要利用电流将其烧断,以写入所需的数据及程序,镕丝一经烧断便无法再恢复,亦即数据无法再更改。

EPROM :可抹除可编程只读存储器(EPROM )可利用高电平将数据编程写入,但抹除时需将线路曝光于紫外线下一段时间,数据始可被清空,再供重复使用。

EEPROM :电子抹除式可复写只读存储器 (EEPROM )”,相比EPROM ,EEPROM 不需要用紫外线照射,也不需取下,就可以用特定的电压,来抹除芯片上的信息,以便写入新的数据。

Flash 存储器:Flash 存储器是一种电子式可清除程序化只读存储器的形式,允许在操作中被多次擦或写的存储器。

2、解释下列名词:存储元件、存储单元、存储单元地址及存储字。

存储元件:用一个具有两种稳定状态,并且在一定条件下状态可互相装换的物理器件来表示二进制数码0和1,这种器件称为存储组件。

存储单元:有若干个存储元组成一个存储单元。

存储单元地址:存储单元按照一定的规则编号,这个编号称为地址,与存储单元一一对应。

半导体存储器双极型 MOS 型(随机存取存储器静态存储器SRAM 动态存储器DRAM用双稳态触发器:不断电不消失 MOS (晶体管极)电容:要不断给电容充电 速度快、集成低、价格贵 集成高、速度慢存储字:一个二进制数有若干位组成,但这个二进制数作为一个整体存入或取出时,这个字称作存储字。

3、存储器的主要功能是什么?如何衡量存储器的性能?答:存储器是具有记忆功能的部件,用来存放程序和数据,是构成嵌入式系统硬件的主要组成部分。

衡量存储器的主要性能指标有:1.存储容量。

2访问速度。

3.价格。

4.功耗。

5.可靠性。

4、为什么把存储系统分成若干不同的层次?主要有哪些层次?它们之间的有什么关系?答:1为了扩大存储器的容量和提高访存速度,将存储器系统分成若干不同的层次。

2有“高速缓冲存储器(Cache)---主存---辅存”3个层次。

3增加Cache的目的是为了提高速度;增加辅存的目的是为了弥补主存的容量不足。

5、试试比较SRAM和DRAM。

静态RAM和动态RAM都属随机存储器,即在程序的执行过程中既可读出又可写入信息。

但静态RAM靠触发器原理存储信息,只要电源不掉电,信息就不丢失;动态RAM靠电容存储电荷原理存储信息,即使电源不掉电,由于电容要放电,信息也会丢失,故需再生刷新。

6、试比较RAM和ROMRAM是随机存取存储器,在程序的执行过程中既可读出又可写入。

ROM是只读存储器,在程序执行过程中只能读出信息,不能写入信息。

7、存储芯片内的地址译码有几种方式?试分析他们各自的特点及应用场合?设计方案有两种:单译码和双译码。

单译码结构也称字结构。

在这种方式中。

地址译码器只有1个。

译码器的输出脚自选线,而自选线选择某个字的所有位。

这种结构有一个缺点,就是当n较大时,译码器将变得复杂而庞大,使存储器的成本上升,性能下降。

适用于小容量存储器。

在双译码方式中,地址译码器分成X向和Y向2个译码器,若每一个译码器有n/2个输入端,它们各可以译出2(n/2次方)个输入状态,那么2个译码器交叉译码的结果,共可译出2(n/2次方)*2(n/2次方)=2(n次方)个输入状态,其中n为地址码的二进制位数。

但此时译码输出线却只有2*2(n/2次方)根。

双译码结构适用于大容量存储器。

8、简述主存的读写过程答:存储器的读出过程是:CPU先给出有效地址,然后给出片选(通常受CPU访存信号控制)信号和读命令,这样就可将被选中的存储单元内的各位信息读至存储芯片的数据线上,完成了读操作。