ConceptHDL原理图设计

- 格式:doc

- 大小:6.41 MB

- 文档页数:20

Allegro Design Entry HDL原理图输入方式孙海峰Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL 环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open an Existing Project用以打开一个已有的项目;Create a New Project用以新建一个项目。

3、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有内容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

第七章Concept HDL原理图设计本章主要介绍Concept HDL原理图设计设计流程、用户界面以及编辑环境,学习如何使用Concept HDL软件来进行原理图设计,并以一些实际例子来给大家讲解如何进行一个项目的原理图设计,在讲解的过程中会对原理图设计过程中需要注意的问题、一些设计技巧以及一些习惯性的设置等做专门批注。

一、原理图设计的基础在进行原理图设计之前,必须学习一下原理图设计的一些基本规范和原理图设计的基本流程。

根据每个公司的要求不一样,原理图设计的规范和流程并不是完全一样的,在此给大家讲解一下基本规范和典型的原理图设计流程。

原理图设计的基本要求是:规范性、可读性、美观性。

1、原理图设计的规范■图幅的使用要统一对于一个项目的原理图设计,顶层图、分页图使用多大的图幅要统一。

在进行原理图设计之前,要选好图幅,如:A2、A3、A4等。

每个公司可以根据自己的需要将图幅设计成一定的格式然后做成原理图库,以便原理图设计者使用从而保证统一性。

■各功能布局的统一性在一页原理图中,各个功能布局要注意统一性。

如:电源一般在左上角,核心芯片在中间,时钟一般在右下角等。

■网络命名统一1)电源和地的命名统一。

如:3V3(3.3V的电源)、2V5(2.5V的电源)、5V(5V的电源)、GND(地平面)、PGND(保护地)等。

2)差分信号命名统一。

如:用P来代替+,用N来代替-。

3)全局网名统一用“\G”来表示。

4)总线的命名统一用“<M..N>”来表示。

5)低有效信号统一用“_N”来表示。

6)数据类信号用DATA来表示,时钟类信号用CLK来表示,地址类信号用ADDR来表示等。

■网名、位号、属性等的字体要大小适中,便于阅读■元件的摆放整齐有序、布局合理2、原理图设计的流程进行一个项目的原理图设计,主要分为3个阶段。

■设计前准备阶段此阶段主要是设计前的准备工作。

包括:总体方案的设计、元件的选型、库的设计及将其添加到项目中。

Concepthdl管脚名字不能使用非法字符如tx[15],改为tx15。

不然会报找不到实体名字的错误Concepthdl grid选项logic grid(预定义0.100 x 5)指在hdl上作图时,图上grid的分辨率,symbol grid(预定义0.050 x 2)指画原件符号本身时grid的分辨率。

如果在画图时出现划线对不上管脚的情况可以减小logic grid的分辨率。

Document grid(预定义0.100 x 5)不清楚Allegro做pcb板步骤总结1 作michanical板子边框,rooute keepin ,package keepin。

标注板子2 place component,先设计基本规则,注意如果有bga器件或者需要自动扇出的器件,要先扇出后再对具体网络进行规则设计如差分对,管脚对等,另外规则设计最好一次完成,考虑到所有情况,而且以后不再更改。

3 定义各个平面层包括加入的虚拟电源平面层,但不copper,多电源且只有一个电源平面层时可以先不定义分割vcc层4 先布需要手动布线的器件,如果有swap pin要先反标回原理图,然后自动布线完成设计。

5 自动布线完毕检查pcb,进行必要的修改gloss,然后检查是否有没连接网络,有无对设计有重大影响的drc 错误,当一切确认无误后,重新排列元件序号位置。

板子上需要加text注明的地方加text6copper各个平面层和信号层,出光绘在做gnd和power封装时,注意需要设置hdl_power属性使其变成一个网络符号。

还有如果封装符号不一样,将会导致packet-xl出错,删除packages,使用symbol重新产生即可传到allgro,封装不可见或不正确的情况。

如果是.dra的情况,修改Sch中元件JEDEC_TYPE的value使其指向正确的值。

(可以用part developer打开元件,重新设置属性,save退出,关闭原理图,重新打开即可以更新原理图重要修改元件的属性)如果是封装中的*.pad不可见,重新修改或创建pad。

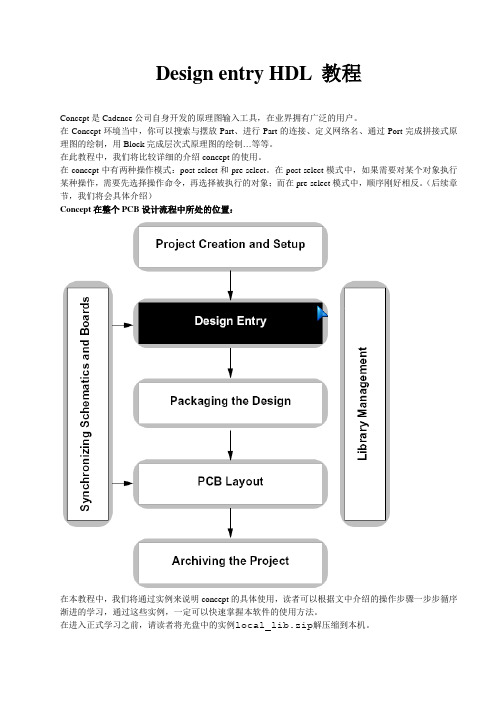

Design entry HDL 教程Concept是Cadence公司自身开发的原理图输入工具,在业界拥有广泛的用户。

在Concept环境当中,你可以搜索与摆放Part、进行Part的连接、定义网络名、通过Port完成拼接式原理图的绘制,用Block完成层次式原理图的绘制…等等。

在此教程中,我们将比较详细的介绍concept的使用。

在concept中有两种操作模式:post-select和pre-select。

在post-select模式中,如果需要对某个对象执行某种操作,需要先选择操作命令,再选择被执行的对象;而在pre-select模式中,顺序刚好相反。

(后续章节,我们将会具体介绍)Concept在整个PCB设计流程中所处的位置:在本教程中,我们将通过实例来说明concept的具体使用,读者可以根据文中介绍的操作步骤一步步循序渐进的学习,通过这些实例,一定可以快速掌握本软件的使用方法。

在进入正式学习之前,请读者将光盘中的实例local_lib.zip解压缩到本机。

本教程包含三大章节:第一章:创建一个项目在本章节中,将具体介绍项目的概念,库,cds_lib,project file以及如何创建项目。

第二章:原理图的绘制:在本章中将具体介绍多页原理图的绘制,内容涉及如何添加part,绘制连接线,绘制bus,检查整个设计等等。

第三章:原理图绘制的高级应用:在本章中将具体介绍层次式原理图的绘制,原理图网络表的产生,使用global find的功能来寻找整个设计中的某个元件以及对元件的属性进行编辑等等。

第一章:创建项目内容概要:●第一节概念1、什么是库2、什么是cds.lib file3、什么是project file●第二节创建一个项目(project)●第三节用project setup 来增加库第一节概念在cadence中,一个project包含如下的对象:1、涉及到的库;2、本地库(design libraries)3、Cds.lib 文件4、Project file(.cpm)接下来,将详细介绍什么是库?从设计原理图、PCB Layout直到进行真正的制造,不同的阶段,需要用到的元件的表现形式是不一样的。

AllegroDesign EntryHDL原理图输入方式孙海峰Design EntryHDL就是Cadence公司原有得原理图设计输入系统,提供了一个全面、高效、灵活得原理图设计环境,具有强大得操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图与平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好得集成在一个工程中,可很方便得实现原理图到PCB得导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述DesignEntry HDL原理图得输入方式。

一、进入DesignEntry HDL用户界面进入HDL原理图输入界面得步骤如下.1、执行“开始/程序/Cadence16、3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中OpenRecent用以打开最后运行得项目;Open Open an ExistingProject用以打开一个已有得项目;Create a New Project用以新建一个项目。

3、点击Createa NewProject新建项目,则进入新建项目向导,填入新建项目名称与保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要得元件库,Design 中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置得所有内容。

7、点击Finish按钮,在接下来得对话框中均确定就可以完成项目得新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径与文件名称;(2)菜单栏——项目所有相关操作得集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF—PCB菜单、工具菜单、窗口菜单与帮助菜单。

Allegro Design Entry HDL原理图输入方式海峰Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open an Existing Project用以打开一个已有的项目;Create a New Project用以新建一个项目。

3、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

Concept HDL原理图设计(二)层次原理图的设计在本章前面章节中,主要讲述了原理图的绘制方法,这一节主要讲述层次原理图的设计方法。

由前面所讲内容可以看出,层次原理图的设计使得原理图的设计更加清晰明了,各模块功能一目了然。

下面将详细讲述层次原理图的设计方法。

一、层次化设计的特点层次化设计技术使用符号代表功能,大大地减少了冗余的信息,并且功能模块能够重复调用,加强了团队合作性。

Design Entry HDL支持两种层次化的设计方法:自上而下的设计(TOP-DOWN)和自下而上的设计方法(DOWN-TOP)。

1、自上而下的设计方法自上而下的设计方法就是首先在顶层图(在创建项目的时候为TOP)中,定义模块(BLOCK),然后在各个模块中进行原理图的设计。

进入到顶层原理图之后,首先规划模块BLOCK1、BLOCK2等。

选择菜单栏BLOCK/ADD或者单击模块工具栏中的按钮来完成模块的添加,在添加的时候软件会自动以BLOCK1、BLOCK2等来给模块命名,如图7_46所示。

7_461)、模块名字的更改选择菜单栏中的BLOCK/Rename命令,在弹出对话框中输入新的模块名字,比如POWER,如图7_47所示。

单击“ok”,可以看到新输入的名字将跟随鼠标一起移动,将鼠标移动到要更改名字的模块上面,点击鼠标左键,BLOCK就会自动地更改为新输入的名字,如图7_48所示。

7_477_482)、模块的移动模块的移动和元件的移动是一样的,此处不再赘述。

3)、模块大小的调整选择菜单栏中的BLOCK/Stretch命令或者选择模块工具栏中的按钮,然后左键单击模块的边沿,松开鼠标左键后,拖动鼠标即可改变模块的大小,达到合适尺寸后再次单击鼠标左键即可完成调整。

4)模块管脚的添加选择菜单栏中的BLOCK/Add Pin/Input Pin(或者Output Pin、Inout Pin)命令,也可以直接选择模块工具栏中的按钮,弹出如图7_49所示对话框,在弹出的对话框中依次添加信号名(输完网络名后,回车输入下一个网络名),如图7_50所示。

Cadence SPB 15.5使用手册本手册仅供交流,甘振华20060207 一、Cadence SPB 15.5 安装方法:先在安装盘路径设置cadence_license文件夹,将cadence15.5源文件的crack文件夹中license.lic文件拷贝至cadence_license文件夹里。

设置环境变量:LM_LICENSE_FILE = ******\license.lic , 指向此SPB 15.5 的LIC路径。

打开安装源文件disk1,运行setup.exe,接受协议,直接安装products。

License Manager 信息为空,直接Next。

填写用户信息。

Control file为空,直接Next。

设置安装路径。

Products 全选。

设置工作文件夹路径。

IntelliCAD 可选件,可任选是否安装。

Footprint Viewer 设为默认。

安装文件夹设为默认,点击Next开始安装程序。

安装过程中………………………..,两个extension选择默认“否”确定:无license.dat 警告。

确定:安装库提示信息。

选择不马上重启计算机,并确定需重启信息,以便继续安装Cadence库文件。

二、安装concept HDL原理库打开源文件夹的disk4,运行setup.exe文件,安装concept HDL 库文件。

库Component的选择,PSpice可任选。

点击Next进行安装库文件。

安装过程中……………………………….安装结束,点击finish。

安装信息检查与修正检查环境变量LM_LICENSE_FILE = ******\license.lic是否被更改若选择安装了PSpice库,则需修正元件库cds.lib 。

打开安装路径下(D:\Cadence\SPB_15.5\share\library)的cds.lib,使用写字板打开编辑:将DEFINE spiceelem ./spiceelem修改为:DEFINE spice_elem ./spice_elem末行留一空行并存储。

Cadence SPB 15.5使用手册本手册仅供交流,甘振华一、Cadence SPB 15.5 安装方法:先在安装盘路径设置cadence_license文件夹,将cadence15.5源文件的crack文件夹中license.lic文件拷贝至cadence_license文件夹里。

设置环境变量:LM_LICENSE_FILE = ******\license.lic , 指向此SPB 15.5 的LIC路径。

打开安装源文件disk1,运行setup.exe,接受协议,直接安装products。

License Manager 信息为空,直接Next。

填写用户信息。

Control file为空,直接Next。

设置安装路径。

Products 全选。

设置工作文件夹路径。

IntelliCAD 可选件,可任选是否安装。

Footprint Viewer 设为默认。

安装文件夹设为默认,点击Next开始安装程序。

安装过程中………………………..,两个extension选择默认“否”确定:无license.dat 警告。

确定:安装库提示信息。

选择不马上重启计算机,并确定需重启信息,以便继续安装Cadence库文件。

二、安装concept HDL原理库打开源文件夹的disk4,运行setup.exe文件,安装concept HDL 库文件。

库Component的选择,PSpice可任选。

点击Next进行安装库文件。

安装过程中……………………………….安装结束,点击finish。

安装信息检查与修正检查环境变量LM_LICENSE_FILE = ******\license.lic是否被更改若选择安装了PSpice库,则需修正元件库cds.lib 。

打开安装路径下(D:\Cadence\SPB_15.5\share\library)的cds.lib,使用写字板打开编辑:将DEFINE spiceelem ./spiceelem修改为:DEFINE spice_elem ./spice_elem末行留一空行并存储。

Allegro Design Entry HDL原理图输入方式孙海峰Design Entry HDL是Cadence公司原有的原理图设计输入系统,提供了一个全面、高效、灵活的原理图设计环境,具有强大的操作编辑功能。

设计者在HDL环境中能够完成整个原理图设计流程,可以进行层次原理图和平面原理图输入、原理图检查、生成料单、生成网表等工作。

HDL还能与Allegro工具很好的集成在一个工程中,可很方便的实现原理图到PCB的导入,以及PCB改动反标到原理图等交互式操作。

接下来,按照原理图设计输入流程,我来详细阐述Design Entry HDL原理图的输入方式。

一、进入Design Entry HDL用户界面进入HDL原理图输入界面的步骤如下。

1、执行“开始/程序/Cadence 16.3/Design Entry HDL”命令,将弹出产品选择对话框2、进入产品界面,弹出Open Project对话框其中Open Recent用以打开最后运行的项目;Open Open an Existing Project用以打开一个已有的项目;Create a New Project用以新建一个项目。

3、点击Create a New Project新建项目,则进入新建项目向导,填入新建项目名称和保存位置,如下图。

4、点击下一步,进入Project Libraries对话框,在可用元件库中为项目添加元件库5、点击下一步,进入Design Name对话框,Library中选择需要的元件库,Design 中可以填写新建项目名称,也可以选择已有元件,对其进行修改。

6、点击下一步,进入Summary对话框,显示前面步骤所设置的所有内容。

7、点击Finish按钮,在接下来的对话框中均确定就可以完成项目的新建,并出现原理图工作界面。

其中:(1)标题栏——显示文件所在路径和文件名称;(2)菜单栏——项目所有相关操作的集合;包含了文件菜单、编辑菜单、视图菜单、元件菜单、画线菜单、文本菜单、模块菜单、群组菜单、显示菜单、仿真菜单、RF-PCB菜单、工具菜单、窗口菜单和帮助菜单。

原理图绘制过程中所需的所有相关操作都可在这些菜单中启动。

(3)工具栏——HDL原理图工作平台有很多工具栏,调用工具栏的方法也很简单,执行Views/Toolbar命令,弹出Customize对话框,即可调用工具栏。

(4)工作窗口——包含Hierarchy View窗口、Global Navigation窗口、ConsoleWindow窗口以及原理图设计窗口。

(5)状态栏——用户界面最下端的状态栏显示原理图基本状态设置。

二、设置Design Entry HDL在做原理图之前,应该做好前期的准备工作,所谓“工欲善其事,必先利其器”,将准备工作做好,再去做原理图,会事半功倍。

接下来,对HDL进行基本设置。

1、元件库的调用设置设计者在进行原理图设计时,需要使用Cadence自带的某些元件库,或者自己开发新的元件库,如何调用这些元件库呢,步骤如下:(1)执行“开始/Cadence/Release 16.3/Project Manager”,再选择产品类型,而后打开新建项目则进入Allegro Project Manager对话框;(2)点击Setup进入Project Setup对话框;在Project Setup对话框中,有Global标签下,设定或修改原理图设计所需的元件库,设计名称以及保存路径。

2、原理图绘制界面的基本设置执行HDL原理图绘制界面菜单栏中Tools/Options命令,或者在Project Setup对话框中T ools标签下点击Design Entry HI后的Setup进入DesignEntryHDL Options对话框,如下图,其中:(1)General——用以设置原理图设计的总体状况;(2)Font——用以设置原理图中元件、网络相关标识的字体、颜色等;(3)Paths——用以设置输入路径;(4)Graphics——用以设置绘图时画线、画点的基本情况;(5)Text——用以设置原理图中添加文本的内容、属性状况;(6)Color——用以设置原理图中元件、线、点、背景等的初始颜色;(7)Grid——用以设置栅格点;(8)Check——用以设置电气、走线、信号名、杂项和在线检查等检查情况;在做原理图的设计绘制前,以上几项设置好就可以了,其它项目不需要改变,只要选择默认设置,这样就完成了原理图设计的基本设置了。

最后原理图打印时,再在Plotting中设定打印页面,如下图。

三、HDL原理图设计结构原理图有两种设计结构:平坦式和层次式,平坦式电路在空间结构上看是在同一层次上的电路,知识整个电路分布在不同的页面,页面之间通过端口连接器连接起来;层次式电路结构上属于不同的空间层次。

1、平坦式电路设计平坦式电路在空间上同一层次,不同页面之间都有端口OFFPAGE连接,虽然它们不在同一页面,但是于再同一个电路图的文件夹中,电学上都是相通的,其结构框图如下图。

2、层次式电路图设计层次式电路在空间上的不同层次,一般先在一张图纸上用框图形式设计总体结构,然后再另一张图纸上设计每个子电路框图代表的结构,知道最后一层电路图不包含子电路框图为止,其结构框图如下。

四、HDL原理图绘制在原理图绘制界面基本设置完成后,下面就可以来进行原理图的绘制了。

1、产生一个设计页面执行File/New命令,就可以新建原理图绘制页面了。

2、调用页面图框在HDL中原理图框式作为Component来添加的,在原理图绘制页面,执行Component/Add命令,可在元件库中调用软件自带或者自己开发的边框封装。

3、元件、输入输出端口、电源接地等原理图封装的添加与编辑原理图页面基本设置完成后,就可以添加元件、端口、电源等封装了,执行Component/Add命令,弹出Component Browser对话框。

在该对话框中,设计者寻找自己所需的元件库以及对应元件,执行Add命令即可添加元件。

在Edit下拉菜单中,可执行元件的删除、移动、颜色变换、排列、复制等一系列编辑操作。

4、元件连线(1)绘制导线:执行Wire/Draw或者Wire/Route命令对元件进行连线和自动走线;(2)添加或修改导线网络名:执行Wire/Signal Name,填入网络名称,再点击相应网络,即可完成网络命名,也可以在走线时右击鼠标执行Signal Name命令来实现走线时定义网络名;执行Text/Change命令,再点击网络名,就可对网络名进行修改;Signal Name对话框如下:(3)绘制总线:执行Wire/Draw命令作导线,加入总线格式网络名,如DATA<7..0>,连线则自动转换成总线;(4)总线分支线命名:执行Wire/Bus Name命令,设置好总线支线名称排列方式,然后单击鼠标左键,再释放鼠标,自上而下贯通所需命名的总线支线如下图所示,然后单击左键,即可完成总线分支的自动编号,其中鼠标单击开始的位置作为高位如下图。

5、元件属性设置原理图设计绘制完成后,要首先确定或修改元件的相关属性,执行Text/Attributes命令,再单击所要编辑属性的元件即可出现Attributes对话框,则可以进行属性修改。

五、原理图检查完成原理图的绘制后,必须对原理图进行检查,以确保原理图能正确完整的导出网表方便PCB设计,其中原理图的检查包含以下几个方面。

(1)位号、电源/地网络检查:每个元件都需要设置位号,且位号不能重叠,可以手动添加位号,也可以在原理图打包时自动产生位号。

注意,位号的设置要与元件建库时的字符头一致;电源、GND检查比较重要,要确保这些网络无错接,无漏接。

(2)单网络检查:执行Tools/Packager Utilities/Electrical Rules Check命令,在弹出的对话框中,选择Single Node Nets检查,点击Run执行单网络检查,可根据单网络报告来检查修改。

(3)信号互连检查:单网络检查不能保证网络是否连接正确,因此有必要进行信号互连检查,首先执行Tools/Expend Design命令,而后执行Tools/Global Find 命令,则可在原理图上全局查找网络和元件,最后再执行Tools/Global Navigation命令,则可以逐个检查网络互连情况。

(4)其它方面检查:原理图检查除了以上的检查,其它检查也很重要,这主要包含总线连接检查,匹配电阻检查,每页原理图的注释文字检查等。

六、打包原理图原理图的打包工作,用以将原理图逻辑设计输入到物理设计,准备PCB布局布线;原理图与PCB之间的交互设计;电子规则检查;生成BOM;生成网表。

后续设计都以此为工作基础,因此,原理图的打包是必不可少的。

1、执行File/Export Physical命令,弹出Export Physical对话框如图:2、选择Package Design选项;3、Package Option中Preserve表示保留所有以前的打包信息,Optimize 表示重新打包更紧密的模块,Repackage表示忽略以前的打包信息重新打包;4、根据实际情况选择Update PCB Editor Board Option、Constraint ManagerData对话框等内容;5、点击OK命令,即可完成打包,打包过程中有时会遇到错误,出现下图。

经常出现的错误,在于元件属性错误,执行Text/Attributes命令,对元件属性进行编辑,使原理图正确打包。

七、创建平面元件在绘制原理图时,需要用到许多元件,虽然Cadence 16.3中具有丰富的元件库,但是这并不能满足设计者的需求,设计者往往需要创建自己的元件库,创建自己的元件平面元件。

Cadence提供了专用的原理图库管理工具——Library Explorer,可以进行元件库管理以及元件的编辑。

1、进入Library Explorer界面,创建新库(1)执行“开始/Cadence/Release 16.3/Library Explorer”,并选择Allegro PCB Librarian XL(PCB Librarian Expert)产品,进入Library Explorer 界面,如下图。

(2)在Library Explorer界面,执行File/New/Build Library命令,即可创建新的元件库,如下图新建元件库0410。

(3)右击新建元件库,即可出现以上命令,执行New Part命令即可在该元件库内创建新元件,如下图。

(4)在新建元件上右击,执行Part Developer命令,进入元件信息编辑界面如图。