第三讲、SOPC设计流程和软硬件协同设计方法(精选)

- 格式:ppt

- 大小:1.37 MB

- 文档页数:22

SOC的软硬件协同设计方法和技术摘要:随着嵌入式系统与微电子技术的飞速发展,硬件的集成度越来越高,这使得将CPU、存储器和I/O设备集成到一个硅片上成为可能,SOC应运而生,并以其集成度高、可靠性好、产品问世周期短等特点逐步成为当前嵌入式系统设计技术的主流。

传统的嵌入式系统设计开发方法无法满足Soc设计的特殊要求,这给系统设计人员带来了巨大的挑战和机遇,因此针对Soc的设计方法学己经成为当前研究的热点课题。

论文首先分析了嵌入式系统设计的发展趋势,论述了传统设计开发方法和工具的局限性,针对Soc设计技术的特点探究了Soc软硬件协同设计方法的流程,并讨论了目前软硬件协同设计的现状。

关键词: 软硬件协同设计,可重用设计,SOC背景:计算机从1946年诞生以来,经历了一个快速发展的过程,现在的计算机没有变成科幻片电影中那样贪婪、庞大的怪物,而是变得小巧玲珑、无处不在,它们藏身在任何地方,又消失在所有地方,功能强大,却又无影无踪,这就是嵌入式系统。

嵌入式系统是以应用为中心、计算机技术为基础、软件硬件可剪裁、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

嵌入式系统是将先进的计算机技术、微电子技术和现代电子系统技术与各个行业的具体应用相结合的产物,这一点决定了它必然是一个技术密集、高度分散、不断创新的知识集成系统。

嵌入式系纫‘泛应用于国民经济和国防建设的各个领域,发展非常迅速,调查数据表明,嵌入式系统的增长为每年18%,大约是整个信息技术产业平均增长的两倍[1],目前世界上大约有2亿台通用计算机,而嵌入式处理器大约60亿个,嵌入式系统产业是二十一世纪信息产业的重要增长点。

随着集成电路制造工艺的飞速发展,嵌入式系统硬件的集成度越来越高,这使得将嵌入式微处理器、存储器、I/O设备等硬件组成部件集成到单个芯片上成为可能,片上系统SoC (System on Chip)应运而生[2]。

SOC极大地缩小了系统体积;减少了板级系统SoB(System on Board)中芯片与芯片之间的互连延迟,从而提高了系统的性能; 强调设计重用思想,提高了设计效率,缩短了设计周期,减少了产品的上市时间。

基于底层硬件的软件设计,涉及了设备驱动程序的设计、嵌入式实时操作系统的定制/移植、基于底层硬件的软件体系架构等实用技术。

主要包括两个方面的内容:一是通用计算机在Windows、Linux和VxWorks等常见操作系统下的串/并/网络通信实现和USB、ISA、PCI 设备/板卡的驱动程序设计;二是嵌入式应用体系的直接基本软件架构与基于μC/OS、DSP/BIOS、WinCE/EXP、μCLinux及VxWorks等常见嵌入式实时操作系统下的基本软件架构及各类常见嵌入式软件体系下的UART、SPI、CAN、EMAC、ADC、DAC、存储器件等外设/接口的驱动软件设计。

书中还介绍了如何使用CPLD/FPGA/PAC等器件进行可编程数字/模拟逻辑软件的设计,进而实现所需的特定外设/接口及其连接与FPGASoPC软硬件协同的设计。

请参考《基于底层硬件的软件设计》软硬件协同设计一、软硬件协同设计的定义:软硬件协同设计是指对系统中的软硬件部分使用统一的描述和工具进行集成开发,可完成全系统的设计验证并跨越软硬件界面进行系统优化。

二、软硬件协同设计理论:首先是系统的描述方法。

目前广泛采用的硬件描述语言是否仍然有效?如何来定义一个系统级的软件功能描述或硬件功能描述?迄今为止,尚没有一个大家公认的且可以使用的系统功能描述语言可供设计者使用。

其次是这一全新的设计理论与已有的集成电路设计理论之间的接口。

可以预见,这种全新的设计理论应该是现有集成电路设计理论的完善,是建立在现有理论之上的一个更高层次的设计理论,它与现有理论一起组成了更为完善的理论体系。

在这种假设下,这种设计理论的输出就应该是现有理论的输入。

第三,这种全新的软硬件协同设计理论将如何确定最优性原则。

显然,沿用以往的最优性准则是不够的。

除了芯片设计师们已经熟知的速度、面积等硬件优化指标外,与软件相关的如代码长度、资源利用率、稳定性等指标也必须由设计者认真地加以考虑。

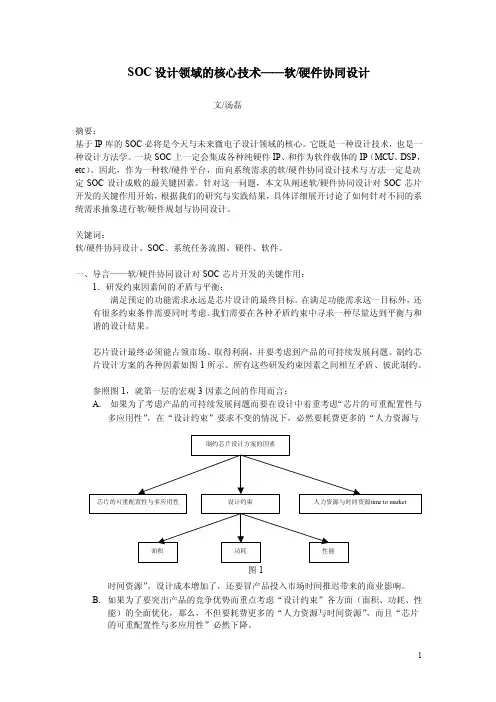

SOPC方案引言:在当今数字技术高速发展的时代,各类电子设备的设计与开发成为了不可或缺的一环。

嵌入式系统的设计需求越来越复杂,为了满足这一需求,诞生了SOPC(System on a Programmable Chip)方案。

本文将详细介绍SOPC方案的定义、优势以及应用领域,以便更好地理解和应用该方案。

定义:SOPC是一种将系统级硬件和软件集成在一个可编程芯片上的设计方案。

通过SOPC方案,用户可以根据自己的需求灵活设计硬件系统,并利用编程方式控制系统的功能和性能。

SOPC方案的核心是可编程逻辑器件,如FPGA(Field Programmable Gate Array)。

优势:1. 灵活性:SOPC方案采用可编程芯片,使得系统硬件可以根据需求进行灵活定制。

不同于传统固定功能的硬件电路,SOPC方案可以根据用户的具体需求进行设计和修改,提供更加灵活的解决方案。

2. 可重构性:利用SOPC方案,用户可以通过重新配置硬件逻辑通过编程方式快速修改和调整系统功能。

这种可重配置性使得系统在设计阶段和实际应用中具备更强的适应性和可扩展性。

3. 性能优化:通过SOPC方案,用户可以根据应用的需求和资源限制精确控制系统的功能和性能。

此外,由于硬件和软件的紧密结合,SOPC方案有助于提高系统的运行效率和优化功耗。

4. 开发效率:SOPC方案通过软件和硬件的集成,简化了系统设计的流程。

借助现成的IP核(Intellectual Property Core)和开发工具,开发人员可以快速搭建嵌入式系统,并且可以使用高级编程语言进行开发。

应用领域:1. 通信领域:SOPC方案在通信设备的设计中得到了广泛应用。

通过SOPC方案,通信设备可以适应不同的接口、协议和传输速率,并且可以进行灵活的调试和维护。

2. 工业自动化:SOPC方案可以用于工业自动化控制系统的设计与开发。

通过SOPC方案,工控系统可以根据具体要求进行硬件逻辑的编程,实现自动化控制和数据采集等功能。

基于FPGA的片上可编程系统(SOPC)设计一.Quartus II,用于完成Nios II系统的综合、硬件优化、适配、编程下载和硬件测试。

Nios II系统是工程的一部分。

二.SOPC Builder是Altera Nios II嵌入式处理器开发软件包,用于实现Nios II 系统的配置、生成、Nios II系统相关的软件的生成Nios II开发分硬件开发和软件开发两个流程,硬件开发过程主要由用户定制系统硬件,然后由SOPC Builder等工具完成系统硬件和对应的开发软件生成。

三.建立系统模块选择Quartus II菜单Tools->SOPC Builder…,打开与Quartus II集成的SOPC开发工具SOPC Builder。

弹出下图:输入系统名,本例中为:nios_ii,HDL选择Verilog。

确认后进入SOPC Builer设计界面。

在右上部分选择目标板和系统时钟,本例中目标板选DE2,系统时钟默认50M。

1.定制Nios 处理器(CPU Core)首先加入的是CPU核,选择组件栏中的Avalon Modules ->Nios II Processor右键点击,选择Add New Nios II Processor Altera Corporation…,打开配置对话框如下图:Nios II提供三个选项,经济、标准、快速的CPU核,我们选经济核。

其他选项表单中都默认,点击Finish完成。

并选择JTAG调试模块,Level1。

2. 加入on_chip_memory使用FPGA内部RAM资源,可以构成RAM或ROM,速度快,特别在调试时因为很少受外部连线等因素的限制很有用。

组件栏中选择Legacy Components->On-Chip Memory打开界面,如下图:定义了4k字节的RAM。

3. 加入JTAG(联合测试行动组)串口JTAG UART在调试中非常有用,在PC主机和FPGA之间进行串行字符流通信。

嵌入式系统设计嵌入式系统设计过程概念特性,特征硬件/软件划分硬件组成部分软件组成部分Estimation -Exploration硬件软件设计(S yn t he s is,La y ou t,…)设计(C om pi l at i on,…)验证和评估(尺寸, 功耗, 性能, …)传统软件/硬件开发模型面临的问题Break the wall today!传统设计方法存在的问题z缺少统一的软硬件表示方法z划分依靠先验定义z不能够验证整个系统z通过HW/SW 边界时很难发现不兼容问题z缺少成熟的设计流程z上市时间问题z描述更改变得困难发展过程z软硬件协同设计早期–主要是针对一个特定的硬件如何进行软件开发或根据一个已有的软件实现具体的硬件结构。

z前者是一个经典的软件开发问题–软件性能的好坏不仅仅取决于软件开发人员的技术水平,更有赖于所使用的硬件平台;z后者是一个软件固化的问题–实现的途径可以是采用一个与原有软件平台相同的硬件处理器,并将软件代码存储于存储器当中,也可以是在充分理解软件的内在功能之后完全用硬件来实现软件的功能。

软硬件共同设计能带来什么?z缩短开发周期z取得更好的设计效果z满足苛刻的设计限制z这种平台的推出将不仅包含芯片本身,还必须包含完整的开发系统和典型应用实例,而供应商提供的服务和技术支持也当然要成为产品不可分割的一部分。

目标和需求z统一的设计方法z执行独立z设计/执行验证z自动软件,硬件,接口合成商业应用z Research(研究)–CADLab, SIR/CASTLE (Germany), Chinook,COSMOS, COSYMA, CoWare, DICE,COMET, LYCOS (Denmark), POLIS,Ptolemy, Riley, TOSCA, AKKA, CODES,VIOOL, COOL…z Commercial(商业)–ArchGen(Synergy System Design, Inc.),Mentor Graphics, Synopsys, Synthesia->Cadence, Co-design Automation->Synopsys, Celoxica, CoWare, etc.缺点z典型的手动划分(manual Partition )z固定应用领域(carefully very specialized) z逐渐增长的评估需求支持很弱(no abstractmodels)z主要强调性能z模型的连贯性在设计重用中不被支持z商业系统更强调协同验证(co-verification)方面(more achievable goal)软硬件协同设计定义z软硬件协同设计定义–The meeting of system-level objectives byexploiting the trade-offs between hardware and software in a system through their concurrentdesign–软硬件共同设计目的是为硬件和软件的协同描述,验证和综合提供一种集成环境。

英文回答:Co—design of software and hardware is an important part of our product design process, which aims to maximize the synergy of hardware and software engineers and to ensure the soundness and efficiency of product functions and structures. Basic processes include four phases of needs analysis, architecture design, interface definition and validation testing. During the needs analysis phase, hardware and software engineers should listen extensively to user needs and ensure that product needs are clear and clear. During the architecture design phase, the software and hardware engineers are required to consult fully to determine the system architecture and division of labour. During the interface definition phase, hardware and software engineers are required to standardize the definition of interface protocols to ensure proper systemmunication. Finally, during the validation testing phase, hardware and software engineers should actively cooperate to ensure the reliability of products. Through this process, our co—engineering of software and hardware can improve the efficiency and quality of product research and development, be in line with the national strategy for science and technology development and promote technological innovation andindustrial upgrading.软硬件协同设计是我国产品设计过程中的重要一环,旨在充分发挥软硬件工程师的协同作用,确保产品功能和架构的合理性和高效性。

简要叙述软硬件协同设计的基本流程英文回答:Basic Flow of Software-Hardware Co-Design:The basic flow of software-hardware co-design involves the following steps:1. Requirement Analysis and Specification: Determine the system requirements, including both hardware and software components.2. System Architecture Design: Partition the system into hardware and software subsystems, considering performance, cost, and feasibility constraints.3. Hardware Architecture Design: Design the hardware architecture, including processors, memory, and I/O interfaces.4. Software Architecture Design: Design the software architecture, including software components, communication protocols, and data structures.5. Co-Simulation and Validation: Simulate the hardware and software systems together to verify their interaction and functionality.6. Integration and Testing: Integrate the hardware and software components and test their overall performance and compliance with requirements.7. Deployment and Maintenance: Deploy the system and provide ongoing maintenance and updates.中文回答:软硬件协同设计的基本流程:软硬件协同设计的基本流程包括以下步骤:1. 需求分析与规范,明确系统需求,包括硬件和软件组件。