艾米verilog笔记10-18

- 格式:pdf

- 大小:188.17 KB

- 文档页数:14

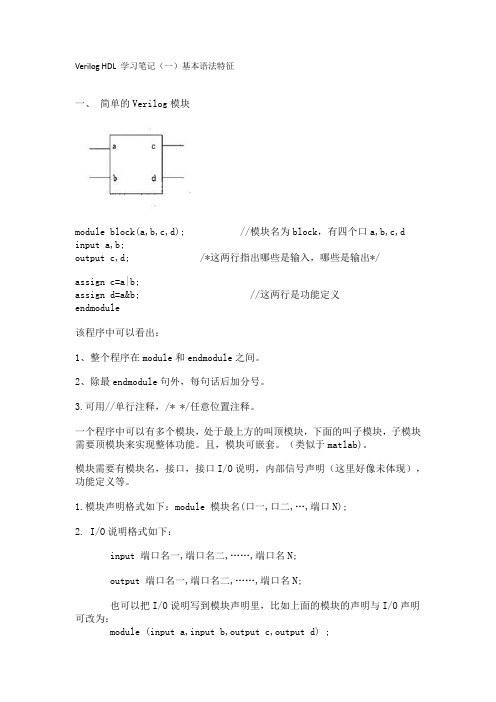

Verilog HDL 学习笔记(一)基本语法特征一、简单的Verilog模块module block(a,b,c,d); //模块名为block,有四个口a,b,c,dinput a,b;output c,d; /*这两行指出哪些是输入,哪些是输出*/assign c=a|b;assign d=a&b; //这两行是功能定义endmodule该程序中可以看出:1、整个程序在module和endmodule之间。

2、除最endmodule句外,每句话后加分号。

3.可用//单行注释,/* */任意位置注释。

一个程序中可以有多个模块,处于最上方的叫顶模块,下面的叫子模块,子模块需要顶模块来实现整体功能。

且,模块可嵌套。

(类似于matlab)。

模块需要有模块名,接口,接口I/O说明,内部信号声明(这里好像未体现),功能定义等。

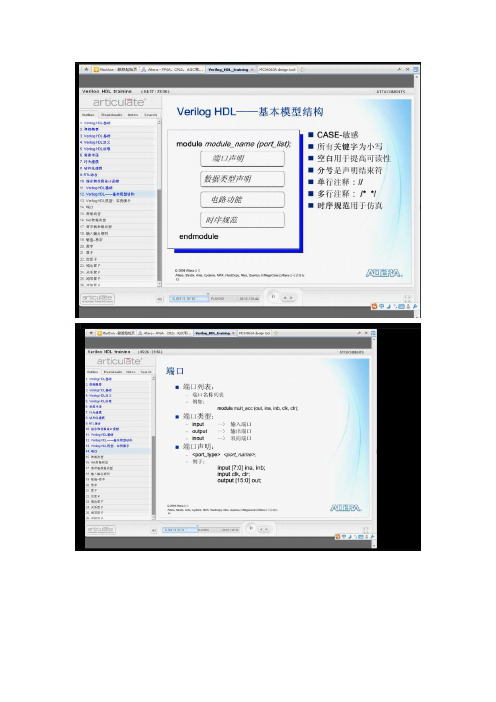

1.模块声明格式如下:module 模块名(口一,口二,…,端口N);2. I/O说明格式如下:input 端口名一,端口名二,……,端口名N;output 端口名一,端口名二,……,端口名N;也可以把I/O说明写到模块声明里,比如上面的模块的声明与I/O声明可改为:module (input a,input b,output c,output d) ;3.逻辑功能定义有以下三种方法:1.用assign 定义。

这种很简单:如例中的:assign c=a|b;2.用实例元件(我的理解,就相当于用一个C语言里的库函数)如:and and_inst(q,a,b)用法是键入元件的名字和相连的引脚即可。

3.用always块用always块可以实现一些复杂的逻辑,比如用if-else语句等。

(暂不太懂,将来再说)下面一段先抄上来,慢慢理解:注意:如果有Verilog模块实现一定的功能,首先应该清楚哪些是同时发生的,哪些是顺序发生的。

上面3个例子分别彩了“assign“语句、实例元件和“always”块。

verilog传奇读书笔记《Verilog传奇》是一本关于Verilog硬件描述语言的书籍,作者通过讲述自己的学习经历和实践经验,向读者展示了Verilog的魅力和实用性。

在阅读这本书的过程中,我深刻地认识到了Verilog在数字电路设计中的重要性,以及如何更好地学习和掌握这门技能。

作者通过对Verilog的发展历程的介绍,让我对这个领域有了更深入的了解。

从最初的简单电路设计,到现在的复杂数字系统,Verilog已经成为了硬件设计领域不可或缺的工具。

同时,随着技术的发展,Verilog 也在不断地更新和完善,为我们提供了更多的功能和便利。

作者通过讲解Verilog的基本语法和编程技巧,使我对这门语言有了更加清晰的认识。

在学习Verilog的过程中,我发现它与C语言有很多相似之处,但也有很多独特的地方。

例如,Verilog中的模块、端口、信号等概念,以及时序控制、并行处理等特性,都使得它在硬件设计中具有更高的效率和灵活性。

此外,作者还通过大量的实例和案例分析,让我对Verilog的应用有了更加直观的认识。

这些实例涵盖了数字逻辑、微处理器、存储器等多个方面,让我看到了Verilog在实际工程中的广泛应用。

同时,这些实例也让我明白了学习Verilog不仅要掌握基本语法,还要学会如何将理论知识应用到实际问题中去。

作者还分享了自己的学习方法和心得,给我带来了很多启示。

他提倡通过动手实践来学习Verilog,认为这是提高技能的最有效途径。

同时,他还强调了学习过程中的耐心和毅力,认为只有不断地努力和积累,才能真正掌握这门技能。

《Verilog传奇》这本书让我对Verilog有了更加全面和深入的了解,也激发了我学习这门技能的兴趣和动力。

在今后的学习和工作中,我将努力学习Verilog,将其运用到实际项目中去,为自己的职业发展打下坚实的基础。

先记下来:1、不使用初始化语句;2、不使用延时语句;3、不使用循环次数不确定的语句,如:forever,while 等;4、尽量采用同步方式设计电路;5、尽量采用行为语句完成设计;6、always 过程块描述组合逻辑,应在敏感信号表中列出所有的输入信号;7、所有的内部寄存器都应该可以被复位;8、用户自定义原件(UDP 元件)是不能被综合的。

一:基本Verilog 中的变量有线网类型和寄存器类型。

线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器,还有可能被优化掉。

二:verilog 语句结构到门级的映射1、连续性赋值:assign连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。

因此连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。

Assign 语句中的延时综合时都将忽视。

2、过程性赋值:过程性赋值只出现在always 语句中。

阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。

建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。

过程性赋值的赋值对象有可能综合成wire, latch,和flip-flop,取决于具体状况。

如,时钟控制下的非阻塞赋值综合成flip-flop。

过程性赋值语句中的任何延时在综合时都将忽略。

建议同一个变量单一地使用阻塞或者非阻塞赋值。

3、逻辑操作符:逻辑操作符对应于硬件中已有的逻辑门,一些操作符不能被综合:===、!==。

4、算术操作符:Verilog 中将reg 视为无符号数,而integer 视为有符号数。

因此,进行有符号操作时使用integer,使用无符号操作时使用reg。

5、进位:通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。

如:Wire [3:0] A,B;Wire [4:0] C;Assign C=A+B;C 的最高位用来存放进位。

6、关系运算符:关系运算符:<,>,<=,>=和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg,net 还是integer。

Verilog学习笔记作者:桂。

时间:2017-06-24 11:07:40前⾔Verilog是硬件描述语⾔,不算FPGA的核⼼部分,以前没有接触过,找了本书翻看⼀下(《Verilog数字系统设计教程第三版》),顺便记录⼀些基础知识,从第三章开始。

第三章:模块结构、基本数据类型、基本运算符 A-模块的结构0、模块基本定义⼀个基本的模块就是:module name(in1,in2,...out1,out2,...)//内部逻辑endmodulw模块基本定义涉及两个要点:1)其他模块作为input的调⽤;2)I/O位宽的设定。

1、always⽤法情形⼀:有 always @(a or b) beginif(a) q<=b;else q<=0;end这个块是每当 a b发⽣变化时执⾏还是a或者b中有⼀个是1或2个都是1时执⾏?答:每当A,B变化时,这个块就执⾏。

ALWAYS后⾯的叫敏感参数列表,不表⽰信号值,⽽是信号变化触发这个块的执⾏。

⼀般的,如果ALWAYS块的敏感参数列表没有带时钟,这个块将被综合成⼀个组合回路。

参照组合回路的真值表。

当输⼊端任何⼀个信号变化时,输出将⽴即做相应的变化。

如果ALWAYS后代的是时钟,那ALWAYS块将被综合成⼀个时序回路。

⼀般情况下,当时钟变化时,ALWAYS块执⾏。

情形⼆:always @(a) begin如果这个a被定义为⼀个reg [4:0]时程序怎么判断执⾏?答:如果综合逻辑没有问题,就是a的每⼀个元素变化时,这个块都要执⾏。

2、assign、wire、always则块的描述语⾔为:module muxtwo(out,a,b,s1)input a,b,s1;//输⼊信号output out;//输出wire ns1,sela,selb; //定义内部连接线assign ns1 = ~s1;assign sela = a&ns1;assign selb = b&s1;assign out = sela|selb;endmodule 其中assign声明语句。

可综合的verilog 语法子集

常用的 RTL 语法结构如下:

模块声明: module…endmodule。

端口声明:input,output,inout(inout 的用法比较特殊,需要注意)。

信号类型:wire,reg,tri 等,integer 常用语for 语句中(reg,wire

是最常用的,一般tri 和integer 用在测试脚本里)。

参数定义:parameter定义参数,只在文件中有效,define。

在整个

运算操作符:各种逻辑操作符、移位操作符、算术操作符大多时可综合

的(注:===与!==是不可综合的)。

比较判断:if…else,case(casex,casez)…default…endcase。

连续赋值:assign,问号表达式(?:)。

always 模块:(敏感表可以为电平、沿信号posedge/negedge;通常和

@连用)。

begin…end(通俗的说,它就是 C 语言里的“{ }”)。

任务定义:task…endtask。

循环语句:for(用的也比较少,但是在一些特定的设计中使用它会起

到事半功倍的效果)。

赋值符号:= 和 <= (阻塞和非阻塞赋值,在具体设计中时很有讲究的)。

verilog HDL学习笔记(基本概念)1. 作为一种硬件描述语言,verilog可以直接描述硬件结构,也可以通过描述系统行为实现建模,其主要特点和功能有:*描述基本逻辑门和基本开关模型。

* 允许用户定义基元。

* 可以指定设计中的端口到端口的延时,路径时延和设计中的时序检查。

*可以采用多种方式进行建模,这些方式包括(1)顺序行为描述建模——使用过程化结构建模,(2)数据流行为方式——使用连续赋值语句方式建模,(3)结构化方式——使用门和模块实例语句描述建模。

* Verilog中有两类数据类型,线网数据类型和寄存器数据类型。

线网数据类型表示构件间的连线,而寄存器类型表示抽象的数据存储元件。

* 能描述层次设计,可使用模块实例结构描述任何层次。

*不仅能在RTL上进行设计描述,而且能在体系结构级和算法级行为上进行描述。

*可以对并发行为和定时行为进行建模。

2. 模块module是verilog HDL最基本的组成单元,模块的实际意义是代表硬件电路上的逻辑实体(实现特定逻辑功能的一组电路),其范围可以从门到很大的系统。

模块的描述方式有行为建模和结构建模,模块之间并行运行。

模块分层,各模块连接完成整个系统需要用一个顶层模块。

每个系统无论多么复杂,总能划分成多个小的功能模块,按下步骤:(1)把系统划分层模块。

(2)规划各模块的接口。

(3)对模块编程并连接各模块完成系统设计。

Verilog HDL通过模块调用(模块实例化)来实现子模块与高层模块的连接。

模块实例化是通过结构建模的方法来完成的,verilog HDL中的子模块的调用确切的说是“嵌入”,这种引用会把子模块电路完全放在高层模块中。

3. verilog HDL区分大小写。

4. 用parameter来声明参数。

5. 常用预处理指令:…define…undef…ifdef…else…endef…include…timescale6. 线网数据类型:表示元件之间的物理连线,它不能存储数据,线网是被驱动的,可以用连续赋值语句或把元件的输出连接到线网等方式给线网提供驱动,给线网提供驱动的赋值和元件就是驱动源。

Verilog学习笔记1.Verilog模块声明内不能再包含模块声明。

2.Verilog有三种操作符: 单元,双元和三元。

优先级单元>双元>三元3.数字表示<size>’<base format><number>,不指明基数,默认为十进制。

不指明位宽,则为默认位宽,和计算机有关。

4.4种电平逻辑: x, z, 0, 1,8种信号强度。

并不是关键字, 其包括: wire, wand, wor, tri, triand, trior, trireg。

6.reg类型不需要驱动源,不赋值它的值就不变。

他和硬件寄存器并不是一个概念。

7.系统任务$<keyword>, 如:a)$display(类似printf)b)$monitor. 只用调用一次,监视的变量有变化,就会被调用。

($monitoron,$monitoroff)c)$stop. 暂停仿真d)$finish. 结束仿真8.编译指令。

`include, `define, 类似于#9.Parameter相当于常量定义?10.assign并行赋值语句,也可以叫连续赋值语句。

可以采用信号声明时初始化的隐形方式。

assign #xxx 延迟赋值。

11.verilog有缩减操作符&,|,^, ~|, ~^12.拼接操作符{ }, 重复操作符,如4{A}13.Verilog常规延时和内延时的区别: 常规延时整体赋值语句延时,而内延时是右侧先算好,到了时间后再赋值。

14.Verilog里有event类型,不知道搞什么鬼。

15.@(*)对所有输入变量敏感。

16.Verilog里有个repeat循环,循环固定次数,和labview里for terminal比较像。

17.begin和end组成顺序块,fork和join组成并行块。

18.模块生成用generate/endgenerate来实现,分为循环生成,条件生成和case生成19.任务采用task/endtask, 加automatic为可重入任务。

1.阻塞问题经典例子:1.非阻塞式:always(posdege@clk)beginb<=a;c<=b;end 2.阻塞式:always(posdege@clk)beginb=a;c=b;end注:非阻塞式语句时,只在块完成后才给被赋值对象赋值;阻塞式语句时,按程序先后给对象赋值,阻塞式结果赋值先后与顺序是有关系的。

两个程序的输出结果是不一样的,如下图示2.常量定义两种方式:1)'define a 3'b0112)parameter a=3'b011;3.case casex casez4.模块中的进程(process)1)Assign2)Always3)Initial4)元件例化5.task和funtion1)task <task名>无端口列表2)调用task时,格式为task名(参数),其中注意参数的相对位置应该与task定义时对应。

例如下例:3)task是定义在模块内部的,不能像C函数哪样可以放在主函数外。

4)函数的格式 function <返回参数类型及位数>函数名5)隐含了一个与函数同名的参数6)两者的区别:Verilog学习笔记21.顺序执行与并发执行1)块间always,assign,元件实例化都是并行执行的;2)Always块内部(=)阻塞语句是顺序执行的,(=>)非阻塞是并发执行的;2.Verilog-1995与Verilog-2001的区别1)信号类型和方向可一起定义;2)敏感信号可以用“,”来代替“or”;3)敏感信号全体信号的变化可以用“*”来替代。

其它不再细说了。

3.Verilog HDL的描述风格1)结构描述,行为描述,数据流描述。

2)Verilog的抽像层次3)缓冲器,非门和三态缓冲门的真傎表4.结构描述从低层下手,从硬件上来分析,一般有开关级和门级两种5.行为描述大多用always语句来反映输入与输出的关系,即用语言来描述:什么样的输入对应有什么样的输出:6.数据流描述是采用找出能够反映输入输出的公式,通常用assign来赋值。

模块(module):模块名称,端口列表,端口类型列表,内部变量定义一级逻辑功能描述输入端口:input 输出端口:output 双向端口:inout例子,全加器Module myadder(a,b,Carry_in,Sum,Carry_out);//端口类型列表Input a,b,carry-in;Output sun,carry_out;Wire a,b,carry-in;Wire sum,carry-out;//逻辑功能描述Assign{carry_out,sum}=a+b+carry_in;Endmodule逻辑功能描述的三种方法Always assign 创建模块实例Assign :用与输入信号与输出信号建立某种联系的情况下,这种联系可以用逻辑表达式或者算数表达式描述。

此外assign只能用来描述组合逻辑电路,不能用于描述时序逻辑电路。

Always:用于描述比较复杂的组合逻辑以及时序逻辑电路。

事件控制:电平触发和边沿触发。

电平触发是当某个信号的电平发生变化是,执行always指定的内容;边沿触发是指信号的上升沿或者下降沿到来时,执行always指定内容(always @ XXX)Posedge 上升沿,negedge 下降沿。

多个触发事件,任一执行(or或者用','代替)//"*"可以代替电平敏感列表的内容,表示将所有输入信号都加入敏感列表“#”为延时信号,后面跟数字表示延时多少基本周期,基本周期是电路仿真的时间单位。

延时程序'timescale 100ns/100ns //定义仿真的基本单位是100nsModule always_delay(Clkout;);Output clkout;Reg clkout;InitialClkout=0; //将输出时钟信号赋初值0//每过100ns时钟信号翻转一次Always #1 clkout=-clkout;Endmodule块语句1 begin...end 其之间可以添加多条语句,这些语句按照出现的顺序执行。

00000000000000000000000000000000000000000000000000000000000000000000000000 ** 功能描述:实现数码管静态显示0~Fmodule led_display(sm_seg,sm_bit,clk,);input clk;output [7:0] sm_seg; //output [7:0] sm_bit; //reg [7:0] sm_seg;reg [7:0] sm_bit;reg [3:0] disp_dat;reg [36:0] count;always @ (posedge clk )begincount = count + 1'b1;sm_bit = 8'b00000000;endalways @ (count[24])begindisp_dat = {count[28:25]};endalways @ (disp_dat)begincase (disp_dat)4'h0 : sm_seg = 8'hc0; // "0"4'h1 : sm_seg = 8'hf9; // "1"4'h2 : sm_seg = 8'ha4; // "2"4'h3 : sm_seg = 8'hb0; // "3"4'h4 : sm_seg = 8'h99; // "4"4'h5 : sm_seg = 8'h92; // "5"4'h6 : sm_seg = 8'h82; // "6"4'h7 : sm_seg = 8'hf8; // "7"4'h8 : sm_seg = 8'h80; // "8"4'h9 : sm_seg = 8'h90; // "9"4'ha : sm_seg = 8'h88; // "a"4'hb : sm_seg = 8'h83; // "b"4'hc : sm_seg = 8'hc6; // "c"4'hd : sm_seg = 8'ha1; // "d"4'he : sm_seg = 8'h86; // "e"4'hf : sm_seg = 8'h8e; // "f"endcaseendendmodule111111111111111111111111111111111111111111111111111111111111111111111 ** 功能描述:实现数码管动态显示0~7module scan_led(clk,rst,sm_seg,sm_bit);input clk,rst;output[7:0] sm_seg;output[7:0] sm_bit;reg[7:0] sm_seg;reg[7:0] sm_bit;reg[15:0] cnt_scan;reg[4:0] dataout_buf;always@(posedge clk or negedge rst)beginif(!rst) begincnt_scan<=0;endelse begincnt_scan<=cnt_scan+1'b1;endendalways @(cnt_scan)begincase(cnt_scan[15:13])3'b000 :sm_bit = 8'b1111_1110;3'b001 :sm_bit = 8'b1111_1101;3'b010 :sm_bit = 8'b1111_1011;3'b011 :sm_bit = 8'b1111_0111;3'b100 :sm_bit = 8'b1110_1111;3'b101 :sm_bit = 8'b1101_1111;3'b110 :sm_bit = 8'b1011_1111;3'b111 :sm_bit = 8'b0111_1111;default :sm_bit = 8'b1111_1110;endcaseendalways@(sm_bit)begincase(sm_bit)8'b1111_1110:dataout_buf=0;8'b1111_1101:dataout_buf=1;8'b1111_1011:dataout_buf=2;8'b1111_0111:dataout_buf=3;8'b1110_1111:dataout_buf=4;8'b1101_1111:dataout_buf=5;8'b1011_1111:dataout_buf=6;8'b0111_1111:dataout_buf=7;default:dataout_buf=8;endcaseendalways@(dataout_buf)begincase(dataout_buf)4'h0 : sm_seg = 8'hc0; // "0"4'h1 : sm_seg = 8'hf9; // "1"4'h2 : sm_seg = 8'ha4; // "2"4'h3 : sm_seg = 8'hb0; // "3"4'h4 : sm_seg = 8'h99; // "4"4'h5 : sm_seg = 8'h92; // "5"4'h6 : sm_seg = 8'h82; // "6"4'h7 : sm_seg = 8'hf8; // "7"4'h8 : sm_seg = 8'h80; // "8"4'h9 : sm_seg = 8'h90; // "9"4'ha : sm_seg = 8'h88; // "a"4'hb : sm_seg = 8'h83; // "b"4'hc : sm_seg = 8'hc6; // "c"4'hd : sm_seg = 8'ha1; // "d"4'he : sm_seg = 8'h86; // "e"4'hf : sm_seg = 8'h8e; // "f"endcaseend endmodule (换22222222222222222222222222222222222222222222222222222222222222222222 ** 功能描述:实现蜂鸣器输出救护车鸣笛声module jiuhuche(clk, beep);input clk;output beep;reg beep;reg [14:0] counter;reg [23:0] tone;parameter clkdivider = 50000000/440/2;always @(posedge clk)begintone <= tone+1'b1;endalways @(posedge clk)beginif(counter==0)counter <= (tone[23] ? clkdivider-1 : clkdivider/2-1);else counter <= counter-1;endalways @(posedge clk)beginif(counter==0)beep <= ~beep;endendmodule3333333333333333333333333333333333333aaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa ** 功能描述:实现蜂鸣器输出警车鸣笛声module beep(clk, beep);input clk;output beep;reg beep;reg [22:0] tone;reg [14:0] counter;always @(posedge clk)begintone <= tone+1;endwire [6:0] ramp = (tone[22] ? tone[21:15] : ~tone[21:15]);wire [14:0] clkdivider = {2'b01, ramp, 6'b000000};always @(posedge clk) if(counter==0) counter <= clkdivider;else counter <= counter-1;always @(posedge clk)beginif(counter==0)beep <= ~beep;endendmodule33333333333333333333333333333333333bbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb** 功能描述:实现蜂鸣器输出警车鸣笛声module beep(clk, beep);input clk;output beep;reg beep;reg [27:0] tone;reg [14:0] counter;always @(posedge clk)begintone <= tone+1;endwire [6:0] fastsweep = (tone[22] ? tone[21:15] : ~tone[21:15]);wire [6:0] slowsweep = (tone[25] ? tone[24:18] : ~tone[24:18]);wire [14:0] clkdivider = {2'b01, (tone[27] ? slowsweep : fastsweep), 6'b000000};always @(posedge clk)beginif(counter==0) counter <= clkdivider;else counter <= counter-1;endalways @(posedge clk)beginif(counter==0)beep <= ~beep;endendmodule444444444444444444444444444444444444444444444444444444444444444444444444 ** 功能描述:实现硬件电子琴功能module key_music(clk,key,buzzout,led);//模块名称key_musicinput clk; //系统时钟50 MHZinput[7:0]key; //按键输入output buzzout; //蜂鸣器输出output[7:0] led;reg buzzout_reg;reg[7:0]key_reg;reg[22:0]counter,count_end; //定义寄存器reg key_flg;initial key_flg = 1'b0;always@(posedge clk)begincounter = counter + 1;//计数器加1if(counter==count_end)begincounter = 0; //计数器清零if(key_flg==1'b1)buzzout_reg = ~buzzout_reg;else buzzout_reg = 1'b0;endendalways@(counter[10:9])beginkey_reg = key;if(key_reg!=8'hff)key_flg = 1'b1;else key_flg = 1'b0;case(key_reg)8'b11111110: count_end=20'd47774; //中音1的分频系数值8'b11111101: count_end=20'd42568; //中音2的分频系数值8'b11111011: count_end=20'd37919; //中音3的分频系数值8'b11110111: count_end=20'd35791; //中音4的分频系数值8'b11101111: count_end=20'd31888; //中音5的分频系数值8'b11011111: count_end=20'd28409; //中音6的分频系数值8'b10111111: count_end=20'd25309; //中音7的分频系数值8'b01111111: count_end=20'd23912; //高音1的分频系数值8'b01111110: count_end=20'd21282; //高音2的分频系数值8'b01111101: count_end=20'd18961; //高音3的分频系数值8'b01111011: count_end=20'h17897; //高音4的分频系数值8'b01110111: count_end=20'd15944; //高音5的分频系数值8'b01011111: count_end=20'd14205; //高音6的分频系数值8'b00111111: count_end=20'd12655; //高音7的分频系数值default: count_end=20'hfffff;endcaseendassign buzzout = buzzout_reg;assign led = ~key_reg;//输出按键状态endmodule555555555555555555555555555555555555555555555555555555555555** 功能描述:实现梁祝乐曲的自动演奏//《梁祝》乐曲时钟:50MHz ////音高与频率的对应关系//---------------------------------------------------------------------- //| | 1 | 2 | 3 | 4 | 5 | 6 | 7 |//|低音 |261.6Hz |293.7Hz |329.6Hz |349.2Hz | 392Hz | 440Hz |493.9Hz | //|中音 |523.3Hz |587.3Hz |659.3Hz |698.5Hz | 784Hz | 880Hz |987.8Hz | //|高音 |1045.5Hz|1174.7Hz|1318.5Hz|1396.9Hz| 1568Hz | 1760Hz |1975.5Hz| //---------------------------------------------------------------------- module song(clk,beep); //模块名称songinput clk; //系统时钟50MHzoutput beep; //蜂鸣器输出端reg beep_r; //寄存器reg[7:0] state; //乐谱状态机reg[15:0]count,count_end;reg[23:0]count1;//乐谱参数:D=F/2K (D:参数,F:时钟频率,K:音高频率)parameter L_3 = 16'd75850, //低音3L_5 = 16'd63776, //低音5L_6 = 16'd56818, //低音6L_7 = 16'd50618, //低音7M_1 = 16'd47774, //中音1M_2 = 16'd42568, //中音2M_3 = 16'd37919, //中音3M_5 = 16'd31888, //中音5M_6 = 16'd28409, //中音6H_1 = 16'd23912; //高音1parameter TIME = 12000000; //控制每一个音的长短(250ms)assign beep = beep_r; //输出音乐always@(posedge clk)begincount <= count + 1'b1; //计数器加1if(count == count_end)begincount <= 16'h0; //计数器清零beep_r <= !beep_r; //输出取反endendalways @(posedge clk)beginif(count1 < TIME) //一个节拍250mScount1 = count1 + 1'b1;elsebegincount1 = 24'd0;if(state == 8'd66)state = 8'd0;elsestate = state + 1'b1;case(state)8'd0,8'd1,8'd2,8'd3: count_end = L_3;//低音"3",持续4个节拍8'd4,8'd5,8'd6: count_end = L_5;//低音"5",持续3个节拍8'd7: count_end = L_6;//低音"6",持续1个节拍8'd8,8'd9,8'd10: count_end = M_1;//中音"1",持续3个节拍8'd11: count_end = M_2;//中音"2",持续1个节拍8'd12: count_end = L_6;//低音"6",持续1个节拍8'd13: count_end = M_1;//中音"1",持续1个节拍8'd14,8'd15: count_end = L_5;//低音"5",持续2个节拍8'd16: count_end = M_1;//中音"1",持续1个节拍8'd17,8'd18: count_end = L_5;//低音"5",持续2个节拍8'd19,8'd20,8'd21: count_end = M_5;//中音"5",持续3个节拍8'd22: count_end = H_1;//高音"1",持续1个节拍8'd23: count_end = M_6;//中音"6",持续1个节拍8'd24: count_end = M_5;//中音"5",持续1个节拍8'd25: count_end = M_3;//中音"3",持续1个节拍8'd26: count_end = M_5;//中音"5",持续1个节拍8'd27,8'd28,8'd29,8'd30,8'd31,8'd32,8'd33,8'd34,8'd35,8'd36,8'd37:count_end = M_2;//中音"2",持续11个节拍8'd38: count_end = M_3;//中音"3",持续1个节拍8'd39,8'd40: count_end = L_7;//低音"7",持续2个节拍8'd41,8'd42: count_end = L_6;//低音"6",持续2个节拍8'd43,8'd44,8'd45: c ount_end = L_5;//低音"5",持续3个节拍8'd46: count_end = L_6;//低音"6",持续1个节拍8'd47,8'd48: count_end = M_1;//中音"1",持续2个节拍8'd49,8'd50: count_end = M_2;//中音"2",持续2个节拍8'd51,8'd52: count_end = L_3;//低音"3",持续2个节拍8'd53,8'd54,8'd55: c ount_end = M_1;//中音"1",持续3个节拍8'd56,8'd57: count_end = L_5;//低音"5",持续2个节拍8'd58: count_end = M_1;//中音"1",持续1个节拍8'd59,8'd60,8'd61,8'd62,8'd63,8'd64,8'd65,8'd66: c ount_end = L_5;//低音"5",持续8个节拍endcaseendendendmodule6666666666666666666666666666666666666666666666666666666666666666666 ** 功能描述:实现液晶1602显示welcome to module lcd1602(clk,rst,data,lcd_e,lcd_rs,lcd_rw);input clk;input rst;output [7:0] data;output lcd_e;output lcd_rs;output lcd_rw;wire XLXN_1;div16 XLXI_1 (.clk(clk),.rst(rst),.clk_16(XLXN_1));lcd XLXI_2 (.clk(XLXN_1),.rst(rst),.data(data[7:0]),.lcd_e(lcd_e),.lcd_rs(lcd_rs),.lcd_rw(lcd_rw));endmodule777777777777777777777777777777777777777777777777777777777777777777 // Copyright (c) 1995-2003 Xilinx, Inc.** 功能描述:实现LCD1602显示PS/2键盘的键值`timescale 1ns / 1psmodule top(clk,rst,data,lcd_e,lcd_rs,lcd_rw,led,ps2ck,ps2dk);input clk;input rst;output [7:0] data;output lcd_e;output lcd_rs;output lcd_rw;output [7:0] led;inout ps2ck;inout ps2dk;wire XLXN_4;wire XLXN_5;wire XLXN_6;div_256 XLXI_1 (.mclk(clk),.reset(rst),.clk(XLXN_6));div16 XLXI_2 (.clk(clk),.rst(rst),.clk_16(XLXN_5));lcd XLXI_3 (.clk(XLXN_5),.data_in(led[7:0]),.rst(XLXN_4),.data(data[7:0]),.lcd_e(lcd_e),.lcd_rs(lcd_rs),.lcd_rw(lcd_rw));ps2_keyboard_interface XLXI_4 (.clk(XLXN_6),.reset(rst),.rx_read(),.tx_data(),.tx_write(),.rx_ascii(led[7:0]),.rx_data_ready(),.rx_extended(),.rx_released(XLXN_4),.rx_scan_code(),.rx_shift_key_on(),.tx_error_no_keyboard_ack(), .tx_write_ack_o(),.ps2_clk(ps2ck),.ps2_data(ps2dk)); endmodule888888888888888888888888888888888888888888888888888888888888** 功能描述:实现VGA彩色信号显示module VGA(clock,switch,disp_RGB,hsync,vsync);input clock; //系统输入时钟 50MHzinput [1:0]switch;output [2:0]disp_RGB; //VGA数据输出output hsync; //VGA行同步信号output vsync; //VGA场同步信号reg [9:0] hcount; //VGA行扫描计数器reg [9:0] vcount; //VGA场扫描计数器reg [2:0] data;reg [2:0] h_dat;reg [2:0] v_dat;//reg [9:0] timer;reg flag;wire hcount_ov;wire vcount_ov;wire dat_act;wire hsync;wire vsync;reg vga_clk;//VGA行、场扫描时序参数表parameter hsync_end = 10'd95,hdat_begin = 10'd143,hdat_end = 10'd783,hpixel_end = 10'd799,vsync_end = 10'd1,vdat_begin = 10'd34,vdat_end = 10'd514,vline_end = 10'd524;always @(posedge clock)beginvga_clk = ~vga_clk;end//************************VGA驱动部分******************************* //行扫描always @(posedge vga_clk)beginif (hcount_ov)hcount <= 10'd0;elsehcount <= hcount + 10'd1;endassign hcount_ov = (hcount == hpixel_end);//场扫描always @(posedge vga_clk)beginif (hcount_ov)beginif (vcount_ov)vcount <= 10'd0;elsevcount <= vcount + 10'd1;endendassign vcount_ov = (vcount == vline_end);//数据、同步信号输assign dat_act = ((hcount >= hdat_begin) && (hcount < hdat_end))&& ((vcount >= vdat_begin) && (vcount < vdat_end));assign hsync = (hcount > hsync_end);assign vsync = (vcount > vsync_end);assign disp_RGB = (dat_act) ? data : 3'h00;//************************显示数据处理部分******************************* //图片显示延时计数器/ *always @(posedge vga_clk)beginflag <= vcount_ov;if(vcount_ov && ~flag)timer <= timer + 1'b1;end */always @(posedge vga_clk)begincase(switch[1:0])2'd0: data <= h_dat; //选择横彩条2'd1: data <= v_dat; //选择竖彩条2'd2: data <= (v_dat ^ h_dat); //产生棋盘格 2'd3: data <= (v_dat ~^ h_dat); //产生棋盘格 endcaseendalways @(posedge vga_clk) //产生竖彩条beginif(hcount < 223)v_dat <= 3'h7; //白else if(hcount < 303)v_dat <= 3'h6; //黄else if(hcount < 383)v_dat <= 3'h5; //青else if(hcount < 463)v_dat <= 3'h4; //绿else if(hcount < 543)v_dat <= 3'h3; //紫else if(hcount < 623)v_dat <= 3'h2; //红else if(hcount < 703)v_dat <= 3'h1; //蓝elsev_dat <= 3'h0; //黑endalways @(posedge vga_clk) //产生横彩条beginif(vcount < 94)h_dat <= 3'h7; //白else if(vcount < 154)h_dat <= 3'h6; //黄else if(vcount < 214)h_dat <= 3'h5; //青else if(vcount < 274)h_dat <= 3'h4; //绿else if(vcount < 334) h_dat <= 3'h3; //紫 else if(vcount < 394) h_dat <= 3'h2; //红 else if(vcount < 454) h_dat <= 3'h1; //蓝 elseh_dat <= 3'h0; //黑endendmodule。