FPGA夏宇闻Verilog学习笔记1

- 格式:doc

- 大小:645.50 KB

- 文档页数:13

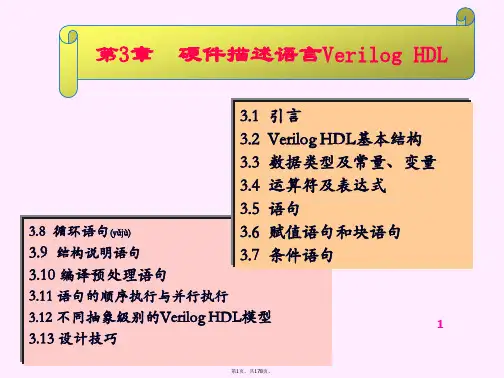

标签: FPGA 初学经典书籍FPGA初学推荐书籍Verilog数字系统设计教程夏宇闻这本书着重讲的是Verilog的语法,有综合语法还有仿真的语法。

看的时候可以只看前七章,后面是应用的例子。

EDA实验与实践周立功周立功写的书对初学者来说很好用,写的很详细,注释也很清晰,非常适合入门。

本书中不仅有可综合的代码,还有quartus 软件的常用功能的讲解。

跟随本书,将实验一个一个的做下去,对FPGA的开发流程就基本了解了。

设计与验证Verilog HDL 吴继华王诚本书是有FPGA开发经验的人写的,关于代码规范性的一本书,里面是FPGA高手的经验总结,对提高写verilog 代码的水平很有帮助。

Verilog HDL应用程序设计实例精讲(含光盘1张)刘福奇刘波这是他们推荐的一本书,我没看过,里面的例程据说讲的很好,可以作为参考代码数字信号处理的FPGA实现(第2版)刘凌译本书详细讲解了FPGA中常用的DSP算法,有详细的代码,可以直接用。

如果想用FPGA做数字信号处理,这本书不错。

无线通信FPGA设计田耘本书和上面一本书,都是非常经典的了。

再推荐两本老外的高级FPGA设计结构、实现也优化(美)马克斯菲尔德(Maxfiel,C.)FPGA设计指南器件、工具和流程(美)马克斯菲尔德(Maxfiel,C.)书名: Xilinx FPGA开发实用教程作者:田耘徐文波出版社:清华大学出版社日期: 2010-3-27 9:51:33价格: 59元详细介绍2007年10月份,作者有幸聆听了Xilinx公司全球CTO Ivo Bolsens先生在清华大学题为“FPGA: The future platform fortransforming, transporting and computing”的演讲,感触颇深。

Ivo先生指出了FPGA的三大应用领域:数字处理中的信号变换、高速交换中的数据收发以及求解中的复杂计算。

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

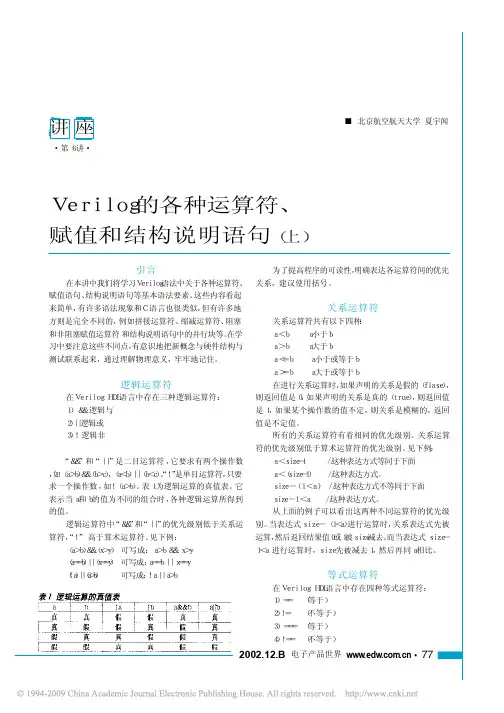

设计技术782002.12.B 电子产品世界这四个运算符都是二目运算符,它要求有两个操作数。

“==”和“!=”又称为逻辑等式运算符。

其结果由两个操作数的值决定。

由于操作数中某些位可能是不定值x和高阻值z,结果可能为不定值x。

而“===”和“!==”运算符则不同,它在对操作数进行比较时对某些位的不定值x和高阻值z也进行比较,两个操作数必需完全一致,其结果才是1,否则为0。

“===”和“!==”运算符常用于case表达式的判别,所以又称为“case等式运算符”。

这四个等式运算符的优先级别是相同的。

表1列出==与===的真值,帮助理解两者间的区别。

下面举一个例子说明“==”和“===”的区别。

例:if(A==1’bx) ¥display(“AisX”); (当A等于X时,这个语句不执行)if(A===1’bx) ¥display(“AisX”); (当A等于X时,这个语句执行)移位运算符在Verilog HDL中有两种移位运算符:<< (左移位运算符) 和 >>(右移位运算符)。

其使用方法如下: a >> n 或 a << na代表要进行移位的操作数,n代表要移几位。

这两种移位运算都用0来填补移出的空位。

下面举例说明:module shift;reg [3:0] start, result;initialbeginstart = 1;//start在初始时刻设为值0001result = (start<<2); //移位后,start的值0100,然后赋给result。

endendmodule从上面的例子可以看出,start在移过两位以后,用0来填补空出的位。

进行移位运算时应注意移位前后变量的位数,下面给出一例。

例:4’b1001<<1 = 5’b10010; 4’b1001<<2 = 6’b100100;1<<6 = 32’b 1000000; 4’b 1001>>1 = 4’b 0100;4’b 1001>>4 = 4’b 0000;位拼接运算符(Concatation)在Verilog HDL语言有一个特殊的运算符:位拼接运算符{}。

FPGA笔记之verilog语言(基础语法篇)笔记之verilog语言(基础语法篇)写在前面:verilogHDL语言是面对硬件的语言,换句话说,就是用语言的形式来描述硬件线路。

因此与等软件语言不同,假如想要在实际的中实现,那么在举行verilog语言编写时,就需要提前有个硬件电路的构思和主意,同时,在编写verilog语言时,应当采纳可综合的语句和结构。

1. verilog 的基础结构1.1 verilog设计的基本单元——module在数字电路中,我们经常把一些复杂的电路或者具有特定功能的电路封装起来作为一个模块用法。

以后在运用这种模块化的封装时,我们只需要知道:1.模块的输入是什么;2.模块的输出是什么;3.什么样的输入对应什么样的输出。

而中间输入是经过什么样的电路转化为输出就不是我们在用法时需要特殊重视的问题。

当无数个这样的模块互相组合,就能构成一个系统,解决一些复杂的问题。

verilog语言的基础结构就是基于这种思想。

verilog中最基本的模块是module,就可以看做是一个封装好的模块,我们用verilog来写无数个基本模块,然后再用verilog描述多个模块之间的接线方式等,将多个模块组合得到一个系统。

那么一个module应当具有哪些要素呢?首先对于一个module,我们应当设计好其各个I/O,以及每个I/O的性质,用于与模块外部的信号相联系,让用法者知道如何连线。

第二,作为开发者,我们需要自己设计模块内部的线路来实现所需要的功能。

因此需要对模块内部浮现的变量举行声明,同时通过语句、代码块等实现模块的功能。

综上所述,我们把一个module分成以下五个部分:模块名端口定义I/O解释第1页共9页。

Verilog学习心得因为Verilog是一种硬件描述语言,所以在写Verilog语言时,首先要有所要写的module在硬件上如何实现的概念,而不是去想编译器如何去解释这个module. 比如在决定是否使用reg定义时,要问问自己物理上是不是真正存在这个register, 如果是,它的clock是什么? D端是什么?Q端是什么?有没有清零和置位?同步还是异步?再比如上面讨论的三态输出问题,首先想到的应该是在register的输出后面加一个三态门,而不是如何才能让编译器知道要“赋值”给一个信号为三态。

同样,Verilog中没有“编译”的概念,而只有综合的概念。

写硬件描述语言的目的是为了综合,所以说要想写的好就要对综合器有很深的了解,这样写出来的代码才有效率。

曾经接触过motorola苏州设计中心的一位资深工程师,他忠告了一句:就是用verilog描述电路的时候,一定要清楚它实现的电路,很多人只顾学习verilog语言,而不熟悉它实现的电路,这是设计不出好的电路来的.一般写verilog code时,对整个硬件的结构应该是很清楚了,最好有详细的电路图画出,时序问题等都应该考虑清楚了。

可以看着图直接写code。

要知道,最初Verilog是为了实现仿真而发明的.不可综合的Verilog 语句也是很重要的.因为在实际设计电路时,除了要实现一个可综合的module外,你还要知道它的外围电路是怎样的,以及我的这个电路与这些外围电路能否协调工作.这些外围电路就可以用不可综合的语句来实现而不必管它是如何实现的.因为它们可能已经实际存在了,我仅是用它来模拟的.所以,在写verilog的时候应该要先明确我是用它来仿真的还是综合的.要是用来综合的话,就必须要严格地使用可综合的语句,而且不同的写法可能产生的电路会有很大差别,这时就要懂一些verilog综合方法的知识.就像前面说的,脑子里要有一个硬件的概念.特别是当综合报错时,就要想一想我这种写法能不能用硬件来实现,verilog毕竟还不是C,很多写法是不可实现的.要是这个module仅是用来仿真的,就要灵活得多了,这时你大可不必太在意硬件实现.只要满足它的语法,实现你要的功能就行了.有网友说关于#10 clk=~clk的问题,虽然这种语句是不可综合的,但是在做simulation和verification是常常用它在testbench中来产生一个clock信号。

fpga语法知识点总结一、Verilog语言Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统级设计。

在FPGA设计中,Verilog语言常常用于描述逻辑功能和时序控制。

Verilog语言包括模块、端口、信号声明、组合逻辑、时序逻辑、行为模拟等部分。

1. 模块:Verilog中的模块是一个最基本的组织单位,它类似于面向对象编程中的类。

每个模块都有自己的输入输出端口和内部逻辑实现。

在FPGA设计中,通常会设计多个模块来实现不同的功能,然后将这些模块连接起来,构成一个完整的系统。

2. 端口:在Verilog中,端口用于定义模块与外部环境的接口。

端口可以被定义为输入端口(input)、输出端口(output)、双向端口(inout)等,用于进行与外部信号的通信。

3. 信号声明:在Verilog中,信号用于传递逻辑信息。

信号可以是单个的位(bit)信号,也可以是多位(bus)信号。

在FPGA设计中,对信号的声明和使用是非常重要的,可以影响到设计的性能和资源占用。

4. 组合逻辑:组合逻辑是一种不含时钟的逻辑电路,其输出仅由输入决定。

在Verilog中,组合逻辑常常使用逻辑运算符和条件语句来描述。

5. 时序逻辑:时序逻辑是一种包含时钟信号的逻辑电路,其输出由时钟信号和输入信号共同决定。

在FPGA设计中,时序逻辑和时序约束非常重要,可以影响到设计的时序性能。

6. 行为模拟:行为模拟是一种用于验证设计功能和性能的技术。

在Verilog中,可以使用行为模拟语句来描述设计的行为,并进行仿真验证。

二、VHDL语言VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统级设计。

在FPGA设计中,VHDL语言和Verilog语言一样,用于描述逻辑功能和时序控制。

VHDL语言包括实体、端口、信号声明、组合逻辑、时序逻辑、行为模拟等部分。

1. 实体:在VHDL中,实体是描述一个硬件单元的基本描述。

Verilog语言是一种硬件描述语言(HDL),用于描述和设计数字电路。

它广泛应用于数字系统的建模、验证和综合,是数字电路设计领域中的重要工具之一。

在Verilog中,模块是最基本的组织单位,模块中包含了电路的功能和行为描述。

本文将介绍Verilog语言的基本语法和模块写法,以帮助读者更好地理解和应用Verilog语言。

一、Verilog基本语法1. 注释在Verilog中,使用双斜杠(//)进行单行注释,使用/* */进行多行注释。

注释可以提高代码的可读性,便于他人理解和维护。

2. 变量声明Verilog中的变量可以分为寄存器变量(reg)和线网(wire)两种类型。

寄存器变量用于存储状态信息,线网用于连接各个逻辑门的输入和输出。

3. 逻辑运算符和位运算符Verilog中包括逻辑运算符(与、或、非等)和位运算符(与、或、异或等),用于对信号进行逻辑和位级操作。

4. 控制语句Verilog支持if-else语句、case语句等控制语句,用于根据不同条件执行不同的操作。

5. 模拟时钟在Verilog中,时钟是电路中的重要部分,通常使用时钟信号来同步各个元件的动作。

时钟可以通过周期性方波信号来模拟,使用$period 函数可以定义时钟的周期。

6. 仿真指令Verilog提供了多种仿真指令,用于初始化信号、设置仿真时间、输出波形图等操作,有助于仿真和调试电路。

二、模块写法1. 模块定义在Verilog中,一个模块包含了一组功能相关的硬件描述,可以看作是一个小型电路的抽象。

模块通过module关键字进行定义,其中包括模块名、输入输出端口声明等信息。

```verilogmodule adder(input wire [3:0] a,input wire [3:0] b,output reg [4:0] c);// 模块内部逻辑描述endmodule```2. 端口声明模块的端口包括输入端口(input)和输出端口(output),可以通过wire和reg进行声明。

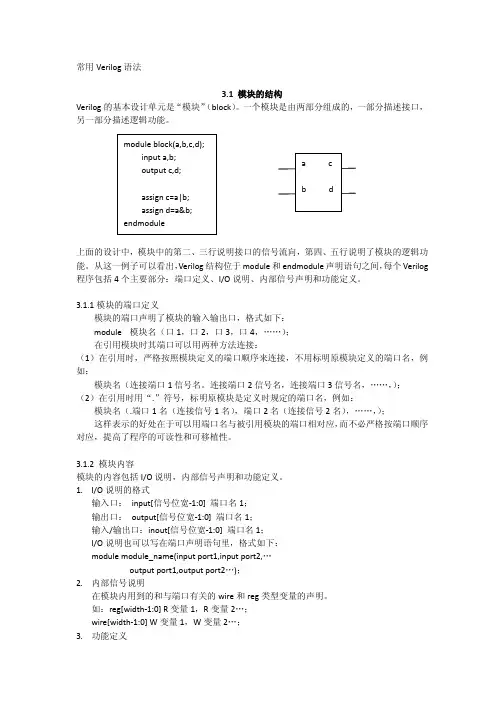

常用Verilog 语法3.1 模块的结构Verilog 的基本设计单元是“模块”(block )。

一个模块是由两部分组成的,一部分描述接口,另一部分描述逻辑功能。

上面的设计中,模块中的第二、三行说明接口的信号流向,第四、五行说明了模块的逻辑功能。

从这一例子可以看出,Verilog 结构位于module 和endmodule 声明语句之间,每个Verilog 程序包括4个主要部分:端口定义、I/O 说明、内部信号声明和功能定义。

3.1.1模块的端口定义模块的端口声明了模块的输入输出口,格式如下:module 模块名(口1,口2,口3,口4,……);在引用模块时其端口可以用两种方法连接:(1)在引用时,严格按照模块定义的端口顺序来连接,不用标明原模块定义的端口名,例如:模块名(连接端口1信号名。

连接端口2信号名,连接端口3信号名,……,);(2)在引用时用“.”符号,标明原模块是定义时规定的端口名,例如:模块名(.端口1名(连接信号1名),端口2名(连接信号2名),……,);这样表示的好处在于可以用端口名与被引用模块的端口相对应,而不必严格按端口顺序对应,提高了程序的可读性和可移植性。

3.1.2 模块内容模块的内容包括I/O 说明,内部信号声明和功能定义。

1. I/O 说明的格式输入口: input[信号位宽-1:0] 端口名1;输出口: output[信号位宽-1:0] 端口名1;输入/输出口:inout[信号位宽-1:0] 端口名1;I/O 说明也可以写在端口声明语句里,格式如下:module module_name(input port1,input port2,…output port1,output port2…);2. 内部信号说明在模块内用到的和与端口有关的wire 和reg 类型变量的声明。

如:reg[width-1:0] R 变量1,R 变量2…;wire[width-1:0] W 变量1,W 变量2…;3. 功能定义模块中最重要的部分是逻辑功能定义部分,有3种方法可在模块中产生逻辑。

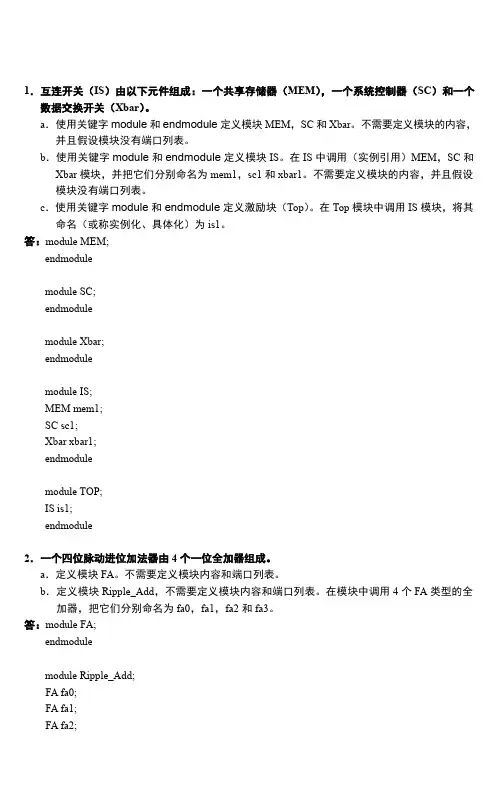

《Verilog数字系统设计教程》夏宇闻第四版思考题答案(第2章)1.Verilog语⾔有什么作⽤?可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型;Verilog HDL的构造性语句可以精确地建⽴信号的模型;2.构成模块的关键词是什么?module,endmodule。

3.为什么说可以⽤Verilog构成⾮常复杂的电路结构?因为Verilog可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型Verilog HDL的构造性语句可以精确地建⽴信号的模型;4.为什么可以⽤⽐较抽象的描述来设计具体的电路结构?因为有可以⽤⽐较抽象描述设计电路结构的语⾔,⽽这种语⾔是适合数字系统设计的语⾔。

5.是否任意抽象的符合语法的Verilog模块都可以通过综合⼯具转变为电路结构?不能。

《FPGA入门教程》看书随笔——RTL设计1、使用verilog进行RTL设计一般可归纳为3种基本的描述方式:(1)数据流描述:采用assign连续赋值语句(2)行为描述:使用always语句或initial语句块的过程赋值语句(3)结构化描述:实例化已有的功能模块或原语,即平常所说的元件例化和IP core.过程赋值语句包括非阻塞过程赋值、阻塞过程赋值和连续过程赋值。

2、RTL级设计时需注意的问题(1)凡是在always或initial语句中赋值的变量,一定是reg类型变量;凡是在assign语句中赋值的变量,一定是wire类型变量、(2)定义存储器:reg[3:0] MEMAORY[0:7];地址为0~7,每个存储单元都是4bit;(3)由于硬件是并行工作的,在Verilog语言的module中,所有描述语句(包括连续辅助语句assign、行为语句块always和initial 语句块以及模块实例化)都是并发执行的。

(4)使用完备的if...else语句,使用个条件完备的case语句并设置default操作。

以防止产生锁存器latch,因为锁存器对毛刺敏感(5)严禁设计组合逻辑反馈环路,它最容易引起振荡、毛刺、时序违规等问题。

(6)不要在两个或两个以上的语句块(always或initial)中对同一个信号赋值3、阻塞赋值与非阻塞赋值(1)阻塞赋值的操作符号为“=”。

它的含义是在计算等式右侧表达式值及完成其赋值时不会被其他的verilog 语句打断,就是说,在当前赋值没有完成之前,它阻塞了其他 verilog 语句的执行。

(2)非阻塞赋值的操作符为“<>在实际使用中,应该遵循的原则是:(1)在时序逻辑中,使用非阻塞赋值(2)在组合逻辑中,使用阻塞赋值(3)在同一个always块中,不要混合使用阻塞赋值和非阻塞赋值(4)在同一个always块中,如果既有组合逻辑又有时序逻辑,使用非阻塞赋值(5)always模块的敏感表为电平敏感信号时,使用阻塞赋值(6)不要使用#0时延进行赋值(7)不要在阻塞赋值中使用时延语句(8)在行为级描述中,如语句间是顺序执行的关系,使用阻塞赋值4、哪些是不可综合的代码(1)对于一些抽象的行为描述代码是不可综合的。

V erilog 数字系统设计教程 学习笔记

1

FPGA 学习

由于工作上的需要,现在又开始学习新的芯片,估计以后会在FPGA 和DSP 这两个方向有发展,以前学的ARM 现在可以待业休息了等待新的起点。

虽然大学的时候学习过《EDA 技术与VHDL 》这门课程,但是我至今才知道VHDL 语言是FPGA 的设计语言之一。

有一个好的指导老师是非常重要的,进入公司后由于实行的是导师制,指导我的导师就让我看《V erilog 数字系统设计教程》,学习一样东西有一本好书是非常重要的,就如同学习C 语言看谭浩强老师的教程,同样学习FPGA 看夏宇闻老师的书一样,确实学到了很多东西,而且会一直研读。

不管学习单片机,ARM ,DSP 还是FPGA 上机练习是非常重要的,所以在学习夏宇闻老师的教程时我就把书中的上机练习题自己练习一遍,并做简要的记录。

设计平台:Quartus II 11.1sp2 Web Edition 仿真平台:ModelSin10.0c Starter Editon

上机练习一 简单的组合逻辑设计

由于是第一个练习,我会将具体的软件使用过程都列出来,方便同我一样的学习者学习。

1、建立一个新的工程

弹出对话框,直接

Next

设置工程目录F:/FPGA V erilog test/lesson1,工程名compare,顶层设计模块名compare

如果你已经有一些要加入工程的文件,可以再该步将文件加入到工程中,没有则直接Next

这一步是选择你需要的设计芯片,由于我们只学习V erilog语言,所以芯片选择随意

V erilog 数字系统设计教程 学习笔记

3

选择仿真语言和综合工具

最后显示我们选择的信息,确认填写是否正确

2、一些参数的设置

设置未使用引脚属性,选择Device and Pin Options

V erilog 数字系统设计教程 学习笔记

5

设置为输入三态

3、这里我们可以编写测试程序

选择V erilog HDL File

编写测试程序

保存到工程目录下

V erilog 数字系统设计教程学习笔记

4、进行程序的编译和综合

编译结果

7

5、进行testbench的设计,运行

这样就在F:\FPGA V erilog test\lesson1\simulation\modelsim文件夹下生成一个compare.vt的文件,我们打开该文件,并进行内容修改

修改前

V erilog 数字系统设计教程学习笔记

全部覆盖,写入自己的测试代码

6、testbench的相关设置

9

编译testbench

设置Test Benches…

V erilog 数字系统设计教程学习笔记

新建

Ok,设置完成

7、进行仿真测试

11

直接启动ModelSim,得到仿真结果

放大

V erilog 数字系统设计教程学习笔记

由波形图可以知道,我们编写的比较器是正确的。

13。