论ASIC与FPGA之争

- 格式:pdf

- 大小:550.52 KB

- 文档页数:4

ASIC与CPU、GPU、FPGA区别?继4月初联发科宣布扩大ASIC产品阵线,推出业内首个7nm 56G PAM4 SerDes IP之后,4月24日,在联发科深圳办公室,联发科举行了一场小型的媒体会,联发科副总经理暨智能设备事业群总经理游人杰及联发科智能显示暨客制化芯片事业部行销处处长彭建凯首次揭秘了联发科的ASIC业务。

什么是ASIC芯片?近年随着以比特币为代表的虚拟货币市场的火爆,催生了一大批生产“挖掘”虚拟货币设备的“矿机”厂商,其中最为知名的要属比特大陆了。

而比特大陆之所以能够在矿机市场异军突起,则主要得益于其自主设计的针对比特币矿机的ASIC芯片。

因为相对于CPU、GPU来说,采用专用的ASIC芯片来“挖矿”更具效率。

以比特大陆的Antminer S9矿机为例,其内部集成了189个ASIC芯片(BM1387),而且采用的是台积电16nm FinFET制程。

同样,目前主流的矿机厂商都采用的是定制的ASIC芯片。

这也使得ASIC芯片开始被大众所熟知。

但是ASIC芯片并不仅仅能被用于“挖矿”,还被用于包括人工智能在内等众多领域。

那么什么才是ASIC芯片?它与我们常见的CPU、GPU等通用型芯片相比又有何不同?早在1981年3月,Sinclair公司推出了一款8位个人电脑ZX81,其所采用的Z80处理器则被认为是最早的ASIC原型。

实际上ASIC是Application-Specific In te grated Circuit(应用型专用集成电路)的缩写,是一种专用芯片,是为了某种特定的需求而专门定制的芯片的统称。

比如专用的音频、视频处理器,同时目前很多专用的AI芯片业可以看作是ASIC 的一种。

与CPU、GPU、FPGA相比如何?CPU与GPU都是我们常见的通用型芯片,它们在各自领域都可以高效地完成任务,但当同样应用于通用基础计算领域时,设计架构的差异直接导致了两种芯片性能的差异。

CPU作为通用处理器,除了满足计算要求,为了更好的响应人机交互的应用,它要能处理复杂的条件和分支,以及任务之间的同步协调,所以芯片上需要很多空间来进行分支预测与优化(control),保存各种状态(cache)以降低任务切换时的延时。

asic与fpga芯片电平标准ASIC和FPGA芯片是常见的数字电路设计和实现解决方案。

它们的设计和制造都需要定义和统一的电平标准,以保证它们的互操作性和可靠性。

下面我们将深入探讨ASIC和FPGA芯片的电平标准。

ASIC芯片的电平标准一般是由芯片制造商或业内相关组织定义的。

ASIC芯片一般采用的是标准的CMOS工艺,因此它们的电平标准也可以采用CMOS的电平标准。

在CMOS电路中,逻辑0和逻辑1分别对应着电平低和电平高。

通常逻辑0的电平标准是接近于0V的电压,而逻辑1的电平标准则是接近于芯片供电电压的电压。

以3.3V的供电电压为例,逻辑1的电平标准一般为2.5V(高电平)。

FPGA芯片的电平标准不同于ASIC芯片,因为FPGA芯片的每一项电路功能都可以通过程序来定制,因此需要更加灵活的电平标准。

通常FPGA芯片采用的是LVCMOS(Low Voltage CMOS)电平标准。

LVCMOS 电平标准的特点是能够支持多个不同的电压标准,包括3.3V、2.5V、1.8V、1.5V等等。

此外,LVCMOS电平标准还提供了不同的速度等级,以满足不同应用场景的需求。

在实际的应用中,ASIC和FPGA芯片的电平标准需要被统一协调,以保证它们之间的兼容性和可靠性。

通常这个问题通过引入中间转接电路来解决。

比如在ASIC芯片和FPGA芯片之间,可以加入一个外部的FPGA芯片作为中间转接电路,以转换电平标准并实现信号的适配。

总之,ASIC和FPGA芯片的电平标准是它们设计和实现中非常重要的一部分。

其定义和统一是保证芯片互操作性和可靠性的重要手段。

芯片设计师和制造商需要严格按照定义的电平标准进行设计和实现,以保证芯片的正确运行和稳定性。

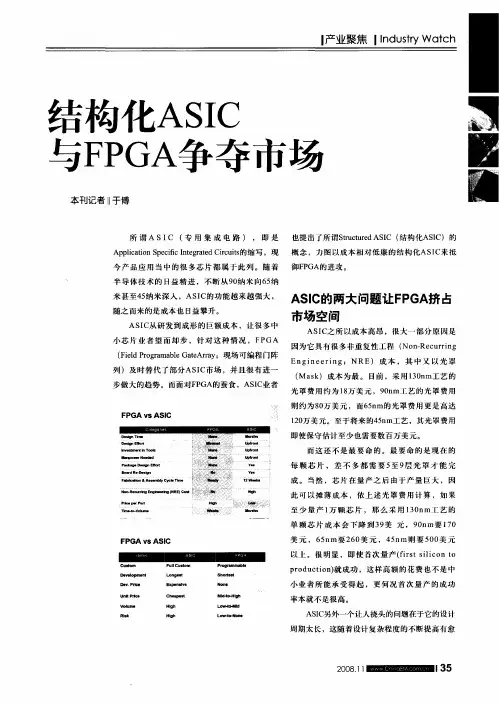

ASIC与FPGA比较谈专用集成电路(ASIC)采用硬接线的固定模式,而现场可编程门阵列(FPGA)则采用可配置芯片的方法,二者差别迥异。

可编程器件是目前的新生力量,混合技术也将在未来发挥作用。

与其他技术一样,有关ASIC技术过时的报道是不成熟的。

新的ASIC产品的数目可能有大幅度下降,但其销售额仍然相当高,尤其是在亚太区。

此外,采用混合式方法,如结构化ASIC,也为该技术注入了新的活力。

同时,FPGA(和其他可编程逻辑器件)也在发挥作用,赢得了重要的大众市场,并从低端应用不断向上发展。

每种技术都有它的支持者。

一般来说,ASIC用于大型项目,而对于需要快速投放市场且支持远程升级的小型项目,FPGA则更为适合。

ASIC和FPGA供应商对这两种技术孰优孰劣不能达成共识,对适合的应用领域也持不同看法。

上述技术及其衍生技术将可能在今后一段时间内长期存在。

Altera Corp的高密度FPGA高级总监David Greenfield指出,FPGA技术的主要优势仍是产品投放市场的时间较短。

他说:“在目前新增的设计方案中,对FPGA的选择倾向超过ASIC。

ASIC技术有其价值所在,它的性能、密度和单位容量都相当出色,不过随着FPGA的发展和ASIC的开发成本不断上升,将会导致ASIC的市场份额不断缩小。

”在上述趋势之后发挥作用的,正是FPGA在性能、密度和制造成本上的发展。

Greenfield指出,高性能曾经是ASIC超出FPGA的优势,当时FPGA在性能和功能上都较逊色。

随着芯片的制造工艺从180nm发展到130nm甚至90nm,上述情况发生了很大变化,现在FPGA的性能已经能够满足大多数应用的需要(要求最高的应用除外),而密度水平则达到逻辑设计的80%。

他解释说:“某些系统设计师也认识到,ASIC的市场领域在于极高性能/密度的产品,这种市场领域风险非常大。

NRE (非重复性工程设计)和开发成本对这种设备而言是最高的。

通用CPU,ASIC,FPGA和NP网络处理器这四种网络交换机体系结构的详细比较分析使用NP+ASIC的体系设计方式是最为完美的选择。

使用ASIC芯片高速处理各种传统的业务,如二层交换、三层路由、ACL、QoS以及组播处理等等,满足核心交换机对于交换机处理性能的需求;而利用NP实现各种非传统或未成熟的业务,根据需要灵活支持IPV6、Load Balancing、VPN、NAT、IDS、策略路由、MPLS、防火墙等多种业务功能,满足核心交换机对于业务按需叠加的需求……多层交换体系结构的引入有效地提高了局域网的速度,对多层交换体系结构排队模型、交换实施和交换结构等方面的了解,可以更深刻地认识到局域网交换机在性能上的提高。

首先明确几个基本概念:排队模型交换结构是指数据从一个端点到达另一个端点的“高速路”,排队是一种用于控制拥塞的缓冲机制,当交换结构出现拥塞时,会在很大程度上直接影响交换机的性能,所以进行拥塞管理是非常有必要的。

在多个端口争用同一个端口时就需要拥塞管理,对信息包进行排队处理。

排队可以采用动态缓冲区排队或固定缓冲区排队,其中动态缓冲区排队时缓冲区长度为固定增量(如每次64K字节),可以更有效地利用缓冲区资源;而固定缓冲区排序时缓冲区的长度是固定的,这样缓冲区的使用效率不高,但比定制控制器(custom conollers)成本低。

排队可以在交换结构的输入端口进行,即输入排队,也可在交换结构的输出端口进行,即输出排队。

在输入排队时,信息包在进入端口处得到缓冲,最高可将吞吐量减少60%,但会造成线路端阻塞;在输出排队时缓冲区设在输出端口,无线路阻塞,但在流量高峰期间会造成缓冲区溢出。

交换实施交换实施用来说明交换决策的地点和方式:是在本地还是在中央地点,是最长匹配还是准确匹配。

交换决策的地点是中央地点时,就是集中交换。

集中交换采用集中发送表,针对交换和识别提供集中控制,为达到实施的快速处理,查询由ASIC完成,集中交换可以执行第2层或第3层查询。

第21卷 第2期电子测量与仪器学报V ol 121 N o 12JOURNAL O F EL ECTRON I C 2007年4月M EASUR E M EN T AND I N STRUM EN T・109 ・本项目为福建省教育厅科技资助项目(编号:JA03005)和福建省自然科学基金计划资助项目(编号:Z0512003)。

本文于2005年12月收到。

王灵芝:硕士研究生;黄春晖:教授。

FPGA 的配置及其接口电路的设计王灵芝 林培杰 黄春晖(福州大学物理与信息工程学院,350002)摘 要:本文介绍对X I L I N X 公司Spartan Ⅱ系列的XC2S50的FPG A 配置数据的方法。

提出了利用CP LD 和F LASH 组成串行配置系统实现对FPG A 的上电配置以及通过计算机并口实现数据的传送和监测的方法。

对内部的控制电路的电路结构、软件设计等方面进行了阐述。

在此系统之上实现了计算机串口与S DRAM 之间的相互通信。

实验结果表明系统功能可靠、实用。

经测试系统最大时钟频率可以达到761923MHz,F LAS H 的读写速率可达到111Mbs 。

与基于单片机配置的方法比较,高速安全的完成对FPG A 的上电配置。

关键词:FPG A,CP LD,F LAS H,串行配置中图分类号:T N43 文献标识码:BConf i gura ti on of FPGA and D esi gn of Its I n terface C i rcu itW ang L ingzhi L in Peijie Huang Chunhui(College of Physics and I nfor mati on Engineering of fuzhou university Fuzhou 350002,China )Abstract:The article intr oduces a configurati on method f or XC2S50FPG A,which is a me mber of Spartan Ⅱfa m ily fr om X I L I N X cor porati on .The configurati on method uses a serial syste m composed of CP LD&F LASH,and realizes data trans m itting and monit oring thr ough the parallel port of a computer .The circuit structure of the contr ol circuit and the s oft w are design are ex p lained .The interface bet w een S DRM and FPG A was designed,and mutual communicati on bet w een the serial port of the computer and S DRAM was realized .Experi m ent result indicates that the syste m functi ons stably and reliably and is p ractical;thr ough testing,the maxi m um syste m cl ock frequency rea 2ches t o 76.923MHz,the reading and writing s peed of F LASH reaches up t o 111Mbs .Compared with m icr ocon 2tr oller configurati on method,the p r oposed method can safely configure FP AG with high s peed during power on .Keyword:FPG A,CP LD ,F LASH,serial configurati on 1 FPG A /CP LD 既继承了ASI C 的大规模、高集成度、高可靠性的优点,又克服了普通ASI C 周期长、投资大、灵活性差的缺点,逐步成为复杂数字硬件电路的理想选择[1-2]。

FPGA与ASIC在电子设计中的比较在电子设计领域中,FPGA(Field Programmable Gate Array)和ASIC (Application-Specific Integrated Circuit)是两种常见的集成电路设计技术,它们在设计复杂电路时起着重要作用。

本文将对FPGA和ASIC在电子设计中的比较进行阐述,以帮助读者更好地了解两者之间的特点和适用场景。

首先,从设计灵活性方面来看,FPGA具有明显优势。

FPGA是一种可编程的硬件,用户可以通过编程来实现不同的功能,并且可以多次重编程。

这种灵活性使得FPGA适用于快速原型设计和产品开发阶段,能够应对需求变化和快速迭代的设计要求。

相比之下,ASIC是一种定制集成电路,设计固定在硅片上,不具备可编程性。

ASIC的设计和制造过程复杂且成本高昂,适用于量产和对性能要求高、功耗和成本要求低的应用场景。

其次,就性能和功耗方面而言,ASIC往往比FPGA具有更高的性能和更低的功耗。

由于ASIC是定制化设计,可以优化电路结构和布局,达到更高的工作频率和更低的功耗。

ASIC通常用于对性能要求非常高的应用,如通信、计算等领域。

而FPGA在性能和功耗上一般不如ASIC,因为FPGA的可编程逻辑存在一定的延迟,且硬件资源有限,但适用于那些对性能要求不是特别苛刻的应用场景。

此外,成本也是影响选择FPGA或ASIC的关键因素之一。

由于FPGA具有可编程性和灵活性,其设计周期短、开发成本低,适合小规模生产和快速原型设计。

而ASIC的设计和制造成本较高,适合大规模生产和长期稳定的产品。

因此,在选择FPGA还是ASIC时,需要综合考虑设计需求、市场定位、生产规模等因素,对成本做出合理评估。

在实际应用中,通常会根据具体的项目需求和设计要求来选择FPGA或ASIC。

当需要快速原型验证、设计迭代频繁或产品生命周期较短时,FPGA是一个较好的选择;而当需要大规模生产、对性能要求极高或产品长期稳定时,ASIC更适合。

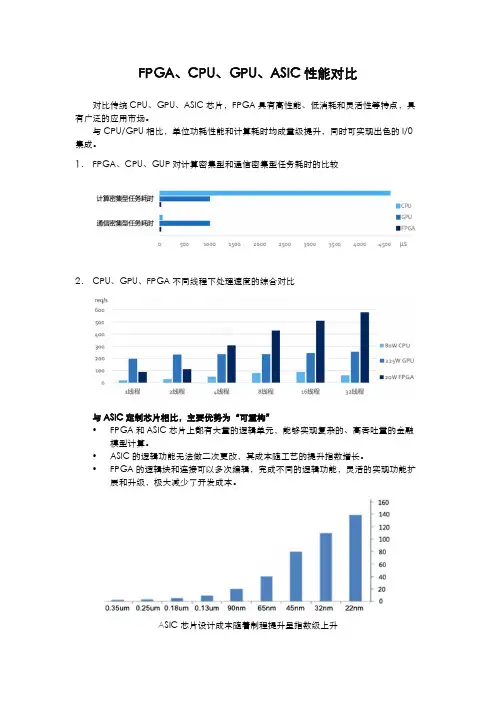

FPGA、CPU、GPU、ASIC性能对比对比传统CPU、GPU、ASIC芯片,FPGA具有高性能、低消耗和灵活性等特点,具有广泛的应用市场。

与CPU/GPU相比,单位功耗性能和计算耗时均成量级提升,同时可实现出色的I/0集成。

1.FPGA、CPU、GUP对计算密集型和通信密集型任务耗时的比较

2.CPU、GPU、FPGA不同线程下处理速度的综合对比

与ASIC定制芯片相比,主要优势为“可重构”

•FPGA和ASIC芯片上都有大量的逻辑单元,能够实现复杂的、高吞吐量的金融模型计算。

•ASIC的逻辑功能无法做二次更改,其成本随工艺的提升指数增长。

•FPGA的逻辑块和连接可以多次编辑,完成不同的逻辑功能,灵活的实现功能扩展和升级,极大减少了开发成本。

A SIC芯片设计成本随着制程提升呈指数级上升。

ASIC、FPGA 和CPU 三者的特点比较

ASIC 芯片内部架构较为简单,不可以硬件编程,只能用来专门处理某一种功能,灵活性最差,但是在执行某一种任务上的效率最高。

ASIC 也被称为专用集成电路。

FPGA 芯片内部架构稍微复杂一些,可以硬件编程,因而可以通过硬件编程语言来改变内部芯片的逻辑结构,从而能够在提供一定灵活性的同时,还能够保证较高的处理效率,算是在灵活性和性能上取了个折中。

FPGA 也被称为可编程集成电路。

FPGA 的特点如下:

(1)采用FPGA 设计ASIC 电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

半定制化的FPGA芯片和全定制化的ASIC芯片当前阶段,GPU 配合CPU 仍然是AI 芯片的主流,而后随着视觉、语音、深度学习的算法在FPGA以及ASIC芯片上的不断优化,此两者也将逐步占有更多的市场份额,从而与GPU达成长期共存的局面。

从长远看,人工智能类脑神经芯片是发展的路径和方向。

本文主要介绍半定制化的FPGA芯片和全定制化的ASIC芯片。

AI 芯片是人工智能时代的技术核心之一,决定了平台的基础架构和发展生态。

芯片发展历程AI 芯片按技术架构分类可分为GPU(Graphics Processing Unit,图形处理单元)、半定制化的FPGA、全定制化ASIC和神经拟态芯片等。

各个芯片的特点如下:GPU 通用性强、速度快、效率高,特别适合用在深度学习训练方面,但是性能功耗比较低。

FPGA 具有低能耗、高性能以及可编程等特性,相对于CPU 与GPU 有明显的性能或者能耗优势,但对使用者要求高。

ASIC 可以更有针对性地进行硬件层次的优化,从而获得更好的性能、功耗比。

但是ASIC 芯片的设计和制造需要大量的资金、较长的研发周期和工程周期,而且深度学习算法仍在快速发展,若深度学习算法发生大的变化,FPGA 能很快改变架构,适应最新的变化,ASIC 类芯片一旦定制则难于进行修改。

当前阶段,GPU 配合CPU 仍然是AI 芯片的主流,而后随着视觉、语音、深度学习的算法在FPGA以及ASIC芯片上的不断优化,此两者也将逐步占有更多的市场份额,从而与GPU达成长期共存的局面。

从长远看,人工智能类脑神经芯片是发展的路径和方向。

本文主要介绍半定制化的FPGA芯片和全定制化的ASIC芯片。

半定制化的FPGAFPGA 是在PAL、GAL、CPLD 等可编程器件基础上进一步发展的产物。

用户可以通过。

1 引言微电子技术的飞速发展,带动数字系统向着高速度、大容量、小体积的集成化方向发展,FPGA(Field Programmable Gate Array)和ASIC(Application Specific Integrated Circuit)电路设计技术是实现系统集成化的重要方式。

但因ASIC和FPGA的设计技术和实现方式有所不同,所以体现在研发周期、降低成本、市场竞争力等方面各有特点和适应性。

掌握两种不同设计技术和实现方式,了解两种技术的发展变化和市场动向,充分发挥各自特点,对研发产品前期的设计路线和市场定位起着重要作用,是产品走向成功的基础。

2 FPGA和ASIC设计特点及应用2.1 FPGA设计FPGA是一种可编程阵列逻辑电路器件。

一般的FPGA采用基于SRAM的查找表逻辑形成结构,就是用SRAM来构成逻辑函数发生器,这种结构每次系统上电时需要加载编程数据。

也有通过熔丝或反熔丝方式实现编程的,但这种实现方式只能编程一次。

FPGA设计最终是产生出所需功能电路的编程FPGA和ASIC设计特点及应用探讨孟李林(西安邮电学院,西安710061)摘要:介绍了ASIC、FPGA的设计步骤和设计流程,重点比较两者之间的设计特点和应用趋向,采用这两种不同方法完成40G高阶数字交叉连接芯片设计。

通过比较表明:FPGA技术适用于小批量、产品更新快、周期短的电子产品设计,可以明显提高设计速度,缩短产品上市时间;ASIC技术适用于大批量、产品比较成熟、生命周期长的电子产品设计。

ASIC的集成度和单片价格都比FPGA有优势。

关键词:现场可编程器件;专用集成电路;系统集成;中图分类号:TN47 文献标识码:A 文章编号:1003-353X(2006)07-0526-04Discussion on the Design Characteristics and Applicationsof ASIC and FPGAMENG Li-lin(Xi'an Institute of Post and Telecommunications, Xi'an 710061, China)Abstract: The design flow of FPFA and ASIC and comparisons were focused on, includingtheir features and their application trends. A space division cross connect chip for 40G higherorder cross connect system was implemented in both design methods. FPGA can shorten time-to-market of electronics products with low design cost, so it is preferable to small lot electronicsproducts with fast updating and short life cycle. Whereas ASIC is higher integrations and lowerprice of per chip than that of FPGA, it suits for mature batch-bulk electronics products.Key words: FPGA;ASIC;system integration基金项目:国家“十五”科技攻关课题(2002BA106B06);国家863计划课题(2003AA1Z1190)半导体技术第31卷第7期2006年7月526Semiconductor Technology Vol. 31 No. 7July 2006527数据。

FPGA和ASIC的概念,他们的区别?答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。

FPGA与ASIC实现系统设计的比较在当今的电子设备中集成电路的应用已经越来越广泛,几乎涉及到每一种电子设备中。

集成电路按其实现技术可以分为2大类:可编程逻辑器件(包括CPLD和FPGA等)和专用集成电路(ASIC)。

下面我们分别从这2类集成电路的特点和如何使用这2类集成电路来实现我们的设计需求来进行比较,以为我们以后的系统设计提供借鉴。

首先我们以FPGA为代表比较可编程逻辑器件和ASIC,它们最大的区别就是FPGA在不知道使用者的具体需求之前就已经按一定的配置制造好了所有的电路,使用者再根据自己的设计需要选用其中的电路来使用,而ASIC是根据使用者的设计需求来制造其中的电路。

由于以上原因使得这2类集成电路具有如下特点:ASIC由厂家定制,有比较低的单片生产成本,但却有很高的设计成本以及缓慢的上市时间;FPGA则具有高度的灵活性,低廉的设计成本以及适中的器件成本和快速的面世时间。

下面我们分别简单介绍使用ASIC和FPGA实现某一设计的的步骤:要设计并生产一颗ASIC其流程大致如下:首先是系统设计,这其中包括设计好系统的对外接口,系统内部大的模块划分,内部模块之间的接口确定,系统时钟的确定等等。

然后进行进一步的详细设计,这一步包括各个大模块内部的再次模块划分,内部小模块之间的接口确定等。

再下一步是进行RTL级编码,即使用硬件描述语言进行实际的电路的设计,类似于软件业的代码编写。

RTL级编码完成后进行RTL级仿真,如果功能正确那么下一步利用综合工具生成网表和SDF文件然后进行前仿真,如果前仿真没有问题即可进行布局布线,布局布线完成后再次提取网表和SDF文件,利用布局布线后的网表和SDF文件进行后仿真,如果后仿真也没有问题即可进行样片的生产。

第16卷第6期重庆职业技术学院学报Vol.16No.62007年11月JournalofChongqingVocational&TechnicalInstituteNov.20071引言可编程逻辑器件(ProgrammableLogicDevice,PLD)给数字系统的设计带来了革命性的变化。

它的影响丝毫不亚于20世纪70年代单片机的发明和使用,PLD能完成任何数字器件的功能,上至CPU,下至简单的74电路。

PLD如同一张白纸,可通过原理图输入法或硬件描述语言,或两者混合自由的设计一个数字系统。

使用PLD来开发数字电路,可以大大缩短设计时间,减少PCB面积,提高系统的可靠性。

PLD的这些优点使得PLD技术从20世纪90年代以后得到飞速的发展,成为电子设计领域中最具有活力和发展前途的一项技术。

2ASIC、FPGA/CPLD的区别2.1ASIC定义及设计分类ASIC(ApplicationSpecificIntergratedCircuits)即专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

目前用CPLD(复杂可编程逻辑器件)和FPGA(现场可编程逻辑门阵列)来进行ASIC设计是最为流行的方式之一,它们的共性是都具有用户现场可编程特性,都支持边界扫描技术,但两者在集成度、速度以及编程方式上具有各自的特点。

ASIC的特点是面向特定用户的需求,品种多、批量少,要求设计和生产周期短,它作为集成电路技术与特定用户的整机或系统技术紧密结合的产物,与通用集成电路相比具有体积更小、重量更轻、功耗更低、可靠性高、性能高、保密性增强、成本降低等优点。

ASIC设计主要有全定制(fullcustom)设计方法和半定制(semi-custom)设计方法。

半定制设计又可分为门阵列设计、标准单元设计、可编程逻辑设计,等等。

全定制方法是完全由设计师根据工艺,以尽可能高的速度和尽可能小的面积以及完全满意的封装、独立地进行芯片设计。

FPGA将逐渐取代ASIC和ASSP

陆绍强

【期刊名称】《电子产品世界》

【年(卷),期】2000(000)009

【摘要】@@ 可编程逻辑技术目前已经能与ASIC(专用集成电路)和ASSP(专用标准产品)争夺市场,并逐渐呈现出取代ASIC和ASSP的趋势,这极大程度上是因为FPGA技术的发展.FPGA产品在逻辑密度、性能和功能上有了极大的提高,同时器件成本也大幅下降.

【总页数】1页(P56)

【作者】陆绍强

【作者单位】Xilinx公司

【正文语种】中文

【中图分类】TP3

【相关文献】

1.新技术助力28纳米FPGA加速蚕食ASSP/ASIC市场 [J], 孔文

2.利用FPGA取代ASSP更经济 [J], 陈志文

3.高端应用ASIC设计服务抢占FPGA和ASSP市场 [J], 富士通半导体

4.XMOS重新定义晶圆——软件定义芯片挑战ASIC、ASSP以及FPGA [J], Tom R.Halfhill;马志强

5.2.5D堆叠硅片互联技术推动FPGA加速取代ASIC和ASSP 赛灵思发布拥有68亿颗晶体管的世界最大容量FPGA [J], 徐俊毅

因版权原因,仅展示原文概要,查看原文内容请购买。