2.4.1 并行输入串行输出

- 格式:doc

- 大小:68.50 KB

- 文档页数:2

第4章并行数字输入/输出端口的使用——数码管显示电路的设计目标通过本章的学习,应掌握以下知识●MSP430系列微控制器的并行数字输入/输出端口●数码管的结构和工作原理●数码管的显示数据与显示代码之间的关系●利用查表实现代码转换的方法——译码程序●函数的格式以及函数的调用●数据类型●循环语句●利用循环语句实现时间延迟引言显示电路是应用系统的一个组成部分,使用者用这个部分可以获取系统工作结果和工作状态的信息。

在学习过程中,通常首先掌握这部分内容的相关知识,这样就能够用显示电路来获得将要学习电路的工作结果和工作状态。

数码管是一种最常用的显示器件,虽然它只能显示数值,而不能像液晶显示器那样还可以显示字符和图形,但是它使用简单,价格便宜,很适用初学者使用,而且数码管电路的工作原理与基于发光二极管的流水灯电路非常类似。

数码管显示电路的工作方式分静态显示和动态显示两种。

前者,数码管的每一个管脚需要占用微控制器芯片的一个信号输出管脚;后者虽然可以减少对微控制器管脚资源的占用,但是这时需要微控制器不停地输出控制信号,即几乎占用了CPU的全部时间。

这里只描述数码管静态显示电路。

本章首先描述MSP430系列微控制器并行数字输入/输出端口的相关寄存器,通过这些寄存器可以完成工作方式的选择以及数据传输的实现;接着讨论如何将显示数据转换为数码管的显示代码;微控制器的工作速度很快,完成一次并行数据传输仅需几个us,因此在连续向数码管进行数据发送之间需要添加具有时间延迟功能的程序块。

14.1MSP430系列微控制器的并行数字输入/输出端口MSP430系列微控制器最多可以提供8个并行数字输入/输出端口,它们被分别命名为P1~P8。

每个并行数字输入/输出端口最多可以提供8个数字输入/输出管脚,它们被分别命名为Px.0~Px.7,这里x可以理解为变量,它表示MSP430系列微控制器可以提供的8个并行数字输入/输出端口中的任意一个。

MSP430系列芯片具有多种封装型式,因此并不是所有芯片都能够提供所有这些并行数字输入/输出管脚资源。

单片机数字输入输出接口扩展设计方法单片机作为一种常见的微控制器,其数字输入输出接口的扩展设计方法是我们在电子工程领域中经常遇到的任务之一。

在本文中,我们将讨论单片机数字输入输出接口的扩展设计方法,并探讨其中的原理和应用。

在单片机系统中,数字输入输出(I/O)接口在连接外围设备时起着至关重要的作用。

通过扩展数字 I/O 接口可以为单片机系统提供更多的输入输出通道,从而提高系统的功能和性能。

下面将介绍几种常见的单片机数字 I/O 接口扩展设计方法。

1. 并行输入输出接口扩展并行输入输出接口扩展是最常见和直接的扩展方法之一。

通常,单片机的内部I/O口数量有限,无法满足一些复杂的应用需求。

通过使用外部并行输入输出扩展芯片,可以将单片机的I/O口扩展到更多的通道,同时保持高速数据传输。

这种方法可以使用注册器和开关阵列来实现数据的输入和输出。

2. 串行输入输出接口扩展串行输入输出接口扩展是一种节省外部引脚数量的方法。

使用串行输入输出扩展器,可以通过仅使用几个引脚实现多个输入输出通道。

这种方法适用于具有较多外设设备且外围设备数量有限的应用场景。

通过串行接口(如SPI或I2C)与扩展器通信,可以实现高效的数据传输和控制。

3. 矩阵键盘扩展矩阵键盘扩展是一种常见的数字输入接口扩展方法。

很多应用中,需要通过键盘输入数据或控制系统。

通过矩阵键盘的使用,可以大大减少所需的引脚数量。

通过编程方法可以实现键盘按键的扫描和解码,从而获取用户输入的数据或控制信号。

4. 脉冲编码调制(PCM)接口扩展脉冲编码调制是一种常见的数字输出接口扩展方法。

它通过对数字信号进行脉冲编码,将数字信号转换为脉冲信号输出。

这种方法适用于需要输出多个连续的数字信号的应用,如驱动器或步进电机控制。

通过适当的电路设计和编程,可以实现高效的数字信号输出。

5. PWM(脉冲宽度调制)接口扩展PWM接口扩展是一种常用的数字输出接口扩展方法。

PWM技术通过改变信号的脉冲宽度来实现模拟信号输出。

单片机的输入输出方式单片机是一种集成电路,具有处理和控制任务的能力。

在实际应用中,单片机通常需要与外设进行数据的输入和输出。

因此,单片机的输入输出方式就成为了一个重要的研究领域。

本文将介绍几种常见的单片机输入输出方式,并分析它们的优缺点。

一、并口输入输出并口输入输出是最常见和简单的一种方式。

通过并行数据总线,单片机可以一次性传输多位二进制数据。

并口通常与外设芯片或者外围元件连接,例如LCD显示屏、键盘等。

并口输入输出的优点是速度快、数据传输稳定可靠,但同时也存在缺点,例如占用较多的引脚资源和布线不便等。

二、串口输入输出串口输入输出是一种使用串行通信协议进行数据传输的方式。

与并口输入输出相比,串口只能传输一位二进制数据。

但是,串口具有节省引脚资源、传输距离较长和可靠性高等优点。

串口输入输出通常与外设设备或者计算机进行数据通信。

串口通信有两种常见标准:RS232和RS485。

RS232主要用于与计算机通信,而RS485多用于远程数据采集和控制系统。

三、模拟输入输出模拟输入输出是一种以模拟电压或电流形式进行数据传输的方式。

单片机可以通过模拟输入输出来与模拟信号传感器进行数据采集和控制。

例如,通过模拟输入可以采集温度、湿度等模拟信号,通过模拟输出可以控制电机、电阻等模拟设备。

模拟输入输出的优点是能够处理连续变化的模拟信号,但在数据精度和稳定性上相对数字信号略有不足。

四、计时器/计数器输入输出计时器/计数器是单片机内部的一个模块,用于测量时间间隔或者对外部事件进行计数。

通过配置计时器/计数器的一些参数,可以实现输入输出功能。

例如,通过计时器/计数器输入输出可以实现PWM输出控制、捕获外部脉冲等功能。

计时器/计数器输入输出的优点是精度高、灵活性强,但需要掌握一些特定的配置知识。

五、中断输入输出中断输入输出是单片机在执行主程序的同时,能够监听外部事件的一种机制。

当外部事件满足特定条件时,单片机会自动跳转到相应的中断服务程序来处理。

移位寄存器的设计及实现移位寄存器(Shift Register)是一种常用的数字逻辑电路器件,它能够将数据按照输入和输出的时序进行移位操作。

通过移位寄存器,我们可以实现数据的串行传输、并行-串行或者串行-并行转换、数据延迟等功能。

本文将对移位寄存器的设计与实现进行介绍。

一、移位寄存器的设计1.串行输入、串行输出的移位寄存器这种移位寄存器称为串行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过一个输入端串行输入,然后通过触发器依次移位,最后从输出端串行输出。

2.并行输入、并行输出的移位寄存器这种移位寄存器称为并行移位寄存器,它包括n个触发器,每个触发器提供一个数据位的存储空间。

数据通过n个输入端并行输入到各个触发器,然后通过控制信号进行同步移位。

最后从n个输出端并行输出。

3.并行输入、串行输出的移位寄存器这种移位寄存器称为并行-串行移位寄存器,它先从n个输入端并行输入数据,然后通过控制信号进行同步移位,并将移位结果通过一个输出端串行输出。

4.串行输入、并行输出的移位寄存器这种移位寄存器称为串行-并行移位寄存器,它先从一个输入端串行输入数据,然后通过触发器进行移位,最后将移位结果从n个输出端并行输出。

1.触发器选择由于是8位移位寄存器,需要选择8个触发器。

常用的触发器有D触发器、JK触发器等,可以根据实际需求选择合适的触发器。

2.输入输出端口设计设计一个输入端口用于串行输入数据。

由于是串行输入,需要一个时钟信号和一个使能信号进行同步移位操作。

同时,设计一个输出端口用于串行输出数据。

3.控制信号电路设计根据串行输入、串行输出的要求,需要设计一个时钟信号和一个使能信号的电路。

使能信号在移位过程中保持逻辑高电平,只有当8位数据全部移位完成时才将使能信号置为逻辑低电平。

二、移位寄存器的实现1.设计一个8位移位寄存器电路,并连接8个D触发器。

2.将串行输入信号与D触发器的数据端相连,时钟信号与D触发器的时钟端相连,使能信号与D触发器的使能端相连。

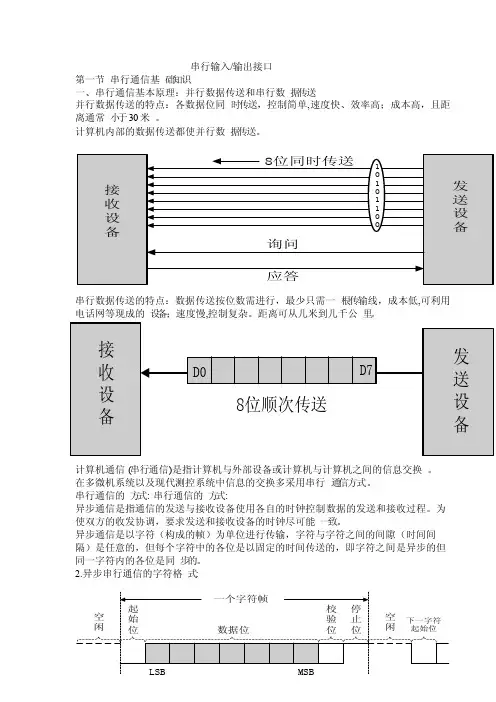

串行输入/输出接口第一节串行通信基础知识一、串行通信基本原理:并行数据传送和串行数据传送并行数据传送的特点:各数据位同时传送,控制简单,速度快、效率高;成本高,且距离通常小于30米。

计算机内部的数据传送都使并行数据传送。

串行数据传送的特点:数据传送按位数需进行,最少只需一根传输线,成本低,可利用电话网等现成的设备;速度慢,控制复杂。

距离可从几米到几千公里。

计算机通信(串行通信)是指计算机与外部设备或计算机与计算机之间的信息交换。

在多微机系统以及现代测控系统中信息的交换多采用串行通信方式。

串行通信的方式:串行通信的方式:异步通信是指通信的发送与接收设备使用各自的时钟控制数据的发送和接收过程。

为使双方的收发协调,要求发送和接收设备的时钟尽可能一致。

异步通信是以字符(构成的帧)为单位进行传输,字符与字符之间的间隙(时间间隔)是任意的,但每个字符中的各位是以固定的时间传送的,即字符之间是异步的但同一字符内的各位是同步的。

2.异步串行通信的字符格式:异步通信的特点:不要求收发双方时钟的严格一致,实现容易,设备开销较小,但每个字符要附加2~3位用于起止位,各帧之间还有间隔,因此传输效率不高。

二、串行通信的传输方向 单工 半双工 全双工传输。

2、半双工是指数据传输可以沿两个方向,但需要分时进行。

3、全双工是指数据可以同时进行双向传输三、串行通信的信号形式近程和远程的串行通信的信号形式不同1.近程通信(本地通信)采用数字信号直接传送,在传送过程中不改变原数据代码的波形和频率.这种数据传送方式称为基带传送方式.2.远程通信计算机A 计算机B利用调制器(Modula tor)把数字信号转换成模拟信号,然后送到通信线路上去,再由解调器(Demodu l ator)把从通信线路上收到的模拟信号转换成数字信号通信是双向的,调制器和解调器合并在一个装置中,这就是通常说的调制解调器MODEM四、传输速率:比特率和波特率1.比特率:每秒钟传输二进制代码的位数,单位是:位/秒(bps)如每秒钟传送240个字符,而每个字符格式包含10位(1个起始位、1个停止位、8个数据位),这时的比特率为:10位×240个/秒= 2400 bps 2.波特率:每秒钟调制信号变化的次数,单位是:波特(Baud)。

1 概述PANTHER(磐狮)是梅特勒-托利多公司最新推出的称重显示仪表。

它主要用于简单的称重显示和定值控制应用场合。

1.1 PANTHER主要特点易安装性:多种电压源-可以选择不同的电压供电。

可选交流电压:100VAC,120VAC,230VAC。

安装简单-面板式仪表只需在控制柜上开一个矩形口,就可以将仪表固定在控制柜上。

密封式(台式/墙式)仪表线束连接采用密封接头,具有防尘、防水效果(附合IP65标准)。

托架结构,可以将PANTHER放置在台上或装在墙上并且角度可调。

可拆装式连接头-所有外部线束连接都使用接线端子,端子排上有连接信号标记。

连接快速方便。

易于使用:显示器-使用荧光显示器,亮度高。

键盘-轻触薄膜键盘,键盘面板采用耐用的树酯材料,抗物理和化学损伤。

灵活性:设定-模块化树形结构参数设定,方便用户寻找设定参数,可设置缺省参数,方便快捷。

输入/输出-串行口提供称重数据输出。

并行输入/输出口可与控制设备连接,接收输入信号及提供输出控制信号。

稳定性:ISO9001认证-PANTHER的设计、制造和测试均是在梅特勒-托利多通过ISO9001质量认证的工厂进行。

工厂装配-PANTHER的所有零部件(包括选件)都在工厂安装调试好。

可维护性-内置诊断程序,易于发现和解决问题。

标准-PANTHER的设计符合有关国际计量和电气安全标准,以及电磁兼容性标准。

1.2 PANTHER技术特性PANTHER有两种型号:密封式(台/墙式)及面板式两种。

1.2.1 硬件特点•7位荧光段码显示器•6个轻触薄膜键盘•接线端子•一体化PCB板结构标准模拟传感器输入接口,可驱动8只350Ω的传感器双向串行口:COM1(RS232)并行口:一个输入,三个输出功能扩展口1.2.2 密封式外观特性•不锈钢外壳•外壳符合NEMA4X(IP65)标准•不锈钢支架•NEMA4X(IP65)密封接头•外部不用螺丝装配•五个LED指示灯指示OVER/UNDER分选或预置点状态1.2.3 面板式外观特性•铝合金拉伸外壳•不锈钢前面板•前面板符合NEMA4(IP65)标准•面板式安装•三个LED指示灯指示过量/正常/欠量,并可与预置点的输出状态对应。

并行输入串行输出移位寄存器原理以并行输入串行输出移位寄存器原理为标题,下面将详细介绍该原理及其应用。

移位寄存器是一种常用的数字电路元件,可以实现数据的平行输入和串行输出。

它由多个触发器组成,每个触发器都可以存储一个位的信息。

在并行输入时,数据可以同时输入到每个触发器中,而在串行输出时,触发器之间的数据按照一定的顺序传递,从而实现数据的移位。

在移位寄存器中,最常见的是串行输入并行输出的移位寄存器,即数据按照一位一位的顺序输入到移位寄存器中,而输出则可以同时输出多个位的数据。

这种移位寄存器的应用非常广泛,例如在串行通信中,可以使用移位寄存器将并行数据转换为串行数据进行传输,而在显示器中,也可以使用移位寄存器逐行扫描显示像素点。

移位寄存器的工作原理基于触发器的特性。

触发器是一种存储状态的元件,它可以根据时钟信号的变化来改变输出状态。

在移位寄存器中,触发器之间通过时钟信号进行串行数据传输。

当时钟上升沿到来时,触发器将其输入数据更新到输出中,并将原来的输出传递给下一个触发器,从而实现数据的移位。

在移位寄存器中,有两种常见的触发器,分别是D触发器和JK触发器。

D触发器是最简单的触发器,它有一个数据输入端D和一个时钟输入端CLK,当时钟信号发生变化时,D触发器将D端的数据更新到输出端Q中。

而JK触发器是一种更复杂的触发器,它有两个数据输入端J和K,以及一个时钟输入端CLK。

当时钟信号发生变化时,JK触发器根据J和K的值来更新输出端Q。

通过组合不同类型的触发器,可以构建出不同类型的移位寄存器,满足不同的应用需求。

除了串行输入并行输出的移位寄存器外,还有并行输入串行输出的移位寄存器。

这种移位寄存器可以同时输入多个位的数据,并将其串行输出。

在这种移位寄存器中,每个触发器都有一个数据输入端,当时钟信号发生变化时,触发器将输入端的数据更新到输出端,并将原来的输出传递给下一个触发器。

通过这种方式,多个位的数据就可以按照一定的顺序进行移位输出。

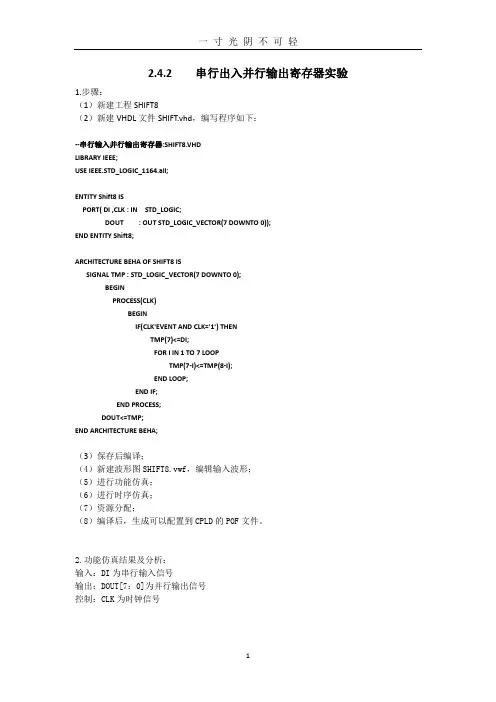

2.4.2 串行出入并行输出寄存器实验1.步骤:(1)新建工程SHIFT8(2)新建VHDL文件SHIFT.vhd,编写程序如下:--串行输入并行输出寄存器:SHIFT8.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.all;ENTITY Shift8 ISPORT( DI ,CLK : IN STD_LOGIC;DOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY Shift8;ARCHITECTURE BEHA OF SHIFT8 ISSIGNAL TMP : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINPROCESS(CLK)BEGINIF(CLK'EVENT AND CLK='1') THENTMP(7)<=DI;FOR I IN 1 TO 7 LOOPTMP(7-I)<=TMP(8-I);END LOOP;END IF;END PROCESS;DOUT<=TMP;END ARCHITECTURE BEHA;(3)保存后编译;(4)新建波形图SHIFT8.vwf,编辑输入波形;(5)进行功能仿真;(6)进行时序仿真;(7)资源分配;(8)编译后,生成可以配置到CPLD的POF文件。

2.功能仿真结果及分析:输入:DI为串行输入信号输出:DOUT[7:0]为并行输出信号控制:CLK为时钟信号(1)功能仿真波形分析:DI串行输入“01010101”DOUT[0:7]并行输出“01010101”因此,该设计能够实现串行输出并行输出的功能。

(2)时序仿真从波形图看出来,并行输出中两条相邻输出时间延迟为1.409ns.3.资源分配。

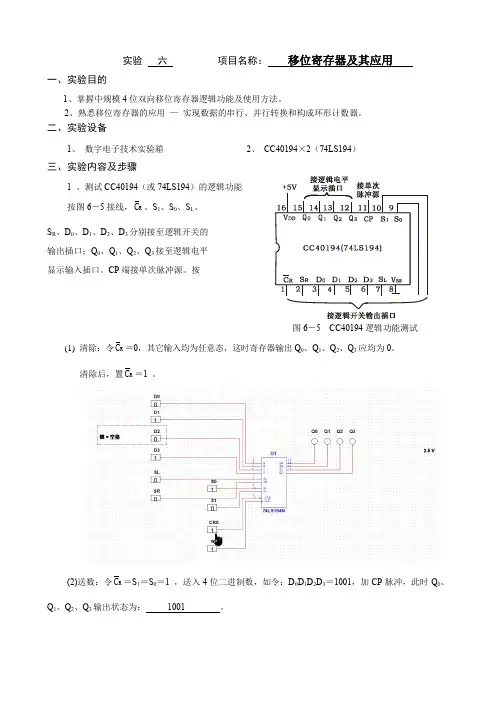

实验六项目名称:移位寄存器及其应用一、实验目的1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。

2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。

二、实验设备1、数字电子技术实验箱2、CC40194×2(74LS194)三、实验内容及步骤1 、测试CC40194(或74LS194)的逻辑功能按图6-5接线,R C、S1、S0、S L、S R、D0、D1、D2、D3分别接至逻辑开关的输出插口;Q0、Q1、Q2、Q3接至逻辑电平显示输入插口。

CP端接单次脉冲源。

按图6-5 CC40194逻辑功能测试(1)清除:令R C=0,其它输入均为任意态,这时寄存器输出Q0、Q1、Q2、Q3应均为0。

清除后,置R C=1 。

(2)送数:令R C=S1=S0=1 ,送入4位二进制数,如令:D0D1D2D3=1001,加CP脉冲,此时Q0、Q1、Q2、Q3输出状态为:1001 。

(3)右移:令R C=1,S1=0,S0=1,然后右移输入端S R送入二进制数码如0,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0100 ;紧接着,右移输入端S R送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:1010 ;紧接着,右移输入端S R送入二进制数码如0,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0101 ;紧接着,右移输入端S R送入二进制数码如0,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0010 。

(4) 左移:先令R C=0进行清零,再令R C=1,S1=1,S0=0,然后左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0001 ;紧接着,左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0011 ;紧接着,左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:0111 ;紧接着,左移输入端S L送入二进制数码如1,加CP脉冲,此时Q0、Q1、Q2、Q3显示为:1111 。

单片机移位寄存器1. 什么是单片机移位寄存器单片机移位寄存器(Shift Register)是一种具有移位功能的寄存器,在数字电子电路中被广泛应用。

它由一组触发器(Flip-Flop)组成,可以将数据按照特定的方式进行移位操作。

2. 移位寄存器的工作原理移位寄存器通常由串行输入、串行输出、并行输入和并行输出四个主要部分组成。

其工作原理如下:•串行输入:数据输入信号逐位地经过寄存器,通过串行输入端口输入。

每当输入一个新的数据位时,原有的数据位将向左移位,腾出位置存放新的数据位。

•串行输出:从移位寄存器的串行输出端口输出数据。

当整个移位寄存器被移位后,最右边的数据位将从串行输出端口输出,同时,原有数据位向右移位填充空出的位置。

•并行输入:通过并行输入端口将整个数据一次性输入到移位寄存器中,不进行移位操作。

•并行输出:通过并行输出端口将整个移位寄存器的内容一次性输出。

3. 移位寄存器的应用场景移位寄存器在数字电子电路中具有广泛的应用,例如:3.1. 数据传输与存储移位寄存器可以用于将数据从一个地方传输到另一个地方,实现数据的序列化和反序列化。

在通信系统中,可以使用移位寄存器将并行数据转换为串行数据进行传输,或者将串行数据转换为并行数据进行处理。

3.2. 并行输入/输出扩展通过移位寄存器,可以将单片机的并行输入/输出引脚扩展为更多的输入/输出引脚。

通过将多个移位寄存器级联,可以实现更多的输入/输出引脚扩展。

3.3. 状态存储移位寄存器可以用于存储状态信息,例如程序计数器(Program Counter)和状态寄存器(Status Register)等。

4. 移位寄存器的类型根据移位寄存器的工作方式和结构特点,常见的移位寄存器包括以下几种类型:4.1. 并行入/串行出移位寄存器(PISO)并行入/串行出移位寄存器有多个并行输入引脚和一个串行输出引脚。

多个并行输入信号可以一次性并行输入到寄存器中,然后按位进行移位,输出到串行输出引脚上。

了解电脑输入输出接口的种类和功能文章标题:了解电脑输入输出接口的种类和功能现代电脑作为人们生活和工作中必不可少的工具,其中输入输出接口的种类和功能在电脑运行和连接外部设备方面起到重要的作用。

本文将详细介绍电脑输入输出接口的种类和功能,帮助读者更好地了解和使用电脑。

一、串行接口串行接口是一种逐位传输数据的接口,其主要功能是用于连接外部设备,例如打印机和调制解调器。

串行接口的种类较多,其中较常见的是RS-232接口和USB接口。

1. RS-232接口RS-232接口是一种标准的串行通信接口,用于连接计算机和其他外部设备,常见的连接设备包括打印机、调制解调器和串口鼠标。

RS-232接口广泛应用于早期计算机,虽然速度较慢,但仍被某些特定设备所使用。

2. USB接口USB接口是一种通用串行总线接口,现已取代了RS-232接口成为主流连接电脑和外部设备的接口。

USB接口具有高速传输、热插拔和扩展性强等优点,适用于连接各种外部设备,如打印机、键盘、鼠标、摄像头和移动设备等。

二、并行接口并行接口是一种同时传输多个比特的接口,其主要功能是高速传输数据。

常见的并行接口包括并行打印接口(LPT接口)和SCSI接口。

1. 并行打印接口(LPT接口)LPT接口是一种常见的并行接口,用于连接电脑和打印机。

LPT接口传输速度相对较慢,但适用于连接一些需要大量数据传输的外部设备。

2. SCSI接口SCSI接口是一种高性能并行接口,用于连接计算机和外部设备,例如硬盘、光驱等。

SCSI接口传输速度较快,适用于对数据传输速度要求较高的设备。

三、视频接口视频接口是用于电脑图像和视频信号传输的接口,其主要功能是将电脑图像显示在外部显示器上。

常见的视频接口包括VGA接口、DVI 接口和HDMI接口。

1. VGA接口VGA接口是一种模拟视频接口,广泛用于连接电脑和显示器。

VGA接口能够传输标清图像信号,常用于老旧设备或低分辨率显示需求。

2. DVI接口DVI接口是一种数字视频接口,可传输高清图像信号。

计算机的输入输出接口技术剖析目前,计算机的输入输出接口技术主要包括以下几类:串行接口、并行接口、网络接口、无线接口等。

1.串行接口:串行接口是一种使用一条数据线进行传输的接口技术。

通常采用串行接口传输的设备有串行口鼠标、串行口键盘等。

串行接口的优点是只需使用一条数据线,节省了硬件成本,但是传输速度较慢。

2.并行接口:并行接口是一种同时使用多条数据线进行传输的接口技术。

常见的并行接口有LPT接口、IDE接口、SCSI接口等。

并行接口的优点是传输速度快,但是由于需要使用多条数据线,导致硬件成本较高。

3.网络接口:网络接口是计算机与局域网、广域网等网络进行连接的接口技术。

常见的网络接口有以太网接口、无线网卡接口等。

通过网络接口,计算机可以实现与其他计算机之间的数据传输和共享。

4.无线接口:无线接口是一种可以实现无线数据传输的接口技术。

常见的无线接口有蓝牙、Wi-Fi、红外线接口等。

无线接口的优点是便于移动和无线连接,但是传输速度相对有限。

在计算机硬件方面,输入输出接口技术常常采用芯片实现。

例如,串行接口常使用UART(Universal Asynchronous Receiver/Transmitter)芯片,它可以将串行数据转换为并行数据以及将并行数据转换为串行数据。

并行接口常使用并行口控制器芯片,它可以实现数据的并行传输和控制。

网络接口则常用网卡芯片,无线接口则常用无线网卡芯片等。

总体而言,输入输出接口技术在计算机中占据着重要的地位,它决定了计算机与外部设备之间信息交互的能力和效率。

随着科技的不断发展,输入输出接口技术也在不断推陈出新,以满足人们对计算机外设更高要求的需求。

寄存器实验报告一、实验目的1. 了解寄存器的分类方法,掌握各种寄存器的工作原理;2. 学习使用Verilog HDL 语言设计两种类型的寄存器。

二、实验设备PC 微机一台,TD-EDA 实验箱一台,SOPC 开发板一块。

三、实验内容寄存器中二进制数的位可以用两种方式移入或移出寄存器。

第一种方法是以串行的方式将数据每次移动一位,这种方法称之为串行移位(Serial Shifting),线路较少,但耗费时间较多。

第二种方法是以并行的方式将数据同时移动,这种方法称之为并行移位(Parallel Shifting),线路较为复杂,但是数据传送的速度较快。

因此,按照数据进出移位寄存器的方式,可以将移位寄存器分为四种类型:串行输入串行输出移位寄存器(Serial In- Serial Out)、串行输入并行输出移位寄存器(Serial In- Parallel Out)、并行输入串行输出移位寄存器(Parallel In- Serial Out)、并行输入并行输出移位寄存器(Parallel In-Parallel Out)。

本实验使用Verilog HDL 语言设计一个八位并行输入串行输出右移移位寄存器(Parallel In- Serial Out)和一个八位串行输入并行输出寄存器(Serial In- Parallel Out),分别进行仿真、引脚分配并下载到电路板进行功能验证。

四、实验步骤1.并行输入串行输出移位寄存器实验步骤1). 运行Quartus II 软件,选择File New Project Wizard 菜单,工程名称及顶层文件名称为SHIFT8R,器件设置对话框中选择Cyclone 系列EP1C6Q240C8 芯片,建立新工程。

2.) 选择File New 菜单,创建Verilog HDL 描述语言设计文件,打开文本编辑器界面。

3.) 在文本编辑器界面中编写Verilog HDL 程序,源程序如下:module lxc(din,r_st,clk,load,dout);input [7:0]din;input clk,r_st,load;output dout;reg dout;reg [7:0]lxc1;always @(posedge clk)if(!r_st)begindout<=0;endelsebeginif(load)beginlxc1=din;endelsebeginlxc1[6:0]=lxc1[7:1];lxc1[7]=0;enddout<=lxc1[0];endendmodule4). 选择File Save As 菜单,将创建的VHDL 设计文件保存为工程顶层文件名SHIFT8R.V。

2.4.1 并行输入串行输出移位寄存器实验

1.步骤:

(1)新建工程SHIFT8R;

(2)新建VHDL文件SHIFT8R.vhd,编写程序如下:

--带有同步并行预置功能的8位右移移位寄存器:SHIFT8R.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SHIFT8R IS

PORT( CLK , LOAD : IN STD_LOGIC ; --CLK是移位时钟信号、LOAD是并行数据预置使能信号DIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0); --DIN是8位并行预置数据端口

QB : OUT STD_LOGIC ); --QB是串行输出端口

END ENTITY SHIFT8R;

ARCHITECTURE BEHAV OF SHIFT8R IS

BEGIN

PROCESS(CLK,LOAD)

VARIABLE REG8 : STD_LOGIC_VECTOR( 7 DOWNTO 0);

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF LOAD='1' THEN

REG8 := DIN; --装载新数据

ELSE

REG8(6 DOWNTO 0):= REG8(7 DOWNTO 1);

-- 此语句表明:一个时钟周期后将上一时钟周期移位寄存器中的高7位

-- 二进制数赋给此寄存器的低7位

END IF;

END IF;

QB <= REG8(0);

END PROCESS; -- 输出最低位

END ARCHITECTURE BEHAV;

(3)保存后编译;

(4)新建波形图SHIFT8R.vwf,编辑输入波形;

(5)进行功能仿真;

(6)进行时序仿真;

(7)资源分配;

(8)编译后,生成可以配置到CPLD的POF文件。

2.功能仿真结果及分析:

输入:DIN[7:0]8为并行输入信号

输出:QB为串行输出信号

控制:CLK为时钟信号

LAOD并行数据预置使能信号

(1)功能仿真:

波形分析:LOAD=1,CLK=1,输入并行信号“01001101”

LOAD=0,每输入一个脉冲,右移一位并从QB 端输出,依次为“01001101” 因此,该设计可以实现并行输入串行输出的右移移位功能。

(2)时序仿真:

串行输出第二位延时8.237ns

3.资源分配

0 1 1 0 0 0 1 1。