基于CPLD控制的发电机组在线监测系统数据采集卡设计

- 格式:pdf

- 大小:151.93 KB

- 文档页数:3

CPLD 数据采集卡基本原理和说明作者:张树成、孙力 指导教师:陈力平【内容摘要】:设计了基于CPLD 的数字电压表,是数据采集卡的采样和显示的核心部件,采用CPLD 器件作为核心处理电路,用EPM7128进行控制,能较好地减小外界干扰,提高分辨率。

采用ADC0809作为数据的采样模块,来进行直流采样。

通过用EPM7128进行控制,在通过LG5641H ,进行7段式数码管显示,显示采集到的直流数据。

另外还设置了一块51芯片,以备控制芯片容量不够时使用。

【关键词】:数据采集 、 直流采样 、 7段数码管显示一、项目背景(创作意图)由于本身就是电信专业的,在之后的课程中也会学习到相应的CPLD 原理,还有VHDL 编程,想通过这样的小制作来提高自己的学习能力和专业技术。

所以也选择了相对比较简单的直流数据采集来进行,即能提高自己也能不拉下学习,也是为了能尽可能的了解一些社会需要的知识。

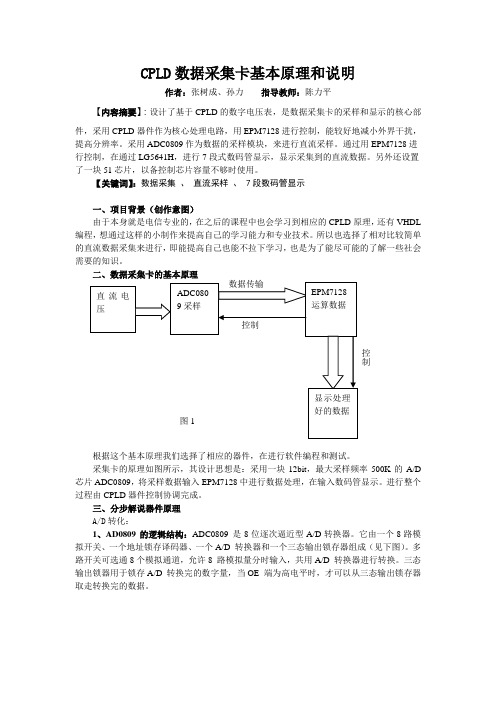

二、数据采集卡的基本原理根据这个基本原理我们选择了相应的器件,在进行软件编程和测试。

采集卡的原理如图所示,其设计思想是:采用一块12bit ,最大采样频率500K 的A/D 芯片ADC0809,将采样数据输入EPM7128中进行数据处理,在输入数码管显示。

进行整个过程由CPLD 器件控制协调完成。

三、分步解说器件原理A/D 转化:1、AD0809 的逻辑结构:ADC0809 是8位逐次逼近型A/D 转换器。

它由一个8路模拟开关、一个地址锁存译码器、一个A/D 转换器和一个三态输出锁存器组成(见下图)。

多路开关可选通8个模拟通道,允许8 路模拟量分时输入,共用A/D 转换器进行转换。

三态输出锁器用于锁存A/D 转换完的数字量,当OE 端为高电平时,才可以从三态输出锁存器取走转换完的数据。

数据传输 直流电压 ADC0809采样 EPM7128运算数据 显示处理好的数据 控制 控制图12、AD0809 的工作原理IN0-IN7:8 条模拟量输入通道ADC0809 对输入模拟量要求:信号单极性,电压范围是0-5V,地址输入和控制线:4条。

一种新型基于CPLD的多通道数据采集卡的设计与实现的开题报告引言:多通道数据采集系统在现代工业自动化中应用广泛,由于其实时性、高精度、强鲁棒性和自动化程度高等特点,已成为自动化领域中得到广泛应用的一种技术。

在多通道数据采集系统中,硬件平台和软件平台是基础,其中硬件平台是数据采集系统的重要组成部分。

本文重点研究了一种新型基于CPLD的多通道数据采集卡的设计与实现。

一、研究背景:多通道数据采集卡主要用于实时采集多种参数信号,包括电压、电流、温度、压力、流量等。

目前市场上常见的数据采集卡通常采用单片机或DSP处理器作为主控芯片,这些芯片的处理能力受到限制,无法满足高速采集、高精度采集等需求。

而CPLD作为一种可编程逻辑器件,其优势在于具有高速、低功耗、低成本和可编程等特点,能够满足高速、高精度和大容量数据处理的需求。

因此,本文研究基于CPLD的多通道数据采集卡,旨在提高数据采集系统的性能和稳定性。

二、研究内容:本文研究的内容主要包括以下方面:1.多通道信号采集模块设计多通道信号采集模块是多通道数据采集卡的主要组成部分。

本文研究设计一种基于CPLD的多通道信号采集模块,能够实时采集多种参数信号,并将其转换为数字信号进行处理。

2.CPLD设计与编程本文采用Xilinx公司的XC95108 CPLD作为主控芯片,设计了CPLD 的硬件电路,并使用HDL语言进行CPLD的编程,以实现多通道信号采集和数据处理功能。

3.与上位机通信接口设计本文设计了与上位机通信的接口,实现了数据的传输和实时监测。

同时,本文还借助LabView软件,实现了可视化操作界面,并进行了相关的性能测试和分析。

三、研究意义:本文研究了一种基于CPLD的多通道数据采集卡的设计与实现,对于提高数据采集系统的性能和稳定性具有重要意义。

该研究能够为相关领域的工程技术人员提供一种新型的数据采集方案,提高数据采集系统的可靠性和灵活性,为实现智能化、自动化和信息化提供技术支持和保障。

基于CPLD的高速数据采集系统的设计与实现摘要:高速数据采集系统在信息科学的各个领域中应用越来越广泛,而基于单片机、ARM的数据采集技术已经很成熟,在对速度要求越来越苛刻的当代社会,这些技术已经显得有些力不从心,我们必须开发新的更高速的数据采集系统才能跟上信息产业发展的脚步,而随着可编程逻辑器件这些年来的迅猛发展,它以其极高的集成度,稳定的性能以及高速、易用的特点,在信息科学的各个领域都得到了广泛的应用,本文提出了一种基于CPLD的高速数据采集系统的设计方法。

关键词:基于CPLD;高速数据;采集系统;设计与实现1、前言数据采集技术是数字系统的重要部分,它与传感器技术、信号处理技术、计算机技术一起构成了现代检测技术的基础。

目前数据采集系统已经被广泛的应用。

在很多实际应用中,传统的采集系统已经不能满足采集要求,需要采样速度很高的甚至是超高采集系统。

本文提出了一种基于CPLD的高速数据采集系统的设计方法。

通过CPLD控制数据连续采集、缓冲,然后通过MCU(C8051F430)读取缓存在SRAM中数据,并且通过USB2.0将缓冲区数据转移到硬盘管理卡,由硬盘管理卡将数据存入海量硬盘。

再利用PC机的强大数据处理功能,MicrosoftVisualC++6.0的MFC类库,设计出一套集数据采集、处理和分析的高速数据采集的可视化系统。

2、系统结构设计本文设计的高速数据采集系统主要由数据采集、数据显示处理和数据传输接口三部分组成。

数据采集系统要解决的问题主要是数据的采集和传输问题。

为了增强设计的灵活性和可扩展性,系统采用CPLD来实现对AD转换器、数据缓存器SRAM、时钟、数据传输的控制逻辑。

系统功能框图如图1。

图1如上图所示,数据采集方案采用的是:带USB2.0控制器的高速单片机+USB传输的方式,目前有一款非常好的自带USB2.0控制器,并且具有51内核的高效率单片机C8051F340,这款单片机的执行速度可达到25MHz,且不用分频,故选用它可高速传输数据到PC机的同时,还可以对RAM进行读取控制。

一种基于CPLD和USB接口的数据采集卡设计本文设计了一种基于CPLD和USB接口的通用数据采集卡,采用AD7606芯片进行数据采集,以CPLD作为主控芯片,通过CY7C68013A芯片与计算机完成USB通信,实现数据传输,上位机程序采用LabVIEW软件进行开发。

【关键词】AD7606 CPLD USB接口数据采集卡LabVIEW1 前言数据采集系统一般由由传感器、数据采集卡和带有可编程软件的计算机组成。

基于计算机的数据采集系统利用行业标准计算机的处理、显示和连通能力,能够灵活方便且低成本地实现满足用户需要测量方案。

数据采集卡就是实现数据采集功能的计算机扩展卡,数据采集卡接口种类有很多,例如PCI、ISA、PXI、RS-232等。

这些都属于传统接口,体积较大,不支持热插拔,缺点比较明显。

USB接口能够完美解决上述问题,因此本文采用USB接口设计数据采集卡。

2 系统硬件设计本文所设计的USB数据采集卡主要包括以下模块:A/D 模块、主控模块和USB模块。

A/D模块主要负责采集信号,然后将信号发送给主控模块。

主控模块主要负责控制A/D模块的A/D芯片完成采集,然后将数据写入到USB芯片的FIFO缓存区中。

USB模块主要负责与计算机进行通信,当FIFO缓存区满时,将数据发送给计算机。

如图1所示为USB数据采集卡的系统框图。

3 系统模块介绍3.1 A/D模块USB数据采集卡的A/D模块采用的是AD7606芯片,AD7606是ADI公司推出的8通道数据采集系统(DAS),该芯片具有16位分辨率,采样频率达到200K,通过5V单电源进行供电,可以采集±10V或±5V的输入信号,具有片内过压保护功能。

AD7606具有片内滤波和高输入阻抗,因此无需驱动运算放大器和外部双极性电源,可简化电路设计。

3.2 主控模块USB数据采集卡的主控模块采用的是EPM1270芯片,EPM1270芯片是Altera公司MAX II系列的CPLD芯片,CPLD 是复杂可编程逻辑器件的简称,传统的CPLD是由PAL、GAL 器件发展而来。

基于CPLD 的电网过电压变频数据采集卡设计杜 林,刘伟明,王有元,司马文霞(重庆大学输配电装备及系统安全与新技术国家重点实验室,重庆400044)摘 要:为了解决过电压信号数据采集的采样长度与存储容量之间的矛盾,提出了一种过电压变频数据采集卡的设计与实现方法,介绍了采集卡的硬件结构、采样原理和软件设计思想。

采集卡采用复杂可编程逻辑器件作为控制核心芯片,其预触发变频采样技术可以保证以较小容量存储器记录完整的电力系统暂态信号。

现场运行经验表明,该采集卡性能稳定可靠,能够较好的记录电力系统过电压的真实情况。

关键词:电网;过电压;在线监测;数据采集;复杂可编程逻辑器件;预触发采样;变频采样中图分类号:TM866文献标志码:A 文章编号:100326520(2008)0821589205基金资助项目:重庆市科委自然科学基金重点项目Data Acquisition C ard with V ariable Sampling Speedfor Monitoring Overvoltage B ased on CPLDDU Lin ,L IU Wei 2ming ,WAN G Y ou 2yuan ,SIMA Wen 2xia(State Key Laboratory of Transmission &Dist ribution Equip ment and Power System Safety andNew Technology ,Chongqing University ,Chongqing 400044,China )Abstract :Overvoltage is a critical factor which influences the security of the power system.It is necessary to re 2search overvoltage so as to guarantee safe operation of power grid.The data acquisition is one of key techniques in the on 2line monitoring system for overvoltage.A remarkable difference between external overvoltage and internal overvoltage in power system sets a higher demand for data acquisition.In order to solve the contradiction of sam 2pling length and storage capacity ,an implementation of data acquisition card with variable sampling speed for over 2voltage is proposed.Hardware structure ,the principle of data sampling and the software design of CPLD is intro 2duced.The data acquisition card employs the complex programmable logic device (CPLD )as the main control chip.With unique pre 2trigger acquisition f unction ,the data acquisition card can restore the waveforms before the power grid fault happening.And with variable sampling speed technique ,the data acquisition card can sample and record the f ull transient signals in power system with smaller memory capacity.The field operation experiences show that the data acquisition card features stable and reliable performance and can record the real overvoltage waveform of power system.K ey w ords :power grid ;overvoltage ;on 2line monitoring ;data acquisition ;CPLD ;pre 2trigger acquisition ;variable sampling speed0 引 言电力系统的工作可靠性与其绝缘水平和过电压大小密切相关。

基于CPLD的数据采集与显示接口电路仿真设计称为复杂可编程规律设计芯片,它是大规模可编程器件,具有高集成度、高牢靠性、高速度的特点。

CPLD是利用技术举行系统设计的载体。

硬件描述语言是EDA技术举行电子系统设计的主要表达手段,语言是常用的硬件描述语言之一;软件开发工具是利用EDA技术举行电子系统设计的智能化的设计工具,常用开发工具有Ⅱ,Ispexpert,Foundation等。

CPLD以高速、高牢靠性、串并行工作方式等特点在电子设计中广泛应用。

它打破了软硬件之间的界限,加速了产品的开发过程。

同样具有性价比高、功能灵便、良好的数据处理能力等特点。

CPLD芯片与单片机结合在高性能仪器仪表中应用广泛。

1 的设计1.1 硬件电路功能用一片MCS-51芯片、一片CPLD/芯片、模/数转换器0809和数/模转换器0832构成一个数据采集系统,并用CPLD/FPGA实现数据采样、D/A转换输出、有关数据显示的控制,单片机完成对A/D转换数据运算。

电路1所示。

系统功能如下:系统按一定速率采集输入U1,经AD0809转换为8位数字量data;输入数据与通过CPLD/FPGA采样后输入单片机举行相关运算,最后通过CPLD/FPGA送至DAC0832转换为△U;数据采集和处理均在数据采集系统控制器的管理下有序举行。

工作速率由时钟信号CLK的速率打算。

1.2 单片机与CPLD/FPGA接口设计单片机采纳以方式与可编程芯片举行数据与控制信息通信,此方式有许多优点:(1)速度快。

其通信工作时序是纯硬件行为,对于MCS-只需一条单字节命令就能完成所需的读/写时序如MOV@DPTR A和MOV A@DPTR。

第1页共6页。