07-锁相环时钟的抖动

- 格式:pdf

- 大小:163.99 KB

- 文档页数:4

时钟抖动的4大根本原因及3种查看途径时钟接口阈值区间附近的抖动会破坏ADC的时序。

例如,抖动会导致ADC在错误的时间采样,造成对模拟输入的误采样,并且降低器件的信噪比(SNR)。

降低抖动有很多不同的方法,但是,在get降低抖动的方法前我们必须找到抖动的根本原因!时钟抖动,why?时钟抖动的根本原因就是时钟和ADC之间的电路噪声。

随机抖动由随机噪声引起,主要随机噪声源包括· 热噪声(约翰逊或奈奎斯特噪声),由载流子的布朗运动引起。

· 散粒噪声,与流经势垒的直流电流有关,该势垒不连续平滑,由载流子的单独流动引起的电流脉冲所造成。

· 闪烁噪声,出现在直流电流流动时。

该噪声由携带载流子的半导体中的陷阱引起,这些载流子在释放前通常会形成持续时间较短的直流电流。

· 爆裂噪声,也称爆米花噪声,由硅表面的污染或晶格错位造成,会随机采集或释放载流子。

查看时钟信号噪声,how?确定性抖动由干扰引起,会通过某些方式使阈值发生偏移,通常受器件本身特性限制。

查看时钟信号噪声通常有三种途径:时域、频域、相位域。

咳咳,敲黑板划重点,以上三种途径的具体方法如下↓↓↓时域图图1. 抖动的时域图时钟抖动是编码时钟的样本(不同周期)间的变化,包括外部和内部抖动。

抖动引起的满量程信噪比由以下公式得出举个栗子,频率为1 Ghz,抖动为100 FS均方根值时,信噪比为64 dB。

在时域中查看时,x轴方向的编码边沿变化会导致y轴误差,幅度取决于边沿的上升时间。

孔径抖动会在ADC输出产生误差,如图2所示。

抖动可能产生于内部的ADC、外部的采样时钟或接口电路。

图2. 孔径抖动和采样时钟抖动的影响图3显示抖动对信噪比的影响。

图中显示了5条线,分别代表不同的抖动值。

x轴是满量程模拟输入频率,y轴是由抖动引起的信噪比,有别于ADC总信噪比。

图3. 时钟抖动随模拟信号增大而提升信噪比由抖动引起的信噪比和有效位数(ENOB)的关系由以下公式定义:SNR = 6.02 N + 1.76 dB其中N =有效位数。

时钟生成电路中锁相环的作用锁相环(Phase-Locked Loop,简称PLL)是一种常用于时钟生成电路中的重要电路,它的作用是使输出时钟信号与输入参考信号保持相位一致。

在现代电子设备中,时钟信号的稳定性对于保证系统性能至关重要,而锁相环正是通过自身的反馈控制机制,实现了高精度和稳定的时钟生成。

锁相环的作用可以从多个方面来解释。

首先,锁相环可以将输入的不稳定时钟信号进行整形和稳定化处理,产生一个相位准确、频率稳定的输出时钟信号。

其原理是通过比较输入时钟信号和反馈信号的相位差,并根据相位差的大小来调整输出时钟信号的频率和相位,使其逐渐与输入参考信号保持一致。

因此,锁相环可以有效消除输入时钟信号的抖动和漂移,提供稳定可靠的时钟信号给后续的电路模块使用。

锁相环还可以实现时钟信号的倍频或分频功能。

通过调整锁相环中的除数和乘法器的参数,可以实现将输入时钟信号的频率放大或缩小到需要的范围。

这对于不同模块之间的时钟频率转换非常有用,可以提高系统的灵活性和兼容性。

锁相环还可以实现时钟信号的相位同步。

在一些需要多个时钟信号同步工作的系统中,锁相环可以将不同模块的时钟信号进行相位调整,使它们在某个特定的相位关系下工作。

这对于实现数据的准确采样和处理非常重要,可以避免因时钟相位不一致而引起的数据错误和时序问题。

除了以上的基本功能,锁相环在实际应用中还有许多衍生和扩展的功能。

例如,锁相环可以通过引入额外的相位调整电路,实现对输入信号相位的连续调节,从而达到相位延迟或相位提前的效果。

这在一些需要实时调整相位的应用中非常有用,如通信系统中的相位调制和解调。

锁相环还可以通过引入滤波器和自适应控制算法,提高系统对噪声和干扰的抑制能力,进一步提高时钟信号的稳定性和抗干扰能力。

这对于提高系统的抗干扰性和抗噪声性能非常重要,尤其是在高速通信和精密测量等领域。

锁相环在时钟生成电路中的作用是非常重要的。

它可以实现时钟信号的整形、稳定化和倍频分频,实现时钟信号的相位同步,并具备一定的相位调节和抗干扰能力。

PLL(锁相环)在计算抖动时,需要考虑的频率范围通常包括以下几个主要部分:

1. 输入信号频率:这是PLL输入的信号频率,通常在数兆赫兹(MHz)或更高。

2. VCO(压控振荡器)频率范围:VCO是PLL的一个重要组成部分,其频率范围决定了PLL的输出频率范围。

通常,VCO 的频率范围可以达到数十兆赫兹至数百兆赫兹。

3. 分频器(Divider)设置:分频器用于将VCO的输出频率分频,以匹配输入信号频率。

分频器的设置会影响PLL的频率范围。

4. 抖动频率范围:抖动是由于PLL内部噪声和非理想特性导致的输出信号频率的微小变化。

抖动频率范围通常在数赫兹至数兆赫兹之间,取决于PLL的具体实现和应用。

总之,在计算PLL抖动时,需要考虑的频率范围包括输入信号频率、VCO频率范围、分频器设置和抖动频率范围。

这些因素共同决定了PLL在特定应用中的性能和稳定性。

锁相环指标-回复什么是锁相环指标?锁相环指标是指用来衡量锁相环(Phase-Locked Loop,PLL)性能的各种参数和指标。

PLL是一种电路系统,通过对输入信号的相位进行比较,并根据比较结果调整本身输出信号的相位,从而使输出信号保持与输入信号的相位同步。

在各种通信、控制和测量领域,PLL已经广泛应用。

而锁相环指标则是评估PLL工作性能和稳定度的重要依据。

有哪些常见的锁相环指标?实际上,锁相环的指标非常多,并且根据具体应用的不同可能略有差异。

下面列举几个常见的锁相环指标:1. 锁定时间(Lock time):指PLL从失锁状态转变为锁定状态所需要的时间。

锁定时间短是衡量PLL性能和适用性的重要指标之一。

2. 锁定范围(Lock range):指PLL在输入信号频率范围内能够保持稳定锁定的能力。

通常用频率范围或相位范围来表示。

3. 噪声性能(Noise performance):指PLL对输入信号中的噪声和扰动的抵抗能力。

好的锁相环应该能够在抑制噪声的同时保持输出信号的稳定性。

4. 抖动(Jitter):指信号在时间上的不稳定性,可以通过锁相环来降低抖动。

抖动越小,表明锁相环性能越好。

5. 相位噪声(Phase noise):指锁相环输出信号相位随时间的变化情况。

相位噪声小的锁相环输出信号更加稳定。

6. 频率稳定度(Frequency stability):指锁相环输出信号频率的变化程度。

频率稳定度好的锁相环输出信号与输入信号的频率差距很小。

以上仅为锁相环指标中的几个常见要素,根据不同应用的需求,可能还会有其他更具体的指标。

锁相环指标如何优化?优化锁相环指标是实际应用中非常重要的任务,因为合理的指标设计和优化可以提高PLL的性能,提高系统的可靠性和稳定性。

1. 设计合适的环路带宽:适当选择环路带宽可以平衡相位噪声和锁定时间的要求。

过高的带宽容易引入噪声,过低的带宽又会增加锁定时间。

2. 添加滤波器:通过添加滤波器来抑制输入信号中的噪声和频率扰动,从而提高锁相环的噪声性能和稳定性。

微电子电路中的时钟信号抖动分析与优化方法研究引言:时钟信号在微电子电路中起着至关重要的作用,它是整个系统的节拍,负责同步各个模块的工作。

然而,由于各种因素的干扰,时钟信号会产生抖动,导致系统性能下降。

因此,对时钟信号的抖动进行分析和优化成为微电子电路设计中的重要课题。

一、时钟信号抖动的来源时钟信号抖动是指时钟信号的周期性变化,主要有以下几个来源:1. 环境干扰:温度变化、电磁辐射等环境因素会对时钟信号产生影响,导致抖动。

2. 电源噪声:电源的不稳定性会引起时钟信号的抖动。

3. 器件非线性:微电子器件的非线性特性会对时钟信号产生影响,引起抖动。

4. 时钟信号传输线路:传输线路的噪声、阻抗不匹配等因素也会导致时钟信号的抖动。

二、时钟信号抖动的影响时钟信号抖动对微电子电路的性能有着重要的影响,主要体现在以下几个方面:1. 时序错误:时钟信号抖动会导致时序错误,使得电路无法按照设计要求正常工作。

2. 时钟偏移:时钟信号抖动会引起时钟频率的偏移,导致电路的时钟周期不稳定。

3. 噪声干扰:时钟信号抖动会引入噪声,影响电路的信号完整性和稳定性。

4. 能耗增加:时钟信号抖动会导致电路频繁切换,增加功耗。

三、时钟信号抖动分析方法为了准确分析时钟信号的抖动情况,可以采用以下几种方法:1. 时钟抖动测量仪器:使用专门的时钟抖动测量仪器,通过测量时钟信号的抖动参数,如峰峰值、均方根值等,来评估抖动情况。

2. 时钟抖动仿真工具:利用电路仿真软件,对时钟信号进行仿真分析,得到时钟信号的波形和频谱,进而分析抖动情况。

3. 时钟抖动模型:建立时钟信号的抖动模型,通过数学方法进行分析,得到时钟信号的抖动特性。

四、时钟信号抖动优化方法为了降低时钟信号的抖动,可以采用以下几种优化方法:1. 电源和地线设计:合理设计电源和地线,减小电源噪声对时钟信号的影响。

2. 环境隔离:采用屏蔽罩、隔离层等措施,减少环境因素对时钟信号的干扰。

3. 时钟信号传输线路设计:采用匹配阻抗、减小传输线路长度等措施,降低传输线路对时钟信号的影响。

锁相环指标-回复什么是锁相环指标?锁相环(PLL)是一种电子反馈系统,用于调节信号的频率和相位。

锁相环指标是用来描述锁相环性能的量化指标。

锁相环指标通常包括锁定时间、锁定范围、抖动、输入偏置等。

锁相环指标的详细解释如下:1. 锁定时间:锁相环的锁定时间是指从输入信号发生变化到锁相环稳定在新的输出状态所需要的时间。

锁定时间越短,锁相环的响应速度越快。

2. 锁定范围:锁相环的锁定范围是指锁相环能够跟踪的输入信号的频率范围。

锁定范围越广,锁相环适应不同频率的输入信号能力越强。

3. 抖动:锁相环的抖动是指输出信号在稳定锁定状态下的频率和相位误差。

抖动越小,锁相环的稳定性和精度越高。

4. 输入偏置:锁相环的输入偏置是指输入信号与锁相环内部参考信号之间的相位差。

输入偏置越小,锁相环的跟踪效果越好。

为何需要锁相环指标?锁相环指标对于电子系统设计和应用至关重要。

它们是评估锁相环性能和判断锁相环是否满足系统需求的依据。

锁相环指标的合理选择可以确保系统的稳定性、精度和实时性。

以移动通信系统为例,锁相环指标的好坏直接影响信号的传输、检测和处理。

在无线通信中,移动信号的频率、相位和稳定性要求非常高,锁相环用于调整持续变化的信号以保持稳定性。

如果锁相环指标不达标,信号将可能失真、丢失或传输不及时。

如何评估锁相环指标?评估锁相环指标需要进行一系列测试和分析。

常见的锁相环指标测试方法有以下几种:1. 测试锁定时间:在输入信号变化时,观察输出信号的响应时间。

多次测试并取平均值以获得可靠的结果。

2. 测试锁定范围:逐渐改变输入信号的频率,观察锁相环的跟踪能力和输出信号的稳定性。

一般使用频谱仪或示波器进行测试。

3. 测试抖动:使用高精度的频率计或相位计对输出信号进行测量,计算其频率和相位误差。

抖动可以通过信号处理和滤波来减小。

4. 测试输入偏置:输入一个稳定的参考信号和待测试信号,测量两者的相位差。

使用示波器或均衡器等仪器进行测量。

锁相环常见问题解答锁相环常见问题解答下载本期常见问题解答(PDF,596KB)参考晶振有哪些要求?我该如何选择参考源?请详细解释⼀下控制时序,电平及要求?控制多⽚PLL芯⽚时,串⾏控制线是否可以复⽤?请简要介绍⼀下环路滤波器参数的设置?环路滤波器采⽤有源滤波器还是⽆源滤波器?PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器?如何设置电荷泵的极性?锁定指⽰电路如何设计?PLL对射频输⼊信号有什么要求?PLL芯⽚对电源的要求有哪些?内部集成了VCO的ADF4360-x,其VCO中⼼频率如何设定?锁相环输出的谐波?锁相环系统的相位噪声来源有哪些?减⼩相位噪声的措施有哪些?为何我测出的相位噪声性能低于ADISimPLL仿真预期值?锁相环锁定时间取决于哪些因素?如何加速锁定?为何我的锁相环在做⾼低温试验的时候,出现频率失锁?⾮跳频(单频)应⽤中,最⾼的鉴相频率有什么限制?频繁地开关锁相环芯⽚的电源会对锁相环有何影响?您能控制PLL芯⽚了么?,R分频和N分频配置好了么?您的晶振输出功率有多⼤?VCO的输出功率有多⼤?您的PFD鉴相极性是正还是负?您的VCO输出频率是在哪⼀点?最低频率?最⾼频率?还是中间的某⼀点?VCO的控制电压有多⼤?您的PLL环路带宽和相位裕度有多⼤?评价PLL频率合成器噪声性能的依据是什么?⼩数分频的锁相环杂散的分布规律是什么?到底⽤⼩数分频好还是整数分频好?ADI提供的锁相环仿真⼯具ADISimPLL⽀持哪些芯⽚,有什么优点?分频–获得⾼精度时钟参考源?PLL,VCO闭环调制,短程⽆线发射芯⽚?PLL,VCO开环调制?时钟净化----时钟抖动(jitter)更⼩?时钟恢复(Clock Recovery)?问题:参考晶振有哪些要求?我该如何选择参考源?答案:波形:可以使正弦波,也可以为⽅波。

功率:满⾜参考输⼊灵敏度的要求。

稳定性:通常⽤TCXO,稳定性要求< 2 ppm。

时钟抖动定义与测量方法引言以5G无线技术、电动汽车和先进移动设备为代表的应用大趋势正影响着全球社会,并将重塑未来的各个产业。

这些大趋势为电子产品,尤其是传感器和MEMS,提供了巨大的商机。

SiTime作为MEMS时钟解决方案的领先供应商,已经出货超过20亿颗MEMS时钟器件,拥有超过90%的MEMS时钟器件市场份额.。

SiTime的使命是为5G通讯、移动物联网、汽车和工业市场的客户解决最具挑战的时钟问题。

1、抖动的定义今天我们就来聊聊时钟抖动的定义与测量方法抖动是时钟信号边沿事件的时间点集合相对于其理想值的离散时序变量。

时钟信号中的抖动通常是由系统中的噪声或其他干扰导致的。

具体因素包括热噪声、电源变化、负载条件、器件噪声以及相邻电路耦合的干扰等。

2、抖动类型时钟信号抖动定义有多种主要如下:周期抖动(Period Jitter)相邻周期抖动(Cycle to Cycle Period Jitter)长期抖动 (Long Term Jitter)相位抖动 (Phase Jitter)时间间隔误差 (Time Interval Error or TIE)2.1 周期抖动周期抖动是时钟信号的周期时间相对于一定数量、随机选定的理想时钟信号周期的偏差。

如果我们能对一定数量的时钟周期进行测量,就可以计算出这一段时间测量窗口内的平均时钟周期以及其标准偏差与峰峰值。

我们通常将标准偏差和峰峰值分别称作RMS 值和Pk-Pk 周期抖动。

许多已发表的文献中往往将周期抖动定义为测得的时钟周期与理想周期之间的差异,但在实际应用中,想要量化理想周期往往有困难。

如果用示波器观察设定频率为 100 MHz 的振荡器的输出,测得的平均周期可能是9.998 ns,而非理想周期的10 ns。

因此,在实际测量中可将测量时间窗口内的平均周期视为理想周期。

2.1.1 周期抖动应用周期抖动在数字系统中的时序冗余度计算方面非常实用。

例如,在一个基于微处理器的系统中,处理器在时钟上升之前需要 1 ns的数据建立时间。

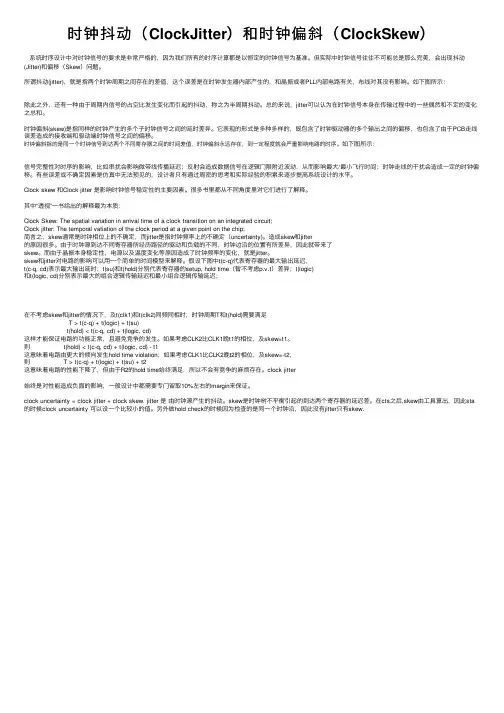

时钟抖动(ClockJitter)和时钟偏斜(ClockSkew)系统时序设计中对时钟信号的要求是⾮常严格的,因为我们所有的时序计算都是以恒定的时钟信号为基准。

但实际中时钟信号往往不可能总是那么完美,会出现抖动(Jitter)和偏移(Skew)问题。

所谓抖动(jitter),就是指两个时钟周期之间存在的差值,这个误差是在时钟发⽣器内部产⽣的,和晶振或者PLL内部电路有关,布线对其没有影响。

如下图所⽰:除此之外,还有⼀种由于周期内信号的占空⽐发⽣变化⽽引起的抖动,称之为半周期抖动。

总的来说,jitter可以认为在时钟信号本⾝在传输过程中的⼀些偶然和不定的变化之总和。

时钟偏斜(skew)是指同样的时钟产⽣的多个⼦时钟信号之间的延时差异。

它表现的形式是多种多样的,既包含了时钟驱动器的多个输出之间的偏移,也包含了由于PCB⾛线误差造成的接收端和驱动端时钟信号之间的偏移。

时钟偏斜指的是同⼀个时钟信号到达两个不同寄存器之间的时间差值,时钟偏斜永远存在,到⼀定程度就会严重影响电路的时序。

如下图所⽰:信号完整性对时序的影响,⽐如串扰会影响微带线传播延迟;反射会造成数据信号在逻辑门限附近波动,从⽽影响最⼤/最⼩飞⾏时间;时钟⾛线的⼲扰会造成⼀定的时钟偏移。

有些误差或不确定因素是仿真中⽆法预见的,设计者只有通过周密的思考和实际经验的积累来逐步提⾼系统设计的⽔平。

Clock skew 和Clock jitter 是影响时钟信号稳定性的主要因素。

很多书⾥都从不同⾓度⾥对它们进⾏了解释。

其中“透视”⼀书给出的解释最为本质:Clock Skew: The spatial variation in arrival time of a clock transition on an integrated circuit;Clock jitter: The temporal vatiation of the clock period at a given point on the chip;简⾔之,skew通常是时钟相位上的不确定,⽽jitter是指时钟频率上的不确定(uncertainty)。

摘要:本文简要介绍了时钟的抖动定义、各种抖动的应用范围、抖动的分解和基于示波器的测量与分析方法。

时钟是广泛用于计算机、通讯、消费电子产品的元器件,包括晶体振荡器和锁相环,主要用于系统收发数据的同步和锁存。

如果时钟信号到达接收端时抖动较大,可能出现:并行总线中数据信号的建立和保持时间余量不够、串行信号接收端误码率高、系统不稳定等现象,因此时钟抖动的测量与分析非常重要。

时钟抖动的分类与定义时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。

TIE又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。

理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟。

Period Jitter是多个周期内对时钟周期的变化进行统计与测量的结果。

Cycle to cycle jitter是时钟相邻周期的周期差值进行统计与测量的结果。

对于每一种时钟抖动进行统计和测量,可以得到其抖动的峰峰值和RMS值(有效值),峰峰值是所有样本中的抖动的最大值减去最小值,而RMS值是所有样本统计后的标准偏差。

如下图1为某100M时钟的TIE、Period Jitter、Cycle to Cycle jitter 的峰峰值和RMS值的计算方法。

图1:三种时钟抖动的计算方法时钟抖动的应用范围在三种时钟抖动中,在不同的应用范围需要重点测量与分析某类时钟抖动。

TIE抖动是最常用的抖动指标,在很多芯片的数据手册上通常都规定了时钟TIE抖动的要求。

对于串行收发器的参考时钟,通常测量其TIE抖动。

如下图2所示,在2.5Gbps的串行收发器芯片的发送端,参考时钟为100MHz,锁相环25倍频到2.5GHz后,为Serializer (并行转串行电路)提供时钟。

当参考时钟抖动减小时,TX输出的串行数据的抖动随之减小,因此,需要测量该参考时钟的TIE抖动。

时钟的抖动及相噪分析动测量一直被称为示波器测试测量的最高境界。

传统最直观的抖动测量方法是利用余辉来查看波形的变化。

后来演变为高等数学概率统计上的艰深问题,抖动测量结果准还是不准的问题就于是变得更加复杂。

时钟的特性可以用频率计测量频率的稳定度,用频谱仪测量相噪,用示波器测量TIE抖动、周期抖动、cycle-cycle抖动。

但是时域测量方法和频域测量方法的原理分别是什么? TIE抖动和相噪抖动之间的关系到底是怎么推导的呢? ScopeArt先生就常遇到类似的问题,为此,特向本文作者主动邀稿。

作者是高人,但很低调。

他为此文花费了很多时间,最终奉献给大家的这篇文章很干货。

希望对仍然纠结在抖动的迷雾中的朋友们有所启发。

抖动是衡量时钟性能的重要指标,抖动一般定义为信号在某特定时刻相对于其理想位置的短期偏移。

这个短期偏移在时域的表现形式为抖动(下文的抖动专指时域抖动),在频域的表现形式为相噪。

本文主要探讨下时钟抖动和相噪以及其测量方法,以及两者之间的关系。

1、抖动介绍抖动是对时域信号的测量结果,反映了信号边沿相对其理想位置偏离了多少。

抖动有两种主要成分:确定性抖动和随机抖动。

确定性抖动是可以重复和预测的,其峰峰值是有界的,通常意义上的DJ是指其pk-pk值;随机抖动是不能预测的定时噪声,分析时一般使用高斯分布来近似表征,理论上可以偏离中间值无限大,所以随机抖动是没有峰到峰边界的,通常意义上的RJ指标是指其RMS值,可以根据其RMS值推算其在一定误码率时的值。

目前最常用的分析方法是使用双狄拉克模型。

该模型假定概率密度函数两侧的尾部是服从高斯分布的,高斯分布很容易模拟,并且可以向下推算出较低的概率分布。

总抖动是RJ和DJ概率密度函数的卷积。

但是,业界对于高斯分布能否精确地描绘随机抖动直方图的尾部还存在争议。

真正的随机抖动是遵守高斯分布的,但实际的测量中多个低幅度的DJ会卷积到一个分布函数,这导致测量出的概率密度分布的中心接近高斯分布,而尾部却夹杂了一些DJ。

时钟的抖动测量与分析时钟抖动的分类与定义时钟抖动通常分为时间间隔误差(Time Interval Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cycle to cycle jitter)三种抖动。

TIE又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量。

理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟。

Period Jitter是多个周期内对时钟周期的变化进行统计与测量的结果。

Cycle to cycle jitter是时钟相邻周期的周期差值进行统计与测量的结果。

对于每一种时钟抖动进行统计和测量,可以得到其抖动的峰峰值和RMS值(有效值),峰峰值是所有样本中的抖动的最大值减去最小值,而RMS值是所有样本统计后的标准偏差。

如下图1为某100M时钟的TIE、Period Jitter、Cycle to Cycle jitter的峰峰值和RMS值的计算方法。

图1:三种时钟抖动的计算方法时钟抖动的应用范围在三种时钟抖动中,在不同的应用范围需要重点测量与分析某类时钟抖动。

TIE抖动是最常用的抖动指标,在很多芯片的数据手册上通常都规定了时钟TIE抖动的要求。

对于串行收发器的参考时钟,通常测量其TIE抖动。

如下图2所示,在2.5Gbps的串行收发器芯片的发送端,参考时钟为100MHz,锁相环25倍频到2.5GHz后,为Serializer(并行转串行电路)提供时钟。

当参考时钟抖动减小时,TX输出的串行数据的抖动随之减小,因此,需要测量该参考时钟的TIE抖动。

另外,用于射频电路的时钟通常也需测量其TIE抖动(相位抖动)。

在并行总线系统中,通常重点关注period jitter和cycle to cycle jitter。

比如在共同时钟总线(common clock bus)中(如图3所示),完整的数据传输需要两个时钟脉冲,第一个脉冲用于把数据锁存到发送芯片的IO Buffer,第二个脉冲将数据锁存到接收芯片中,在一个时钟周期内让数据从发送端传送到接收端,当发送端到接收端传输延迟(flight time)过大时,数据的建立时间不够,传输延迟过小时,数据的保持时间不够;同理,当这一个时钟的周期值偏大时,保持时间不够;周期值偏小时,建立时间不够。

基于改进延迟锁相环的高速低抖动时钟电路的开发与设计沈学锋【期刊名称】《电子设计工程》【年(卷),期】2016(024)009【摘要】文中针对传统时钟产生电路精度低且抖动大的问题,开发与设计了一种基于改进延迟锁相环的时钟电路。

电路仿真结果表明,当输入时钟信号频率为20~150 MHz 时,输出时钟信号占空比稳定在(50±0.15)%,时钟抖动在0.8 ps之内,不仅实现了精度的增大,且还具有低抖动的功能,满足了高速高精度 ADC转换器的时钟要求。

%In this paper, a clock generating circuit based on the improved PLL clock circuit is developed and designedfor the low precision and high jitter of the traditional clock circuit. And the circuit simulation results show that when the input clock signal frequency is 20 MHz to 150 MHz, the output clock signal duty cycle stabilizer in (50 ± 0.15)%, and clock jitter is under 0.8 ps. It not only achieve increased accuracy, but also has low shake function, to meet the high-speed high-precision ADC converter clock requirements.【总页数】4页(P48-50,53)【作者】沈学锋【作者单位】中国石油大学华东胜利学院,山东东营 257061; 中国石油大学华东信息与控制工程学院,山东东营 257061【正文语种】中文【相关文献】1.一种应用于TDC的低抖动延迟锁相环电路设计 [J], 吴金;张有志;赵荣琦;李超;郑丽霞2.基于FPGA的低抖动时钟锁相环设计方法 [J], 安书董;李明;王宛人;吴波;索晓杰3.250 MHz 时钟产生电路中低抖动锁相环的仿真与设计 [J], 高静;王彬;张晰泊;姚素英4.用于高速模数转换器的电荷泵型低抖动时钟管理电路 [J], 李楠楠; 黄正波; 季惠才; 盛炜; 张鸿5.用于时钟恢复电路的低抖动可变延迟线锁相环电路 [J], 李曙光;朱正;郭宇华;任俊彦因版权原因,仅展示原文概要,查看原文内容请购买。

第53卷 第12期2020年12月通信技术Communications Technology Vol.53 No.12Dec. 2020·3116·文献引用格式:冯景, 张繁. 一种降低时钟锁相环抖动的技术研究[J].通信技术,2020,53(12):3116-3121.FENG Jing, ZHANG Fan. Technique Research for Reducing PLL Jitter [J].CommunicationsTechnology,2020,53(12):3116-3121.doi:10.3969/j.issn.1002-0802.2020.12.037一种降低时钟锁相环抖动的技术研究*冯 景1,张 繁2(1.亿嘉和科技股份有限公司,江苏 南京 210012; 2.上海诺基亚贝尔股份有限公司,江苏 南京 210037)摘 要:高速SERDES 串行器内部锁相环的参考时钟有严格的要求,根据某25Gbps 数据率SERDES 芯片的156.25MHz 参考时钟的随机抖动均方差要求,进行锁相环电路设计,根据实测结果,对降低时钟锁相环抖动方案进行技术研究,通过时钟锁相环电路设计优化,从而得到低抖动锁相环优化配置方案。

关键词:SERDES;随机抖动均方差;锁相环;抖动中图分类号:TN79+1 文献标识码:A 文章编号:1002-0802(2020)-12-3116-06Technique Research for Reducing PLL JitterFENG Jing 1, ZHANG Fan 2(1.YIJIAHE Technology Co. Ltd., Nanjing Jiangsu 210012, China; 2.Shanghai Nokia Bell Co. Ltd., Nanjing Jiangsu 210037, China)Abstract: The reference clock of PLL (phase-locked loop) inside the high-speed SERDES Serializer has strict requirements. Based on the requirements of RMS jitter for 156.25MHz reference clock of a SERDES device with 25Gbps datarate, a PLL circuit design is done. According to the test results, a technical method for low PLL jitter is explored, and the PLL circuit design is optimized so as to acquire the most optimized PLL configruation method for low PLL jitter.Keywords: SERDES; RMS; PLL; jitter0 引 言随着通信和计算机技术的发展,数据传输速率不断提高, 高速SERDES(Serializer-Deserializer)数据率已经达到10Gbps 、25Gbps 或以上,在这些高速SERDES 系统中,都需要锁相环为其提供工作时钟。

锁相环时钟的抖动2008年11月22日

什么是抖动?如下图所示,抖动是信号和此刻信号理想位置相比短时间的变化。

这种输出信号从理想位置的偏离会给数据传输质量带来负面影响。

在很多情况下,其他的信号偏离,如信号偏差(signal skew),噪声耦合一起组合起来称作抖动。

偏离(用±ps来表示)可能发生在信号的上升沿或者下降沿。

时钟信号可能会由不同的源导致或者耦合而来,并且在不同频率也不一样。

抖动过大会不正确的传输数据流,增加通讯信号的误码率(BER)。

抖动会导致超过时序裕量,让电路不能正确工作。

为了确保系统的可靠性,精确测量抖动很有必要。

1. 抖动源

通常的抖动源包括:

锁相环的内部电路

晶振的随机热噪声

其他振荡器

晶振振荡的随机机械噪声

信号传输器

走线和电缆

接口

接收器

除了这些源,端接依赖,串扰,反射,趋肤效应,电源塌陷,地弹和临近设备的电磁串扰也会增加抖动量。

如果存在临近的同步同相,反射和串扰都会被放大。

除了电源和地导致的噪声,电路阻抗的变化是数据通讯电路中大部分抖动的来源。

2. 抖动的组成

抖动的2个主要组成部分是随机抖动(random jitter)和确定性抖动(deterministic jitter)

1) 随机抖动

随机抖动是由于电路内部内在的噪声造成的,典型的是呈现出高斯分布。

随机抖动(RJ)是由于随机源,如衬底和电源。

电源噪声影响信号的上升速率在切换点产生时序问题。

随机抖动是平方的和,呈现钟形曲线。

由于随机噪声没有边界,所以它的特性通过标准偏差来表示

2) 确定性抖动

确定性抖动依赖于数据样式(data pattern),来源于独立的源。

源通常和设备传输介质有关,但是也有可能由电源噪声,串扰和信号调制有关。

确定性抖动时线性的相加,它通常有特别的源。

确定性抖动没有按高斯随机分布,并且幅度有边界。

确定性抖动(DJ)的特性通过它的边界,峰峰值来表示。

3. 抖动的种类

抖动的种类有很多。

周期性抖动,周期间抖动,半周期间抖动将在下文具体描述。

1) 周期性抖动

周期性抖动是时钟输出转变时期(典型的是上升沿)和理想位置相比的变化。

周期性抖动用时间或者频率测量和表达。

周期性抖动测量用来计算系统中的时间裕量,如tSU和tCO。

2) 周期间抖动

周期间抖动是从一个时钟周期到下一个时钟周期之间的差别。

周期间抖动很难测量,通常要用时间间隔分析器。

如下图所示,J1和J2是测量的抖动值。

在多次测量中的最大值称作最大的周期间抖动。

3) 半周期间抖动

半周期抖动是测量是在一个周期到下半个周期时钟转变过程和理想位置对比的最大的改变。

图3所示为半周期间抖动。

4. 抖动的指标

锁相环的特性测量需要一些参数。

通常有3个指标来表示锁相环的特性,抖动生产,抖动容限,抖动传输。

1) 抖动生产

抖动生产是测量锁相环内在的抖动,在锁相环的输出测量。

抖动生产是通过一个没有抖动的信号作为参考,来测量输出的抖动。

抖动生产通常为周期抖动的峰值。

2) 抖动容限

抖动容限是测量在相对于基准频率情况下加入抖动情况下锁相环能正确运行的能力(例如,在不同频率的不同程度的抖动的情况下是否能保持锁定)。

抖动容限通常为输入抖动的掩码。

3) 抖动传输

抖动传输和抖动衰减基于输入不同的抖动时,输出的不同程度的抖动。

输入不同幅度和频率的抖动,输出用不同设置的带宽来测量。

因为内在抖动始终存在,低频抖动会比高频抖动的衰减低。

抖动传输典型为一个带宽图表。