ARM寄存器简介

- 格式:doc

- 大小:78.50 KB

- 文档页数:6

arm9处理器的内部寄存器结构

ARM9处理器是一种32位的嵌入式处理器,内部包含了多种寄存器,这些寄存器扮演着不同的角色,用于存储不同类型的数据和指令,从而实现处理器的各种功能。

ARM9处理器的内部寄存器结构主要包括:

1.通用寄存器:ARM9处理器有16个32位的通用寄存器,这些寄存器不仅可以用于存储数据,还可以用于存储指令中的操作数。

通用寄存器还可以用于存储函数的参数和返回值。

2.程序计数器(PC):程序计数器是一个32位的寄存器,用于存储当前正在执行的指令的地址。

当处理器执行完一条指令后,PC会自动递增,指向下一条指令的地址。

3.状态寄存器:状态寄存器用于存储处理器的当前状态。

例如,它可以用于存储处理器的运行模式,或者存储处理器的条件码。

4.堆栈指针(SP):堆栈指针用于指向当前的堆栈顶部。

当处理器需要执行函数调用或其他需要使用堆栈的指令时,它会将数据压入堆栈中,并将堆栈指针减小。

当函数返回时,处理器会将数据从堆栈中弹出,并将堆栈指针增加。

5.链接寄存器(LR):链接寄存器用于存储函数调用的返回地址。

当函数被调用时,处理器将当前指令的地址存储在LR中。

当函数执行完毕后,处理器会将LR中的地址作为返回地址,跳转回调用函数的地方。

6.中断寄存器:中断寄存器用于存储当前中断的状态。

当处理器

接收到一个中断时,它会将当前的状态保存在中断寄存器中,并跳转到中断处理程序的地址。

总之,ARM9处理器的内部寄存器结构是非常复杂的,不同类型的寄存器扮演着不同的角色。

通过合理地利用这些寄存器,程序员可以实现各种复杂的嵌入式应用。

ARM寄存器及功能介绍R0-R15寄存器1、ARM 寄存器组介绍ARM 处理器⼀般共有 37 个寄存器,其中包括:(1) 31 个通⽤寄存器,包括 PC(程序计数器)在内,都是 32 位的寄存器。

(2) 6 个状态寄存器,都是 32 位的寄存器。

ARM 处理器共有 7 种不同的处理器模式:⽤户模式(User),快速中断模式(FIQ),普通中断模式(IRQ),管理模式(Svc),数据访问中⽌模式(Abort),未定义指令中⽌模式(Und),系统模式(Sys),在每⼀种处理器模式中有⼀组相应的寄存器。

在任意⼀种处理器模式下,可见的寄存器包括 15 个通⽤寄存器(R0~R14)、⼀个或者⼆个状态寄存器以及程序计数器(PC)。

在所有的寄存器中,有些是各模式共⽤同⼀个物理寄存器,有些寄存器是各个模式⾃⼰拥有独⽴的物理寄存器其中 r0~r3 主要⽤于⼦程序间传递参数, r4~r11 主要⽤于保存局部变量,但在 Thumb 程序中,通常只能使⽤ r4~r7 来保存局部变量;r12 ⽤作⼦程序间scratch 寄存器,即 ip 寄存器; r13 通常⽤做栈指针,即 sp; r14 寄存器⼜被称为连接寄存器(lr),⽤于保存⼦程序以及中断的返回地址; r15 ⽤作程序计数器(pc),由于 ARM 采⽤了流⽔线机制,当正确读取了 PC 的值后,该值为当前指令地址加8 个字节,即 PC 指向当前指令的下两条指令地址。

CPSR和SPSR都是程序状态寄存器,其中SPSR是⽤来保存中断前的CPSR中的值,以便在中断返回之后恢复处理器程序状态。

2.CPSR寄存器详解所有处理器模式下都可访问当前程序状态寄存器CPSR。

CPSR中包含条件码标志、中断禁⽌位、当前处理器模式以及其他状态和控制信息。

在每种异常模式下都有⼀个对⽤的程序状态寄存器SPSR。

当异常出现时,SPSR⽤于保存CPSR的状态,以便异常返回后恢复异常发⽣时的⼯作状态。

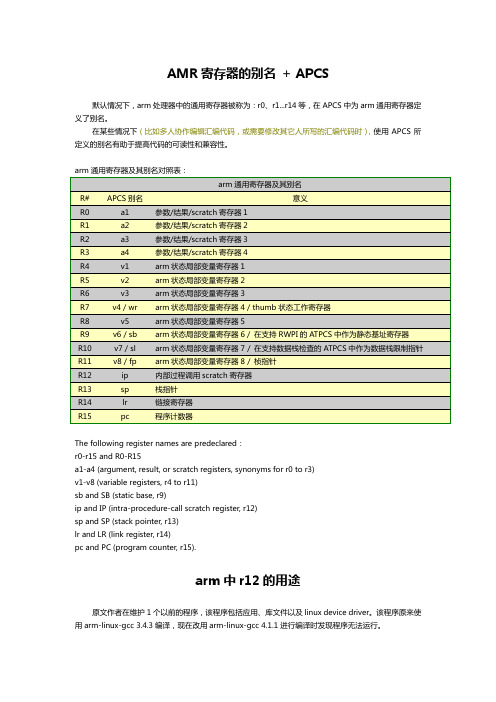

AMR寄存器的别名+ APCS默认情况下,arm处理器中的通用寄存器被称为:r0、r1...r14等,在APCS中为arm通用寄存器定义了别名。

在某些情况下(比如多人协作编辑汇编代码,或需要修改其它人所写的汇编代码时),使用APCS所定义的别名有助于提高代码的可读性和兼容性。

arm通用寄存器及其别名对照表:The following register names are predeclared:r0-r15 and R0-R15a1-a4 (argument, result, or scratch registers, synonyms for r0 to r3)v1-v8 (variable registers, r4 to r11)sb and SB (static base, r9)ip and IP (intra-procedure-call scratch register, r12)sp and SP (stack pointer, r13)lr and LR (link register, r14)pc and PC (program counter, r15).arm中r12的用途原文作者在维护1个以前的程序,该程序包括应用、库文件以及linux device driver。

该程序原来使用arm-linux-gcc 3.4.3编译,现在改用arm-linux-gcc 4.1.1进行编译时发现程序无法运行。

经原文作者测试,发现当使用shared library形式编译程序后无法运行,而使用static linking形式编译程序后可正常运行。

这是由于在arm-linux-gcc 4.1.1所使用的新的规范中,r12不仅作为通用寄存器,还被称为Intra-Procedure-call scratch register。

Register r12 (IP) may be used by a linker as a scratch register between a routine and any subroutine it calls (for details, see §5.3.1.1, Use of IP by the linker). It can also be used within a routine to hold intermediate values between subroutine callsBoth the ARM- and Thumb-state BL instructions are unable to address the full 32-bit address space, so it may be necessary for the linker to insert a veneer between the calling routine and the called subroutine. Veneers may also be needed to support ARM-Thumb inter-working or dynamic linking. Any veneer inserted must preserve the contents of all registers except IP (r12) and the condition code flags; a conforming program must assume that a veneer that alters IP may be inserted at any branch instruction that is exposed to a relocation that supports inter-working or long branches.——引用自:"Procedure Call Standard for the ARM Architecture"19th January, 2007, Richard Earnshaw.由上述说明可知,若在汇编代码中使用了bl命令,而r12又被作为通用寄存器使用时,则r12的值可能会被链接器插入的veneer代码所修改,若是单纯的c源码则不会出现此问题。

ARM体系结构是一种经典的32位精简指令集(RISC)处理器架构。

在ARM处理器架构中,有许多专用寄存器用于特定的功能,例如控制处理器状态、存储系统和I/O设备的配置信息等。

以下是ARM处理器架构中三个常见的专用寄存器的名称及其功能:1.程序状态寄存器(CPSR)程序状态寄存器(CPSR)是ARM处理器架构中最重要的专用寄存器之一。

它用于存储处理器的当前执行状态,包括当前处理器模式(用户模式、系统模式等)、条件标志位(零标志、负标志等)以及中断屏蔽状态。

通过读取和修改CPSR的值,软件可以控制处理器的执行状态,例如启用或禁用中断、切换处理器模式等。

CPSR的位字段结构非常复杂,需要仔细阅读ARM体系结构手册以理解其所有细节。

2.控制寄存器(CR)控制寄存器(CR)是用于控制处理器操作模式和系统功能的专用寄存器。

其中包括了配置指令和操作类型,如分支指令的方式(指数或者相关)、数据访问权限(只读或者读写)等。

通过对CR的设置,软件可以控制处理器的操作行为,例如启用或禁用高速缓存、配置分支预测算法等。

CR寄存器中的内容对于系统的性能和功能有着重要的影响,因此需要谨慎设置。

3.中断控制寄存器(ICR)中断控制寄存器(ICR)用于存储处理器中断系统的配置信息和状态。

ICR包括了中断屏蔽寄存器和中断向量寄存器两部分。

中断屏蔽寄存器用于控制处理器对各种中断的响应,包括屏蔽中断、启用中断等。

中断向量寄存器用于存储中断向量表的起始位置区域,当发生中断时,处理器从中断向量表中读取相应中断处理程序的入口位置区域。

ICR的设置对于系统的中断处理有着重要的影响,需要根据具体的系统需求进行合理配置。

总结上述是在ARM处理器架构中,三个常见的专用寄存器及其功能。

这些专用寄存器对于处理器的操作和系统的性能有着重要的影响,需要在系统软件开发和调试过程中予以重视。

更多的专用寄存器和其功能还需要开发者去阅读ARM体系结构手册获取更多了解。

arm寄存器的分类ARM寄存器是ARM体系结构中的一部分,用于存储和处理数据。

根据其功能和用途的不同,ARM寄存器可以分为通用寄存器、程序状态寄存器、系统控制寄存器和浮点寄存器等多个类别。

一、通用寄存器通用寄存器是最常用的寄存器类型,用于存储临时数据、变量和计算结果等。

ARM体系结构提供了16个32位的通用寄存器,分别用R0-R15表示。

其中,R0-R12可用于存储数据和计算结果,R13为堆栈指针SP,R14为链接寄存器LR,R15为程序计数器PC。

通用寄存器具有快速访问和高灵活性的特点,可以在程序执行过程中频繁读写。

在函数调用过程中,通用寄存器用于保存临时变量、函数参数和返回值,保证程序的正确执行。

二、程序状态寄存器程序状态寄存器(CPSR)是ARM体系结构中的一种特殊寄存器,用于存储和控制程序的执行状态。

CPSR寄存器是一个32位的寄存器,包含了当前程序的运行状态、中断控制状态和条件执行状态等信息。

CPSR寄存器的位域有多个,其中最重要的有条件执行位、中断控制位和程序状态位等。

条件执行位用于控制条件分支指令的执行,中断控制位用于控制中断的使能和禁止,程序状态位用于记录程序的运行状态,如运行模式、状态标志和当前指令的执行情况等。

三、系统控制寄存器系统控制寄存器(SCR)是ARM体系结构中的一种特殊寄存器,用于存储和控制系统的运行状态。

SCR寄存器是一个32位的寄存器,包含了系统的控制状态、访问权限和异常处理等信息。

SCR寄存器的位域有多个,其中最重要的有访问权限位、异常处理位和系统控制位等。

访问权限位用于控制对系统资源的访问权限,异常处理位用于控制异常处理器的行为,系统控制位用于控制系统的运行方式和功能。

四、浮点寄存器浮点寄存器是ARM体系结构中的一种特殊寄存器,用于存储和处理浮点数数据。

ARM体系结构提供了16个32位或64位的浮点寄存器,分别用S0-S31或D0-D31表示。

其中,S0-S15用于单精度浮点数操作,D0-D15用于双精度浮点数操作。

Arm汇编第⼀讲Arm寄存器与七种模式两种状态⽬录Arm学习第⼀讲 Arm寄存器与模式Arm寄存器1.1 什么是寄存器寄存器(register) 学过windows逆向的都知道.在汇编中同样有寄存器的概念. 寄存器是CPU的⼀个组成部分,⾥⾯放着指令⼂数据⼂和地址等相相关资源给CPU使⽤.⽽他们的速度是很快的. 在windows x86汇编下. 速度分别就是eax > ecx > ebx > edx ... 等. 寄存器速度⽐内存块. ⼜分为通⽤寄存器.以及专⽤寄存器.通⽤寄存器通⽤寄存器⼀般看名字就知道是通⽤的.它的功能就是完成通⽤的就算功能,谁都可以使⽤.专⽤寄存器专⽤寄存器⼀般特征有特别⽤处的寄存器. 如: 记录状态的状态寄存器记录下⼀条执⾏指令的寄存器. 栈寄存器等. 是不可以随便修改的.Arm寄存器运⾏模式寄存器运⾏模式在学习Arm汇编的时候.⾸先说⼀下Arm寄存器的运⾏模式,为什么要说⼀下运⾏模式. 原因在于Arm寄存器在各个模式下有单独的不同的名字以及含义.这个需要了解.⽤户模式(USR)Arm处理器正常的程序执⾏状态,在windows中我们就理解为是应⽤程序.是ring3程序快速中断模式(FIQ)⾼速数据传输或者通道处理外部中断模式(IRQ)通⽤的中断处理,⼀般就是系统发⽣中断的时候,Arm所运⾏的环境.管理模式(SVC)操作系统使⽤的保护模式数据访问终⽌模式(ABT)当数据或者指令预取终⽌的时候进⼊该模式,可⽤于虚拟存储以及存储保护.系统模式(SYS)运⾏具有特权的操作系统任务相当于内核模式. x86下的ring0未定义指令终⽌模式(UND)当未定义的指令执⾏的时候进⼊该模式以上数据模式暂时只需要了解USR即可.中寄存器介绍在Arm汇编中.有 37个寄存器其中 31个通⽤的. 6个状态寄存器然后在31 个通⽤寄存器中⼜分为未分组寄存器和分组寄存器未分组寄存器见名之意未分组的意思在各个运⾏模式下都是可以使⽤的.通⽤的寄存器.他们分别是 R0~R7分组寄存器所谓分组寄存器,指的就是在不同的模式下有不同的寄存器例如sp_und ⽽在abort(ABT) 模式下就叫做 sp_abt,反正就是进⼊不同的模式下会⾃动进⾏切换.⽽R8-R12 寄存器很特殊,只有在快速模式下(FIQ)名字才不⼀样R13寄存器R13寄存器⼀般称为栈指针,在⽤户模式与系统模式下⼀般就代表SP栈顶指针的意思⽽在其它模式下则叫做sp_x 这⾥的后缀 X 特指某⼀种模式下的后缀名. 如在UND模式下. 那么就叫做sp_und在FIQ模式下就叫做 sp_FIQR14寄存器R14寄存器也叫作LR寄存器(链接寄存器) 通常作⽤就是保存⼦程序或者中断的返回的地址.除了 USR(⽤户模式) 和 SYS(系统模式) 其它模式都叫做LR_X (x还是特指的意思)R15寄存器(PC)R15寄存器也叫作PC寄存器总是执向正在取值的指令. 学过x86汇编的应该知道.这个寄存器就类似于x86平台下的EIP寄存器CPSR(状态寄存器)当前程序状态的CPSR寄存器. 类似于x86下的EFLAGS寄存器2.3各个模式下的⼀览图下列表格就代表各个平台下的寄存器名称.可做参考.系统和⽤户模式管理模式终⽌模式中断模式未定义模式快速中断模式R0R0R0R0R0R0R1R1R1R1R1R1R2R2R2R2R2R2R3R3R3R3R3R3R4R4R4R4R4R4R4R4R4R4R4R4系统和⽤户模式管理模式终⽌模式中断模式未定义模式快速中断模式R5R5R5R5R5R5R6R6R6R6R6R6R7R7R7R7R7R7R8R8R8R8R8R8_FIQR9R9R9R9R9R9_FIQR10R10R10R10R10R10_FIQR11R11R11R11R11R11_FIQR12R12R12R12R12R12_FIQR13_SP R13_SVC R13_ABT R13_IRQ R13_UND R13_FIQR14_LR R14_SVC R14_ABT R14_IRQ R14_UND R14_FIQR15(PC)R15(PC)R15(PC)R15(PC)R15(PC)R15(PC)CPSR CPSR CPSR CPSR CPSR CPSRSPSR_SVC SPSR_ABT SPSR_IRQ SPSR_UND SPSR_FIQ2.54状态寄存器状态寄存器,⼀般就是保存程序执⾏过程中的⼀些状态. ⽐如计算是否进位. 是否溢出.等.状态寄存器如下表⽰|N|Z|C|V|.......|I|F|T|MODE|状态寄存器只⽤到了 0-4位(MODE0 4-8位(IFT) 以及28-31位(NZCV n是第31位)0-4位称为ModeBits 是⽤来定位我们的CPU所运⾏的模式4 - 8 表⽰打断标志位(Interrupt Disable bits) 表⽰是否关中断作⽤如下Interrupt Disable bits作⽤I7位: 如果为1则表⽰关闭IRQF6位: 如果F = 1则表⽰关闭FIQ其中⽐较特殊的就是第五位 T如果T = 1 则表⽰我们的程序运⾏在 Arm状态如果T = 0 则表⽰我们的程序运⾏在 thumb状态下⾯会说明什么是Arm状态,什么是Thumb状态其中第28-31位表⽰条件代码状态标志位作⽤如下Condition Code Flags(条件代码标志)位数以及作⽤(31-28位)N (Negative result from ALU flag)31位: 表⽰运算结果是否为负.为负数则是1 否则就是0Z (Zero result from ALU flag)30位: 表⽰运算结果是否为0.如果为0就是1 否则就是0C (ALU operation Carried Out)29位: 表⽰进位标志加减运算有没有进位有就是1否则就是0V (ALu operation oVerflowed)28位: 表⽰溢出位. 计算结果有没有溢出,溢出了就是1否则就是0运⾏状态 Arm&Thumb状态在Arm汇编中,他有七种运⾏模式两种运⾏状态两种运⾏状态分别是 ARM 以及 Thumb状态Thumb状态这个状态是16位指令也就是2个字节 ArmV4版本后,假如的⼀种16位指令模式. 可以看做是ARM指令压缩形式的⼦集,具有16位的代码密度(也就是2个字节指令长度),但是只能是⽀持通⽤功能,必要的时候仍然需要ARM 指令.⽽Thumb-2 技术则扩充了受限的16位thumb 指令集. 以及额外的32位指令,使指令集的使⽤更加⼴泛.下⾯是两种状态下寄存器的对应表Thumb状态Arm状态R0-R7(通⽤寄存器)与ARM相等R0-R7CPSR (同上)CPSRFP(栈底指针)R11(栈底指针)IP R12SP(栈顶)R13LR(保存返回地址指令)R14PC(当前指令)R15。

ARM 内核寄存器和基本汇编语言讲解•一、ARM内核寄存器▪ 1.1 M3/M4内核寄存器▪ 1.2 A7内核寄存器▪ 1.3 ARM中的PC指针的值•二、ARM汇编语言▪ 2.1 ARM汇编基础▪ 2.2 汇编伪指令▪ 2.3 ARM汇编指令集•三、代码反汇编简析▪ 3.1 不同编译器的反汇编▪ 3.2 C 和汇编比较分析开头直接来看几个简单的汇编指令:MOV R0,R1MOV PC,R14上面的指令中使用了汇编MOV指令,但是其中的R0,R1,R14,PC分别是什么?哪来的?怎么用?要讲ARM 汇编语言,必须得先了解ARM的内核寄存器,内核处理所有的指令计算,都需要用到内核寄存器,所以ARM汇编里面指令大都是基于寄存器的操作。

文章前推荐韦东山老师的单片机核心视频,视频可以在韦东山老师官网里面找到:百问网ARM版本简单介绍:对于M3/M4而言:R13,栈指针(Stack Pointer)•R13寄存器中存放的是栈顶指针,M3/M4 的栈是向下生长的,入栈的时候地址是往下减少的。

•裸机程序不会用到PSP,只用到MSP,需要运行RTOS的时候才会用到PSP。

•堆栈主要是通过POP,PUSH指令来进行操作。

在执行PUSH 和 POP 操作时, SP 的地址寄存器,会自动调整。

R14 ,连接寄存器(Link Register)•LR 用于在调用子程序时存储返回地址。

例如,在使用BL(分支并连接,Branch and Link)指令时,就自动填充 LR 的值(执行函数调用的下一指令),进而在函数退出时,正确返回并执行下一指令。

如果函数中又调用了其他函数,那么LR将会被覆盖,所以需要先将LR寄存器入栈。

•保存子程序返回地址。

使用BL或BLX时,跳转指令自动把返回地址放入r14中;子程序通过把r14复制到PC来实现返回•当异常发生时,异常模式的r14用来保存异常返回地址,将r14如栈可以处理嵌套中断R15,程序计数器(Program Count)•在Cortex-M3中指令是3级流水线,出于对Thumb代码的兼容的考虑,读取pc时,会返回当前指令地址+4的值。

ARM寄存器详解 ARM A系列寄存器的情况 这是寄存器的总表,下⾯是CPU的各个模式,上⾯的纵轴就是寄存器组。

CPU在运⾏的时候为什么会有寄存器? 想象CPU是⼀个圈⼀直在运转,然后寄存器⾥⾯有⼤量的指令,这些指令不知道从哪⾥来的,但是⼀般情况下我们的程序在计算我们的程序,我们的程序⼀般是放在内存⾥⾯的,它从内存⾥⾯把这些程序读进来之后,在运⾏,但是如果现在这个程序在运⾏时异常,那么就要进⾏CPU状态的切换,除了状态切换之外,当前的⼀些数据结果需要进⾏⼀个保存,但是如果要把这个结果存到内存去,内存并不稳定并且很慢,所以就要想办法能不能找到⼀个临时空间保存⼀下,这就是为什么会诞⽣寄存器。

设置寄存器的原因就是为了更好的去控制和达到效率,ARM体系为了很好的去控制CPU,设定了哪些寄存器? User纵轴上的⼗三个寄存器称为通⽤寄存器,R13是⼀个⽐较特殊的寄存器,也叫做SP,就是占指针的寄存器,就是指向某⼀些占空间,R14是LR,就是连接寄存器,它肯定是去连接某⼀个地⽅。

R15是PC,这是程序计数器,这是CPU在每⼀个空间切换的时候的计数器,最下⾯那个也就是APSR或者CPSR,PSR就是程序状态寄存器,A代表应⽤程序状态寄存器,C代表当前程序状态寄存器。

在往下就类似于R17,只不过它叫做SPSR,S就是以保存程序代表寄存器或者我们也可以称为存储状态寄存器,通过这些我们⼤概把寄存器了解了。

那么这上⾯分为通⽤的,那么下⾯就是特殊寄存器,从横向来看,我们可以看到在USR模式下⾯,这样寄存器挺全的,但是USR下⾯没有SPSR,就是没有存储状态的寄存器,然后FIQ快速中断模式下⾯⾯是共享R0到R7,意思就是这些模式下的R0到R7它们与USR模式下的R0到R7是共享的,这样如果存储⼀些数据在R0到R9下⾯,突然发⽣异常,切换到另⼀个模式,那么我们就应该要想办法把这个存取⼀下,因为另⼀个模式可能也要往这⾥⾯写东西,那么写之前就应该把USR模式下的先保留⼀下,到时候退出解决后在还原回来,所以我们要⼀个R0到R7这块寄存器是共享的,同样FIQ后⾯⼏个模式的R8到R12也是和USR共享的,只有FIQ是⾃⼰独有的,同样的我们在看到PC计数器也是共享的,还有SPSR也是共享的,但是SPSR每个状态都有⾃⼰独有的。

ARM程序设计的基本概念ARM(Advanced RISC Machines)是一种流行的处理器架构,广泛应用于多种设备,包括智能手机、平板电脑、物联网设备等各种嵌入式系统。

ARM程序设计的基本概念包括指令集架构、寄存器、存储器访问和程序流程控制等方面。

1.指令集架构(Instruction Set Architecture,ISA):ISA是ARM处理器的核心组成部分,包括了处理器能够识别和执行的指令集合。

ARM指令集被设计成简洁且高效,以满足节能和性能的要求。

ARM处理器通常支持两种ISA:ARM模式和Thumb模式。

ARM模式下指令长度为32位,能提供更多的功能和更高的性能,而Thumb模式下指令长度为16位,适用于内存空间有限的设备。

2.寄存器:ARM处理器包含多个寄存器,用于存储数据和地址。

常见的寄存器包括通用寄存器、程序计数器、堆栈指针和链接寄存器等。

通用寄存器用于存储计算过程中的临时数据,ARMv8-A体系结构有31个32位的通用寄存器。

程序计数器(PC)指向当前执行的指令地址,堆栈指针(SP)用于管理函数调用时的局部变量和返回地址,链接寄存器(LR)用于存储函数调用的返回地址。

3.存储器访问:ARM处理器通过内存访问指令进行与存储器的交互。

存储器分为两种类型:寄存器文件和主存。

寄存器文件是位于处理器内部的高速存储器,用于暂时存放指令和数据。

主存则是位于处理器外部的大容量存储器,用于存放程序和数据。

ARM处理器通过加载指令将数据从主存中读取到寄存器中,通过存储指令将数据从寄存器写回主存。

存储器访问需要注意对齐和字节顺序等问题,以确保高效的数据交换和正确的数据操作。

4.程序流程控制:程序流程控制是ARM程序设计中的核心概念之一,用于控制指令的执行顺序。

最常见的程序流程控制语句包括分支、跳转和循环等。

分支(Branch)指令用于根据条件改变程序的执行顺序,比如根据一些条件是否成立进行不同的处理。

ARM寄存器简介ARM处理器含有37个寄存器,这些寄存器包括以下两类寄存器。

(1)31个通用寄存器:包括程序计数器PC等,这些寄存器都是32位寄存器。

(2)6个状态寄存器:状态寄存器也是32位的寄存器,但是只使用了其中的12位。

1.通用寄存器在ARM处理器的7种模式下都有一组对应的寄存器组。

在任意时刻,可见的寄存器组包括15个通用寄存器R0~R14、一个或两个状态寄存器和PC。

在所有的寄存器中,有些是各种模式下共用的同一个物理寄存器,有些是各种模式自己独立拥有的物理寄存器。

详细如表1-3所示。

表1-3 ARM物理寄存器用户模式系统模式特权模式中止模式未定义指令模外部中断模快速中断模R0 R0 R0 R0 R0 R0 R0R1 R1 R1 R1 R1 R1 R1R2 R2 R2 R2 R2 R2 R2R3 R3 R3 R3 R3 R3 R3R4 R4 R4 R4 R4 R4 R4R5 R5 R5 R5 R5 R5 R5R6 R6 R6 R6 R6 R6 R6R7 R7 R7 R7 R7 R7 R7R8 R8 R8 R8 R8 R8 R8_fiq R9 R9 R9 R9 R9 R9 R9_fiq R10 R10 R10 R10 R10 R10 R10_fiq R11 R11 R11 R11 R11 R11 R11_fiq R12 R12 R12 R12 R12 R12 R12_fiq R13 R13 R13_svc R13_abt R13_und R13_irq R13_fiq R14 R14 R14_svc R14_abt R14_und R14_irq R14_fiq PC PC PC PC PC PC PCCPSR CPSR CPSR CPSR CPSR CPSR CPSRSPSR_svc S PSR_abt SPSR_und SPSR_irq SPSR_fiq 通用寄存器通常又可以分为下面3类。

n 未备份寄存器:包括R0~R7。

n 备份寄存器:包括R8~R14。

n 程序计数器PC:即R15。

1)未备份寄存器R0~R7对于每个未备份寄存器来说,在所有的处理器模式下指的都是同一个物理寄存器,在异常中断造成处理器模式切换时,由于不同的处理器模式使用相同的物理寄存器,可能造成寄存器中数据被破坏。

未备份寄存器没有被系统用于特别的用途,任何可采用通用寄存器的应用场合都可以使用未备份寄存器。

2)备份寄存器R8~R14备份寄存器中的每个寄存器对应于两个不同的物理寄存器。

例如,当使用快速中断模式下的寄存器时,寄存器R8和寄存器R9分别记做R8_fiq和 R9_fiq,当使用用户模式下的寄存器时,寄存器R8和寄存器R9分别记做R8_usr和R9_usr 等。

在这两种情况下使用的是不同的物理寄存器,系统没有将这几个寄存器用于任何的特殊用途。

中断处理非常简单,仅仅使用R8~R14寄存器时,FIQ处理程序可以不必执行保存和恢复中断现场的指令,从而可以使中断处理过程很迅速。

对于备份寄存器R13、R14来说,每个寄存器对应于6个不同的物理寄存器,其中的一个是用户模式和系统模式共用的,另外的5个则对应于其他5种处理器模式,采用下面的方法来标识。

R13_<mode>,其中<mode>是usr、svc、abt、und、irq和fiq的一种。

R13通常用做堆栈指针。

每一种模式都拥有自己的物理R13。

程序初始化R13,使其指向该模式专用的栈地址。

当进入该模式时,可以将需要使用的寄存器保存在R13所指的栈中,当退出该模式时,将保存在R13所指的栈中的寄存器值弹出。

这样就实现了程序的现场保护。

寄存器R14又被称为连接寄存器(LR),在ARM中有下面两种特殊用途。

① 每一种处理器模式在自己的物理R14中存放当前子程序的返回地址。

当通过BL或者BLX指令调用子程序时,R14被设置成该子程序的返回地址。

在子程序中,当把R14的值复制到程序计数器PC中时,就实现了子程序返回。

可以通过下面两种方式实现这种子程序的返回操作。

◆执行下面任何一条指令MOV pc, LRBX LR◆在子程序入口使用下面指令将PC保存到栈中:STMFD SP!, {registers}, LR}相应地,下面的指令可以实现子程序的返回:LDMFD SP!, { registers}, LR }② 当发生异常中断的时候,该模式下的特定物理R14被设置成该异常模式将要返回的地址。

对于某些异常,R14的值可能与将返回的地址有一个常数的偏移量。

具体的返回方式与上面的子程序返回方式基本相同。

3)程序计数器PC→R15程序计数器R15又被记作PC。

它虽然可以作为一般的通用寄存器使用,但是有一些指令在使用R15时有一些特殊限制。

当违反了这些限制时,该指令执行的结果将是不可预料的。

由于ARM采用了流水线机制,当正确读取了PC的值时,该值为当前指令地址值加8个字节。

也就是说,对于ARM指令集来说,PC指向当前指令的下两条指令的地址。

由于ARM指令是字对齐的,PC值的第0位和第1位总为0。

需要注意的是,当使用指令STR/STM保存R15时,保存的可能是当前指令地址值加8字节,也可能保存的是当前指令地址加12字节。

到底是哪种方式,取决于芯片具体设计方式。

无论如何,在同一芯片中,要么采用当前指令地址加8,要么采用当前指令地址加12,不能有些指令采用当前指令地址加8,另一些指令采用当前指令地址加12。

因此对于用户来说,尽量避免使用STR/STM指令来保存R15的值。

当不可避免这种使用方式时,可以先通过一些代码来确定所用的芯片使用的是哪种实现方式。

假设R0指向可用的一个内存字,下面代码可以在R0指向的内存字中返回该芯片所采用的地址偏移量。

SUB R1, PC, #4 ;R1中存放下面STR指令的地址STR PC, [R0] ;将PC=STR地址+offset保存到R0中LDR R0, [R0] ;SUB R0, R0, R1 ;offset=PC-STR地址2.程序状态寄存器CPSR(当前程序状态寄存器)可以在任何处理器模式下被访问。

每一种模式下都有一个专用的物理状态寄存器,称为SPSR(备份程序状态寄存器)。

当特定的异常中断发生时,这个寄存器用于存放当前程序状态寄存器的内容。

在异常退出时,可以用 SPSR中保存的值来恢复CPSR。

CPSR的具体格式如下。

31 30 29 28 27 26 7 6 5 4 3 21 0 N Z C V Q DNMLRAZ I F I M4 M3 M M01)条件标志位N(Negative)、Z(Zero)、C(Carry)及V(oVerflow)统称为条件标志位。

大部分的ARM指令可以依据CPSR中的这些标志位来选择性地执行。

各条件标志位的具体含义,如表1-4所示。

表 CPSR标志位含义标志位含义N 本位设置成当前指令运算结果的bit[31]的值当两个补码表示的有符号整数运算时,N=1表示运算的结果为负数,N=0 表示结果为正数或零Z Z=1表示运算结果是0,Z=0表示运算结果不是零对于CMP指令,Z=1表示进行比较的两个数大小相等C 在加法指令中(包括比较指令CMN),结果产生进位了,则C=1,表示无符号数运算发生上溢出,其他情况下C=0在减法指令中(包括比较指令CMP),结果产生借位了,则C=0,表示无符号数运算发生下溢出,其他情况下C=1对于包含移位操作的非加/减法运算指令,C中包含最后一次被溢出的位的数值,对于其他非加/减法运算指令,C位的值通常不受影响V 对于加/减法运算指令,当操作数和运算结果为二进制的补码表示的带符号数时,V=1表示符号位溢出其他的指令通常不影响V位2)Q标志位在ARM v5的E系列处理器中,CPSR的bit[27]称为Q标志位,主要用于指示增强的DSP指令是否发生了溢出,同样的,SPSR的bit[27]也称为Q标志位,用于在异常中断发生时保存和恢复CPSR中的Q标志位。

3)CPSR中的控制位CPSR的低8位I、F、T及M[4:0]统称为控制位,当异常中断发生时这些位发生变化。

在特权级的处理器模式下,软件可以修改这些控制位。

① I中断禁止位当I=1时禁止IRQ中断。

当F=1时禁止FIQ中断。

通常一旦进入中断服务程序可以通过置位I和F来禁止中断,但是在本中断服务程序退出前必须恢复原来I、F位的值。

② T控制位,用来控制指令执行的状态,即说明本指令是ARM指令还是Thumb 指令。

对于不同版本的ARM处理器,T控制位的含义是有些不同的。

对于ARM v3及更低的版本和ARM v4的非T系列版本的处理器,没有ARM和Thumb 指令的切换,所以T始终为0。

对于ARM v4及更高版本的T系列处理器,T控制位含义如下。

当T=0,表示执行ARM指令。

当T=1,表示执行Thumb指令。

对于ARM v5及更高的版本的非T系列处理器,T控制位的含义如下。

当T=0表示执行ARM指令。

当T=1表示强制下一条执行的指令产生为定义指令中断。

③ M 控制位控制位M[4:0]称为处理器模式标识位,具体说明如表1-5所示。

表1?5 CPSR 处理器模式位M[4:0] 处理器模式可访问的寄存器0b10000 User PC,R14~R0,CPSR0b10001 FIQ PC,R14_fiq~R8_fiq,R7~R0,CPSR,SPSR_fiq0b10010 IRQ PC,R14_irq~R13_irq,R12~R0,CPSR,SPSR_irq0b10011 Supervisor PC,R14_svc~R13_svc,R12~R0,CPSR,SPSR_svc0b10111 Abort PC,R14_abt~R13_abt,R12~R0,CPSR,SPSR_abt0b11011 Undefined PC,R14_und~R13_und,R12~R0,CPSR,SPSR_und0b11111 System PC,R14~R0,CPSR(ARM v4及更高版本)④CPSR的其他位用于将来ARM版本的扩展,程序可以先不操作这些位。