LVDS与高速PCB设计

- 格式:pdf

- 大小:95.22 KB

- 文档页数:3

环测威官网:/阻抗控制技术在高速数字电路设计中非常重要,其中必须采用有效的方法来确保高速PCB 的优异性能。

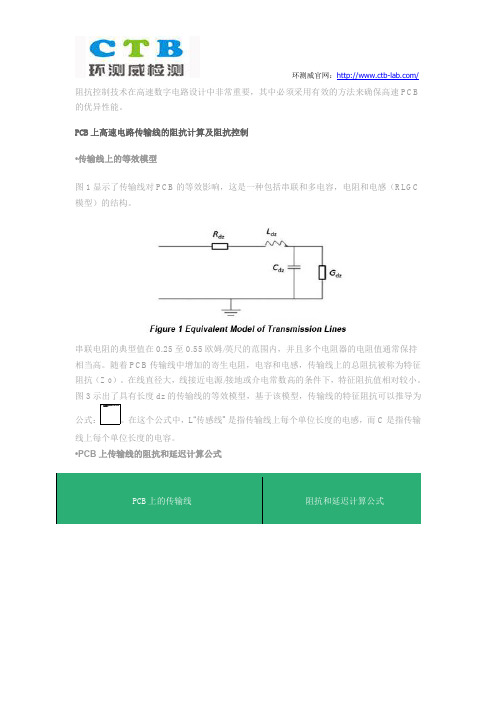

PCB上高速电路传输线的阻抗计算及阻抗控制•传输线上的等效模型图1显示了传输线对PCB的等效影响,这是一种包括串联和多电容,电阻和电感(RLGC 模型)的结构。

串联电阻的典型值在0.25至0.55欧姆/英尺的范围内,并且多个电阻器的电阻值通常保持相当高。

随着PCB传输线中增加的寄生电阻,电容和电感,传输线上的总阻抗被称为特征阻抗(Z 0)。

在线直径大,线接近电源/接地或介电常数高的条件下,特征阻抗值相对较小。

图3示出了具有长度dz的传输线的等效模型,基于该模型,传输线的特征阻抗可以推导为公式:。

在这个公式中,L“传感线”是指传输线上每个单位长度的电感,而C是指传输线上每个单位长度的电容。

环测威官网:/在上面的公式中,Z 0表示阻抗(欧姆),W表示线的宽度(英寸),T表示线的粗细(英寸),H表示到地面的距离(英寸),是指衬底的相对介电常数,t PD是指延迟时间(ps / inch)。

•传输线的阻抗控制布局规则基于上述分析,阻抗和信号的单位延迟与信号频率无关,但与电路板结构,电路板材料的相对介电常数和布线的物理属性有关。

这一结论对于理解高速PCB和高速PCB设计非常重要。

而且,外层信号传输线的传输速度比内层传输速度快得多,因此关键线布局的排列必须考虑这些因素。

阻抗控制是实现信号传输的重要前提。

但是,根据传输线的电路板结构和阻抗计算公式,阻抗仅取决于PCB材料和PCB层结构,同一线路的线宽和布线特性不变。

因此,线路的阻抗在PCB的不同层上不会改变,这在高速电路设计中是不允许的。

本文设计了一种高密度高速PCB,板上大多数信号都有阻抗要求。

例如,CPCI信号线的阻抗应为650欧姆,差分信号为100欧姆,其他信号均为50欧姆。

根据PCB布线空间,必须使用至少十层布线,并确定16层PCB设计方案。

由于电路板的整体厚度不能超过2mm,因此在堆叠方面存在一些困难,需要考虑以下问题:1)。

2.LVDS信号在PCB上的设计要点LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express 为代表的第三代I/O标准中采用,而在我们的项目中PCI-Express信号正是采用的是LVDS信号。

LVDS信号不仅是差分信号,而且还是高速数字信号。

因此LVDS 传输媒质不管使用的是PCB线还是电缆,都必须采取措施防止信号在媒质终端发生反射,同时应减少电磁干扰以保证信号的完整性。

只要我们在布线时考虑到以上这些要素,设计高速差分线路板并不很困难。

下面简要介绍LVDS信号在PCB 上的设计要点:2.1布成多层板有LVDS信号的电路板一般都要布成多层板。

由于LVDS 信号属于高速信号,与其相邻的层应为地层,对LVDS信号进行屏蔽防止干扰。

对于密度不是很大的板子,在物理空间条件允许的情况下,最好将LVDS信号与其它信号分别放在不同的层。

例如,在四层板中,通常可以按以下进行布层:LVDS 信号层、地层、电源层、其它信号层。

2.2 LVDS信号阻抗计算与控制。

LVDS信号的电压摆幅只有350mV,适于电流驱动的差分信号方式工作。

为了确保信号在传输线当中传播时不受反射信号的影响,LVDS信号要求传输线阻抗受控,通常差分阻抗为100+/-10Ω。

阻抗控制的好坏直接影响信号完整性及延迟。

如何对其进行阻抗控制呢?(1)确定走线模式、参数及阻抗计算。

LVDS分外层微带线差分模式和内层带状线差分模式。

阻抗可以通过合理设置参数,利用相关软件计算得出。

通过计算,阻抗值与绝缘层厚度成正比,与介电常数、导线的厚度及宽度成反比。

(2)走平行等距线及紧耦合原则。

确定走线线宽及间距后,在走线时严格按照计算出的线宽和间距,两线的间距要一直保持不变,也就是要保持平行(可以放图)。

同时在计算线宽和间距时最好遵守紧耦合的原则,也就是差分对线间距小于或等于线宽。

当两条差分信号线距离很近时,电流传输方向相反,其磁场相互抵消,电场相互耦合,电磁辐射也要小得多。

东南大学硕士学位论文LVDS信号完整性分析及高速背板设计姓名:胡劲松申请学位级别:硕士专业:电磁场与微波技术指导教师:朱晓维;洪伟20040301LVDS信号完整性分析及高速背板设计第二章高速电路板设计技术及其信号完整性分析2.1高速电路设计中的信号完整性综述【7】阁2.1典型的背板与子板结构中的信号干扰情况高速rU路中的信号完整性问题丰要包括噪声、串扰(crosstalk)、电源分配、电磁干扰(EMI)与电磁兼容(EMC)等。

噪声丰要来自于振铃(上冲和F冲)、阻抗火配、反射和终端负载。

振铃是在高频信号时钟的上升沿和下降沿,在信号建立的过程中产生的。

阻抗失配的主要是因为大多数高速设备都存在高阻驱动利低阻接收的方式,多层PCB扳阻抗的不可控以及带有多个插槽或子板的PCI总线的存在。

反射包括正发射和负发劓,当信号的波前遇到高阻时,将发生正发射并带来上冲:反之,当信号遇到低阻时,将发生负反射并带来下冲。

终端负载技术包括在发射端的串联接法,以及在接收端的并联接法(上拉、下拉、Thevenin、AC和二极管)。

此外还有一种同步切换噪声(SSN),它是由电流返同路径,地跳垌I去耦等因素造成的。

当两条走线靠在起时,其中一‘条走线中电流的变化将会引起相邻走线中的电流流动,这种现象就叫交扰,交扰一般发生在高频信号的上升沿和F降卅。

山丁电容和寄生电感的影响,在电源平面会存在许多复杂的喈振。

而地面和电源面上的谐振都会引起大量的共模EMI。

2.2电源[9】【1o】高速系统电源殴计的目标就是为板上的高速设各提供一个噪声尽可能小的纯净的电源。

东南大学坝十学位论文62.2.1电压损失和噪声问题图2.2电源总线和电源面的示意图在常见的低频电路中,经常采用电源总线为所有板上的器件供电。

但由于总线不可能是完全无耗的,这样总线【:的电压损失将会使总线上的某些设备得不到它的理想:[作电压。

同时每个高速设备产生的噪声也会被其他没备中。

在高频电路中,我们就可以为不同的电压级别分配不同的电源面米解决这些问题。

收稿日期:2009-11 作者简介:范丹(1985—),男,硕士研究生,研究方向为光电对抗与信息处理。

高速LVDS 接口电路设计范 丹1,何永强1,方晋贤2(1.军械工程学院,河北石家庄050003;2.广州军区76321部队,广东广州510500) 摘要:随着数字电路数据量的提高,数据的传输速率也越来越快,LVDS (低压差分信号)标准越来越多的应用在FPG A 和ASI C 器件中。

文章对LVDS 信号的特点进行了分析,说明了PC B 设计中差分走线的注意事项并结合实际应用设计了一块LVDS 接口板。

关键词:LVDS;PC B 设计;接口;阻抗匹配中图分类号:T N41 文献标识码:A 文章编号:1006-2394(2010)04-0007-02D esi gn of L V D S I n terface C i rcu itF AN Dan 1,HE Yong 2qiang 1,F ANG J in 2xian2(1.O rdnance Engineering College,Shijiazhuang 050003,China;2.Guangzhou M ilitary Regi on,Unit 76321,Guangzhou 510500,China )Abstract:A l ong with the rap id devel opment of digital circuit technol ogy,higher data trans m issi on rate is required .A s a result,more and more LVDS (Low 2Voltage D ifferential Signaling )standards are used in digital devices .The char 2acteristic of LVDS is analyzed .The attenti ons on PCB design with LVDS are exp lained .And then a LVDS interface board is made .Key words:LVDS (l ow 2v oltage differential signaling );PCB design;interface;i m pedance matching0 引言随着电子信息技术的进步,对数据传输速率的要求也越来越高。

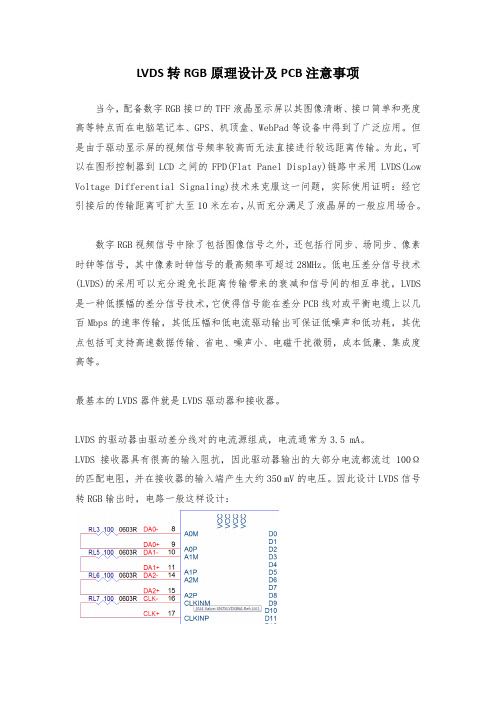

LVDS转RGB原理设计及PCB注意事项当今,配备数字RGB接口的TFF液晶显示屏以其图像清晰、接口简单和亮度高等特点而在电脑笔记本、GPS、机顶盒、WebPad等设备中得到了广泛应用。

但是由于驱动显示屏的视频信号频率较高而无法直接进行较远距离传输。

为此,可以在图形控制器到LCD之间的FPD(Flat Panel Display)链路中采用LVDS(Low Voltage Differential Signaling)技术来克服这一问题,实际使用证明:经它引接后的传输距离可扩大至10米左右,从而充分满足了液晶屏的一般应用场合。

数字RGB视频信号中除了包括图像信号之外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

低电压差分信号技术(LVDS)的采用可以充分避免长距离传输带来的衰减和信号间的相互串扰,LVDS 是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出可保证低噪声和低功耗,其优点包括可支持高速数据传输、省电、噪声小、电磁干扰微弱,成本低廉、集成度高等。

最基本的LVDS器件就是LVDS驱动器和接收器。

LVDS的驱动器由驱动差分线对的电流源组成,电流通常为3.5 mA。

LVDS接收器具有很高的输入阻抗,因此驱动器输出的大部分电流都流过100Ω的匹配电阻,并在接收器的输入端产生大约350 mV的电压。

因此设计LVDS信号转RGB输出时,电路一般这样设计:LVDS是串行接口,RGB信号传输时,是将每个基色信号的数据排成一纵队,采用差分数据线按顺序进行输出。

在一个时钟脉冲周期内,一对差分数据线可以传输7bit数据。

LVDS18对于单路6bit LVDS接口,需要3对差分数据线,即RX0-和RX0十,RX1-和RX1+,RX2-和RX2+。

因每对差分数据线可以传输7bit数据,这样,3对差分数据线可以传输3×7bit=21 bit,除R0~R5、G0~G5、B0~B5占去18bit,还剩下3bit 用于传输HS(行同步)、VS(场同步)、DE(有效数据选通)信号(若HS、VS信号不传输,将空余2bit)。

㊀2020年㊀第5期仪表技术与传感器Instrument㊀Technique㊀and㊀Sensor2020㊀No.5㊀收稿日期:2019-04-08基于PXI的LVDS高速通信板卡设计白宏义,李锦明,郭㊀淳(中北大学电子测试国家重点实验室,山西太原㊀030051)㊀㊀摘要:针对采集系统与计算机的高速数据传输问题,设计了基于PXI接口的通信板卡㊂板卡以FPGA为控制核心,控制LVDS进行数据采集,将数据通过PXI接口发送给计算机,通过WDM驱动结构完成PXI总线连接到计算机的软件接口,并编写上位机程序对板卡进行测速㊂不同于传统数据采集卡,没有采用专用的PCI芯片,单独以FPGA来实现PXI接口㊂测试证明,设计的通信板卡可以实现高速数据采集功能,速度可达107MB/s,在节约成本的同时加快了PXI板卡的开发周期㊂关键词:PXI接口;LVDS;FPGA;数据采集卡;WDM驱动;PCI芯片中图分类号:TN710㊀㊀㊀文献标识码:A㊀㊀㊀文章编号:1002-1841(2020)05-0033-04DesignofLVDSHighSpeedCommunicationBoardBasedonPXIBAIHong⁃yi,LIJin⁃ming,GUOChun(StatekeyLaboratoryofElectronicTesting,NorthUniversityofChina,Taiyuan030051,China)Absrtact:AcommunicationboardbasedonPXIinterfacewasdesignedtosolvetheproblemofhigh⁃speeddatatransmissionbetweenacquisitionsystemandcomputer.TheboardtookFPGAasthecontrolcore,controlledLVDSfordatacollection,sentdatatothecomputerthroughPXIinterface,completedthesoftwareinterfaceconnectingPXIbustothecomputerthroughWDMdriverstructure,andwrotetheuppercomputerprogramtomeasuretheboardspeed.Differentfromthetraditionaldataacquisitioncard,PXIinterfacewasimplementedbyFPGAinsteadofspecialPCIchip.Thetestprovesthatthehigh⁃speeddataacquisitionfunctioncanberealizedwiththespeedupto107MB/s,whichnotonlysavesthecostbutalsospeedsupthedevelopmentcycleofPXIboardcard.Keywords:PXIbus;LVDS;FPGA;dataacquisitioncard;WDMdriver;PCIchip0㊀引言随着电子技术发展,在基于计算机控制的采集系统中,建立采集设备和计算机高速有效的数据传输通道成为至关重要的一环㊂在采集大容量㊁高带宽的数据时,PXI接口速度可以达到132MB/s,数据位能够扩展到64位,有着较大的优点[1-2]㊂当前,开发PXI总线接口主要使用专用PCI接口芯片PCI9054和PCI9052[3-4],成本较高,开发周期较长㊂因此,提出单独采用FPGA实现PXI协议,能够降低成本,加快开发周期,具有一定的工程应用价值㊂1㊀系统总体设计板卡主要作用是接收采集设备发来的2路高速LVDS接口,通过FIFO对数据进行缓存,然后将数据通过PXI接口发送给计算机,上位机对数据进行实时监测㊂实现PXI接口包括3部分,PXI协议VHDL实现模块,WDM驱动,PXI接口电路㊂系统的总体设计如图1所示㊂图1㊀总体设计框图2㊀系统硬件电路设计2.1㊀LVDS接口电路LVDS电路采用的是DS92LV1023和DS92LV1224芯片,能够产生低压差分信号,DS92LV1023内部有10位并行总线,能够实时将10位并行数据转成内部包含时钟的高速串行数据,DS92LV1224可以将内部包含时钟的高速串行数据转成并行数据,将内部的时钟信号剥离出来,进行时钟重建㊂同时,FPGA作为主控芯片,可以实时完成TCLK和RCLK的同步,从而保证了大容量数据高速稳定传输[5-6]㊂如图2和图3所示是两组芯片硬件电路设计㊂㊀㊀㊀㊀㊀34㊀InstrumentTechniqueandSensorMay.2020㊀图2㊀LVDS发送端电路设计图2.2㊀PXI接口电路主控芯片FPGA采用EP2C35F484C8,速度为-8,编译后系统速度可以达到133MHz[7]㊂PXI接口涉及到诸多信号,信号根据不同功能可以分为几种类型㊂PXI接口作为一个功能模块,通过FPGA芯片的I/O管脚与PXI接口信号组相连[8],如图4所示㊂3㊀系统软件设计板卡以quartus软件为开发环境进行搭建和实现,总体逻辑设计图如图5所示,接收控制模块用来控制LVDS的时序,接收采集系统发来的数据㊂数据处理模块用来对数据进行编帧,串并转换等操作㊂PXI协议VHDL实现模块用来实现PXI协议和接口逻辑,并控制PXI接口时序进行PXI总线与FPGA进行数据交互㊂测试台发来数据,接收控制模块接收数据并将其放入4K的FIFO模块中;数据处理模块对收到数据加上帧头帧尾等标志㊂随后数据进入16K的FIFO模块,根据full2信号判断FIFO模块的数据量,如果达到标定的数据量,控制PXI总线对数据进行读写操作㊂图3㊀LVDS接受端电路设计图图4㊀PXI接口电路3.1㊀PXI协议VHDL实现板卡设计的PXI接口包含4个模块,如图6所示㊂3.1.1㊀配置空间设置该模块用来定义PCI配置空间㊂配置空间共有16个寄存器,即16个双字空间,AD(5ʒ2)就对应这16个地址㊂第1个地址的高16位是板卡的设备ID图5㊀软件设计总体框图号:4258;第1个地址的低16位是板卡的供应商ID号:1100㊂PCI配置空间有6个基址寄存器Base0-5,板卡主要用到两个基址寄存器㊂Base0寄存器:分配一段地址空间给FPGA的内存寄存器,用内存映射的形式访问FPGA的内存寄存器㊂㊀㊀㊀㊀㊀第5期白宏义等:基于PXI的LVDS高速通信板卡设计35㊀㊀图6㊀PXI接口Base1寄存器:分配一段地址空间给FPGA的IO寄存器,用I/O的形式访问FPGA的IO寄存器㊂3.1.2㊀接口逻辑接口逻辑包含两部分:地址译码,命令译码㊂地址译码是对总线发来的地址进行锁存,用来判断设备是否应该响应当前总线操作;命令译码是对总线锁存的命令类型进行锁存:对总线发来的不同命令做出相应的操作㊂在地址和命令传输结束后,总线在过程中成为数据总线,用于传输数据㊂3.1.3㊀奇偶校验在地址段和数据段中,奇偶校验对地址数据总线和命令操作位的正确性进行保护㊂既对AD(31ʒ0)与CBE(3ʒ0)进行校验㊂PXI数据总线校验保证0数据误码㊂3.1.4㊀状态机PXI总线传输主要通过帧开始标志信号FRAME;初始化设备选择信号IRTY;目标设备准备就绪信号TRDY;设备选择命中信号DEVSEL;总线命令和字节允许信号CBE;地址数据复用信号AD进行控制㊂图7为PXI读写操作状态机,共分为5个状态,S1是空闲状态,S2是地址或过渡状态,S3是忙状态,S4是传输状态,S5是停止状态㊂S1状态是PXI设备的初始状态,如果FRAME=1或者IRDY=0,一直保持该空闲状态㊂当FRAME=0和IRDY=1,S1进入S2状态即是地址过渡状态,开始进行地址周期,主要是对地址,命令和FRAME进行判断㊂主设备IRDY低电平表明准备接收发来的第1个数据项㊂当主设备IRDY和FRAME同时低电平且DEVSEL=1时,表明它已经完成交易的第一个数据段并且进入S4状态㊂如果IRDY和FRAME没有同时为低,一直维持S2状态㊂如果信号DEVSEL=0进入S3状态,表示主设备不进行采样操作,同时目标还没有声明交易,即总线访问的地址没有命中,处于总线忙状态㊂IRDY和TRDY同时低电平,表明数据是完整,成功地读取了第一个(且唯一的)数据项㊂在状态S4的时候如果FRAME变低,开始进入停止状态,在S3状态时,如果FRAME变低,开始进入停止状态㊂3.2㊀PXI读写时序仿真结果用QuartusⅡ12.0下的SignalTap工具对PXI信号图7㊀读写状态机进行捕捉,得到PXI读写操作时序如图8和图9所示㊂图6中AD(31ʒ0)输出值为42581100,表示设备的ID号是4258,供应商ID号是1100;CBE(3ʒ0)输出值为1010表示进行配置空间读操作㊂图7中CBE(3ʒ0)输出值为1010表示对配置寄存器进行写操作,AD(31ʒ0)输出0X4是地址,0X7是数据,表示向配置寄存器地址0X4写入数据0X7㊂图8㊀PXI读操作时序图9㊀PXI写操作时序读写时序说明:第1个周期:主机把FRAME信号拉低,IRDY拉高说明一个新的PXI操作开始;主机把CBE(3:0)置对应操作位;主机把AD(31:0)置地址操作位;设备卡检测到主机发起新的PXI操作;设备卡锁存CBE命令信息;设备卡锁存AD(31:0)的地址信息㊂第2个周期:主机把FRAME信号拉高,IRDY拉低;设备卡检测CBE命令操作,确认是哪种操作类型:IO操作,内存操作,配置操作;设备卡检测地址信息,确认是否本卡㊂第3个周期:设备卡确认是本卡操作,把DEVSEL信号拉低,STOP信号和TRDY拉高,响应主机操作;主机收到DEVSEL低,确认设备卡响应㊂第4个周期:设备卡将TRDY信号拉低,当前PXI交易完成㊂第5个周期:主机将IRDY和FRAME拉高,确认交易完成;设备卡将DEVSEL,TRDY,STOP拉高,确认交易完成㊂㊀㊀㊀㊀㊀36㊀InstrumentTechniqueandSensorMay.2020㊀第6个周期:主机将IRDY和FRAME释放三态,当前交易结束;设备卡将DEVSEL,TRDY,STOP释放三态,当前交易结束㊂3.3㊀WDM驱动WDM驱动程序是PXI总线连接到计算机的软件接口㊂在计算机上安装DRIVERWORKS2.7和2000DDK驱动等工具,自动生成驱动框架,用户只需要在它的框架之下,添加用户自己的代码用来实现PXI读写功能[9-10]㊂用户代码的操作句柄为NTSTATUSPcitioDevice::PCITIO_IOCTL_INTCSR_Handler(KIrpI),用来实现PXI读写操作㊂4㊀测试控制LVDS采集发来的一路数据,并通过PXI接口发送给计算机的上位机㊂以收到的一路数据为例,如图10所示,上位机收到的部分数据㊂ 146F 作为数据帧头, EB90 作为数据帧尾,中间为数据,从01到FF一共255个字节㊂图10㊀数据帧格式上位机接收完毕后,点击软件上的 读取数据 按钮,设备开始读出的数据同时将数据保存到计算机中㊂上位机软件上传数据界面如图11所示㊂图11㊀上位机上传数据界面数据完全保存之后,点击软件上的 数据分析 按钮对数据中的丢帧和错误帧进行分析等㊂分析结果如图12所示㊂一共收到2048MByte数据,总帧数为7C97D9㊂经软件分析没有出误码或数据丢失情况,数据传输稳定可靠㊂板卡的测速界面,如图13所示㊂上位机对从PXI接口收到的数据执行1500次读取操作,一次读取512KB,图12㊀数据分析结果通过测试得知,一共用了7s完成1500次采集,根据速度公式:1500ˑ0.5MB/7s=107MB/s,速度较快㊂图13㊀上位机界面5㊀结束语该设计单独使用FPGA实现了PXI接口,节约了PCI9054㊁PCI9052等专用PCI芯片,可以降低成本,加快PXI接口的开发周期㊂同时,速度可以到达107MB/s,误码率和数据丢失情况基本为0㊂再结合LVDS㊁PXI和FPGA优点可以有效解决采集设备与计算机的高速数据传输问题㊂参考文献:[1]㊀杨文豪.基于PXI总线的高速图像采集模块的设计与实现[D].太原:中北大学,2017.[2]㊀闵亚军.基于PXI总线的模数转换模块设计与实现[D].成都:电子科技大学,2017.[3]㊀樊刘华,彭旭锋,张跃林.基于双通信接口的多通道信号源设计[J].电子器件,2017(4):833-837[4]㊀张鹏飞,冯春阳,王玮,等.基于PXI总线的A/D数据采集模块设计[J].电子技术应用,2012,38(11):87-90.[5]㊀来卫国.10位BLVDS串化器DS92LV1023和解串器DS92LV1224的原理及应用[J].电子设计工程,2002(8):45-47.[6]㊀薛隆全,文丰,张时华.基于LVDS总线的高速长距数据传输的设计[J].电子设计工程,2009,17(2):45-46;48.[7]㊀代云启.PXI总线高速数据采集模块研制[D].桂林:桂林电子科技大学,2009.[8]㊀孟庆辉.基于FPGA的PCI接口设计[D].哈尔滨:哈尔滨工业大学,2006.[9]㊀郭凡.PXI总线接口的设计与应用[D].武汉:华中科技大学,2009.[10]㊀方明.基于FPGA开发的CPCI总线多功能卡及WDM驱动程序设计与实现[D].上海:上海交通大学,2009.作者简介:白宏义(1993 ),硕士研究生,主要研究方向为动态测试㊁数据采编存储㊂E⁃mail:1248426876@qq.com李锦明(1971 ),副教授,主要研究方向为动态测试㊁智能仪器技术㊂。

PCB高速板4层以上的设计经验PCB高速板4层以上的布线经验:1、3点以上连线,尽量让线依次通过各点,便于测试,线长尽量短。

2、引脚之间尽量不要放线,特别是集成电路引脚之间和周围。

3、不同层之间的线尽量不要平行,以免形成实际上的电容。

4、布线尽量是直线,或45度折线,避免产生电磁辐射。

5、地线、电源线至少10-15mil以上(对逻辑电路)。

6、尽量让铺地多义线连在一起,增大接地面积。

线与线之间尽量整齐。

7、注意元件排放均匀,以便安装、插件、焊接操作。

文字排放在当前字符层,位置合理,注意朝向,避免被遮挡,便于生产。

8、元件排放多考虑结构,贴片元件有正负极应在封装和最后标明,避免空间冲突。

9、目前印制板可作4—5mil的布线,但通常作6mil线宽,8mil线距,12/20mil焊盘。

布线应考虑灌入电流等的影响。

10、功能块元件尽量放在一起,斑马条等LCD附近元件不能靠之太近。

11、过孔要涂绿油(置为负一倍值)。

12、电池座下最好不要放置焊盘、过空等,PAD和VIL尺寸合理。

13、布线完成后要仔细检查每一个联线(包括NETLABLE)是否真的连接上(可用点亮法)。

14、振荡电路元件尽量*近IC,振荡电路尽量远离天线等易受干扰区。

晶振下要放接地焊盘。

15、多考虑加固、挖空放元件等多种方式,避免辐射源过多。

高速PCB过孔设计技巧在高速PCB板设计中,过孔设计是一个重要因素,它由孔、孔周围的焊盘区和POWER层隔离区组成,通常分为盲孔、埋孔和通孔三类。

在PCB板设计过程中通过对过孔的寄生电容和寄生电感分析,总结出高速PCB板过孔设计中的一些注意事项。

目前高速PCB板的设计在通信、计算机、图形图像处理等领域应用广泛,所有高科技附加值的电子产品设计都在追求低功耗、低电磁辐射、高可靠性、小型化、轻型化等特点,为了达到以上目标,在高速PCB板设计中,过孔设计是一个重要因素。

1、过孔过孔是多层PCB板设计中的一个重要因素,一个过孔主要由三部分组成,一是孔;二是孔周围的焊盘区;三是POWER层隔离区。

LVDS信号的PCB设计1、LVDS信号的工作原理和特点对于高速电路,尤其是高速数据总线,常用的器件一般有:ECL、BTL、GTL和GTL+等。

这些器件的工艺成熟,应用也较为广泛,但都存在一个共同的弱点,即功耗大。

新兴的CMOS工艺的低电压差分信号器件(即Low Voltage Differencial Signal 简称LVDS )给了我们另一种选择。

可以说LVDS器件为高速低功耗电路设计提供了新的选择,得到广大硬件工程师的钟爱。

LVDS器件的工作原理如下:其中发送端是一个为3.5mA的电流源,产生的3.5mA的电流通过差分线的其中一路到接收端。

由于接收端对于直流表现为高阻,电流通过接收端的100欧姆的匹配电阻产生350mA 的电压,同时电流经过差分线的另一条流回发送端。

当发送端进行状态变化时它通过改变流经100欧姆电阻的电流的方向产生有效的'0'和'1'态。

LVDS的特点是电流驱动模式,低电压摆幅350mV可以提供更高的信号传输率,使用差分传输的方式可以使信号的噪声和EMI都减少:LVDS有以下主要特点:A、低的输出电压摆幅(350mV)B、低的信号边缘变化率, dV/dt 0.350V/0.5ns = 0.7V/nsC、差分特征是磁干扰相互抵销,消除共模噪声,减少EMI。

2、LVDS信号在PCB上的要求1)只要有LVDS信号的板最少都要有四层。

LVDS信号布在与地平面相邻的布线层。

例如,对于四层板而言,通常可以按以下进行层排布;LVDS信号层、地层、电源层、其他信号层。

2)对于LVDS信号,必须进行阻抗控制(通常将差分阻抗控制在100欧姆)。

对于不能控制阻抗的PCB布线必须小于500MIL。

这样的情况主要表现在连接器上,所以在布局时要注意将LVDS器件放在靠近连接器处,让信号从器件出来后就经过连接器到达另一单板。

同样,让接收端也靠近连接器,这样就可以保证板上的噪声不会或很少耦合到差分线上。