第二十一次课 触发器逻辑功能的描述2

- 格式:pdf

- 大小:1.56 MB

- 文档页数:55

例题:1用与非门组成的基本RS 触发器如图(a )所示,设初始状态为0,已知输入R 、S 的波形图如下图,画出输出Q 、Q 的波形图。

&&G G 12(a)(b)R RS SQQQ Q解:由可画出输出Q 、Q 的波形如图所示。

图中虚线所示为考虑门电路的延迟时间的情况。

2主从JK 触发器如图所示,设初始状态为0,已知输入J 、K 的波形图如图,画出输出Q 的波形图。

CP G 4G Q 1J 1K Q(b)3C1&G &G 2&1&&7G &56&CP8&G G G 19G ''┌┌(a)触从器发主触发器QQ Q Q J K解:如图所示。

3维持—阻塞D触发器如图所示,设初始状态为0,已知输入D的波形图如图所示,画出输出Q的波形图。

解:由于是边沿触发器,在波形图时,应注意以下两点:(1)触发器的触发翻转发生在时钟脉冲的触发沿(这里是上升沿)。

(2)判断触发器次态的依据是时钟脉冲触发沿前一瞬间(这里是上升沿前一瞬间)输入端的状态。

根据D触发器的功能表或特性方程或状态转换图可画出输出端Q的波形图如图所示。

12345CPDQ图波形图第22章时序逻辑电路大纲要求:掌握时序逻辑电路的特点及组成了解时序逻辑电路的分析步骤和方法,计数器的状态转换表、状态转换图和时序图的画法;触发器触发方式不同时对不同功能计数器的应用连接掌握计数器的基本概念、功能及分类了解二进制计数器(同步和异步)逻辑电路的分析了解寄存器和移位寄存器的结构、功能和简单应用了解计数型和移位寄存器型顺序脉冲发生器的结构、功能和分析应用计数器是数字电路和计算机中广泛应用的一种逻辑部件,可累计输入脉冲的个数,可用于定时、分频、时序控制等。

按计数功能:加法计数器、减法计数器、可逆计数器按计数脉冲引入方式:异步计数器、同步计数器按计数制:二进制计数器、十进制计数器、N 进制计数器22.1 二进制计数器按二进制的规律累计脉冲个数,它也是构成其它进制计数器的基础。

触发器逻辑功能的几种方法触发器是一种数据库对象,它可以在数据修改时自动执行指定的操作。

触发器的逻辑功能可以通过多种方法来实现。

下面将介绍几种常用的方法。

1. 使用SQL语句实现逻辑功能使用SQL语句可以实现触发器的逻辑功能。

在触发器中可以使用 INSERT、UPDATE、DELETE 语句来对其他表或触发器中的数据进行操作。

例如,可以创建一个触发器,在插入一条新记录时,自动将记录的信息插入到另一个表中。

具体实现如下:CREATE TRIGGER `insert_trigger` AFTER INSERT ON `table1` FOR EACH ROW BEGIN INSERT INTO `table2`(`col1`, `col2`) VALUES (NEW.`col1`, NEW.`col2`); END;上述代码中,insert_trigger 是触发器的名称,table1 和 table2 是两个表的名称。

当在 table1 中插入一条记录时,触发器会自动将这条记录的 col1 和 col2 列的值插入到 table2 中。

2. 使用存储过程实现逻辑功能存储过程是一种预先编译的SQL语句集合,可以在需要时直接调用。

使用存储过程也可以实现触发器的逻辑功能。

例如,可以创建一个存储过程,完成将记录的信息插入到另一个表的操作。

具体实现如下:CREATE PROCEDURE `insert_procedure`(IN `col1_value` INT, IN `col2_value` VARCHAR(50)) BEGIN INSERT INTO`table2`(`col1`, `col2`) VALUES (`col1_value`, `col2_value`); END;上述代码中,insert_procedure 是存储过程的名称,table2 是目标表的名称。

当需要将一条记录的信息插入到 table2 中时,可以调用此存储过程,将需要插入的值作为参数传递进去。

数字电子技术基础阎石主编(第五版)信息科学与工程学院基础部SR锁存器电平触发的触发器脉冲触发的触发器基本RS 触发器同步结构的触发器主从结构的触发器【】内容回顾时序逻辑电路的最基本部件-双稳态触发器边沿触发的触发器边沿结构的触发器1K1JC1QQ ′CLKJK >1K1JC1QQ ′CLKJK>上升沿触发下降沿触发【例1】分析边沿JK触发器的输出波形(设初态为0状态) 。

(下降沿触发)CLKJKQ置1置0保持保持置1置0保持【例2】分析边沿JK 触发器的输出波形(设初态为0状态) 。

(上升沿触发)CLK K J Q保持5.6 触发器的逻辑功能及其描述方法5.6.1 触发器按逻辑功能的分类(时钟触发器)一 、SR 触发器 按照逻辑功能触发器可分为SR 触发器、JK 触发器、D 触发器、T 触发器和T ′触发器 凡在时钟信号作用下,具有如右表所示功能的触发器称为SR 触发器2.约束条件=SR 1.定义:表S 0000011110000*********1100R 0111Q Q *1*1*SRQ010********. 特性方程:由特性表和约束条件画出输出端Q *的卡诺图为111××则可写出触发器输出端的方程为⎪⎩⎪⎨⎧=′+=∗0SR Q R S Q SR 触发器的特性方程。

表S 00000111100000001111111100R 0111Q Q *1*1*4.状态转换图:将触发器的特性表用图形方式表现出来,即为状态转换图S 00000111100000001111111100R 0111Q Q *1*1*00状态11状态1S =1R =0S =0R =1S =×R =0S =0R =×5. 逻辑符号二、JK触发器1.定义:凡在时钟信号作用下,具有右表功能的触发器称为JK触发器。

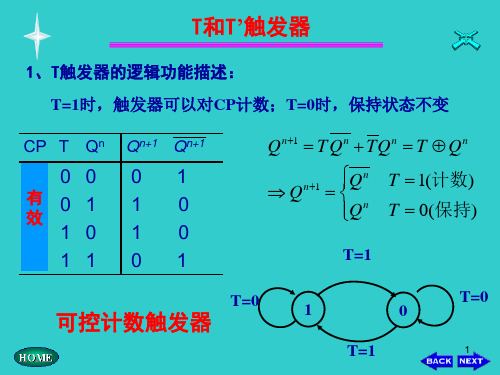

表J000 011110011111111K111Q Q*12.特性方程:由特性表可得输出端卡诺图为JK Q1000011111111特性方程为QKQJQ′+′=*3.状态转换图:由特性表可得状态转换图表J 00000111100000001111111100K 0111Q Q *101J = ×K =1J =×K =0J =0K =×J =1K = ×4. 逻辑符号:1K1JC1QQ ′CLKJK>1K1JC1QQ ′CLKJK>三 、T 触发器2.特性方程:QT Q T Q ′+′=*凡在时钟信号作用下,具有下表所示功能的触发器称为T 触发器1.定义:由特性表可得00100011110T 1Q Q *表3.状态转换图:由特性表可得状态转换图00100011110T 1Q Q *表边沿触发器,时钟下降沿触发4. 逻辑符号:令JK 触发器的J =K =T ,就可实现T 触发器。

触发器。

称为时,特别得,当',*1T Q Q T ′==四 、D 触发器DQ =*2.特性方程: 凡在时钟信号作用下,具有下表所示功能的触发器称为D 触发器。

1.定义:由特性表可得00100011110D 1Q Q *表3.状态转换图:边沿触发器,时钟上升沿触发由特性表可得状态转换图4. 逻辑符号:00100011110D 1Q Q *表(e) D 触发器DQ =*(c) T 触发器QT Q T Q ′+′=*(b) JK 触发器QK Q J Q ′+′=*⎪⎩⎪⎨⎧=′+=0*SR Q R S Q (a) RS触发器(d) T (d) T’’触发器Q Q ′=*【例1】已知触发器初态为0,画出在CLK 信号连续作用下各触发器的输出波形 。

1*1==D Q 22*Q D Q ′==333*Q K Q J Q ′+′=3333)(Q Q Q Q ′′+′=3Q =CLKQ 1Q 2Q 3Q 1CLKC11D>Q 2CL KC11D>Q 3CLKC11J>1K【例2】已知触发器初态为0,画出在CLK 信号连续作用下各触发器的输出波形 。

Q 2CLK C11D>Q 3CLK C11J>1KQ 1CLK C11N>Q 5CLK C11J>1KQ 4CLK C11N>Q 6CLKC11J 1K续作用下各触发器的输出波形 。

↓′=,Q Q *1↑=,Q Q *2↓=,Q Q *3QK JQ Q ′+=*Q 2CLK C11D>Q 3CLK C11J>1KQ 1CLK C11N>QT Q T Q ′+′=*续作用下各触发器的输出波形 。

↑=,1*4Q ↑′=,Q Q *5,┓Q Q ′=*6Q 5CLK C11J>1KQ 4CLK C11N>Q 6CLKC11J 1KQK JQ Q ′+=*QT Q T Q ′+′=*↓′=,11*Q Q ↑=,22*Q Q ↓=,33*Q Q ↑=,1*4Q ↑′=,55*Q Q ,┓66*Q Q ′=【例2】已知触发器初态为0,画出在CLK 信号连续作用下各触发器的输出波形 。

CLKQ 1Q 2Q 3Q 4Q 5Q 6【例3】 边沿触发器组成的电路如图所示,已知其输入波形,试分别画出Q 1、Q 2端的波形。

端的波形。

设电路初态均为0。

1212345CLK ABQ Q C)(111′==+AQ D Q n BA QB A Q B A Q K Q J Q BA KB A J ⊕=′⊕′+′⋅⊕=′+′=⊕′=⊕=*)()(,5.6.2 触发器的电路结构和逻辑功能、触发方式的关系一、电路结构和逻辑功能触发器的电路结构和逻辑功能之间不存在固定的对应关系如SR触发器可以是电平触发的同步结构,也可以是脉冲触发的主从结构。

同步SR触发器主从结构的SR触发器图5.4.1同样的JK触发器有主从结构的和维持阻塞结构的二、电路结构和触发方式触发器的触发方式是由电路结构决定的,即电路结构形式与触发方式之间有固定的对应关系如同步SR 触发器属于电平触发,在CLK =1触发器动作SRC L KtttQ采用主从结构的触发器,属于脉冲触发方式,是在CLK 的下降沿(的下降沿(↓↓)触发器的状态发生变化。

如主从SR 触发器和主从JK 触发器SRC L KtttQt主从JK 触发器:JKC L KtttQt主从JK 触发器:5.6触发器的逻辑功能及其描述方法01K 1Q 11J 0Q 置的信号进入主触发器时,只允许置的信号进入主触发器时,只允许,,====采用两个电平触发D 触发器构成的触发器、维持阻塞结构的触发器以及利用门传输延迟时间构成的触发器都属于边沿触发方式如维持阻塞D 触发器属于上升沿触发0DC L KtttQ边沿JK 触发器1J 1KC 1QQ ′J KC L K5.7 集成触发器及其应用常用集成触发器目前市场上出售的集成触发器产品通常为JK触发器和D触发器两种类型。

5.7.1 集成JK 触发器集成JK 触发器74LS112 74LS112为下降沿触发的双JK 触发器。

S D 、R D 分别为异步置1端和异步置0端,均为低电平有效。

常用的有74LS112、CC4027等。

1. 74LS112的外引脚图和逻辑符号2. 2. 逻辑功能逻辑功能 74LS11274LS11274LS112的功能表的功能表3.3. 时序图时序图异步置0异步异步置1异步置0异步5.7.2集成D触发器1.双D触发器74LS74外引脚图和逻辑符号双D触发器74LS74(a) 外引脚图 (b)逻辑符号2.2. 逻辑功能逻辑功能双D触发器74LS74的功能表触发方式为CP上升沿触发。

低电平有效的异步置异步置00端和异步置异步置11端3.时序图3. 时序图置D异步置1置D 74LS74的时序图异步置05.7.3 触发器逻辑功能的转换Q′CLKJK触发器:逻辑功能最完善D触发器:单端输入,使用最方便1. JK →RS 触发器(1)写出已有、待求触发器的特性方程:JK 触发器:Q K Q J Q ′+′=*⎪⎩⎪⎨⎧=′+=0*SR Q R S Q RS 触发器:(2) 将待求触发器的特性方程变换为与已有触发器的特性方程一致 :QR Q Q S Q R S Q ′+′+=′+=)(*Q S Q R S Q R Q S SQ ′+′+=′+′+=)()(,′′+==R S K S J 则0=SR ∵又(3)比较两个特性方程,求出转换逻辑 :RS ′=R SR R S R S K =+′=+′=∴01. JK→RS触发器令:J = S,K = R (4) 画电路图2. JK→D触发器令:J = D,K=D′3. JK→T触发器令:J = K=T4. JK→T’触发器令:J = K=15. D →T ’触发器Q D ′=令:7. D →JK 触发器QK Q J Q ′+′=*DQ =*QK Q J D ′+′=令:设计要求:四人参加比赛,每人一个按钮,其中最先按下按钮者,相应的指示灯亮;其他人再按按钮不起作用。

电路的核心是74LS175四D 触发器。

其内部包含了四个D 触发器,各输入、输出以字头相区别,管脚图见下页。

5.7.45.7.4应用举例------四人抢答器CLR D CP QQ CLRD CPQ Q CLR D CP Q Q CLR D CP Q Q 1Q Q 11D 2Q Q 22D GND 4Q Q 44D 3Q Q 33D 时钟清零U SC 公用清零公用时钟74LS175管脚图+5V 1Q 1Q 2Q 2Q 3Q 3Q 4Q 4Q D 1D 2D 3D 4CLR CP & 1& 2& 2清零CP 赛前先清零0输出为零发光管不亮74LS175。