【精品博文】基于FPGA的原理图PCB设计

- 格式:doc

- 大小:13.52 KB

- 文档页数:3

基于FPGA\CPLD最小系统PCB的制作电子信息科学与技术专业:何胜军指导教师:郭杰荣摘要:基于FPGA\CPLD最小系统PCB的制作是通过PROTEL软件来实现的。

本文讲述的是利用在1999年,PROTEL公司推出的新一代电子线路设计系统——PROTEL99软件来绘制完整的最小系统电路原理图,并进行电气规则检测、生成网络报表以及对PCB进行布局、布线、工艺流程,制作出最小系统EDA的双面PCB。

EDA最小系统具有系统控制、功能实现以及结果显示的功能。

本文是以ALTERA公司MAX7128S系列的EPM7128SLC84-15CPLD芯片为中心,利用外围的AT89C51单片机、按键开关、ROM、数码显示管来完成一个完整的EDA最小系统。

关键词:FPGA\CPLD,PROTEL99,双面PCB,最小系统Designing of the Minimum System PCB Basedon FPGA \CPLDElectronic and Information Science and TechnologyCandidate:He Sheng-JunAdvisor:Guo Jie-rongAbstract: A minimum system PCB which is based on FPGA\CPLD can be realized by using PROTELL99. This article tells us how to draw a complete circuit of a minimum system through using a new generation circuit design system-PROTEL99 which is released by PROTEL company in 1999, and makes out the double-side PCB by running the electrical check, generating netlist and placing, routing PCB and designing the technology process. EDA minimum system has functions including system control function realizing and result showing. This article is centered around on ALTERA company’s chip EPN7128S2C84-15CPLD of the series of MAX7128S, and completes EDA minimum system with the use of AT89C51 single-chip microcomputer, keyboard switch and digit display.Keywords:FPGA\CPLD, PROTEL99, Double-side PCB, Minimum system引言在电子竞赛设计中,可编程逻辑器件作为系统的控制核心已广泛应用。

如何实现FPGA设计与PCB设计并行复杂度日益增加的系统设计要求高性能FPGA的设计与PCB设计并行进行。

通过整合FPGA和PCB设计工具以及采用高密度互连(HDI)等先进的制造工艺,这种设计方法可以降低系统成本、优化系统性能并缩短设计周期。

图1:FPGA和PCB设计团队必须并行工作,不断地交换数据和信息以确保系统设计成功。

电子工业背后的推动力是对更快、更便宜的产品的需求以及在竞争厂商之前将产品推向市场。

IC技术的进步一直以来就是促使功能增加和性能提高的主要因素之一,而FPGA技术也一直以非常快的速度在发展。

与过去FPGA仅仅用作胶合逻辑不同的是,现在FPGA 已经被用来实现主要系统功能。

FPGA的逻辑门数已达1千万,内核速度达到400MHz,能提供高达11Gbps的下一代芯片间通信速度。

而与此同时,它仍然保持着非常合理的成本,因此,与ASIC和定制IC相比,FPGA是一种更具有吸引力的选择。

IC和FPGA技术的进步对下游产业产生的效应影响到了PCB行业,这些高管脚数和高性能封装推动新的PCB生产及设计技术具有诸如嵌入无源器件、数千兆位信号和EMI分析等功能,并对专用的高密度和高性能布线提出了需求。

基本的系统设计方法也在发生变化,对FPGA和PCB的设计可以并行进行以降低系统成本、优化系统性能并缩短设计周期。

PCB和FPGA一般是在不同的设计环境下创建,过去这些设计方案很少相互沟通。

然而,随着高性能、高密度FPGA器件的日益流行,为满足紧张的上市时间表,如今PCB和FPGA 设计团队必须并行工作(见图1),不断地交换数据和信息以确保整个系统设计获得成功。

当在PCB上实现高端FPGA时,设计工程师面临性能优化和系统设计生产率的双重挑战。

设计工程师必须问自己:是什么问题使得过程慢了下来?需要做什么来获得最佳性能?这些问题的答案可帮助他们鉴别可实现更小、更便宜和更快系统的解决方案。

设计效率的挑战设计工程师需要并行设计PCB和FPGA时,FPGA设计工程师再也不能像以前那样独立地设计,然后将完成的FPGA设计交给PCB设计工程师就可了事。

fpga原理图设计方法

FPGA原理图设计方法如下:

1. 准备工作

在开始设计FPGA原理图之前,首先需要明确设计目标,了解所需电路功能,并准备好设计所需的电路元件、电源以及相关工具和软件。

2. 确定电路结构

根据电路功能和要求,设计电路的整体结构。

通常可以将电路划分为几个模块,然后根据模块功能设计对应的电路。

3. 绘制原理图

使用电子设计自动化工具(EDA工具)来绘制FPGA的原理图。

在绘制原理图时,应按照电路结构逐个模块进行绘制,并使用合适的元件符号和连线方式。

4. 连接电路元件

根据电路结构和原理图,逐个连接电路元件。

注意保持电路的连续性和正确性,在绘制连线时避免交叉和短路。

5. 添加电源和地

为电路添加合适的电源和地引脚,并按照原理图正确连接电源和地线。

在连接时,确保电源和地的连接正确无误,并符合电路的电源要求。

6. 绘制引脚定义

根据电路功能和FPGA引脚规格,在原理图中添加引脚定义。

引脚定义通常包括输入、输出以及其他特殊功能引脚。

7. 进行验证和修改

完成原理图绘制后,对原理图进行验证,确保电路设计无误。

如果发现问题或需要修改,及时进行调整和改进。

8. 生成输出文件

根据原理图和设计需求,使用EDA工具将原理图转化为

FPGA的可配置文件(如HDL代码或bit文件),以便后续进

行FPGA的配置和实现。

以上是FPGA原理图设计的一般方法,根据具体的设计需求

和EDA工具的使用习惯,可能还需要进行其他操作或步骤。

注意在设计过程中,避免出现相同的文字或标题,以免混淆和歧义。

利用高速FPGA设计PCB的要点及相关指导原则随着现场可编程门阵列(FPGA)已发展成为真正的可编程系统级芯片,利用这些芯片设计印制电路板(PCB)的任务变得愈加复杂。

目前动辄数百万门的电路密度和6Gbps以上的收发器数据传输率及其它考虑事项影响着系统开发人员在机械和电气方面的板级设计工作。

裸片、芯片封装和电路板构成了一个紧密连结的系统,在这个系统中,要完全实现FPGA的功能,需要对PCB板进行精心设计。

采用高速FPGA进行设计时,在板开发之前和开发期间对若干设计问题进行考虑是十分重要的。

其中包括:通过滤波和在PCB板上的所有器件上均匀分配足够功率来减小系统噪声;正确端结信号线,以把反射减至最小;把板上迹线之间的串扰降至最低;减小接地反弹和Vcc降低(也称为Vcc凹陷)的影响;正确匹配高速信号线上的阻抗。

任何人在为性能极高的FPGA设计IC封装时,都必须特别注意信号完整性和适于所有用户和应用的多功能性之间的平衡问题。

例如,Altera最大的Stratix II GX器件采用1,508引脚封装,工作电压低至1.2V,并具有734个标准I/O、71个低压差分信令(LVDS)信道。

它还有20个高速收发器,支持高达6.375Gbps的数据率。

这就让该架构能够支持许多高速网络和通信总线标准,包括PCI Express和SerialLite II。

在设计中,用户可以通过优化引脚排列来减少串扰。

信号引脚应该尽可能靠近接地引脚,以缩短封装内的环路长度,尤其是重要的高速I/O。

在高速系统中,主要的串扰源是封装内信号路径之间的电感耦合。

当输出转换时,信号必须找到通过电源/接地平面的返回路径。

环路中的电流变化产生磁场,从而在环路附近的其它I/O引脚上引起噪声。

同时转换输出时,这种情形加剧。

因为环路越小,感应就越小,故电源或接地引脚靠近每个高速信号引脚的封装可以把附近I/O引脚上的串扰影响减至最小。

为了把电路板成本降至最低,并把所有信号路径的系统信号完整性提高到最大,需要对电路板材料、分层数目(堆叠)和版图进行精心的设计和构建。

基于高速FPGA的PCB设计技术如果高速PCB设计能够像连接原理图节点那样简单,以及像在计算机显示器上所看到的那样优美的话,那将是一件多么美好的事情。

然而,除非设计师初入PCB设计,或者是极度的幸运,实际的PCB设计通常不像他们所从事的电路设计那样轻松。

深圳捷多邦科技有限公司作为PCB打样行业的一匹黑马,始终走在PCB打样行业的前列。

捷多邦的高级工程师在谈到这样一个问题时说到,在设计最终能够正常工作、有人对性能作出肯定之前,PCB设计师都面临着许多新的挑战。

这正是目前高速PCB设计的现状--设计规则和设计指南不断发展,如果幸运的话,它们会形成一个成功的解决方案。

绝大多数PCB是精通PCB器件的工作原理和相互影响以及构成电路板输入和输出的各种数据传输标准的原理图设计师与可能知道一点甚至可能一点也不知道将小小的原理图连线转换成印刷电路铜线后将会发生什么的专业版图设计师相互合作的成果。

通常,对最终电路板的成败负责的是原理图设计师。

但是,原理图设计师对优秀的版图技术懂得越多,避免出现重大问题的机会就越多。

如果设计中含有高密度的FPGA,很可能会有许多挑战摆放在精心设计的原理图前面。

包括数以百计的输入和输出口数量,超过500MHz(某些设计中可能更高)的工作频率,以及小至半毫米的焊球间距等,这些都将导致设计单元之间产生不应有的相互影响。

并发开关噪声第一个挑战很可能就是所谓的并发开关噪声(SSN)或并发开关输出(SSO)。

大量的高频数据流将在数据线上产生振铃和串扰之类的问题,而电源和地平面上也会出现影响整个电路板性能的地线反弹和电源噪声问题。

为了解决高速数据线上的振铃和串扰,改用差分信号是很好的第一步。

由于差分对上的一条线是吸收(Sink)端,另一条提供源电流,因此能从根本上消除感应影响。

利用差分对传输数据时,由于电流保持在局部,因此有助于减小返回路径中的感应电流产生的反弹噪声。

对于高达数百MHz甚至数GHz的射频,信号理论表明,在阻抗匹配时可以传送最大信号功率。

PCB 光板测试机基本的测试原理是欧姆定律,其测试方法是将待测试点间加一定的测试电压,用译码电路选中PCB 板上待测试的两点,获得两点间电阻值对应的电压信号,通过电压比较电路,测试出两点间的电阻或通断情况。

重复以上步骤多次,即可实现对整个电路板的测试。

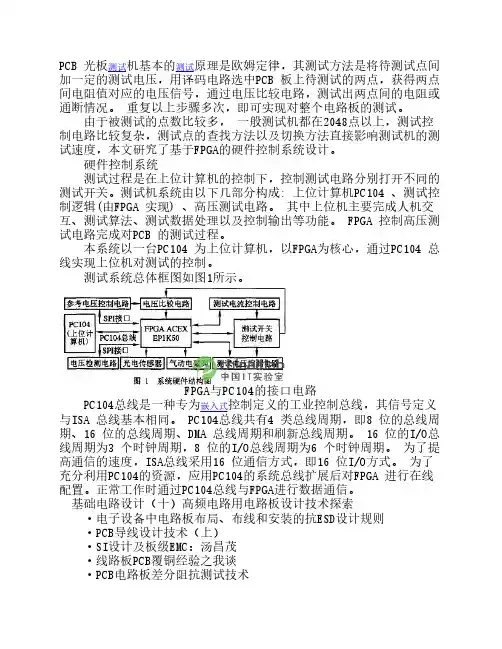

由于被测试的点数比较多, 一般测试机都在2048点以上,测试控制电路比较复杂,测试点的查找方法以及切换方法直接影响测试机的测试速度,本文研究了基于FPGA的硬件控制系统设计。

硬件控制系统 测试过程是在上位计算机的控制下,控制测试电路分别打开不同的测试开关。

测试机系统由以下几部分构成: 上位计算机PC104 、测试控制逻辑(由FPGA 实现) 、高压测试电路。

其中上位机主要完成人机交互、测试算法、测试数据处理以及控制输出等功能。

FPGA 控制高压测试电路完成对PCB 的测试过程。

本系统以一台PC104 为上位计算机,以FPGA为核心,通过PC104 总线实现上位机对测试的控制。

测试系统总体框图如图1所示。

FPGA与PC104的接口电路 PC104总线是一种专为嵌入式控制定义的工业控制总线,其信号定义与ISA 总线基本相同。

PC104总线共有4 类总线周期,即8 位的总线周期、16 位的总线周期、DMA 总线周期和刷新总线周期。

16 位的I/O总线周期为3 个时钟周期,8 位的I/O总线周期为6 个时钟周期。

为了提高通信的速度,ISA总线采用16 位通信方式,即16 位I/O方式。

为了充分利用PC104的资源,应用PC104的系统总线扩展后对FPGA 进行在线配置。

正常工作时通过PC104总线与FPGA进行数据通信。

基础电路设计(十)高频电路用电路板设计技术探索 ·电子设备中电路板布局、布线和安装的抗ESD设计规则 ·PCB导线设计技术(上) ·SI设计及板级EMC:汤昌茂 ·线路板PCB覆铜经验之我谈 ·PCB电路板差分阻抗测试技术 ·PCB导线设计技术(下) 根据测试机系统设计要求,需要对测试电压及两通道参考电压进行自检,即A/D转换通道至少有3 路。

引言随着经济和科学技术的发展,电梯在高层建筑物的作用越来越凸出。

目前电梯主要分为机械系统与控制系统两大部份,而电梯的控制系统主要有三种控制方式分别是:继电路控制系统(“早期安装的电梯多位继电器控制系统)、基于FPGA控制系统、微机控制系统。

实现继电路控制系统方法很多,可以用标准逻辑器件、可编程序控制器PLC、单片机等方案来实现。

但是这些方法的功能修改及调试都需要硬件电路的支持,在一定程度上增加了功能修改及系统调试的困难,且该系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,已渐渐被人民淘汰。

微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷,没能广泛应用电梯中。

而基于FPGA的电梯控制系统由于可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点,在电梯控制中得到广泛应用,从而使电梯由传统的继电器控制方式发展为计算机控制的一个重要方向,成为当前电梯控制和技术改造的热点之一。

本文给出一个基于FPGA的6层自动升降电梯控制系统的设计方案。

它的设计是采用通俗易懂的Verilog HDL硬件描述语言使用EDA技术在Quartus II软件平台上设计完成,程序设计、编译以及时序仿真通过后再下载到开发板配合外围电路(模拟电梯的电路)来验证该系统的可行性。

这个系统分主要有6个模块,分别是键盘响应寄存处理模块、上升/下降请求寄存处理模块、电梯运行和停止处理模块、开门/关门与延时处理模块、电梯运行方向判断模块和电梯运行状态显示模块。

通过模块化设计不仅提高了程序编程错误的排查能力还提高了系统的可靠性。

1 概论1.1 电梯国内外现状1.1.1国内现状电梯作为中国对外最早的行业经过多年的发展,电梯产品无论在数量和质量都有了显著的提高,和国外产品差距越来越小。

考虑到经济性,现有国内的电梯控制系统,通常采用微机或可编程逻辑控制器对变频器进行多段速控制。

![毕业设计(论文)-基于fpga的电路设置[管理资料]](https://uimg.taocdn.com/e964cc9527d3240c8547ef07.webp)

摘要FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

目前以硬件描述语言(Verilog 或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至FPGA 上进行测试,是现代IC 设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,一个出厂后的成品FPGA的逻辑块的连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

本文设计的实验板目的就是验证所设计的电路的逻辑功能。

实验板以EP1C6Q240C8为主,配以存储器、数据配置、复位、实时时钟、I/O口分配、扩展接口、独立按键及LED、液晶显示、数码管显示、蜂鸣器和电源等功能电路。

而其中的独立按键及LED、液晶显示、数码管显示、蜂鸣器就是验证时的直接展现。

关键字:FPGA,硬件原理图,测验ABSTRACTFPGA(Field-Programmable Gate Array),It is based on the further development of the product of PAL、GAL、CPLD etc.. It is in the field of application-specific integrated circuit (ASIC)for a half customize the circuit, it solves the shortage, and custom circuit overcomes original programmable gate device limited number of faults. Now completed the above circuit design by the Hardware description language, can pass by the simple integrated and layout, rapid replication to test on FPGA, it is the mainstream of modern IC design verification. These can edit component can be used to achieve some basic logic gate(such as AND、OR、XOR、NOT ) or, more complex combination of some functions such as decoder or mathematical equations. In most of the FPGA, these can edit component also includes memory devices such as flip-flop or other more complete memory block. According to the system designer, through the FPGA links can edit the internal logic pieces together. One of the products of the factory, logical block of FPGA can be changed according to the designer, so the FPGA can complete the required logic functions.The purpose of this experimental plate is to verify that the logic function of circuit. The primary device is EP1C6Q240C8 on this experimental plate, use with the circuit of memory, Data configuration, reset, real-time clock, I/O port, expand interface, independent buttons and LED, LCD display, digital display, buzzers and power etc.. And that the independent buttons and LED, LCD display, digital display show directly of the checkoutKey Words: FPGA, Hardware diagram, quiz目录第1章绪论 (1)设计背景 (1)设计目的和意义 (2)论文的结构安排 (2)第2章 FPGA开发板原理图分析 (3)FPGA电路 (4)存储电路 (6)Flash存储器 (6)SRSM存储器 (7)SDRAM存储器 (8)配置电路 (9)复位电路 (11)时钟电路 (12)FPGA I/O口分配电路 (13)扩展接口电路 (13)外扩I/O口PACK2 (18)外设PACK接口电路 (18)FPGA扩展接口电路 (19)验证功能电路 (17)按键及LED电路 (17)蜂鸣器电路 (18)七段数码管显示电路 (18)液晶显示电路 (19)实时时钟电路 (19)电源电路 (24)系统电源电路 (24)FPGA电源电路 (25)第3章实验板的测验 (28)读取按键信号 (28)第4章结论 (27)参考文献 (28)致谢 (29)第1章绪论设计背景半导体技术一直遵循著名的摩尔定律持续地发展,回顾半导体的发展历史,当一种技术具有可编程特性时,它就会处于支配的地位。

毕业设计(论文)-基于FPGA的电机控制————————————————————————————————作者:————————————————————————————————日期:基于FPGA的电机控制指导老师:设计了一个基于现场可编程门阵列(FPGA)的电机控制系统。

简单介绍了步进电机和直流电机的工作原理和工作特点,并根据两种电机的不同特性设计了基于FPGA的不同的控制电路:以改变频率来控制步进电机的转速;调节脉冲的占空比大小改变输出电压的大小,从而达到控制直流电机的转速的目的。

关键字:FPGA 步进电机直流电机电机控制PWMDesign of the Motor-Control Based on FPGAAbstract: the electromotor control system is designed based on FPGA. This paper simply introduces the principle and the characrers of current-motor and step-motor.And what’s more,different control circuits based FPGA are designed accordering to the different characteristic of current-motor and step-motor. The rotate speed of step-motor is controlled by changing frequency .The output-voltage changes accordering to the rate of impulses,and so the aim to control the rotate of current-motor achieve.Keyword : step-motor motor-control PWM FPGA目录1.系统设计 (3)1.1功能介绍 (3)1.2电机控制简介 (3)1.2.1步进电机的控制 (3)1.2.2直流电机的控制 (3)1.3总体设计方案 (4)1.3.1总体设计思路 (4)1.3.2方案论证与比较 (4)2.单元电路设计 (7)2.1.步进电机驱动电路 (7)2.2.直流电机驱动电路 (8)3.软件设计 (8)3.1实现方法 (8)3.2 程序流程图 (9)4.系统测试 (10)5.结论及参考文献 (10)5.1.结论: (10)5.2.参考文献: (10)6.附录 (10)前言步进电机:一般,电动机都是连续旋转,而步进电动机却是一步一步转动的。

PCB设计---PCB中的FPGA(CPLD)设计1.概述FPGA(Field Programmable Gate Array:现场可编程逻辑门阵列),是一种可编程的集成电路,通过对芯片中门电路进行编程,实现相应的逻辑功能,进而实现相应的电气功能。

FPGA具有很大的灵活性,行业应用广泛,如通信、安防、工控、国防军工等,有大量的电气设备都使用到FPGA芯片。

2.FPGA调管脚的目的PCB设计过程中,通过调整FPGA的IO管脚,实现线路短、顺畅,保证信号有更佳的层面分配、更好的电气性能…,从而保证更好满足板厚要求、层数要求、阻抗要求,降低生产成本等。

3.调管脚的一般原则(调管脚上网络)a)专用管脚不能调,如Config部分管脚;IO管脚可以交换,见图1.图1 配置管脚b)同电压bank的IO可以交换管脚,不同电压bank的IO不能交换管脚。

c)交换管脚时,优先在同一bank内进行,其次是bank间。

d)全局时钟只能在全局时钟之间交换管脚,不能和IO交换管脚上网络。

e)差分线调管脚时需要注意:原则上P对P、N对N,且是一对一对交换,不能一对差分的两根线分别交换到其他两队差分的各一根线。

f)在布线前,把自己的交换需求、交换原则和客户沟通清楚。

g)交换管脚后,需要客户确认并更新原理图;PCB设计师需要根据更新后的原理图进行网表更新,并核对。

4.Bank划分做完扇出后,根据原理图,对bank进行物理区分,建议在PCB中分出区域,便于识别。

如图2所示,对将要进行调管脚的bank进行了“分割”,每个区域对应一个bank。

图2 bank划分5.对bank中管脚基本功能的认知与分析FPGA的管脚通常可以实现多种逻辑功能,在不同应用下,要求有所不同。

例如图3所示:a.如果都用作普通IO,管脚是没有区别的;b.如果是分配给DDR3,那么DQS信号就需要放在专用的管脚上来;c.如果使用差分,需要注意对应的P和N,除非客户说明没区别。

哈尔滨工程大学本科生毕业论文基于FPGA的自动调焦电路设计与实现院(系):信息与通信工程学院专业:电子信息工程学号:学生姓名:指导教师:副教授2009年6月哈尔滨工程大学本科生毕业论文摘要随着超大规模集成电路的发展以及现代光学仪器设备在智能化、简便化方面的突破,令数字光学设备迅速普及。

数字信号处理理论的成熟与发展使得基于数字信号处理方式的自动调焦成为可能。

本设计使用FPGA作为数字信号处理与系统控制的核心器件。

将由摄像头输入的模拟电视信号转换为数字电视信号;经过FPGA处理后再将其转换为模拟电视信号输出,并由电视机显示;同时FPGA控制电机的进退实现自动调焦。

系统硬件部分以FPGA为核心,搭载输入视频处理器SAA7111AHZ与数字视频编码器SAA7120以及RAM等其他附属电路。

系统软件部分使用I2C总线实现对输入视频处理器和数字视频编码器的初始化,实现PAL制式模拟电视信号-YUV数字电视信号-PAL制式模拟电视信号的转换,并使用电视机将其输出。

根据复合视频图像信号的相关原理,对输入视频的中心区域进行灰度熵值的运算,并控制电机的转动方向以阈值法实现自动调焦。

在本设计中,完成了相关的软件和硬件设计,并经过调试后,能够实现较好效果的自动调焦。

关键词:FPGA;灰度熵;输入视频处理器;数字视频编码器哈尔滨工程大学本科生毕业论文ABSTRACTThe digtal optical equipments become popular,with the development of very-large-scale integrated circuits and the major breakthrough of the modern optical equipments in intelligentizating and facilitating process. The automatic focusing which based on digital signal processing can be realized.In this desgin, FPGA is the key component of digital signal processing and system control.Firstly, an analog TV signal captured by the camera is transformed to a digital TV signal; and then the digtal TV signal is processed by FPGA and finally it is transformed to an analog TV signal output; at the same time, the automatic focusing is realized by the motor controled by FPGA.In the hardware part of the system,FPGA is used as the key component,with accessory circuit such as video input processor, digital video encoder and so on.In the software part, the video input processor and digital video encoder is initialized throgh the I2C bus in order to realize the interconversion of PAL standard analog TV signals and YUV digital TV signals ,which are the output of monitor. According to the theory of composite video signal,the system selects the center part of the input video and calculates its gray region entropy , then control the motor rotation to realize automatic focusing using the thresholding method.In this design, the relevant software and hardware are completed, and can bring automatic focusing into effect well after testing .Key words: FPGA;Gray entropy; Video Input Processor; Digital Video Encoder哈尔滨工程大学本科生毕业论文目录第1章绪论 (1)1.1 课题背景和意义 (1)1.2 国内外研究现状 (2)1.2.1 概述 (2)1.2.2 国外研究现状 (3)1.2.3 国内研究现状 (4)1.3 主要研究内容 (5)第2章自动调焦系统相关理论 (6)2.1 复合视频图像信号 (6)2.1.1 电视扫描原理 (6)2.1.2 复合视频图像信号的组成 (6)2.1.3 复合视频图像信号主要制式 (8)2.2 I2C总线 (9)2.2.1 概述 (9)2.2.2 I2C总线的主要特点 (10)2.2.3 I2C总线的工作状态及时序 (11)2.3 自动调焦的几种主要方法 (13)2.3.1 测距方法 (13)2.3.2 聚焦检测方法 (14)2.4 基于灰度熵值法的自动调焦算法 (15)2.4.1 灰度熵值提取算法 (15)2.4.2 阈值判断算法 (15)2.5 本章小结 (16)第3章自动调焦系统的硬件设计 (17)3.1 总体方案 (17)3.2 FPGA最小系统 (18)哈尔滨工程大学本科生毕业论文3.2.1 芯片简介 (18)3.2.2 FPGA的配置 (20)3.3 视频输入处理器及系统 (22)3.3.1 SAA7111AHZ芯片简介 (22)3.3.2 SAA7111AHZ的应用电路 (23)3.4 视频输出处理器及系统 (25)3.4.1 SAA7120芯片简介 (25)3.4.2 SAA7120的应用电路 (26)3.5 其他电路设计 (27)3.5.1 电源电路 (28)3.5.2 外置RAM电路 (28)3.5.3 串口电路 (28)3.5.4 LED指示灯电路 (29)3.6 电路系统的PCB设计 (29)3.7 本章小结 (30)第4章自动调焦系统程序设计 (32)4.1 编程环境 (32)4.1.1 VHDL硬件描述语言特点 (32)4.1.2 VHDL的设计流程 (33)4.1.3 编译环境QuartusII的设计特点 (34)4.1.4 QuartusII开发软件的设计流程 (35)4.2 软件设计总体流程 (36)4.3 视频转换芯片的初始化 (36)4.3.1 I2C总线设计 (37)4.3.2 视频转换芯片的初始化寄存器设置 (37)4.4 自动调焦算法的编程实现 (41)4.5 本章小结 (44)哈尔滨工程大学本科生毕业论文第5章系统仿真、调试与性能分析 (45)5.1 系统仿真结果 (45)5.2 系统调试 (46)5.3 系统性能分析 (49)5.4 本章小结 (49)结论 (511)参考文献 (522)致谢 (555)哈尔滨工程大学本科生毕业论文第1章绪论1.1 课题背景和意义自动调焦,又称为自动对焦、自动聚焦。

基于FPGA的电子画图板设计路红娟;蒋伟【摘要】随着信息技术的不断发展,数据采集技术已成为重要的现代化工具,并且其应用范围在不断扩大,在通信、雷达、医疗、遥测遥感等领域得到了广泛的应用。

主要利用FPGA对鼠标的坐标信号进行采集,加上相关算法,实现了实时在液晶显示器上显示鼠标移动轨迹的效果。

%With the continuous developmentof information technology, data acquisition technology becomes an important modern tool, and its scope of application is expandet. It is widely used in communication, radar, medical, remote sensing and other fields. This real-time system is mainly based on a high-speed FPGA data acquisition for the mouse, with relative algorithm to display the effect of the mouse moving on the LCD monitor.【期刊名称】《机械制造与自动化》【年(卷),期】2014(000)005【总页数】3页(P120-121,125)【关键词】FPGA;鼠标;液晶显示器;数据采集【作者】路红娟;蒋伟【作者单位】无锡工艺职业技术学院,江苏宜兴214206;无锡工艺职业技术学院,江苏宜兴214206【正文语种】中文【中图分类】TP2740 引言随着科技的发展以及环保的需求,现在各行各业逐渐向无纸化时代进军,如办公无纸化,无纸实训室等等。

所以现在美术专业的学生,小孩子的涂鸦学画画等,都转向了无纸环保的电子画图板。

【精品博文】基于FPGA的原理图PCB设计电源供电方案选择由于FPGA的可编程性,同一芯片在不同应用需求下,使用的逻辑资源不一样时,功率可能会有很大差别,因此在不同应用下可根据功率等来选择不同电源方案。

之前看到看过大牛crazybingo写的一篇关于电源方案的博文,地址如下:/crazybingo/p/36109我也分享下自己用过的电源方案,到目前为止,我用过3个FPGA 方案。

(1) 方案1:3片AMS1117,这个方案应该很多人用,使用3片固定式输出LDO,用的较多的是SOT-223封装。

(2) 方案2:两片TPS7A7001 ADJ生成3.3V和1.2V,一片Sipex 6201生成2.5V。

TPS7A7001是TI公司生产的LDO,带底部散热焊盘,SOIC-8 PowerPAD封装,压差380mV。

Sipex 6201,固定电压输出,SOT-23封装,200mA ,320mV (200mA)压差。

转换过程如下,5V通过7A7001生成3.3V,3.3V分别通过7A7001和6201生成1.2V和2.5V,这样总共用3片LDO,有些时候,我也用2片7A7001共同生成3.3V。

前面两个方案layout尺寸都不大,但在功耗较大时,发热严重,而如果用开关电源,layout尺寸一般又都比较大,Altera推出了一系列小体积开关电源芯片,并且不需要使用电感,这种芯片在使用上类似LDO,并且纹波在5mV内,性能堪称一流。

Altera官方描述:1. 高功率密度,小封装尺寸2. 高效率和热性能3. 很少的器件数量以及很高的可靠性,280,000年MTBF4. 非常容易设计及市场化5. 技术支持保证100%的设计通过率(3) 方案3:使用两片EN5339(3A),分别生成3.3V和1.2V,使用1片EN5229(2A),生成2.5V。

这个方案我也是第一次用,板子还没投出去,心里也没不是很踏实,后期调试了再进行总结。

【精品博文】基于FPGA的原理图PCB设计

我的开发工具:Cadence 16.6,所用FPGA为Altera

家的。

画FPGA原理图需准备以下资料:(1) 原理图库文件(2) 芯片手册(3) Pin out file原理图库文件可以从官网上下载,比如我用cadence画Altera家EP4CE115F29I7N原理图,就直接下载EP4CE115.OLB文件。

https:///support/support-resources/downlo

ad/board-layout-test/pcb/pcb-cadence.html原理图中,这种大量管脚的芯片一般分为多个part,包括电源、地、各个bank、配置等。

芯片手册几乎给出了关于这个芯片设计(Cyclone IV Device Handbook)的所有需注意的问题,包括配置方式、全局时钟网络、专用时钟接口、lvds接口等。

pin out file中有每个管脚的详细说明。

(1)芯片配置配置方式主要有JTAG 或AS模式我只预留JTAG接口,有些板子上预留了两个下载接口,一个JTAG,用于下载程序,一个AS,用于固化程序,感觉这样很麻烦,我在固化时选择JIC(JTAG Indirect Configuration File)文件,尽管相对于AS模式会固化程序

会慢一点,但毕业还是JTAG方式,这样就省去了烦琐的

AS模式。

JTAG方式有用的信号其实就4个:TCK(测试时钟)、TDO(测试数据输出)、TMS(测试模式选择)、TDI (测试数据输入),再加上VCC和GND,共6根线,所以

其实可以把标准10pin下载口简化为6pin,标准10pin下载口体积大,而6pin连接器可以自己选择,这样更方便。

nConfig、nStatus、CONF_DONE、TMS、TDI需要上拉,TCK需要下拉。

配置芯片一般为EPCS系列,如EPCS64,EPCS128,相应地,可以用ST公司的M25P64和M25P128代替,连接方式如下图所示。

画完原理图,一定要检查下面16个管脚,连接是否正确,否则,板子很可能不工作(2)专用时钟专用时钟输入与输出的选择仍然需要参考,首先,专用时钟输入管脚都是可以驱动内部PLL的,可以配置为普通IO输入,但不能配置为输出管脚,之前有一次就因为没太注意,把这个管脚用作了输出,结果板子出了问题。

而专用时钟输出管脚,可以用于普通IO输出,也可以用于时钟输出。

设计时,最好是把专用时钟输入管脚全部用作时钟输入,把专用时钟输出管脚全部胜任专用时钟输出,毕竟,IO 资源一般不会这么紧张。

(3)lvds设计关于lvds设计,需要仔细看技术手册和Pin-Out Files for Altera Devices,下载地址:

https:///support/literature/lit-dp.html#Cyclo ne-IV对于c4,rx和tx复用,见Cyclone IV Device Handbook 第133页,从pin out file里也可以看出,P和N都是确定好了的,如DIFFIO_T35P和DIFFIO_T35N。

而对于c5器件,存在专用lvds通道,rx和tx是分开的,例

如DIFFIO_RX_B1P和DIFFIO_RX_B1N为一对。

关于lvds 部分的具体设计,在另一个专题lvds技术连载中会涉及到。

到这里,关于FPGA设计原理图部分基本上是说完了。