IC静电放电的测试方法

- 格式:docx

- 大小:13.84 KB

- 文档页数:4

芯片静电测试标准引言随着电子技术的快速发展,芯片已成为现代社会的关键组成部分。

然而,芯片在生产和使用过程中容易受到静电的损害。

为了确保芯片的质量和可靠性,制定芯片静电测试标准至关重要。

本文将对芯片静电测试标准进行全面、详细、完整和深入的探讨。

测试目的芯片静电测试的主要目的是评估芯片在静电环境下的性能和可靠性。

通过测试,可以检测芯片是否容易受到静电损害,以及是否满足相关的测试标准。

测试结果将用于指导芯片的设计、生产和使用,以降低芯片的静电敏感性,提高芯片的品质。

测试方法芯片静电测试一般包括以下几个方面的测试方法:1. 静电放电测试静电放电测试是评估芯片在静电放电事件下的性能的基本方法。

测试时,通过模拟静电放电事件,将芯片暴露在不同的放电电压和放电能量下,观察芯片的反应。

常用的测试方法包括人体模型(HBM)测试和机器模型(MM)测试。

1.1 人体模型(HBM)测试人体模型(HBM)测试是模拟人体静电放电对芯片的影响。

测试时,将芯片连接到接地板上,然后将预定的放电电压施加在芯片的引脚上,观察芯片的输出和/或损坏情况。

1.2 机器模型(MM)测试机器模型(MM)测试是模拟机器静电放电对芯片的影响。

测试时,将芯片连接到模拟电路上,通过一个预定的电容来模拟机器的静电放电,观察芯片的输出和/或损坏情况。

2. 静电放电保护测试静电放电保护测试是评估芯片的静电放电保护性能的方法。

通过测试,可以确定芯片是否具有有效的静电放电保护电路,以防止静电放电损伤芯片。

2.1 静电放电保护电路设计静电放电保护电路的设计是芯片静电测试中的关键环节。

设计时需要考虑芯片的特性和预期的静电放电情况,选择合适的保护元件和保护拓扑,以提高芯片的静电放电保护性能。

2.2 静电放电保护测试方法静电放电保护测试主要包括放电幅值测试和放电速率测试。

通过这些测试方法,可以验证芯片的静电放电保护电路的性能,以及是否满足相关的测试标准。

3. 静电敏感性测试静电敏感性测试是评估芯片在静电环境下的敏感性的方法。

IC-生产储存方法及防静电注意事项(一).IC (DIE)的储藏:IC 的储藏包括IC腐蚀防护及静电防护问题。

1. 储存环境温度应控制在5°C ~25°C及湿度在40%RH~60%RH间。

2. 储存时应避免储存环境温度变化过于激烈,湿度过高或过低,湿度过高和温差过大容易导致水蒸气凝结现象,湿度过低容易导致静电强度过高。

(相对湿度与静电强度关系以及各类芯片静电破坏电压见附表)3. 长时间储存时,最好储存在惰性气体(如N2)中。

4. 应避免储存时,在IC上有机械力的产生,而造成IC崩裂。

5. 应使用抗静电的材料来装存IC。

(二). IC(DIE)的取用方法:1.注意人员及环静境适当的接地,避免引起静电问题。

2.勿用手接触IC(die)以免造成污染、静电破坏、腐蚀或打线不易问题。

3.应使用真空吸笔拾取IC,而避免使用镊子夹子以防止机械应力造成IC的崩裂。

4.使用适当之真空吸笔头,并保持吸笔头的清洁。

(三).静电防护操作实例:1. 焊接作业:(1)焊锡炉:(a)外壳直接接地。

(b)锡液温度保持在245±5°C。

(c)COB不可过锡炉。

(2)铬铁:(a)使用三孔式插头,否则应自金属线部位接一耐热线直接接地。

(b)待焊品不可加电源。

(c)待焊品具有充电特性的部品(如电容器,PIEZO等)应先行放电。

2. 电源:(1)三孔式插座:接地线直接接地。

(2)两孔式插座:另接一直接接地之接地线。

3. 仪器设备:(1)使用电源的仪器采取机壳直接接地方式。

(2)未使用电源的仪器采取机壳间接接地方式(如机壳先经过1MΩ电阻在再接地)。

4. 工作区域:(1)使用导电性塑料及地垫。

(2)使用离子风扇(若限于工作环境可免用)。

5. 操作人员:(1)采取间接接地方式如配带静电手环。

6. 测试机台:(1)更换待测板时应先关机,同时电源电路应放电。

(2)测试机台上的充电组件放电。

7. 仪器修护:(1)修护人员应配带静电手表。

5种ESD防护方法静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前人设计了很多静电放电模型。

常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。

芯片级一般用HBM做测试,而电子产品则用IEC 6 100042的放电模型做测试。

为对 ESD 的测试进行统一规范,在工业标准方面,欧共体的 IEC 6100042 已建立起严格的瞬变冲击抑制标准;电子产品必须符合这一标准之后方能销往欧共体的各个成员国。

因此,大多数生产厂家都把 IEC 6100042看作是 ESD 测试的事实标准。

我国的国家标准(GB/T 17626.21998)等同于I EC 6 100042。

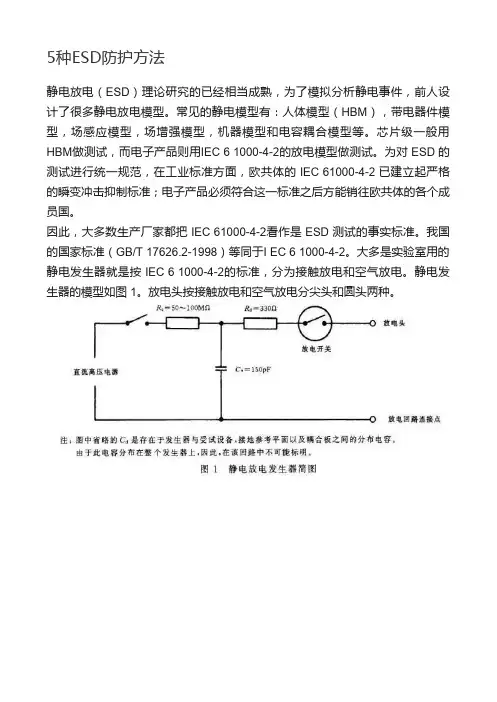

大多是实验室用的静电发生器就是按 IEC 6 100042的标准,分为接触放电和空气放电。

静电发生器的模型如图 1。

放电头按接触放电和空气放电分尖头和圆头两种。

IEC 6100042的 静电放电的波形如图2,可以看到静电放电主要电流是一个上升沿在1nS左右的一个上升沿,要消除这个上升沿要求ESD保护器件响应时间要小于这个时间。

静电放电的能量主要集中在几十MHz到500MHz,很多时候我们能从频谱上考虑,如滤波器滤除相应频带的能量来实现静电防护。

IEC 6100042规定了几个试验等级,目前手机CTA测试执行得是3级,即接触放电6KV,空气放电8KV。

很多手机厂家内部执行更高的静电防护等级。

当集成电路( IC )经受静电放电( ESD)时,放电回路的电阻通常都很小,无法限制放电电流。

例如将带静电的电缆插到电路接口上时,放电回路的电阻几乎为零,造成高达数十安培的瞬间放电尖峰电流,流入相应的 IC 管脚。

瞬间大电流会严重损伤 IC ,局部发热的热量甚至会融化硅片管芯。

HBM、MM&CDM静电放电模拟器静电放电模拟器目 录目 录 (1)1.概述 (2)2.基本设置 (2)2.1使用前的准备 (2)2.2放电重复时间(REPEAT TIME)设置 (3)2.3静电放电次数(ESD NUMBER)设置 32.4 测试电压的调节(ADJ) (4)3HBM试验 (4)3.1 HBM OUT与测试 (4)3.2 HBM试验电压等级 (6)3.3 HBM试验管脚组合 (8)3.4 HBM敏感度分类 (11)3.5HBM测试注意事项124. MM试验 (13)4.1 MM OUT的输出与选择 (13)4.1.1 OUT接线与MM选择 (13)4.1.2输出电压、正负极性的设置 (13)4.2 MM试验电压大小与极性 (13)4.3 MM试验管脚组合 (14)4.4.MM静电试验电压和极性的选择154.5选择静电放电重复频率 (15)4.6 MM的ESDS分类 (16)4.7 MM试验的特点与注意事项 (16)4.8. MM与HBM放电的比较(相同电压下,哪个损坏程度大? (16)5 CDM试验 (18)5.1 CDM充电的2种常用方法D-CDM与F-CDM (18)5.1.1 直接充电方法D-CDM (18)5.1.2 感应充电方法F-CDM (18)5.1.3 两种带电方法接线的比较 (19)5.2 CDM的设置与接线 (19)5.3 选择CDM静电试验电压和极性 (20)5.4 CDM试验电压等级 (20)5.5 CDM试验特点与注意事项 (20)5.6 CDM的放电 (21)5.7 CDM敏感度分类 (22)6 使用操作注意事项 (23)7 主要技术指标 (24)8 技术支持与售后服务 (24)9. 定期校准 (24)ESD-china的优势..............................................................................................................错误!未定义书签。

第一章 简介 (Introduction) 在互补式金氧半(CMOS)集成电路中,随着量产制程的演进,组件的尺寸已缩减到深次微米(deep-submicron)阶段,以增进集成电路(IC)的性能及运算速度,以及降低每颗芯片的制造成本。

但随着组件尺寸的缩减,却出现一些可靠度的问题。

在次微米技术中,为了克服所谓热载子(Hot-Carrier)问题而发展出LDD(Lightly-Doped Drain)制程与结构; 为了降低 CMOS组件汲极(drain)与源极(source)的寄生电阻(sheet resistance) Rs 与 Rd,而发展出Silicide制程; 为了降低 CMOS 组件闸级的寄生电阻 Rg,而发展出 Polycide 制程 ; 在更进步的制程中把Silicide 与 Polycide 一起制造,而发展出所谓 Salicide 制程。

在 1.0微米(含)以下的先进制程都使用上述几种重要的制程技术,以提升集成电路的运算速度及可靠度。

CMOS制程技术的演进如表1-1所示,其组件结构示意图如图1-1所示。

表1-1 CMOS 制程技术的演进Feature3 2 1 0.80.50.350.25Size(μm)Junction0.80.50.350.30.250.20.15Depth(μm)Gate-Oxide50040020015010070 50Thickness(A)LDD No No Yes Yes Yes Yes YesSalicide No No No No Yes Yes Yes(Silicide)图1-1但是,CMOS 组件因为上述先进的制程技术以及缩得更小的组件尺寸,使得次微米CMOS集成电路对静电放电 (Electrostatic Discharge ESD)的防护能力下降很多。

但外界 环境中所产生的静电并未减少,故CMOS集成电路因ESD而损伤的情形更形严重。

举例来说,当一常用的输出缓冲级(output buffer)组件的信道宽度(channel width)固定在300 微米(μm),用2微米传统技术制造的NMOS组件可耐压超过3千伏特(人体放电模式);用1微米制程加上LDD技术来制造的组件,其ESD耐压度不到2 千伏特;用 1 微米制程加上 LDD 及 Silicide 技术来制造的组件,其 ESD 耐压度仅约 1 千伏特左右而已。

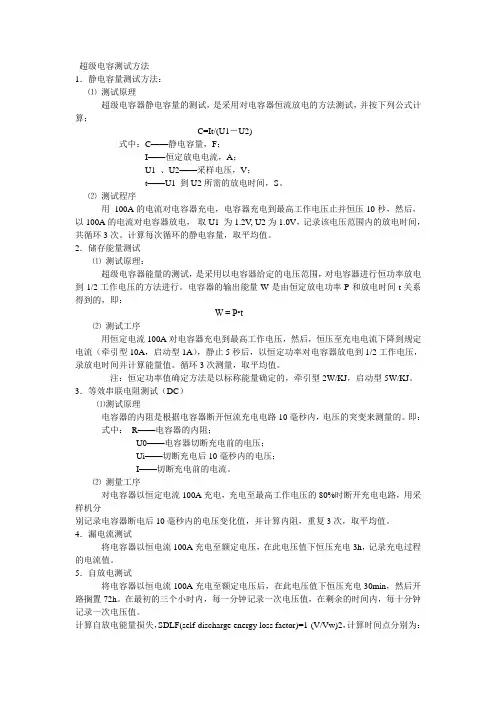

超级电容测试方法1.静电容量测试方法:⑴测试原理超级电容器静电容量的测试,是采用对电容器恒流放电的方法测试,并按下列公式计算;C=It/(U1-U2)式中:C——静电容量,F;I——恒定放电电流,A;U1 、U2——采样电压,V;t——U1 到U2所需的放电时间,S。

⑵测试程序用100A的电流对电容器充电,电容器充电到最高工作电压止并恒压10秒,然后,以100A的电流对电容器放电,取U1 为1.2V, U2为1.0V,记录该电压范围内的放电时间,共循环3次。

计算每次循环的静电容量,取平均值。

2.储存能量测试⑴测试原理:超级电容器能量的测试,是采用以电容器给定的电压范围,对电容器进行恒功率放电到1/2工作电压的方法进行。

电容器的输出能量W是由恒定放电功率P和放电时间t关系得到的,即:W = P•t⑵测试工序用恒定电流100A对电容器充电到最高工作电压,然后,恒压至充电电流下降到规定电流(牵引型10A,启动型1A),静止5秒后,以恒定功率对电容器放电到1/2工作电压,录放电时间并计算能量值。

循环3次测量,取平均值。

注:恒定功率值确定方法是以标称能量确定的,牵引型2W/KJ,启动型5W/KJ。

3.等效串联电阻测试(DC)⑴测试原理电容器的内阻是根据电容器断开恒流充电电路10毫秒内,电压的突变来测量的。

即:式中:R——电容器的内阻;U0——电容器切断充电前的电压;Ui——切断充电后10毫秒内的电压;I——切断充电前的电流。

⑵测量工序对电容器以恒定电流100A充电,充电至最高工作电压的80%时断开充电电路,用采样机分别记录电容器断电后10毫秒内的电压变化值,并计算内阻,重复3次,取平均值。

4.漏电流测试将电容器以恒电流100A充电至额定电压,在此电压值下恒压充电3h,记录充电过程的电流值。

5.自放电测试将电容器以恒电流100A充电至额定电压后,在此电压值下恒压充电30min,然后开路搁置72h。

在最初的三个小时内,每一分钟记录一次电压值,在剩余的时间内,每十分钟记录一次电压值。

IC卡封装中的ESD影响及对策1、引言ESD对整个半导体产业具有非常大的影响,每年半导体工业因为ESD造成的经济损失以数十亿美元计。

随着金卡工程和IC卡国产化在中国的逐步深入推广,ESD对IC卡模块封装这种集成电路封装形式的影响成为一个研究课题。

ESD的产生机理是什么?它对IC卡模块封装的影响体现在哪些方面?对这些影响应该采取什么措施去改善或消除?本文对上述问题进行了初步的探讨,并结合上海斯伦贝谢智能卡技术有限公司的实际例子提出了几点控制ESD影响的简单措施。

2、ESD及产生原因组成物质的原子包含电子和质子。

物质获得或者损失电子时,物质表现为带有正电或负电。

静电是正电荷或负电荷在物质表面积累的结果。

电荷积累通常由物质的接触、分离或者摩擦引起,通常称为摩擦生电。

影响电荷积累的因素很多,包括物体的接触程度、摩擦系数和分离速率等。

在影响因素消除之前,电荷会持续积累,随后释放,或者一直积累到周围物质的绝缘属性或绝缘保护失效为止。

一旦绝缘属性被改变,会迅速实现静电平衡。

ESD(Electrostatic Storage Deflection,静电积聚转移)是电荷的快速平衡,电荷的迅速平衡被称为静电放电。

研究表明,人走在地毯上由于摩擦产生的电荷,可引发高达20KV的静电压。

由于电荷是在阻力很小的情况下迅速释放的,因此释放时的等效电流可以超过20安培。

如果是通过集成电路或者其它对ESD敏感的元器件放电,那么大电流很可能会严重损坏原本只能传导微安级或毫安级电流的线路。

3、ESD对IC卡模块封装的影响ESD的影响存在于晶圆片生产、集成电路封装、器件测试、装配和使用的集成电路整个生命周期。

不管什么原因,只要在器件表面或周围区域积累电荷,就会产生ESD。

ESD每年造成的半导体工业经济损失高达数十亿美元。

集成电路器件对ESD非常敏感。

集成电路器件应该工作在一定的电压、电流和功耗限定范围内。

大量聚集的静电荷在条件适宜时就会产生高压放电(如空气湿度高于65%,或操作人员的接触等),静电放电通过器件引线的高压瞬时传送,可能会使氧化层(即绝缘体)断开,造成器件功能失常。

第一章簡介 (Introduction) 在互補式金氧半(CMOS)積體電路中,隨著量產製程的演進,元件的尺寸已縮減到深次微米(deep-submicron)階段,以增進積體電路(IC)的性能及運算速度,以及降低每顆晶片的製造成本。

但隨著元件尺寸的縮減,卻出現一些可靠度的問題。

在次微米技術中,為了克服所謂熱載子(Hot-Carrier)問題而發展出LDD(Lightly-Doped Drain)製程與結構; 為了降低CMOS元件汲極(drain)與源極(source)的寄生電阻(sheet resistance) Rs 與 Rd,而發展出Silicide製程; 為了降低 CMOS 元件閘級的寄生電阻 Rg,而發展出 Polycide 製程 ; 在更進步的製程中把Silicide 與 Polycide 一起製造,而發展出所謂Salicide 製程。

在 1.0微米(含)以下的先進製程都使用上述幾種重要的製程技術,以提昇積體電路的運算速度及可靠度。

CMOS製程技術的演進如表1-1所示,其元件結構示意圖如圖1-1所示。

(Silicide)圖1-1但是,CMOS 元件因為上述先進的製程技術以及縮得更小的元件尺寸,使得次微米CMOS積體電路對靜電放電(Electrostatic Discharge ESD)的防護能力下降很多。

但外界環境中所產生的靜電並未減少,故CMOS積體電路因ESD而損傷的情形更形嚴重。

舉例來說,當一常用的輸出緩衝級(output buffer)元件的通道寬度(channel width)固定在300 微米( m),用2微米傳統技術製造的NMOS元件可耐壓超過3千伏特(人體放電模式);用1微米製程加上LDD技術來製造的元件,其ESD耐壓度不到2 千伏特;用 1 微米製程加上 LDD 及 Silicide 技術來製造的元件,其 ESD 耐壓度僅約1 千伏特左右而已。

由此可知,就算元件的尺寸大小不變,因製程的先進,元件的 ESD 防護能力亦大幅地滑落;就算把元件的尺寸加大,其 ESD 耐壓度不見得成正比地被提昇,元件尺寸增大相對地所佔的佈局面積也被增大,整個晶片大小也會被增大,其對靜電放電的承受能力卻反而嚴重地下降,許多深次微米 CMOS 積體電路產品都面臨了這個棘手的問題。

IC静电放电的测试陆坚(中国电子科技集团公司第58研究所,江苏无锡214035)摘要:本文主要论述了静电放电(ESD)人体放电模式的测试过程,包括测试标准、IC管脚的测试组合、IC失效判别以及静电放电敏感度等级分类等。

关键词:ESD;HBM;静电放电故障临界电压中国分类号:TN407 文献标识码:A1 前言静电放电(ESD,electrostatic discharge)是电子工业最花代价的损坏原因之一,它会影响到生产合格率、制造成本、产品质量与可靠性以及公司的可获利润。

随着IC产品的制造工艺不断微小化,ESD引起的产品失效问题越来越突出。

为了能够了解我们所制造的IC产品的抵抗静电打击的能力,提升产品的质量,减少因ESD而引起的损伤,世界各地的IC工程师们研制出了许多静电放电模拟器,用来模拟现实生活中的静电放电现象,用模拟器对IC进行静电测试,借以找出IC的静电放电故障临界电压。

本文就是结合我们现在使用的静电放电模拟器(ZapMaster)详细介绍静电放电的测试过程。

2静电放电模式及国际标准目前在世界工业界对静电放电的模式大致定义了四种:人体模式HBM(humanbodymodel)、机器模式MM(machine model)、器件充电模式CDM(charge device model)、电场感应模式FIN(neldinducedmodel)。

因为在IC的制造和使用过程中,人体和IC接触的机会最多,由人体静电损伤造成IC失效的比例也最大,而且在实际应用中工业界也大多采用HBM模式来标注IC 的静电等级。

所以本文将着重介绍HBM的测试方法和判别标准。

人体模式(HBM),是指人体在地上走动、摩擦或者其他因素在人体上已积累了静电,当此人去直接接触IC时,人体上的静电便会经IC的管脚而进入IC内,再由IC放电到地去。

此放电过程会在短到几百个纳秒的时间内产生数安培的瞬间放电电流,这个电流会把IC内部的元件烧毁。

IC 静电放电的测试方法

1 前言

静电放电(ESD,electrostaTIc discharge)是电子工业最花代价的损坏原因之一,它会影响到生产合格率、制造成本、产品质量与可靠性以及公

司的可获利润。

随着IC 产品的制造工艺不断微小化,ESD 引起的产品失效

问题越来越突出。

为了能够了解我们所制造的IC 产品的抵抗静电打击的能

力,提升产品的质量,减少因ESD 而引起的损伤,世界各地的IC 工程师们

研制出了许多静电放电模拟器,用来模拟现实生活中的静电放电现象,用模

拟器对IC 进行静电测试,借以找出IC 的静电放电故障临界电压。

本文就是

结合我们现在使用的静电放电模拟器(ZapMaster)详细介绍静电放电的测试

过程。

2 静电放电模式及国际标准

目前在世界工业界对静电放电的模式大致定义了四种:人体模式

HBM(humanbodymodel)、机器模式MM(machine model)、器件充电模式CDM(charge device model)、电场感应模式FIN(neldinducedmodel)。

因为在IC 的制造和使用过程中,人体和IC 接触的机会最多,由人体静电损伤造。