第二讲:Lattice公司的isp1016芯片资料

- 格式:ppt

- 大小:155.50 KB

- 文档页数:13

采用ispLSI1016芯片设计数控系统的位置板大连理工大学林乐忠王永青胡力耘摘要采用新型的大规模可编程集成芯片)))ispL SI1016设计数控系统中的位置板,与采用其它IC芯片设计的位置板相比,可改善整个位置环的逻辑和电气特性,对于提高整个数控系统的加工精度和可靠性,具有实用价值。

关键词:ispLSI1016计数器位置反馈Design of Position Feedback C ard of NC System with the ispLSI1016DeviceLin Lezhong Wang Yongqing Hu LiyunAbstract T he autho r desig ns and develops the position feedback card w ith the new insystem pro-gr ammable large scale integ ration device)paring with using the other g ener al IC de-vices,this card can improv e the logic and electr ic character i stics o f the whole position loop of N C system.T his design has a practical meaning for raising the pr ecisio n,reliability of the N C sytem.Key Words:ispLSI1016;counter;position feedback1引言位置板是实现闭环数控系统的关键硬件,其特性好坏直接影响整个数控系统的性能。

大型精密数控机床的运动部件行程较长,必须用位数多的位置板构成位置环,以实现位置闭环控制,这要求设计多位计数器。

用标准的IC芯片或一般的可编程逻辑器件PLD(如PAL、GAL等)可以完成这一设计,但是由于此类芯片的功能与管脚有限,而设计要求的逻辑较复杂,以致设计所用的芯片个数会过多,电路板的尺寸过大,同时电路的时延问题严重,时序难以保证,从而使设计难度增大。

---------------------元器件的分类:semiconductor, electronic components, integrated circuits (IC), passive components, active components, connectors, resistors, capacitors, diodes, transistors, switches, sockets一般分主动和被动元器件。

主动类的主要是指集成电路,就是我们说的IC或芯片;被动类的指接插件、电阻、电容、二极管、三极管、开关、插座等。

我们的业务多集中在主动类(体积小、价值大),兼做被动类(体积大、价值一般小,但也有很贵的)。

-------------------元器件厂家:brand, manufacturer全球有5000家以上行业认可的元器件生产厂家,生产的元器件有百万种之多,而且不断的推陈出新,用新产品来替代老产品。

元器件行业是现代工业的基础。

所有的电子产品都需要元器件来做成成品。

好比是建筑业,建筑公司就是我们现在说的OEM (original equipment manufacturer)。

他们采购不同的建筑材料(对我们就是元器件)来做房子(对我们就是电子产品和设备)。

众多的厂家生产的产品,其实独一无二的很少(哪怕是Intel生产的CPU,其他也有生产的,比如AMD、TI和Cyrix),某一厂家生产的大多数产品都有其他的厂家能生产,只不过在具体的性能指标上有这样那样的不同,很多是可以互相替换的。

缩写:MOT: Motorola 摩托罗拉TI: Texas Instrument 德州仪器NS: National Semiconductor美国国家半导体公司Int: IntelAMD: Advanced Micro DevicesAD: Analog Devices美国模拟器件公司Ray: Raytheon美国雷神公司BB: Burr-BrownHar: Harris哈里斯公司Sie: Siemens西门子LT: Linear Tech 凌力尔特公司Level1: Level OneTosh: Toshiba东芝Sam: Samsung 三星CY: Cypress 美国CYPRESS半导体公司Fuji: Fujitsu日本富士通公司GS: General Semiconductor美国通用仪器公司半导体公司GI: General InstrumentHP: Hewlett-Packard 惠普Hit: Hitachi 日立Lat: Lattice莱迪斯半导体公司TI: Texas Instrument德州PH: PhilipsST: SGS-Thomson Microelectronics汤姆逊电子集团---------------------型号的含义:part#, part number, pin number所有元器件都通过型号来标识。

Lattice ispMACH TM 4000V/B/C/Z 设计指南及常见问题解答目录1介绍 (4)1.1特征 (4)1.2产品系列和器件选择手册 (4)1.3性能分析 (5)1.3.1超快性能 (5)1.3.2最低功耗 (6)2体系结构概述 (7)2.1ISP MACH4000体系结构 (7)2.2结构特征 (9)2.2.1逻辑分配器和3种速度路径 (9)2.2.2带可编程延时的输入寄存器 (10)2.2.3灵活的时钟和时钟使能 (10)2.2.4初始化控制 (11)2.2.5ORP BYPASS多路复用器 (11)2.2.6I/O 单元 (12)2.2.7OE 控制 (12)3设计实现 (13)3.1全局约束 (13)3.1.1Fitter 选项 (13)3.1.2利用率选项 (14)3.2约束编辑器 (15)3.2.1设备设置表 (15)3.2.2封装察看/引脚编辑规划 (15)3.2.3引脚/节点位置分配 (16)3.2.4组分配 (16)3.2.5I/O类型设置 (16)3.2.6资源预留 (17)3.2.7缺省设置 (17)3.3资源约束 (17)3.3.1使用源约束注意事项 (17)3.3.2源约束语法 (18)3.4优化设计方法 (21)3.4.1ispLEVEL 约束选项控制 (21)3.4.2HDL 源文件约束控制 (22)4器件应用要点 (22)4.14K系列器件VCC和VCCO的作用和连接 (22)4.24K系列器件各电源上电时间及要求 (22)4.34K系列器件的全局复位 (22)4.4关于4K系列器件时钟的用法 (22)4.5全局输出使能信号 (23)4.6CPLD的I/O口作为双向口使用时应注意的问题 (23)4.7关于设计中使用宽多路复用器的问题 (24)4.8未使用引脚的处理 (25)4.9I/O5V兼容问题 (25)4.10I/O口的电平设置 (25)4.114K系列器件引脚上、下拉电阻,OD,慢摆率特性的设定 (25)4.12关于引脚的缺省值和更改 (27)4.134K系列器件功耗的计算 (27)4.144K系列器件节点温度的计算 (27)4.154K器件的热插拔 (28)4.16ISP JTAG编程/测试信号 (28)4.17CPU加载的频率 (28)4.184K系列器件可承受的加载次数 (28)4.19加载过程中I/O口的状态 (28)4.20综合工具的选择 (29)4.21关于约束文件 (29)4.22用嵌入的M ODEL S IM 仿真 (29)4.23M ODEL S IM应用点滴 (30)4.244K器件上电电压阀值 (30)4.25ISP LEVER中的版本控制功能 (31)4.26ISP LEVER中C ONSTRAINT E DITOR的G LOBAL C ONSTRAINTS设置 (32)4.27ISP LEVER中的时序分析 (33)5ISPLEVER优化参数快速指南 (33)5.1ISP LEVER常用约束优化参数的含义与推荐设置 (33)5.2ISP LEVER推荐的优化参数设置 (35)6ISPLEVER安装说明 (36)6.1ISP LEVER安装说明 (36)6.2ISP VM S YSTEM安装说明 (37)7相关资料 (37)1介绍ispMACH4000 器件包括3.3V、2.5V和1.8V三个系列。

HW-USBN-2AispDOWNLOAD CablesUser’s GuideispDOWNLOAD CablesFeatures•Support for all Lattice programmable products–1.2V to 5V programming–Ideal for design prototyping and debugging•Connect to multiple PC interfaces–USB (v.1.0, v.2.0)–PC Parallel Port•Easy-to-use programming connectors•Versatile flywire, 2 x 5 (.100”) or 1 x 8 (.100”) connectors• 6 feet (2 meters) or more of programming cable length (PC to DUT)•Lead-free/RoHS compliant constructionFigure 1. USB Cable – HW-USBN-2A (Parallel Cable - HW-DLN-3C Not Shown)ispDOWNLOAD CablesLattice ispDOWNLOAD® Cable products are the hardware connection for in-system programming of all Lattice devices. After completion of the logic design and creation of a programming file with the Lattice Diamond®, isp-LEVER® Classic or PAC-Designer® software, the Lattice Diamond Programmer, or Lattice's ispVM™ System soft-ware is used to control the programming of devices directly on the PC board. No additional components are required to program a device.After you complete your logic design and create a programming file with the Lattice Diamond/ispLEVER develop-ment tools, you can use ispVM™ System software or Diamond Programmer to program devices on your board. The ispVM System/Diamond Programmer software automatically generates the appropriate programming com-mands, programming addresses and programming data based on information stored in the programming file and parameters you set in ispVM/Diamond Programmer. Programming signals are then generated from the USB or par-allel port of a PC and directed through the ispDOWNLOAD Cable to the device. No additional components are required for programming.ispVM System/Diamond Programmer software is included with all Lattice design tool products and is available for download from the Lattice web site at .ispDOWNLOAD CablesispDOWNLOAD Cable Pin DefinitionsThe functions provided by the ispDOWNLOAD cables correspond with available functions on Lattice programmable devices. Since some devices contain different programming features, the specific functions provided by the isp-DOWNLOAD cable may depend on the selected target device. ispVM System/Diamond Programmer software will automatically generate the appropriate functions based on the selected device. See Table 1 for an overview of the ispDOWNLOAD cable functions.Table 1. ispDOWNLOAD Cable Pin DefinitionsispDOWNLOAD Cable Pin NameispDOWNLOAD CablePin TypeDescriptionVCCProgramming VoltageInputConnect to V CC or V CCJ plane of the target device. T ypical I CC = 10mA. Y our board design supplies the power for V CC . Note: This may not be the same as a target device’s V CCO plane.SDO/TDO Test Data Output Input Used to shift data out via the IEEE1149.1 (JT AG) programming standard.SDI/TDI Test Data Input Output Used to shift data in via the IEEE1149.1 programming standard.ispEN/Enable/ PROG Enable Output Enable device to be programmed.TRST Test Reset Output Optional IEEE 1149.1 state machine reset. DONE DONEInput DONE indicates status of configuration MODE/TMS Test Mode Select Input Output Used to control the IEEE1149.1 state machine.GND GroundInput Connect to ground plane of the target device SCLK/TCK Test Clock Input Output Used to clock the IEEE1149.1 state machineINITInitializeInputIndicates that ORCA ® device is ready for configuration.Figure 2. ispDOWNLOAD Cable In-System Programming Interface for the PC (HW-USB-1A or HW-USB-2A)11. Lattice PAC-Designer ® software does not support programming with USB cables. T o program ispPAC devices with these cables, use the ispVM System software/Diamond Programmer.Figure 3. ispDOWNLOAD Cable In-System Programming Interface for the PC (HW-DLN-3C and Equivalents)11.HW7265-DL3, HW7265-DL3A, HW-DL-3B, HW-DL-3C and HW-DLN-3C are functionally equivalent products.ispDOWNLOAD Cables Figure 3. ispDOWNLOAD Cable In-System Programming Interface for the PC (pDS4102-DL2 or pDS4102-DL2A)Figure 4. Figure 4. ispDOWNLOAD Cable In-System Programming Interface for the PC (HW7265-DL2 or HW7265-DL2A)1.For reference purposes, the 2x10 connector on the HW7265-DL2 or HW7265-DL2A is equivalent to Tyco 102387-1. This will interface tostandard 100-mil spacing 2x5 headers, or a 2x5 keyed, recessed male connector such as the 3M N2510-5002RB. Programming SoftwareispVM System/Diamond Programmer is the preferred programming management software tool for all Lattice devices and download cables. The latest version of ispVM System software or the Lattice Diamond Program-mer is available for download from the Lattice web site at /software.Target Board Design ConsiderationsA 4.7K pull-down resistor is recommended on the TCK connection of the target board. This pull-down is recom-mended to avoid inadvertent clocking of the TAP controller induced by fast clock edges or as V CC ramps up. This pull-down is recommended for all Lattice programmable families.For Lattice device families that feature low power, it is recommended to add a 500 ohm resistor between V CCJ and GND during the programming interval when a USB ispDOWNLOAD cable is connected to a very low power board design. A FAQ is available that discusses this in more depth at:/support/faqs/details.cfm?id=2205The JTAG programming port speed may need to be governed when using the ispDOWNLOAD cables connected to customer PCBs. This is especially important when there is long PCB routing or with many daisy-chained devices. The Lattice programming software can adjust the timing of TCK applied to the JTAG programming port from the cable. This low-precision port setting of TCK depends on many factors, including the PC speed and the type of cable used (parallel port, USB or USB2). This software feature provides an option to slow the TCK for debug or noisy environments. A FAQ is available that discusses this in more depth at:/support/faqs/details.cfm?id=974The USB Download Cable can be used to program Power Manager or ispClock products with Lattice programming software. When using the USB cable with the Power Manager I devices, (POWR604, POWR1208, POWR1208P1), you must slow do TCK by a factor of 2. A FAQ is available that discusses this in more depth at:/support/faqs/details.cfm?id=306ispDOWNLOAD CablesProgramming Flywire and Connection ReferenceRefer to T able 2 when connecting a flywire download cable to systems that use the 1x8-position or 2x5-position connectors. For newer Lattice FPGA families, a 1x10 connector used in conjunction with the ispDOWNLOAD USB cable adds support for the DONE and INITN signals. Both of these signals are inputs to the cable, and can be used to help verify device configuration.Table 2. Flywire Conversion ReferenceFunction FlywireCableWireLabel1x10Connector1x8Connector2x5ConnectorV CC1Red VCC116TDO/SO/SPI_SO Brown TDO227TDI/SI/SPI_SI Orange TDI335ispEN2/Enable/PROGRAMN/SN/SPI_SS_B Y ellow ispEN/PROG4410TRST3/CRESET_B Green TRST/DONE559TMS/MODE Purple TMS663GND Black GND77 4 (2 and 8) TCK4/SCLK/CCLK/SPI_SCK White TCK881DONE3Green TRST/DONE9INITN/CDONE Blue INITN101. For devices that have a V CCJ pin, the V CCJ must be connected to the cable’s V CC, and a 0.1µF decoupling capacitor is required on V CCJclose to the device. Please refer to the device data sheet to determine if the device has a V CCJ pin.2. For older Lattice ISP devices, a 0.01µF decoupling capacitor is required on ispEN/ENABLE of the target board.3. The TRST and DONE pin is multiplexed on the ispDOWNLOAD USB cable. If the device TRST signal is available on the board, connect theUSB flywire TRST/DONE wire to TRST. If the device DONE signal is available on the board (or if both TRST and DONE are available), con-nect the USB flywire TRST/DONE wire to DONE. Please make sure the correct setting is selected in ispVM/Diamond Programmer (Options, Cable and I/O Port Setup). This will tell ispVM/Diamond Programmer whether the TRST/DONE cable is used as a TRST or a DONE signal.4. A 4.7K pull-down resister is recommended on TCK of the target board.Table 3 lists the recommend pin connections. Please contact Lattice technical support for information on unlisted devicefamilies.(e-mail:***************************,phone:1-800-LATTICE).Table 3. Recommended Pin ConnectionsDevice Family TDI TDO TMS TCK ispEN/PROG1,6TRST2/DONE3,6INITN3,6VCC GND LatticeECP3™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory LatticeECP2M™/LatticeECP2™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory LatticeECP™/LatticeEC™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory LatticeXP2™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory LatticeXP™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory LatticeSC™/LatticeSCM™Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory iCE40™Mandatory Mandatory N/A Mandatory Mandatory Recommended Recommended Mandatory Mandatory MachXO2™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory MachXO™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory ORCA®/FPSC Mandatory Mandatory Mandatory Mandatory Optional Optional Optional Mandatory Mandatory ispXPGA®Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory ispXPLD™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory ispMACH® 4000Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory ispMACH/ispLSI® 5000Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory MACH®4A4Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory ispGDX2™Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory ispClock™Mandatory Mandatory Mandatory Mandatory N/A N/A5N/A Mandatory Mandatory Platform Manager™Mandatory Mandatory Mandatory Mandatory N/A Optional5N/A Mandatory Mandatory Power Manager/Power Manager II Mandatory Mandatory Mandatory Mandatory N/A Optional5N/A Mandatory MandatoryispDOWNLOAD CablesTable 3. Recommended Pin Connections (Continued)Device Family TDI TDO TMS TCK ispEN/PROG1,6TRST2/DONE3,6INITN3,6VCC GND ispPAC®Mandatory Mandatory Mandatory Mandatory N/A N/A N/A Mandatory Mandatory1. Refer to the ispDOWNLOAD Cable ispEN Pin section below for detailed information on connecting the ispEN/ENABLE pin.2. Refer to the ispDOWNLOAD Cable TRST Pin section below for detailed information on connecting the TRST pin.3. The DONE and INITN signals are only available on the ispDOWNLOAD USB cable. These signals are inputs to the cable and can be used to help verify deviceconfiguration.4. Please refer to the device data sheet. Not all packages have the ENABLE or TRST pin.5.When using P AC-Designer® software to program ispPAC devices, do not connect this pin.6.When using these connections, be sure to select the correct settings in the Cable and I/O Port Setup dialog in the ispVM System/Diamond Programmer soft-ware.Connecting the ispDOWNLOAD CableThe target board must be un-powered when connecting, disconnecting, or reconnecting the ispDOWNLOAD Cable. Always connect the ispDOWNLOAD Cable’s GND pin (black wire), before connecting any other JTAG pins. Failure to follow these procedures can result in damage to the target programmable device. ispDOWNLOAD Cable TRST PinConnecting the board TRST pin to the cable TRST pin is not recommended. Instead, connect the board TRST pin to Vcc. If the board TRST pin is connected to the cable TRST pin, instruct ispVM/Diamond Programmer to drive the TRST pin high as follows:1.Select the Options menu item.2.Select Cable and I/O Port Setup.3.Check the TRST/Reset Pin Connected checkbox.4.Select the Set High radio button.If the proper option is not selected, the TRST pin will be driven low by ispVM/Diamond Programmer. Consequently, the BSCAN chain will not work because the chain will be locked into RESET state.ispDOWNLOAD Cable ispEN PinThe following pins should be grounded:•BSCAN pin of the 2000VE devices•ENABLE pin of MACH4A3/5-128/64, MACH4A3/5-64/64 and MACH4A3/5-256/128 devices.However, the user has the option of having the BSCAN and ENABLE pins driven by the ispEN pin from the cable. In this case, ispVM/Diamond Programmer must be configured to drive the ispEN pin low as follows:1.Select the Options menu item.2.Select Cable and I/O Port Setup.3.Check the ispEN/BSCAN Pin Connected checkbox.4.Select the Set Low radio button.Feature HW-USBN-2A HW-USB-2A HW-USB-1A HW-DLN-3C HW7265-DL3, HW7265-DL3A,HW-DL-3B,HW-DL-3C HW7265-DL2HW7265-DL2A PDS4102-DL2PDS4102-DL2AUSB X X XPC-Parallel XXXXXX1.2V Support X X 1.8V Support X X X X X X X2.5-5.0V Support X X X X X X X XX2x5 Connector X X X X X XX1x8 Connector X X X X X XXFlywire X XXX XLead-free Construction X X Available for orderXXispDOWNLOAD CablesTable 4. ispDOWNLOAD Cable Feature SummaryEach ispDOWNLOAD Cable ships with two small connectors that help you keep the flywires organized. The follow-ing manufacturer and part number is one possible source for equivalent connectors:•1x8 Connector (e.g. Samtec SSQ-108-02-T -S)•2x5 Connector (e.g. Samtec SSQ-105-02-T -D)The ispDOWNLOAD Cable flywire or headers are intended to connect to standard 100-mil spacing headers (pins spaced 0.100 inch apart). Lattice recommends a header with length of 0.243 inches or 6.17 mm. Though, headers of other lengths may work equally well.Ordering InformationDescriptionOrdering Part Number China RoHS Environment-Friendly Use Period (EFUP)ispDOWNLOAD cable (USB). Contains 6' USB cable, flywire connectors, 8-position (1x8) adapter and 10-position (2x5) adapter, lead-free, RoHS compliant construction.HW-USBN-2AispDOWNLOAD cable (PC only). Contains parallel port adapter, 6' cable, flywire connectors, 8-position (1x8) adapter and 10-position (2x5) adapter, lead-free, RoHS compliant construction.HW-DLN-3CNote: Additional cables are described in this document for legacy purposes only, these cables are no longer produced. The cables currently available for order are fully equivalent replacement items.Technical Support AssistanceHotline:1-800-LATTICE (North America)+1-503-268-8001 (Outside North America)e-mail:***************************Internet:ispDOWNLOAD CablesRevision HistoryDate Version Change Summary——Previous Lattice releases.July 200924.1Added Target Board Design Considerations text section.Added Programming Flywire and Connection Reference section head-ing.October 200924.2Added information related to the physical specifications of the flywireconnectors.November 201124.3Document transferred to user’s guide format.Added Figure USB Cable – HW-USBN-2A.Updated Recommend Cable Connections table for MachXO2 devices.Updated Target Board Design Considerations section.Added Appendix A.February 201224.4Updated document with new corporate logo.October 201224.5Added iCE40 configuration port pin names to the Flywire ConversionReference table.Added iCE40 information to Recommended Cable Connections table.ispDOWNLOAD CablesAppendix A. Troubleshooting the USB Driver InstallationIt is essential that you install the drivers before connecting your PC to the USB cable. If the cable is connected before installing the drivers, Windows will try to install its own drivers that may not work.If you have attempted to connect the PC to the USB cable without first installing the appropriate drivers, or have trouble communicating with the Lattice USB cable after installing the drivers, following the steps below:1.Plug in the Lattice USB cable. Choose Start > Settings > Control Panel > System. In the System Propertiesdialog box, click the Hardware tab and Device Manager button. Under Universal Serial Bus controllers, you should see Lattice USB ISP Programmer. If you do not see this, look for the Unknown Device with the yellow flag.2.Double click on the Unknown Device icon.3.Click Reinstall Driver.4.Select Browse for driver software on your computer.For Lattice EzUSB DriverFor FTDI FTUSB Driver5.Browse to the isptools\ispvmsystem directory for the Lattice EzUSB driver or the isptools\ispvmsystem\Drivers\FTDIUSBDriver directory for the FTDI FTUSB driver. For Diamond installations, browse tolscc/diamond/data/vmdata/drivers. Click Next.6.Select Install this Driver software anyway. The system will update the driver.7.Click Close and finish installing the USB driver. Under Control Panel >System >Device Manager > Univer-sal Serial Bus Controllers should include the following:For the Lattice EzUSB Driver: Lattice USB ISP Programmer device installed.For the FTDI FTUSB Driver: USB Serial Converter A and Converter B devices installed.If you are experiencing problems or need additional information, contact Lattice Technical Support.HW-USBN-2A。

ATmega16单片机中文技术资料一、概述ATmega16是一款高性能、低功耗的8位微控制器,由Atmel公司推出。

它基于AVR增强型RISC结构,拥有丰富的外设资源和灵活的编程特性,广泛应用于工业控制、消费电子、通信设备等领域。

二、主要特性1. 内核:AVR增强型RISC结构,最高工作频率为16MHz。

2. 存储:16KB的程序存储器(Flash)、512B的EEPROM和1KB 的SRAM。

3. 外设接口:32个通用I/O口、8个通道的10位ADC、2个8位定时器/计数器、1个16位定时器/计数器、1个串行通信接口(USART)、1个串行外设接口(SPI)和1个两线接口(TWI)。

4. 工作电压:2.7V至5.5V,支持低功耗模式。

5. 封装:采用TQFP和PDIP封装,便于嵌入式系统设计。

三、引脚功能1. VCC:电源正极,接2.7V至5.5V电压。

2. GND:电源负极,接地。

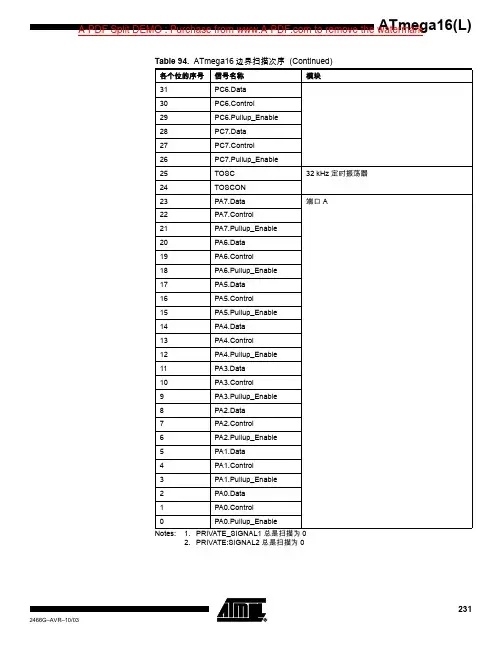

3. PA0PA7:端口A,具有通用I/O、模拟输入和外围设备功能。

4. PB0PB7:端口B,具有通用I/O、JTAG接口和外围设备功能。

5. PC0PC7:端口C,具有通用I/O、模拟输入和外围设备功能。

6. PD0PD7:端口D,具有通用I/O和外围设备功能。

7. XTAL1/XTAL2:晶振输入/输出,用于外部晶振或陶瓷谐振器。

8. AVCC:模拟电源,为ADC和模拟电路提供电源。

10.RESET:复位输入,低电平有效。

四、编程与开发1. 编程语言:支持C语言和汇编语言编程。

2. 开发工具:可使用Atmel Studio、AVR Studio等集成开发环境进行程序编写、编译和调试。

3. 烧录方式:通过ISP、JTAG、HVPP等接口进行程序烧录。

本文档旨在为您提供ATmega16单片机的中文技术资料,帮助您更好地了解这款微控制器,为您的项目开发提供支持。

后续内容将详细介绍ATmega16的外设功能、编程方法及应用实例。

Lattice 产品一、公司简介Lattice半导体公司(Lattice Semiconductor)成立于1983年,专业从事设计、开发和销售高性能的可编程逻辑器件和相关软件。

Lattice是ISP(In System Programmable)技术的发明者,ISP技术极大的促进了PLD产品的发展。

1999年收购V antis(原AMD子公司),2001年收购Lucent微电子的FPGA部门,是世界第三大可编程逻辑器件供应商。

目前Lattice公司在上海设有研发部门。

二、Lattice的ISP技术Lattice公司于1991 年革命性地率先推出高密度在系统可编程(In System Programmable)逻辑器件,从而开创了可编程逻辑器件的市场。

通过使用ISP器件,工程师们可以在电路板上直接对可编程器件进行编程或再编程,有效缩短产品上市周期、降低生产成本。

Lattice开发的ISP 技术使用户在产品的整个寿命周期中获得无形的利益。

从设计、制造到现场升级、维护,采用Lattice ISP 产品可以加速产品的上市并降低研发成本。

Lattice ISP 技术帮助工程师缩短系统试制时间、简化生产流程并采用经证实更有效的方式进行现场升级和维护。

三、Lattice的产品线Lattice目前主要有6个产品系列:●CPLDComplex Programmable Logic Device●ispXPLDeXpanded Programmable Logic Devices●ispXPGA●ORCA FPSC●IspPAC●ispGDX2Lattice 的所有产品都具备isp功能,即所有芯片均可满足在线配置或重配置。

四、CPLD——Complex Programmable Logic Device1、CPLD的性能Lattice的CPLD颇有特色,在业界具有很强的竞争力,包括早期的ispLSI系列产品和MACH系列、ispMACH4000系列、ispLSI5000系列、和ispMACH5000系列产品。

LCMXO2-1200ZE-P1-EVNPRODUCT SELECTOR GUIDE2012FPGA • CPLD • MIXED SIGNAL • INTELLECTUAL PROPERTY • DEVELOPMENT KITS • DESIGN TOOLSCONTENTS■A dvanced Packaging (4)■F PGA Products (6)■C PLD Products (8)■M ixed Signal Products (8)■Intellectual Property and Reference Designs (10)■D evelopment Kits and Evaluation Boards (14)■P rogramming Hardware (18)■FPGA and CPLD Design Software (19)■P AC-Designer® Design Software (19)Page 2Affordable InnovationLattice Semiconductor is committed to delivering value through innovative low cost, low powersolutions. We’re innovating every day to drive down costs and deliver greater value. Fromcost sensitive consumer electronics to leading edge communications equipment, designersare using Lattice products in a growing number of applications. We’ve shipped over a billiondevices to customers worldwide and we understand that we must deliver cost effectivesolutions and excellent service in order to succeed.FPGA, PLD and Mixed Signal ProductsLattice FPGA (Field Programmable Gate Array) solutions offer unique features, low power,and excellent value for FPGA designs. We are also the leading supplier of low-density CMOSPLDs, and our CPLD and SPLD solutions deliver an optimal fit for a variety of PLD designchallenges.Our Platform Manager™, Power Manager II and ispClock™ mixed signal product familiesfeature a combination of programmable logic and programmable analog circuitry that allowssystem designers to reduce system cost and design time. These innovative products provide afast and easy solution for integrating a wide range of power and clock management functionswithin a single integrated circuit. These products can replace numerous discrete components,reducing cost and conserving board space, while providing users with additional designflexibility and time-to-market benefits.Software and Intellectual PropertyOur Lattice Diamond® development tool suite, iCEcube2™ design software, PAC-Designersoftware, and IP core program allow design engineers to easily customize our devices for theirunique system requirements.Lattice Diamond software tools enable users to synthesize a design, perform analysis, debug,and download a logic configuration to our FPGA devices, while iCEcube2 software supportsour iCE40 family of FGPAs. PAC-Designer software is used in the design of our mixed signalproducts.Our IP core program, LatticeCORE™, provides pre-tested, reusable functions, allowingdesigners to focus on their unique system architectures. These IP cores provide industry-standard functions including PCI Express, DDR, Ethernet, CPRI, Serial RapidIO 2.1, SPI4,and embedded microprocessors. In addition, a number of independent IP providers haveteamed with Lattice to offer additional high quality, reusable IP cores. Partners are selected fortheir industry leadership, high development standards, and commitment to customer support.Page 3Page 4Organic Flip Chip BGAFine Pitch BGA1704-BallOrganic fcBGA 42.5 x 42.5 mm 3.25 mm height 1.00 mm pitch1152-BallOrganic fcBGA 35 x 35 mm 3.50 mm height 1.00 mm pitch1020-BallOrganic fcBGA Revision 233 x 33 mm 3.25 mm height 1.00 mm pitch1152-Ball fpBGA 1156-Ball fpBGA 35 x 35 mm 2.60 mm height 1.00 mm pitc h868-Ball fpBGA 900-Ball fpBGA 31 x 31 mm 2.60 mm height 1.00 mm pitch648-Ball fpBGA 672-Ball fpBGA 27 x 27 mm 2.60 mm height 1.00 mm pitch484-Ball fpBGA 23 x 23 mm 2.60 mm height 1.00 mm pitch324-Ball ftBGA 19 x 19 mm 1.70 mm height 1.00 mm pitch256-Ball ftBGA 17 x 17 mmOption 1: 1.55 mm height Option 2: 2.10 mm height Option 3: 1.70 mm height 1.00 mm pitch 256-Ball caBGA 14 x 14 mm 1.70 mm height 0.80 mm pitch332-Ball caBGA 17 x 17 mm 2.00 mm height 0.80 mm pitch208-Ball ftBGA 17 x 17 mm 1.55 mm height 1.00 mm pitch256-Ball fpBGA 17 x 17 mm 2.10 mm height1.00 mm pitchFine Pitch BGAChip Array BGANote: Packages shown actual size. Height specification is max.Page 5208-Pin PQFP 28 x 28 mm (body)4.10 mm height 0.50 mm pitch176-Pin TQFP 24 x 24 mm (body)1.60 mm height 0.50 mm pitch144-Pin TQFP 20 x 20 mm (body)1.60 mm height 0.50 mm pitch100-Pin TQFP 128-Pin TQFP 14 x 14 mm (body)1.6 mm height0.50 mm pitch (100 TQFP)0.40 mm pitch (128 TQFP )44-Pin TQFP10 x 10 mm (body)1.20 mm height 1.60 mm height 0.80 mm pitch 48-Pin TQFP 7 x 7 mm (body)1.20 mm height 1.60 mm height0.50 mm pitchTQFP/PQFP64-Pin QFNS 9 x 9 mm1.00 mm height 0.50 mm pitch 100-Ball csBGA 132-Ball csBG A 8 x 8 mm1.35 mm height 0.50 mm pitch 284-Ball csBGA 12 x 12 mm 1.00 mm height 0.50 mm pitch 328-Ball csBGA 10 x 10 mm 1.50 mm height 0.50 mm pitch 132-Ball ucBGA 6 x 6 mm1.00 mm height 0.40 mm pitch 25-Ball WLCSP2.5 x 2.5 mm 0.62 mm height 0.40 mm pitch84-Pin QFNS 7 x 7 mm1.00 mm height 0.50 mm pitch 48-Pin QFNS 7 x 7 mm1.00 mm height 0.50 mm pitch144-Ball csBGA 7 x 7 mm1.10 mm height 0.50 mm pitch64-Ball ucBGA 4 x 4 mm1.00 mm height 0.40 mm pitch 32-Pin QFNS 5 x 5 mm1.00 mm height 0.50 mm pitch 32-Pin QFN 5 x 5 mm0.60 mm height 0.50 mm pitch 56-Ball csBGA 6 x 6 mm1.35 mm height 0.50 mm pitch 81-Ball csBGA 5 x 5 mm1.00 mm height 0.50 mm pitch 225-Ball ucBGA 7 x 7 mm1.00 mm height 0.40 mm pitch 24-Pin QFNS 4 x 4 mm1.00 mm height 0.50 mm pitch64-Ball csBGA 5 x 5 mm1.10 mm height 0.50 mm pitch121-Ball csBGA 6 x 6 mm1.00 mm height 0.50 mm pitch 121-Ball ucBGA 5 x 5 mm1.00 mm height 0.40 mm pitch 81-Ball ucBGA 4 x 4 mm1.00 mm height 0.40 mm pitch 49-Ball ucBGA 3 x 3 mm1.00 mm height 0.40 mm pitch 36-Ball ucBGA2.5 x 2.5 mm 1.00 mm height0.40 mm pitchQFNS / QFNChip Scale BGAUltra Chip Scale BGAWafer Level Chip ScaleNote: Packages shown actual size. Height specification is max.NEWiCE40™Page 6Page 71) Pb-free only.ispClock ProductsPage 8Platform Manager and Power Manager II Device Selector Guide* ispPAC-POWR1014A OnlyPage 9LatticeCORE IP CoresFor a complete listing of IP cores from Lattice and its 3rd party partners, please go to /ip.1. LatticeSCM™ MACO®-based IP cores are not included in this table.Page 10IP SuitesLattice IP Suites provide many of the functions required to develop a total solution for common FPGA applications. In addition, multipleLattice FPGA families are supported with each IP Suite, so designers can develop solutions across multiple Lattice families, taking advantage of the best features of each. The following table summarizes which IP cores are included in each IP Suite, and which FPGA families are supported.Page 11Page 12Page 14Features- Power connections and power sources - ispVM™ programming support- On-board and external reference clock sources• Available on Windows and Linux platforms • Software and IP with a 60-day license (Windows or Linux)• Variety of demos • USB download cable• Comprehensive Image Processing IP Library • On-board Broadcom ® Broadreach™ PHY Enables IP over Coax• On-board FTDI Chip provides easy programming via low cost USB cable- Gigabit Ethernet MAC Demo using Mico32- DDR3 Memory Controller Demo• Available on Windows and Linux platforms • USB A to USB B (Mini) Cable for FPGA Programming via a PC• 12V AC Power Adapter and International Plug Adapters•QuickSTART GuideFeaturesFeaturesFeaturesLatticeECP3 Versa Development KitHDR-60 Video Camera Development KitLatticeECP3 PCI Express Development KitLatticeXP2 Brevia2 Development Kit• LatticeECP3 PCI Express x1/x4 Solutions Board- PCI Express x1 and x4 edge connector interfaces- On-board Boot Flash- Both Serial SPI Flash and Parallel Flash via MachXO programming bridge - Shows interoperation with a highperformance DDR2 memory component - Switches, LEDs, displays for demo purposes- Input connection for lab-power supply• FPGA-based Image Signal Processing• Fully Production-Ready HDR Camera Design • 1080p Capable @ 60 frames per second• Supports up to 16 Megapixel Sensors • Supports up to two sensors simultaneously • Full 60fps in streaming mode needs no external frame buffer• Fast Auto Exposure Instantly Adjust to Changing Light• Greater than 120 dB High Dynamic Range (HDR) Performance• Direct HDMI/DVI output from FPGA • Extremely Low-Latency• The LatticeECP3 Versa Evaluation Board:- PCI Express 1.1 x1 Edge Connector Interface- Two Gigabit Ethernet Ports (RJ45)- 4 SMA Connectors for SERDES Access - USB Mini for FPGA Programming- LatticeECP3 FPGA: LFE3-35EA-FF484- 64 Mbit Serial Flash memory - 1 Gbit DDR3 Memory- 14-segment alpha-numeric display - Switches and LEDs for demos - SERDES Eye Quality Demo - 4 PCI Express Demos• LatticeXP2 FPGA: LFXP2-5E-6TN144C • 2 Mbit SPI Flash Memory • 1 Mbit SRAM• Programmed via included mini-USB Cable • 2x20 and 2x5 Expansion Headers• Push buttons for General Purpose I/O and Reset• 4-bit DIP Switch for user-defined inputs • 8 Status LEDs for user-defined outputsDevelop PCIe-based platforms using a low-cost, low-power SERDES-basedFPGA with proprietary and Lattice provided designs.A fully production ready High Dynamic Range (HDR) camera, designed to fit into commercially available camera housings. Supports full 1080p resolution at 60 frames per second in streaming mode through the FPGA, without the need for an external frame buffer.Industry’s lowest cost platform for design-ing PCI Express and Gigabit Ethernet based systems. The kit includes free demos and reference designs.Easy-to-use, low-cost platform for evaluat-ing and designing with LatticeXP2 FPGAs.2011. Standard list price: $299.Page 15FeaturesFeaturesFeaturesispMACH 4000ZE Pico Development KitiCEblink40 Evaluation KitMachXO2 Pico Development KitMachXO2 Control Development Kit• Pre-programmed Pico Power Demo • ispMACH 4000ZE device (LC4256ZE-5MN144C)• Power Manager II device(ispPAC-POWR6AT6-01SN32I)• LCD panel• USB mini jack socket for power, JTAG programming, and I 2C interface• 2X15 header landing for off-board expansion provides access to LC4256ZE GPIOs, POWR6AT6 VMON inputs, I 2C, and JTAG chain• Push-button for global reset• 4-bit DIP switch to user-defined inputs • 3.3V and 2.5V supply rails• Two versions:- High Performance: iCE40HX1K-VQ100 - Low Power: iCE40LP1K-QN84• Powered by USB input• 1Mbit SPI PROM (enough for two iCE40HX1K images using WarmBoot)• Four capacitive-touch buttons (requires FPGA logic)• Four user LEDs• MachXO2 LCMXO2-1200ZE• 4-character 16-segment LCD display • 4 capacitive touch sense buttons • 1 Mbit SPI Flash• I 2C temperature sensor• Current and voltage sensor circuits • Expansion header for JTAG, I 2C• Standard USB cable for device programming and I 2C communication• RS-232/USB & JTAG/USB interface • RoHS-compliant packaging and process• MachXO2 LCMXO2-1200HC• Power Manager II ispPAC-POWR1014A • 128Mbit LPDDR memory, 4Mbit SPI Flash • Current and voltage sensor circuits • SD memory card socket • Microphone• Audio Amplifier and Delta-Sigma ADC• Up to two DVI sources and one DVI output.• Up to two Display Inputs (7:1 LVDS) and one Display Output (7:1 LVDS)• Audio output channel• Expansion header for JTAG, SPI, I 2C and PLD I/Os.• Current and voltage sensor circuits • Battery or USB power source• RoHS-compliant packaging and process • Marked for CE, China RoHS Environmental-Friendly Use Period (EFUP) and WasteElectrical and Electronic Equipment (WEEE) Directives• One USB connector cable • QuickSTART Guide• Dual PMOD header compatible with Digilent PMOD boards (6x2 header)• 3.33 MHz oscillator (can be modified to support 33.33 MHz or 333 kHz)• 1.2V and 3.3V power supplies• All iCE40HX1K I/O available on headers or 0.1” through-holes• Watch battery• QuickSTART Guide• LEDs & switches• Standard USB cable for device programming • RS-232/USB & JTAG/USB interface• RoHS-compliant packaging and process • AC adapter (international plugs)• QuickSTART GuideBattery-powered, low-cost platform to accelerate the evaluation of ispMACH 4000ZE CPLDs.Page 16FeaturesFeaturesMachXO Control Development Kit FeaturesFeaturesMachXO Pico Dev. Kit & MachXO Control Dev. KitPower Manager II Hercules Development KitProcessorPM Development KitPlatform Manager Development Kit• Preloaded Control SoC Demo• MachXO LCMXO2280• Power Manager II ispPAC-POWR1014A• 2Mbit SPI Flash & 1Mbit SRAM• I2C temperature sensor• Current and voltage sensor circuits• On-board fan• Interface to 16 x 2 LCD panel*• SD memory and CompactFlash memory card sockets*• Audio output channel• Expansion header for SPI & I2C• LEDs & switches• Standard USB cable for deviceprogramming and I2C communication• RS-232/USB & JTAG/USB interface• 3” x 1” prototyping area• RoHS-compliant packaging and process* LCD panel and SD/CompactFlash memory not included in thedevelopment kit• The Standard Edition Hercules DevelopmentKit features the following:- Preloaded Board Digital ManagementDemo- Hercules Standard Edition eval board- Power Manager II ispPAC-POWR1220AT8 and MachXOLCMXO2280 PLD• The Advanced Edition Hercules DevelopmentKit features the following:- Preloaded Board Digital ManagementDemo- Hercules Advanced Edition evaluationboard with CompactPCI headers- Power Manager II ispPAC-POWR1220AT8 and MachXOLCMXO2280 PLD- Backplane accessory evaluation boardand power supply for live hot-swap• AC adapter (international plugs)• USB Connector Cable• RoHS-compliant packaging and process• Pre-configured Processor Support Demo• ProcessorPM-POWR605• Power Manager II POWR6AT6• 3.3V, 2.5V, and 1.8V supply rails• LEDs• Slide potentiometer• 2x14 expansion header• USB mini jack socket (program/power)• 2 Push-Buttons• Preloaded Power Management Demo• LPTM10-12107, Platform Manager, 208-ballftBGA package• 35mm slide pots to emulate supply railvariations• Pads for user I/O, LED, and switches• JTAG and I2C interface headers• USB Cable• 4-Bit DIP Switch• JTAG and I2C Header Landings• RoHS-compliant packaging and process• USB connector cable• QuickSTART Guide• AC adapter with international plugs• Programmable with ispVM System software• QuickSTART GuideVersatile, ready to use hardware platformsfor evaluating and designing with PowerManager II devices. A Standard and Ad-vanced Edition of each kit is available.Versatile, ready-to-use hardware platformfor evaluating and designing with Proces-sorPM power management devices.A versatile, ready-to-use hardware plat-form for evaluating and designing withPlatform Manager devices.Features:Breakout Board Evaluation Kits•Preprogrammed with hardware test programLCMXO2-1200ZE-1TG144C PLD (MachXO2Breakout Board), LCMXO2280C-FTN256CPLD (MachXO2280 Breakout Board),POWR1014A-02TN48I (POWR1014ABreakout Board), or LC4256ZE-TN144C CPLD(ispMACH 4256ZE Breakout Board)• LEDs•Expansion Header LandingsBreakout Board Evaluation Kits for selectMachXO2, MachXO, ispMACH 4000ZE,Power Manager II devices offer convenienthardware evaluations by providing easyhand-access to PLD I/Os.•Prototyping Area•USB Mini Jack Socket (Program/Power)•JTAG Header Landing•RoHS-compliant packaging and process•USB connector cableMachXO Mini Development Kit Features• MachXO PLD: LCMXO2280C-4TN144C• 2 Mbit SPI Flash memory• 1 Mbit SRAM• I2C temperature sensor• USB mini jack sockets for power, JTAG programming, and RS-232 debugging• 2X16 header for off-board expansion provides access to top and right side MachXO banks • Push-buttons for sleep mode and reset• 4-bit DIP switch to user-defined inputs• ADC/DAC circuit• Sleep circuit• 8 LEDs for user-defined outputs• RoHS-compliant packaging and process• Two USB connector cables • QuickSTART GuidePage 17Programming HardwarePage 18PAC-Designer — Mixed-Signal Design SoftwarePage 19Technical SupportUSA & Canada: 1-800-LATTICE (528-8423)For other locations: +1-503-268-8001PLDTechnicalandSoftware:***************************MixedSignal:***********************Additionally, customers can receive technical support for Lattice’s Programmable Logic Products from our Asia based applications group, by contacting Lattice Asia applications during the hours of 8:30 a.m. to 5:30 p.m. Beijing Time (CST) +0800 UTC (Chinese and English language only).Asia: +86-21-52989090********************************Corporate HeadquartersLattice Semiconductor Corporation 5555 Northeast Moore CourtHillsboro, Oregon 97124-6421 USA Telephone: +1-503-268-8000Facsimile: +1-503-268-8347Web: Software LicensingEmail:************************Web: /licensing/index.cfmCopyright © 2012 Lattice Semiconductor Corporation. All brand names or product names are trademarks or registered trademarks of their respective holders. Lattice Semiconductor Corporation, L Lattice Semiconductor Corporation (logo), L (stylized), L (design), Lattice (design), Lattice Diamond, LSC, E 2CMOS, FlashBAK, flexiFLASH, flexiMAC, flexiPCS, FreedomChip, GAL, GDX, Generic Array Logic, HDL Explorer, iCE40, iCEblink, iCEcube2, IPexpress, ISP , ispATE, ispClock, ispDOWNLOAD, ispGAL, ispGDS, ispGDX, ispGDXV, ispGDX2, ispGENERATOR, ispJTAG, ispLeverCORE, ispLSI, ispMACH, ispPAC, ispTURBO, ispVIRTUAL MACHINE, ispVM, ispXP , ispXPGA, ispXPLD, LatticeCORE, LatticeECP3, LatticeECP2, LatticeECP2M, LatticeECP , LatticeECP-DSP , LatticeMico, LatticeMico8, LatticeMico32, LatticeSC, LatticeSCM, LatticeXP , LatticeXP2, MACH, MachXO, MachXO2, MACO, ORCA, PAC, PAC-Designer, PAL, Performance Analyst, Platform Manager, ProcessorPM, PURESPEED, Reveal, Silicon Forest, Speedlocked, Speed Locking, sysCLOCK, sysCONFIG, sysDSP , sysHSI, sysI/O, sysMEM, The Simple Machine for Complex Design, TransFR, UltraMOS, and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries. ISP is a service mark of Lattice Semiconductor Corporation.August 2012 • Order #: I0211HLCMXO2-1200ZE-P1-EVN。

Atmega16单片机介绍Atmega16单片机介绍ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RW W),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态;ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声;Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

ATmega16解锁刚刚把以前锁死的两块Mega16给解开锁,之前自己也解了很多次就是没解开。

在网上看了一些解锁的方法,都是说在ISP下载功能被禁止时,可以用JTAG下载来改变熔丝位ISPEN=0,让Mega16恢复ISP下载功能。

如果两种下载方式都被锁死的情况下,就只能用高压并行的方式来修改熔丝位。

还有一种很简单的方法就是在Mega16的XTAL1和XTAL2引脚接上一个振荡信号,使单片机能处在工作状态,改变其熔丝位。

Mega16的熔丝位配置错和对单片机的某些误操作很容易使单片机不能正常工作。

一种情况是在配置熔丝位时误将ISPEN或JTAGEN置为1(或没有在复选框中打钩),单片机的ISP和JTAG下载功能没有使能,使得单片机被锁死。

还有一种情况是配置的时钟源熔丝位CKSEL3/0与单片机本身工作的时钟源不相符,这也是单片机被锁死的原因。

我的两块Mega16都是由于时钟源选择错误导致被锁死,我也是今天刚注意到这个问题的。

我将一块正常运行的51的XTAL2与Mega16的XTAL1连接,将51的XTAL1与Mega16的XTAL2连接,这样被锁死的Mega16就可以正常运行了。

然后,先要在读取其熔丝位的配置,然后我把时钟源CKSEL3/0的熔丝位改成内部RC振荡8MHZ(改成自己单片机适合的熔丝位即可),将改后的配置写入单片机。

最后将与51连接的线断开,重新将下载器与电脑接上,就可以给M16下载程序了。

1.编程与状态说明(1)在avr的器件手册中,使用已编程(programmed)和未编程(unprogrammed)定义熔丝位的状态。

未编程表示熔丝位状态为“1”(禁止);已编程表示熔丝位状态为“0”(允许)。

(2)avr的熔丝位可以多次编程,不是一次性的opt熔丝。

(3)熔丝位的配置可以通过并行方式、isp串行方式和jtag串行方式实现。

(4)avr芯片加密锁定后(lb2/lb1=1/0,0/0)不能通过任何方式读取芯片内部的flash和eeprom数据,但是熔丝位的状态仍然可以读取,只是不能修改配置。

HIC1016多功能电源集成电路

HIC1016是一块应用于东芝系列大屏幕彩电开关电源中的多功能电源集成电路。

1.内电路原理方框图

HIC 1016集成电路内含电源二次回路的误差电平检测、取样放大、待机控制以及行与场输出等复合保护电路。

其集成块的内电路方框图及典型应用电路如图所示。

2.引脚功能及数据

HIC 1016集成电路的引脚功能及数据见表所列。

3.典型应用电路

HIC1016典型应用电路如图所示。

HIC 1016的开路电阻见表所列,供判断IC好坏时参考。

HIC1016集成电路内部元件的规格数据见表所列。