Low Power Design of High Speed CMOS Pulse Stream Neuron Circuit

- 格式:pdf

- 大小:1.26 MB

- 文档页数:5

256K (32K x 8) Static RAMCY62256Features•High speed —55ns •Temperature Ranges —Commercial: 0°C to 70°C —Industrial: –40°C to 85°C —Automotive: –40°C to 125°C •Voltage range —4.5V – 5.5V•Low active power and standby power•Easy memory expansion with CE and OE features •TTL-compatible inputs and outputs •Automatic power-down when deselected •CMOS for optimum speed/power•Available in a Pb-free and non Pb-free standard 28-pin narrow SOIC, 28-pin TSOP-1, 28-pin Reverse TSOP-1 and 28-pin DIP packagesFunctional Description [1]The CY62256 is a high-performance CMOS static RAM organized as 32K words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE) and active LOW output enable (OE) and Tri-state drivers. This device has an automatic power-down feature, reducing the power consumption by 99.9% when deselected.An active LOW write enable signal (WE) controls the writing/reading operation of the memory. When CE and WE inputs are both LOW, data on the eight data input/output pins (I/O 0 through I/O 7) is written into the memory location addressed by the address present on the address pins (A 0through A 14). Reading the device is accomplished by selecting the device and enabling the outputs, CE and OE active LOW,while WE remains inactive or HIGH. Under these conditions,the contents of the location addressed by the information on address pins are present on the eight data input/output pins.The input/output pins remain in a high-impedance state unless the chip is selected, outputs are enabled, and write enable (WE) is HIGH.Note:1.For best practice recommendations, please refer to the Cypress application note “System Design Guidelines” on .A 9A 8A 7A 6A 5A 4A 3A 2COLUMN DECODERR O W D E C O D E RS E N S E A M P SINPUTBUFFERPOWER DOWNWE OEI/O 0CE I/O 1I/O 2I/O 3I/O 7I/O 6I/O 5I/O 4A 10A 13A 11A 12A A 14A 1Logic Block Diagram32K × 8ARRAYPin ConfigurationsProduct PortfolioProductV CC Range (V)Speed (ns)Power DissipationOperating, I CC(mA)Standby, I SB2(µA)Min.Typ.[2]Max.Typ.[2]Max.Typ.[2]Max.CY62256L Com’l/Ind’l 4.55.05.555/702550250CY62256LL Commercial 7025500.15CY62256LL Industrial 55/7025500.110CY62256LLAutomotive5525500.11512345678910111415162019181721242322Top ViewNarrow SOIC 121325282726GNDA 6A 7A 8A 9A 10A 11A 12A 13WE V CC A 4A 3A 2A 1I/O 7I/O 6I/O 5I/O 4A 14A 5I/O 0I/O 1I/O 2CE OE A 0I/O 322232425262728125101115141312161918173420217689OEA 1A 2A 3A 4WE V CC A 5A 6A 7A 8A 9A 0CE I/O 7I/O 6I/O 5GND I/O 2I/O 1I/O 4I/O 0A 14A 10A 11A 13A 12I/O 3TSOP I Top View (not to scale)Reverse Pinout 22232425262728125101115141312161918173420217689OE A 1A 2A 3A 4WE V CC A 5A 6A 7A 8A 9A 0CE I/O 7I/O 6I/O 5GND I/O 2I/O 1I/O 4I/O 0A 14A 10A 11A 13A 12I/O 3TSOP I Top View (not to scale)12345678910111415162019181721242322Top ViewDIP 121325282726GNDA 6A 7A 8A 9A 10A 11A 12A 13WE V CC A 4A 3A 2A 1I/O 7I/O 6I/O 5I/O 4A 14A 5I/O 0I/O 1I/O 2CE OE A 0I/O 3Pin DefinitionsPin Number Type Description1–10, 21, 23–26Input A 0–A 14. Address Inputs11–13, 15–19, Input/Output I/O 0–/O 7. Data lines. Used as input or output lines depending on operation27Input/Control WE . When selected LOW, a WRITE is conducted. When selected HIGH, a READ is conducted20Input/Control CE . When LOW, selects the chip. When HIGH, deselects the chip22Input/ControlOE . Output Enable. Controls the direction of the I/O pins. When LOW, the I/O pins behave as outputs. When deasserted HIGH, I/O pins are Tri-stated, and act as input data pins14GroundGND . Ground for the device28Power Supply V CC . Power supply for the deviceNote:2.Typical specifications are the mean values measured over a large sample size across normal production process variations and are taken at nominal conditions (T A = 25°C, V CC ). Parameters are guaranteed by design and characterization, and not 100% tested.Maximum Ratings(Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage to Ground Potential(Pin 28 to Pin 14)..............................................–0.5V to +7V DC Voltage Applied to Outputsin High-Z State[3]....................................–0.5V to V CC + 0.5V DC Input Voltage[3]................................–0.5V to V CC + 0.5V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... > 2001V (per MIL-STD-883, Method 3015)Latch-up Current.................................................... > 200 mA Operating RangeRange Ambient Temperature (T A)[4]V CC Commercial0°C to +70°C 5V± 10% Industrial–40°C to +85°C 5V± 10% Automotive–40°C to +125°C 5V± 10%Electrical Characteristics Over the Operating RangeParameter Description Test ConditionsCY62256−55CY62256−70Unit Min.Typ.[2]Max.Min.Typ.[2]Max.V OH Output HIGH Voltage V CC = Min., I OH = −1.0 mA 2.4 2.4V V OL Output LOW Voltage V CC = Min., I OL = 2.1 mA0.40.4VV IH Input HIGH Voltage 2.2V CC+0.5V 2.2V CC+0.5VVV IL Input LOW Voltage–0.50.8–0.50.8V I IX Input Leakage Current GND < V I < V CC–0.5+0.5–0.5+0.5µA I OZ Output Leakage Current GND < V O < V CC, Output Disabled–0.5+0.5–0.5+0.5µAI CC V CC Operating SupplyCurrent V CC = 5.5V,I OUT = 0 mA,f = f Max = 1/t RCL25502550mALL25502550I SB1Automatic CEPower-down Current—TTL Inputs V CC = 5.5V, CE > V IH,V IN > V IH or V IN < V IL,f = f MaxL0.40.60.40.6mALL0.30.50.30.5I SB2Automatic CEPower-down Current—CMOS Inputs V CC = 5.5V,CE > V CC− 0.3VV IN > V CC− 0.3V, orV IN < 0.3V, f = 0L250250µALL - Com’l0.150.15LL - Ind’l0.1100.110LL - Auto0.115Capacitance[5]Parameter Description Test Conditions Max.UnitC IN Input Capacitance T A = 25°C, f = 1 MHz, V CC = V CC(typ.)6pFC OUT Output Capacitance8pF Thermal Resistance[5]Parameter Description Test Conditions DIP SOIC TSOP RTSOP UnitΘJA Thermal Resistance(Junction to Ambient)Still Air, soldered on a 4.25 x 1.125 inch,2-layer printed circuit board75.6176.5693.8993.89°C/WΘJC Thermal Resistance(Junction to Case)43.1236.0724.6424.64°C/WNotes:3.V IL (min.)= −2.0V for pulse durations of less than 20 ns.4.T A is the “Instant-On” case temperature.5.Tested initially and after any design or process changes that may affect these parameters.AC Test Loads and WaveformsData Retention CharacteristicsParameter DescriptionConditions [6]Min.Typ.[2]Max.Unit V DR V CC for Data Retention 2.0V I CCDRData Retention CurrentL V CC = 2.0V , CE > V CC − 0.3V ,V IN > V CC − 0.3V , or V IN < 0.3V250µA LL - Com’l 0.15µA LL - Ind’l 0.110µA LL - Auto0.110µA t CDR [5]Chip Deselect to Data Retention Time 0ns t R [5]Operation Recovery Timet RCnsData Retention WaveformNote:6.No input may exceed V CC + 0.5V .3.0V 5V OUTPUTR1 1800ΩR2990Ω100pF INCLUDING JIG AND SCOPEGND90%10%90%10%<5ns<5ns5V OUTPUTR1 1800ΩR2990Ω5pFINCLUDING JIG AND SCOPE (a)(b)OUTPUT1.77VEquivalent to:THE VENIN EQUIVALENTALL INPUT PULSES 639ΩV CC(min)V CC(min)t CDRV DR >2V DATA RETENTION MODEt RCEV CCSwitching Characteristics Over the Operating Range[7]Parameter DescriptionCY62256−55CY62256−70Unit Min.Max.Min.Max.Read Cyclet RC Read Cycle Time5570nst AA Address to Data Valid5570nst OHA Data Hold from Address Change55nst ACE CE LOW to Data Valid5570nst DOE OE LOW to Data Valid2535nst LZOE OE LOW to Low-Z[8]55nst HZOE OE HIGH to High-Z[8, 9]2025nst LZCE CE LOW to Low-Z[8]55nst HZCE CE HIGH to High-Z[8, 9]2025nst PU CE LOW to Power-up00nst PD CE HIGH to Power-down5570ns Write Cycle[10, 11]t WC Write Cycle Time5570nst SCE CE LOW to Write End4560nst AW Address Set-up to Write End4560nst HA Address Hold from Write End00nst SA Address Set-up to Write Start00nst PWE WE Pulse Width4050nst SD Data Set-up to Write End2530nst HD Data Hold from Write End00nst HZWE WE LOW to High-Z[8, 9]2025nst LZWE WE HIGH to Low-Z[8]55ns Notes:7.Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specifiedI OL/I OH and 100 pF load capacitance.8.At any given temperature and voltage condition, t HZCE is less than t LZCE, t HZOE is less than t LZOE, and t HZWE is less than t LZWE for any given device.9.t HZOE, t HZCE, and t HZWE are specified with C L = 5 pF as in (b) of AC Test Loads. Transition is measured ±500 mV from steady-state voltage.10.The internal Write time of the memory is defined by the overlap of CE LOW and WE LOW. Both signals must be LOW to initiate a Write and either signal canterminate a Write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the Write.11.The minimum Write cycle time for Write Cycle #3 (WE controlled, OE LOW) is the sum of t HZWE and t SD.Switching WaveformsRead Cycle No. 1 (Address Transition Controlled)[12, 13]Read Cycle No. 2 (OE Controlled)[13, 14]Write Cycle No. 1 (WE Controlled)[10, 15, 16]Notes:12.Device is continuously selected. OE, CE = V IL .13.WE is HIGH for Read cycle.14.Address valid prior to or coincident with CE transition LOW.15.Data I/O is high impedance if OE = V IH .16.If CE goes HIGH simultaneously with WE HIGH, the output remains in a high-impedance state. 17.During this period, the I/Os are in output state and input signals should not be applied.ADDRESSDATA OUTPREVIOUS DATA VALIDDATA VALIDt RCt AAt OHA50%50%DATA VALIDt RCt ACEt DOEt LZOEt LZCE t PUHIGH IMPEDANCEt HZOE t HZCEt PDIMPEDANCEICCISBHIGH DATA OUTOECEV CC SUPPLY CURRENTt HDt SDt PWEt SAt HAt AWt WCt HZOEDATA IN VALIDNOTE 17DATA I/OADDRESSCEWEOEWrite Cycle No. 2 (CE Controlled)[10, 15, 16]Write Cycle No. 3 (WE Controlled, OE LOW)[11, 16]Switching Waveforms (continued)t WCt AWt SAt HAt HDt SDt SCEDATA IN VALIDWEDATA I/OADDRESSCEt HD t SDt LZWEt SAt HAt AWt WCt HZWEDATA IN VALIDNOTE 17DATA I/OADDRESSWECETypical DC and AC Characteristics1.21.41.00.60.40.24.04.55.05.56.01.61.41.21.00.8−5525125−55251251.21.00.8N O R M A L I Z E D t A A120100806040200.01.02.03.04.0O U T P U T S O U R C E C U R R E N T (m A )SUPPLY VOLTAGE (V)NORMALIZED SUPPLY CURRENT vs.SUPPLY VOLTAGENORMALIZED ACCESS TIME vs.AMBIENT TEMPERATURE AMBIENT TEMPERATURE (°C)NORMALIZED SUPPLY CURRENT vs.AMBIENT TEMPERATUREAMBIENT TEMPERATURE (°C)OUTPUT VOLTAGE (V)OUTPUT SOURCE CURRENT vs.OUTPUT VOLTAGE 0.00.81.41.11.00.94.04.55.05.56.0N O R M A L I Z E D t A ASUPPLY VOLTAGE (V)NORMALIZED ACCESS TIME vs.SUPPLY VOLTAGE 120140*********0.01.02.03.04.0O U T P U T S I N K C U R R E N T (m A )080OUTPUT VOLTAGE (V)OUTPUT SINK CURRENT vs.OUTPUT VOLTAGE0.60.40.20.0N O R M A L I Z E D I C CN O R M A L I Z E D I C C , I S BI CCI CCV CC = 5.0VV CC = 5.0V T A = 25°CV CC = 5.0V T A = 25°CI SBT A = 25°C0.60.801.31.2V IN = 5.0V T A = 25°C1.4V CC = 5.0V V IN = 5.0V−55251052.52.01.5CURRENT vs.AMBIENT TEMPERATUREAMBIENT TEMPERATURE (°C)1.00.50.0–0.5I SB3.0STANDBY V CC = 5.0V V IN = 5.0VI S B 2 µATruth TableCE WE OE Inputs/Outputs ModePowerH X X High-Z Deselect/Power-down Standby (I SB )L H L Data Out Read Active (I CC )L L X Data In WriteActive (I CC )LHHHigh-ZOutput DisabledActive (I CC )Typical DC and AC Characteristics (continued)3.02.52.01.51.00.50.01.02.03.04.0N O R M A L I Z E D I P OSUPPLY VOLTAGE (V)TYPICAL POWER-ON CURRENT vs.SUPPLY VOLTAGE 30.025.020.015.010.05.00200400600800D E L T A t (n s )AA CAPACITANCE (pF)TYPICAL ACCESS TIME CHANGE vs.OUTPUT LOADING1.251.000.7510203040N O R M A L I Z E D I C CCYCLE FREQUENCY (MHz)0.05.00.010000.50V CC = 4.5V T A = 25°CV CC =5.0V T A = 2 5°C V IN = 0.5VNORMALIZED I CC vs. CYCLE TIMEOrdering InformationSpeed(ns)Ordering Code PackageDiagram Package TypeOperatingRange55CY62256LL−55SNI51-8509228-pin (300-mil Narrow Body) SNC Industrial CY62256LL−55SNXI28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−55ZXI51-8507128-pin TSOP I (Pb-free)CY62256LL−55SNE51-8509228-pin (300-mil Narrow Body) SNC AutomotiveCY62256LL−55SNXE28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−55ZE51-8507128-pin TSOP ICY62256LL−55ZXE28-pin TSOP I (Pb-free)CY62256LL−55ZRXE51-8507428-pin Reverse TSOP I (Pb-free)70CY62256LL−70PC51-8501728-pin (600-Mil) Molded DIP Commercial CY62256LL−70PXC28-pin (600-Mil) Molded DIP (Pb-free)CY62256L−70SNC51-8509228-pin (300-mil Narrow Body) SNCCY62256L−70SNXC28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70SNC28-pin (300-mil Narrow Body) SNCCY62256LL−70SNXC28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70ZC51-8507128-pin TSOP ICY62256LL−70ZXC28-pin TSOP I (Pb-free)CY62256L–70SNI51-8509228-pin (300-mil Narrow Body) SNC IndustrialCY62256L–70SNXI28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70SNI28-pin (300-mil Narrow Body) SNCCY62256LL−70SNXI28-pin (300-mil Narrow Body) SNC (Pb-free)CY62256LL−70ZXI51-8507128-pin TSOP I (Pb-free)CY62256LL−70ZRI51-8507428-pin Reverse TSOP ICY62256LL−70ZRXI28-pin Reverse TSOP I (Pb-free)Please contact your local Cypress sales representative for availability of these partsPackage DiagramsPackage Diagrams (continued)28-pin Thin Small Outline Package Type 1 (8 x 13.4 mm) (51-85071)51-85071-*GDocument #: 38-05248 Rev. *F Page 13 of 14All product and company names mentioned in this document are the trademarks of their respective holders.Package Diagrams (continued)51-85074-*F28-pin Reverse Thin Small Outline Package Type 1 (8x13.4 mm) (51-85074)Document History PageDocument Title: CY62256, 256K (32K x 8) Static RAM Document Number: 38-05248REV.ECN NO.IssueDateOrig. ofChange Description of Change**11345403/06/02MGN Change from Spec number: 38-00455 to 38-05248Remove obsolete parts from ordering info, standardize format*A11522705/23/02GBI Changed SN Package Diagram*B11650609/04/02GBI Added footnote 1Corrected package description in Ordering Information table*C238448See ECN AJU Added Automotive product information*D344595See ECN SYT Added Pb-free packages on page# 10*E395936See ECN SYT Changed address of Cypress Semiconductor Corporation on Page# 1 from“3901 North First Street” to “198 Champion Court”Added CY62256L–70SNXI package in the Ordering Information on Page # 10 *F493277See ECN VKN Updated Ordering Information table。

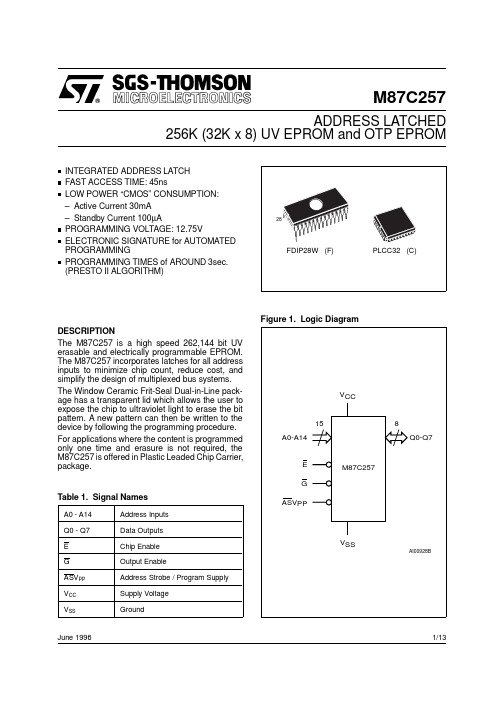

M87C257ADDRESS LATCHED256K (32K x 8) UV EPROM and OTP EPROMJune 19961/13Figure 1. Logic DiagramINTEGRATED ADDRESS LATCH FAST ACCESS TIME: 45nsLOW POWER “CMOS” CONSUMPTION:–Active Current 30mA –Standby Current 100µAPROGRAMMING VOLTAGE: 12.75VELECTRONIC SIGNATURE for AUTOMATED PROGRAMMINGPROGRAMMING TIMES of AROUND 3sec.(PRESTO II ALGORITHM)DESCRIPTIONThe M87C257 is a high speed 262,144 bit UV erasable and electrically programmable EPROM.The M87C257 incorporates latches for all address inputs to minimize chip count, reduce cost, and simplify the design of multiplexed bus systems.The Window Ceramic Frit-Seal Dual-in-Line pack-age has a transparent lid which allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written to the device by following the programming procedure.For applications where the content is programmed only one time and erasure is not required, the M87C257 is offered in Plastic Leaded Chip Carrier,package.Table 1. Signal NamesFigure 2A. DIP Pin ConnectionsFigure 2B. LCC Pin ConnectionsDEVICE OPERATIONThe modes of operation of the M87C257 are listed in the Operating Modes. A single power supply is required in the read mode. All inputs are TTL levels except for V PP and 12V on A9 for Electronic Signa-ture. Read ModeThe M87C257 has two control functions, both of which must be logically active in order to obtain data at the outputs. Chip Enable (E) is the power control and should be used for device selection.Output Enable (G) is the output control and shouldNotes:1.Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings"may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the SGS-THOMSON SURE Program and other relevant quality documents.2.Minimum DC voltage on Input or Output is –0.5V with possible undershoot to –2.0V for a period less than 20ns. Maximum DC voltage on Output is V CC +0.5V with possible overshoot to V CC +2V for a period less than 20ns.Table 2. Absolute Maximum Ratings (1)IH IL IDTable 3. Operating ModesTable 4. Electronic Signaturebe used to gate data to the output pins, inde-pendent of device selection. Assuming that the addresses are stable (AS = V IH ) or latched (AS =V IL ), the address access time (t AVQV ) is equal to the delay from E to output (t ELQV ). Data is available at the output after delay of t GLQV from the falling edge of G, assuming that E has been low and the ad-dresses have been stable for at least t AVQV -t GLQV .The M87C257 reduces the hardware interface in multiplexed address-data bus systems. The proc-essor multiplexed bus (AD0-AD7) may be tied to the M87C257’s address and data pins. No sepa-rate address latch is needed because the M87C257 latches all address inputs when AS is low.Standby ModeThe M87C257 has a standby mode which reduces the active current from 30mA to 100µA (Address Stable). The M87C257 is placed in the standby mode by applying a CMOS high signal to the E input. When in the standby mode, the outputs are in a high impedance state, independent of the G input.Two Line Output ControlBecause EPROMs are usually used in larger mem-ory arrays, this product features a 2 line control function which accommodates the use of multiple memory connection. The two line control function allows:a. the lowest possible memory power dissipation,b. complete assurance that output bus contention will not occur.For the most efficient use of these two control lines,E should be decoded and used as the primary device selecting function, while G should be made a common connection to all devices in the arraycontrol bus. This ensures that all deselected mem-ory devices are in their low power standby mode and that the output pins are only active when data is desired from a particular memory device.Figure 3. AC Testing Input Output WaveformFigure 4. AC Testing Load CircuitTable 5. AC Measurement ConditionsTable 6. Capacitance (1) (T A = 25 °C, f = 1 MHz )System ConsiderationsThe power switching characteristics of Advance CMOS EPROMs require careful decoupling of the devices. The supply current, I CC , has three seg-ments that are of interest to the system designer:the standby current level, the active current level,and transient current peaks that are produced by the falling and rising edges of E. The magnitude of this transient current peaks is dependent on the capacitive and inductive loading of the device at the output. The associated transient voltage peaks canbe suppressed by complying with the two lineoutput control and by properly selected decoupling capacitors. It is recommended that a 0.1µF ceramic capacitor be used on every device between V CC and V SS . This should be a high frequency capacitor of low inherent inductance and should be placed as close to the device as possible. In addition, a 4.7µF bulk electrolytic capacitor should be used between V CC and V SS for every eight devices. The bulk capacitor should be located near the power supply connection point. The purpose of the bulk capacitor is to overcome the voltage drop caused by the inductive effects of PCB traces.Notes:1.V CC must be applied simultaneously with or before V PP and removed simultaneously or after V PP .2.Maximum DC voltage on Output is V CC +0.5V.Table 7. Read Mode DC Characteristics (1)(T A = 0 to 70°C, –40 to 85°C, –40 to 105°C or –40 to 125°C; V CC = 5V ± 5% or 5V ± 10%; V PP = V CC )CC PP PP 2. Sampled only, not 100% tested.3.In case of 45ns speed see High Speed AC measurement conditions.Table 8A. Read Mode AC Characteristics (1)(T A = 0 to 70°C, –40 to 85°C, –40 to 105°C or –40 to 125°C; V CC = 5V ± 5% or 5V ± 10%; V PP = V CC )Notes:1. V CC must be applied simultaneously with or before V PP and removed simultaneously or after V PP .2. Sampled only, not 100% tested.Table 8B. Read Mode AC Characteristics (1)(T A = 0 to 70°C, –40 to 85°C, –40 to 105°C or –40 to 125°C; V CC = 5V ± 5% or 5V ± 10%; V PP = V CC )Figure 5. Read Mode AC WaveformsNote: 1.V CC must be applied simultaneously with or before V PP and removed simultaneously or after V PP .Table 9. Programming Mode DC Characteristics (1)(T A = 25 °C; V CC = 6.25V ± 0.25V; V PP = 12.75V ±0.25V)CC PP PPTable 10. Programming Mode AC Characteristics (1)(T A = 25 °C; V CC = 6.25V ± 0.25V; V PP= 12.75V ± 0.25V)ProgrammingWhen delivered (and after each erasure for UV EPROM), all bits of the M87C257 are in the "1"state. Data is introduced by selectively program-ming "0"s into the desired bit locations. Although only "0"s will be programmed, both "1"s and "0"s can be present in the data word. The only way tochange a "0" to a "1" is by die exposition to ultra-violet light (UV EPROM). The M87C257 is in the programming mode when V PP input is at 12.75V, G is at V IH and E is pulsed to V IL . The data to be programmed is applied to 8 bits in parallel to the data output pins. The levels required for the ad-dress and data inputs are TTL. V CC is specified to be 6.25 V ± 0.25 V.Figure 6. Programming and Verify Modes AC WaveformsPRESTO II Programming AlgorithmPRESTO II Programming Algorithm allows to pro-gram the whole array with a guaranteed margin, in a typical time of 3.5 seconds. Programming with PRESTO II involves the application of a sequence of 100µs program pulses to each byte until a correct verify occurs (see Figure 7). During programming and verify operation, a MARGIN MODE circuit is automatically activated in order to guarantee that each cell is programmed with enough margin. No overprogram pulse is applied since the verify in MARGIN MODE provides necessary margin to each programmed cell. Program InhibitProgramming of multiple M87C257s in parallel with different data is also easily accomplished. Except for E, all like inputs including G of the parallel M87C257 may be common. A TTL low level pulse applied to a M87C257’s E input, with V PP at 12.75V,will program that M87C257. A high level E inputinhibits the other M87C257s from being pro-grammed.Program VerifyA verify (read) should be performed on the pro-grammed bits to determine that they were correctlyprogrammed. The verify is accomplished with G at V IL , E at V IH , V PP at 12.75V and V CC at 6.25V.Figure 7. Programming FlowchartElectronic SignatureThe Electronic Signature (ES) mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment to automatically match the device to be programmed with its corresponding programming algorithm. The ES mode is functional in the 25°C ± 5°C ambient temperature range that is required when program-ming the M87C257.T o activate the ES mode, the programming equip-ment must force 11.5V to 12.5V on address line A9 of the M87C257, with V CC = V PP = 5V. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from V IL to V IH. All other address lines must be held at V IL during Electronic Signature mode. Byte 0 (A0=V IL) repre-sents the manufacturer code and byte 1 (A0=V IH) the device identifier code. When A9 = V ID, AS need not be toggled to latch each identifier address. For the SGS-THOMSON M87C257, these two identi-fier bytes are given in Table 4 and can be read-out on outputs Q0 to Q7.ERASURE OPERATION (applies for UV EPROM) The erasure characteristics of the M87C257 is suchthat erasure begins when the cells are exposed to light with wavelengths shorter than approximately 4000 Å. It should be noted that sunlight and some type of fluorescent lamps have wavelengths in the 3000-4000 Å range. Research shows that constant exposure to room level fluorescent lighting could erase a typical M87C257 in about 3 years, while it would take approximately 1 week to cause erasure when exposed to direct sunlight. If the M87C257 is to be exposed to these types of lighting conditions for extended periods of time, it is suggested that opaque labels be put over the M87C257 window to prevent unintentional erasure. The recommended erasure procedure for the M87C257 is exposure to short wave ultraviolet light which has wavelength 2537Å. The integrated dose (i.e. UV intensity x exposure time) for erasure should be a minimum of 15 W-sec/cm2. The erasure time with this dos-age is approximately 15 to 20 minutes using an ultraviolet lamp with 12000 µW/cm2 power rating. The M87C257 should be placed within 2.5 cm (1 inch) of the lamp tubes during the erasure. Some lamps have a filter on their tubes which should be removed before erasure.ORDERING INFORMATION SCHEMENote: 1.High Speed, see AC Characteristics section for further information.For a list of available options (Speed, V CC Tolerance, Package, etc...) refer to the current Memory Shortform catalogue.For further information on any aspect of this device, please contact the SGS-THOMSON Sales Office nearest to you.-4545 ns -6060 ns -7070 ns -8080 ns -9090 ns -10100 ns -12120 ns -15150 ns -20200 nsX ± 5% blank± 10%F FDIP28W CPLCC3210 to 70 °C 6–40 to 85 °C 7–40 to 105 °C 3–40 to 125 °CX Additional Burn-in TRTape & Reel PackingFDIP28WDrawing is not to scalePLCC32Drawing is not to scaleInformation furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of t hird parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.© 1996 SGS-THOMSON Microelectronics - All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - T aiwan - Thailand - United Kingdom - U.S.A.。

HC-MOS Power DissipationIf there is one single characteristic that justifies the existence of CMOS,it is low power dissipation.In the quiescent state,high-speed CMOS draws five to seven orders of magnitude less power than the equivalent LSTTL function.When switching,the amount of power dissipated by both metal gate and high-speed silicon gate CMOS is directly propor-tional to the operating frequency of the device.This is be-cause the higher the operating frequency,the more often the device is being switched.Since each transition requires power,power consumption increases with frequency.First,one will find a description of the causes of power con-sumption in HC-CMOS and LSTTL applications.Next will fol-low a comparison of MM54HC/MM74HC to LSTTL power dissipation.Finally,the maximum ratings for power dissipa-tion imposed by the device package will be discussed.Quiescent Power ConsumptionIdeally,when a CMOS integrated circuit is not switching,there should be no DC current paths from V CC to ground,and the device should not draw any supply current at all.However,due to the inherent nature of semiconductors,a small amount of leakage current flows across all reverse-biased diode junctions on the integrated circuit.These leakages are caused by thermally-generated charge carriers in the diode area.As the temperature of the diode in-creases,so do the number of these unwanted charge carri-ers,hence leakage current increases.Leakage current is specified for all CMOS devices as I CC .This is the DC current that flows from V CC to ground when all inputs are held at either V CC or ground,and all outputs are open.This is known as the quiescent state.For the MM54HC/MM74HC family,I CC is specified at ambi-ent temperatures (T A )of 25˚C,85˚C,and 125˚C.There are three different specifications at each temperature,depend-ing on the complexity of the device.The number of diode junctions grows with circuit complexity,thereby increasing the leakage current.The worst case I CC specifications for the MM54HC/MM74HC family are summarized in Table 1.In ad-dition,it should be noted that the maximum I CC current will decrease as the temperature goes below 25˚C.TABLE 1.Supply Current (I CC )for MM54HC/MM74HCSpecified at V CC =6V T A Gate Buffer MSI Unit 25˚C 2.0 4.08.0µA 85˚C 204080µA 125˚C4080160µATo obtain the quiescent power consumption for any CMOS device,simply multiply I CC by the supply voltage:P DC =I CC V CCSample calculations show that at room temperature the maximum power dissipation of gate,buffer,and MSI circuits at V CC =6V are 10µW,20µW,and 40µW,respectively.Dynamic Power ConsumptionDynamic power consumption is basically the result of charg-ing and discharging capacitances.It can be broken down into three fundamental components,which are:1.Load capacitance transient dissipation 2.Internal capacitance transient dissipation 3.Current spiking during switching.Load Capacitance Transient DissipationThe first contributor to power consumption is the charging and discharging of external load capacitances.Figure 1is a schematic diagram of a simple CMOS inverter driving a ca-pacitive load.A simple expression for power dissipation as a function of load capacitance can be derived starting with:Q L =C L V CC where C L is the load capacitance,and Q L is the charge on the capacitor.If both sides of the equation are divided by the time required to charge and discharge the capacitor (one pe-riod,T,of the input signal),we obtain:Since charge per unit time is current (Q L /T =l)and the in-verse of the period of a waveform is frequency (1/T =f):l L =C L V CC f To find the power dissipation,both sides of the equation must be multiplied by the supply voltage (P =Vl),yielding:P L =C L V CC 2f One note of caution is in order.If all the outputs of a device are not switching at the same frequency,then the power con-sumption must be calculated at the proper frequency for each output:P L =V CC 2(C L1f 1+C L2f 2+...+C Ln f n )Examples of devices for which this may apply are:counters,dual flip-flops with independent clocks,and other integrated circuits containing dual,triple,etc.,independent circuits.AN005021-1FIGURE 1.Simple CMOS Inverter Driving aCapacitive External LoadFairchild Semiconductor Application Note 303February 1984HC-CMOS Power DissipationAN-303©1998Fairchild Semiconductor Corporation AN005021Internal Capacitance Transient DissipationInternal capacitance transient dissipation is similar to load capacitance dissipation,except that the internal parasitic “on-chip”capacitance is being charged and discharged.Fig-ure 2is a diagram of the parasitic nodal capacitances asso-ciated with two CMOS inverters.C 1and C 2are capacitances associated with the overlap of the gate area and the source and channel regions of the P-and N-channel transistors,respectively.C 3is due to the overlap of the gate and source (output),and is known as the Miller capacitance.C 4and C 5are capacitances of the para-sitic diodes from the output to V CC and ground,respectively.Thus the total internal capacitance seen by inverter 1driving inverter 2is:C l =C 1+C 2+2C 3+C 4+C 5Since an internal capacitance may be treated identically to an external load capacitor for power consumption calcula-tions,the same equation may be used:P l =C l V CC 2f At this point,it may be assumed that different parts of the in-ternal circuitry are operating at different frequencies.Al-though this is true,each part of the circuit has a fixed fre-quency relationship between it and the rest of the device.Thus,one value of an effective C l can be used to compute the internal power dissipation at any frequency.More will be said about this shortly.Current Spiking During SwitchingThe final contributor to power consumption is current spiking during switching.While the input to a gate is making a tran-sition between logic levels,both the P-and N-channel tran-sistors are turned partially on.This creates a low impedance path for supply current to flow from V CC to ground,as illus-trated in Figure 3.For fast input rise and fall times (shorter than 50ns for the MM54HC/MM74HC family),the resulting power consump-tion is frequency dependent.This is due to the fact that the more often a device is switched,the more often the input is situated between logic levels,causing both transistors to be partially turned on.Since this power consumption is propor-tional to input frequency and specific to a given device in any application,as is C l ,it can be combined with C l .The result-ing term is called “C PD,”the no-load power dissipation ca-pacitance.It is specified for every MM54HC/MM74HC de-vice in the AC Electrical Characteristic section of each data sheet.It should be noted that as input rise and fall times become longer,the switching current power dissipation becomes more dependent on the amount of time that both the P-and N-channel transistors are turned on,and less related to C PD as specified in the data sheets.Figure 4is a representation of the effective value of C PD as input rise and fall times in-crease for the MM54HC/MM74HC08,MM54HC/MM74HC139,and MM54HC/MM74HC390.To get a fair comparison between the three curves,each is divided by the value of C PD for the particular device with fast input rise and fall times.This is represented by “C PD0,”the value of C PD specified in the data sheets for each part.This comparison appears in Figure 5.C PD remains constant for input rise and fall times up to about 20ns,after which it rises,approaching a linear slope of 1.The graphs do not all reach a slope of 1at the same time because of necessary differences in circuit design for each part.The MM54HC/MM74HC08exhibits the greatest change in C PD ,while the MM54HC/MM74HC139shows less of an increase in C PD at any given frequency.Thus,the power dissipation for most of the parts in the MM54HC/MM74HC family will fall within these two curves.One notable exception is the MM54HC/MM74HCU04.AN005021-2FIGURE 2.Parasitic Internal CapacitancesAssociated with Two InvertersAN005021-3AN005021-4FIGURE 3.Equivalent schematic of a CMOS inverter whose input is between logic levels 2Inputs that do not pull all the way to V CC or ground can also cause an increase in power consumption,for the same rea-son given for slow rise and fall times.If the input voltage is between the minimum input high voltage and V CC ,then the input N-channel transistor will have a low impedance (i.e.,be “turned on”)as expected,but the P-channel transistor will not be completely turned off.Similarly,if the input is between ground and the maximum input low voltage,the P-channel transistor will be fully on and the N-channel transistor will be partially on.In either case,a resistive path from V CC to ground will occur,resulting in an increase in power con-sumption.Combining all the derived equations,we arrive at the follow-ing:P TOTAL =(C L +C PD )V CC 2f+l CC V CC This equation can be used to compute the total power con-sumption of any MM54HC/MM74HC device,as well as any other CMOS device,at any operating frequency.It includes both DC and AC contributions to power usage.C PD and l CC are supplied in each data sheet for the particular device,and V CC and f are determined by the particular application.Comparing HC-CMOS to LSTTLAlthough power consumption is somewhat dependent on frequency in LSTTL devices,the majority of power dissi-pated below 1MHz is due to quiescent supply current.LSTTL contains many resistive paths from V CC to ground,and even when it is not switching,it draws several orders of magnitude greater supply current than HC-CMOS.Figure 6is a bar graph comparison of quiescent power requirements (V CC )x(l CC )between LSTTL and HC-CMOS devices.The reduction in CMOS power consumption as compared to LSTTL devices is illustrated in Figure 7and Figure 8.These graphs are comparisons of the typical supply current (l CC )re-quired for equivalent functions in MM54HC/MM74HC,MM54HC/MM74C,CD4000,and 54LS/74LS logic families.The currents were measured at room temperature (25˚C)with a supply voltage of 5V.Figure 7represents the supply current required for a quad NAND gate with one gate in the package switching.The MM54HC/MM74HC family draws slightly more supply cur-rent than the 54C/74C and CD4000series.This is mainly due to the large size of the output buffers necessary to source and sink currents characteristic of the LSTTL family.Other reasons include processing differences and the larger internal circuitry required to drive the output buffers at high frequencies.The frequency at which the CMOS device draws as much power as the LSTTL device,known as the power cross-over-frequency,is about 20MHz.In Figure 8,which is a comparison of equivalent flip-flops (174)and shift registers (164)from the different logic fami-lies,the power cross-over frequency again occurs at about 20MHz.The power cross-over frequency increases as circuit com-plexity increases.There are two major reasons for this.First,having more devices on an LSTTL integrated circuit means that more resistive paths between V CC and ground will occur,and more quiescent current will be required.In a CMOS in-tegrated circuit,although the supply leakage current will in-AN005021-5FIGURE parison of Typical C PD for MM54HC/MM74HC08,MM54HC/MM74HC139MM54HC/MM74HC390as a Function ofInput Rise and Fall Time.t rise =t fall,V CC =5V,T A =25˚CAN005021-6FIGURE 5.Normalized Effective C PD (Typical)for Slow Input Rise and Fall Times.t rise =t fall,V CC =5V,T A =25˚C AN005021-7FIGURE 6.High Speed CMOS (HC-CMOS)vs.LSTTLQuiescent Power Consumption crease,it is of such a small magnitude (nanoAmps per de-vice)that there will be very little increase in total power consumption.Secondly,as system complexity increases,the precentage of the total system operating at the maximum frequency tends to decrease.Figure 9shows block diagrams of a CMOS and an equivalent LSTTL system.In this abstract system,there is a block of parts operating at the maximum frequency (F max ),a block operating at half F max ,a block op-erating at one quarter F max ,and so on.Let us call the power consumed in the first section P1.In a CMOS system,since power consumption is directly proportional to the operating frequency,the amount of power consumed by the second block will be (P1)/2,and the amount used in the third section will be (P1)/4.If the power consumed over a large number of blocks is summed up,we obtain:P TOTAL =P1+(P1)/2+(P1)/4+...+(P1)/(2n–1)and P TOTAL ≤2(P1)Now consider the LSTTL system.Again,the power con-sumed in the first block is P1.The amount of power dissi-pated in the second block is something less than P1,but greater than (P1)/2.For simplicity,we can assume the best case,that P2=(P1)/2.The power consumption for all system blocks operating at frequencies F max /2and below will be dominated by quiescent current,which will not change with frequency.The power used by blocks 3through n will be ap-proximately equal to the power dissipated by block 2,(P1)/2.The total power consumed in the LSTTL system is:P TOTAL =(P1+(P1)/2+(P1)/2+...+(P1)/2P TOTAL =P1+(N–1)(P1)/2and for n >2,P TOTAL >2(P1)Thus,an LSTTL system will draw more power than an equivalent HC-CMOS system.This effect is further illustrated in Figure 10.An arbitrary sys-tem is composed of 200gates,150counters,and 150full adders,with 50pF loads on all of the outputs.The supply voltage is 5V,and the system is at room temperature.For this system,the worst case power consumption for CMOS is about an order of magnitude lower than the typical LSTTL power requirements.Thus,as system complexity increases,CMOS will save more power.Maximum Power Dissipation LimitsIt is important to take into consideration the maximum power dissipation limits imposed on a device by the package when designing with high-speed CMOS.The plastic small-outline (SO)can dissipate up to 500mW,and the ceramic DIP and plastic DIP can dissipate up to 700mW.Although this limit will rarely be reached in typical high-speed applications,the MM54HC/MM74HC family has such large output current source and sink capabilities that driving a resistive load could possibly take a device to the 500or 700mW limit.This maximum power dissipation rating should be derated,start-ing at 65˚C for the plastic packages and 100˚C for the ce-ramic packages.The derating factor is different for each package.The factor for the plastic small-outline is −8.83mW/˚C;the plastic DIP ,−12mW/˚C;and the ceramic DIP ,−14mW/˚C.This is illustrated in Figures 11,12.Thus,if a device in a plastic DIP package is operating at 70˚C,then the maximum power dissipation rating would be 700mW −(70˚C −65˚C)(12mW/˚C)=640mW.Note that the maxi-mum ambient temperature is 85˚C for plastic packages and 125˚C for ceramic packages.AN005021-8FIGURE 7.Supply Current vs.Input Frequencyfor Equivalent NAND GatesAN005021-9FIGURE 8.Supply Current vs.FrequencyAN005021-10FIGURE parison of Equivalent CMOSand LSTTL Systems AN005021-11FIGURE 10.System Power vs.FrequencyMMHC74HC vs.LSTTL 4AN005021-12 FIGURE11.Plastic Package(MM74HC) High Temperature Power Derating for MM54HC/MM74HC FamilyAN005021-13FIGURE12.Ceramic Package(MM54HC)High Temperature Power Deratingfor MM54HC/MM74HC FamilySummaryThe MM54HC/MM74HC high-speed silicon gate CMOS fam-ily has quiescent (standby)power consumption five to seven orders of magnitude lower than the equivalent LSTTL func-tion.At high frequencies (30MHz and above),both families consume a similar amount of power for very simple systems.However,as system complexity increases,HC-CMOS uses much less power than LSTTL.To keep power consumption low,input rise and fall times should be fast (less than 50to 100ns)and inputs should swing all the way to V CC and ground.There is an easy-to-use equation to compute the power con-sumption of any HC-CMOS device in any application:P TOTAL =(C L +C PD )V CC 2f+l CC V CC The maximum power dissipation rating is 500mW per pack-age at room temperature,and must be derated as tempera-ture increases.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMI-CONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or sys-tems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and (c)whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.Fairchild Semiconductor Corporation AmericasCustomer Response Center Tel:1-888-522-5372Fairchild Semiconductor EuropeFax:+49(0)180-5308586Email:**********************Deutsch Tel:+49(0)8141-35-0English Tel:+44(0)1793-85-68-56Italy Tel:+39(0)2575631Fairchild SemiconductorHong Kong Ltd.13th Floor,Straight Block,Ocean Centre,5Canton Rd.Tsimshatsui,Kowloon Hong KongTel:+8522737-7200Fax:+8522314-0061National Semiconductor Japan Ltd.Tel:81-3-5620-6175Fax:81-3-5620-6179A N -303H C -C M O S P o w e r D i s s i p a t i o nFairchild does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.。

DESIGN FEATURES L New Generation of 14-Bit 150Msps ADCs Dissipates a Third the Powerof the Previous Generation without Sacrificing AC Performanceby Clarence Mayott IntroductionThe LTC2262 family of ultralow power,high speed analog-to-digital convert-ers dissipates less than one third thepower of comparable earlier-genera-tion ADCs while maintaining excellentAC performance. Ultralow powermakes it possible to add features to andimprove the performance of power-limited applications while remainingwithin the power budget. Of course,improved operating efficiency alsoreduces recurring operating costs inapplications found in 3G/4G LTE andWiMAX basestation equipment.In addition to offering considerably lower power, the ADCs in the LTC2262 family incorporate a unique set of digi-tal output features that help to simplify layout and reduce digital feedback. The low power core of the LTC2262 is also integrated into multichannel parts, including 4-channel ADCs and 2-channel ADCs. For a complete list of the ultralow-power ADC family, see Table 1.Low Power, High Performance The LTC2262 family includes 14- and 12-bit ADCs that span sampling rates from 25Msps (which can sample down to 1Msps) to 150Msps, while consuming approximately 1mW for every megasample-per-second. For instance, the LTC2262-14 is a 14-bit, 150Msps ADC that consumes only 149mW of power from a 1.8V supply.It is important to note that the ultralow power dissipation for this pipelined ADC architecture comes without sacrificing performance. The LTC2262-14 has a typical signal-to-noise ratio (SNR) of 72.8dB and SFDR of 88dB at baseband. Figure 1 shows the typical AC performance of the LTC2262-14 sampling a 30MHzsine wave at 150Msps (data from thecircuit of Figure 2). The exceptionallow power operation improves thermalperformance in compact enclosures,where high temperatures can degradeSNR.Digital OutputsThe LTC2262 family also offers someunique digital features to simplifyoverall design in a wide variety ofapplications. The LTC2262 can beconfigured to run in one of three dataoutput modes: full rate CMOS, doubledata rate (known as DDR) CMOS, andDDR LVDS.Full rate CMOS presents the data onall 14 lines and consumes the lowestpower. This mode is identical acrossLinear’s parallel CMOS output ADCsso designers can use a much lowerpower ADC without changing FPGAcode or ASIC design.Table 1. The new generation of ultralow-power ADCsSample Rate Resolution Single Channel T wo Channel Four Channel 25Msps12-Bit L TC2256-12L TC2263-12L TC2170-1214-Bit L TC2256-14L TC2263-14L TC2170-14 40Msps12-Bit L TC2257-12L TC2264-12L TC2171-1214-Bit L TC2257-14L TC2264-14L TC2171-14 65Msps12-Bit L TC2258-12L TC2265-12L TC2172-1214-Bit L TC2258-14L TC2265-14L TC2172-14 80Msps12-Bit L TC2259-12L TC2266-12L TC2173-1214-Bit L TC2259-14L TC2266-14L TC2173-14 105Msps12-Bit L TC2260-12L TC2267-12L TC2174-1214-Bit L TC2260-14L TC2267-14L TC2174-14 125Msps12-Bit L TC2261-12L TC2268-12L TC2175-1214-Bit L TC2261-14L TC2268-14L TC2175-14 150Msps12-Bit L TC2262-12N/A N/A14-Bit L TC2262-14N/A N/AFREQUENCY (MHz)–100–110–120–70–60–80–90AMPLITUDE(dBFS)–50–30–40–20–10010203040507060Figure 1. Typical performance of the LTC2262-14L DESIGN FEATURESIf board space or FPGA GPIO is lim-ited, then the DDR CMOS mode can be used reduce the number of data lines. In double data rate LVDS mode, two data bits are multiplexed and output on each differential output pair, one valid on the rising edge of the clock, the other on the falling edge. This allows the data to be clocked out on half the data lines, which reduces the number of lines to seven for the 14-bit ADCs, and six for the 12-bit ADCs.DDR LVDS mode functions in a similar fashion, with two bits clocked out on each data line on each clock cycle, but because it is a differential signal it uses 14 data lines, versus the 28 lines required for standard LVDS signaling. DDR LVDS uses an additional 10mW but the differential signaling provides some rejection ofdigital noise, also known as digitalfeedback.Digital FeedbackDigital feedback occurs when energyfrom ADC outputs couples back intothe analog section, causing interactionthat appears as odd shaping in thenoise floor and spurs in the ADC outputspectrum. The worst situation is atmidscale, where all outputs are chang-ing from ones to zeroes, or vice versa,generating large ground currents thatcouple back into the input.Digital feedback at both the devicelevel and the system level can bemade worse by poor layout choices.Long output busses, routing at lowcharacteristic impedance and heavycapacitive loading at the receivingdevice all conspire to produce higherpulse currents in the output stages.The use of the maximum digitaloutput supply voltage (OV DD) similarlymaximizes digital currents. Placementof OV DD bypass on the bottom of theboard, with added lead inductance,large bodied capacitors, small diam-eter vias, thick boards, and thermalrelief all raise the impedance of thesupply rails to the output section,increasing the potential for noisesources. Returning OGND to a poorlygrounded paddle makes things worse.These layout conditions together con-spire to increase ground bounce onthe substrate, which leads to digitalfeedback.ANALOG INPUTT2Figure 2.Typical application of the LTC2261-14severe cases, localized regions of the noise floor may be elevated by 20dB. If a narrow band application happens to collide with the elevated region of the noise floor, the result is a real loss of SNR on the order of 20dB. While good layout can help reduce the effects of digital feedback, it may not be enough to eliminate the problem.The LTC2262 includes a unique digital feedback mitigation feature called “alternate bit polarity mode.” Digital feedback is likely to occur when sampling a small input signal that iscurrents that can couple back into the analog inputs, maximizing digital feedback. When alternate bit polarity mode is used, every odd data line is inverted. So, instead of 14 data lines simultaneously switching between 0 and 1, half are switching in one direction, half in the other direction. This produces a cancellation of fields, significantly reducing the resulting ground currents, and minimizing digital feedback. To decode this data, simply apply an inverter on each odd data line in the receiver.results in designs with low level input signal.Multiple Channel VersionsThe LTC2262 ultralow power core is also available in 2- and 4-channel ADCs. The LTC2175-14 is a quad, 14-bit ADC that samples at 125Msps. The LTC2175 dissipates only 558mW of total power—only 139.5mW per ADC. At 125Msps, each channel outputs two bits at a time, using only two lines per ADC. This reduces the number of dataA M P L I T U D E (dB )FREQUENCY (Hz)–1144k8k 12k 16k 20k 24k 28k 32k–119–118–117–116–115–123–122–121–120Figure 3. LTC2261 noise floor in normal operationA M P L I T U D E (dB )FREQUENCY (Hz)–114–1234k8k 12k 16k 20k 24k 28k 32k–122–121–120–119–118–117–116–115Figure 5. Noise floor with alternate bit polarity and data output randomizer enabledcontinued on page 30dissipates only 558mW oftotal power—only 139.5mW per ADC. At 125Msps, each channel outputs two bits at a time, using only two lines per ADC. This reduces the number of data lines used by the LTC2175, and allows it to be packaged in a space-saving 7mm × 8mm QFNpackage.L DESIGN IDEASFigure 3. Battery discharge current vs voltage for the LTC4099 battery conditioning functionBATTERY VOL TAGE (V)B A T T E R YC U R R E N T (m A )6090120300150Figure 2. Yearly capacity loss vs temperature and SoC for Li-Ion batteriesTEMPERATURE (°C)C A P A C I T Y L O S S (%)20304010050activation energy can come from heat or the terminal voltage. The more acti-vation energy available from these two sources the greater the chemical reac-tion rate and the faster the aging.Li-Ion batteries that are used in the automotive environment must last 10 to 15 years. So, suppliers of automotive Li-Ion batteries do not rec-ommend charging the batteries above 3.8V. This does not allow the use of the full capacity of the battery, but is low enough on the activation energy PDF to keep corrosion to a minimum. The iron phosphate battery anode has a shallower discharge curve, thus retaining more capacity at 3.8V.Battery manufacturers typically store batteries at 15°C (59°F) and a 40% state of charge (SoC), to minimize aging. Ideally, storage would take place at 4% or 5% SoC, but it must never reach 0%, or the battery may be damaged. Typically, a battery pack protection IC prevents a battery from reaching 0% SoC. But pack protection cannot prevent self-discharge and the pack protection IC itself consumes some current. Although Li-Ion batter-ies have less self-discharge than most other secondary batteries, the storage time is somewhat open-ended. So, 40% SoC represents a compromise between minimizing aging and preventing dam-age while in storage (see Figure 2).In portable applications, the reduc-tion in capacity from such a reduced SoC strategy is viewed negatively in marketing specifications. But it is sufficient to detect the combinationof high ambient heat and high bat-tery SoC to implement an algorithm that minimizes aging while ensuring maximum capacity availability to the user.Battery Conditioner Avoids Conditions that Accelerate Aging The LTC4099 has a built-in battery conditioner that can be enabled ordisabled (default) via the I 2C interface. If the battery conditioner is enabled and the LTC4099 detects that the battery temperature is higher than ~60°C, it gently discharges the battery to minimize the effects of aging. The LTC4099 NTC temperature measure-ment is always on and available to monitor the battery temperature. This circuit is a micropower circuit, draw-ing only 50nA while still providing full functionality.The amount of current used to dis-charge the battery follows the curve shown in Figure 3, reaching zero when the battery terminal voltage is ~3.85V. If the temperature of the battery pack drops below ~40°C and a source ofenergy is available, the LTC4099 once again charges the battery. Thus, the battery is protected from the worst-case battery aging conditions.ConclusionAlthough the aging of Li-Ion batteries cannot be stopped, the LTC4099’s battery conditioner ensures maximum battery life by preventing the battery-killing conditions of simultaneous high voltage and high temperature. Further, the micropower, always on NTC moni-toring circuit ensures that the battery is protected from life-threatening conditions at all times. L lines used by the LTC2175, and allows it to be packaged in a space saving 7mm × 8mm QFN package.The dual version of the LTC2262 is the LTC2268. It dissipates 299mW of total power, or 150mW per ADC. It also has LVDS serial output lines that re-duce space, and allow the LTC2268 to be in a 6mm × 6mm QFN package.The dual and quad versions of LTC2262 are available in 12- and 14-bit versions, in speed grades from 25Msps up to 125Msps. A complete list of the variant is shown in Table 1.Each device shares the excellent AC performance of the LTC2262, and features better than 90dB of chan-nel-to-channel isolation. The serial outputs of the multiple channel parts mitigate the effect of digital feedback, producing a clean output spectrum. In sum, the performance of LTC2262 is not sacrificed when migrating into multiple channel parts.Conclusion The LTC2262 ultralow-power ADC simplifies design with a unique combi-nation of features. Digital noise can be reduced by using DDR LVDS signaling, alternate bit polarity mode, or the data randomizer. The number of data lines needed to transmit 14 bits of data can be reduced to seven with DDR CMOS signaling, which simplifies layout. The LTC2262 is part of a pin-compatible family of 12-bit and 14-bit ADCs with sample rates from 25Msps to 150Msps, with power consumption ranging from35mW at 25Msps up to 149mW at 150Msps while maintaining excellent AC performance characteristics. LLTC2262, continued from page 25。

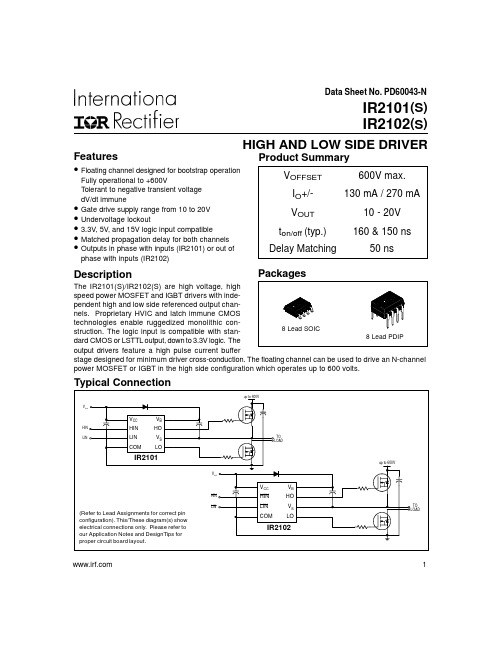

Data Sheet No. PD60043-NFeaturesHIGH AND LOW SIDE DRIVERProduct Summary 1IR2101/IR2102 (S)Absolute Maximum RatingsAbsolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage param-eters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.Note 1: Logic operational for V S of -5 to +600V. Logic state held for V S of -5V to -V BS . (Please refer to the Design Tip DT97-3 for more details).Recommended Operating ConditionsThe input/output logic timing diagram is shown in figure 1. For proper operation the device should be used within the recommended conditions. The V S offset rating is tested with all supplies biased at 15V differential.IR2101/IR2102 (S)Static Electrical CharacteristicsV BIAS (V CC , V BS ) = 15V and T A = 25°C unless otherwise specified. The V IN , V TH and I IN parameters are referenced to COM. The V O and I O parameters are referenced to COM and are applicable to the respective output leads: HO or LO.Dynamic Electrical CharacteristicsV BIAS (V CC , V BS ) = 15V, C L = 1000 pF and T A = 25°C unless otherwise specified.IR2101/IR2102 (S)IR2101/IR2102 (S) Lead DefinitionsSymbol DescriptionHIN Logic input for high side gate driver output (HO), in phase (IR2101)HIN Logic input for high side gate driver output (HO), out of phase (IR2102)LIN Logic input for low side gate driver output (LO), in phase (IR2101)LIN Logic input for low side gate driver output (LO), out of phase (IR2102)V B High side floating supplyHO High side gate drive outputV S High side floating supply returnV CC Low side and logic fixed supplyLO Low side gate drive outputCOM Low side returnLead Assignments8 Lead PDIP8 Lead SOICIR2101IR2101S8 Lead PDIP8 Lead SOICIR2102IR2102SIR2101/IR2102 (S)Figure 1. Input/Output Timing DiagramHIN LINHO LOHIN LIN Figure 3. Delay Matching Waveform DefinitionsHIN LIN50%50%IR2101/IR2102 (S)IR2101/IR2102 (S)IR2101/IR2102 (S)IR2101/IR2102 (S)IR2101/IR2102 (S)IR2101/IR2102 (S)Case outlines。