语法详细讲解

载入存储设备

可以通过使用一个循环或系统任务来载入存有数据的整个存储 器。

ata ,,,,,,,,,,,,,,,0 000 ,,,,,,,,,,,,,,,0 101

reg [3:0] mem [0:15];

,,,,,,,,,,,,,,,1

initial

100

$readmemb(“my_rom_data”,mem); always @ (addr or read_en_)

,,,,,,,,,,,,,,,0

的节点或测试模块中在多个地方被赋值的信号)进行赋值。 initial begin

#10 assign top.dut.fsml.state_reg = `init_state;

语字语强语强法符法制法制详串详详激激,细,细,细励励,,讲讲,讲,,解,解,解

#20 deassign top.dut.fsml.state_reg; end force 和 release 用于寄存器类型和网络连接类型(例如:门级扫 描寄存器的输出)的强制赋值,强制改写其它地方的赋值。

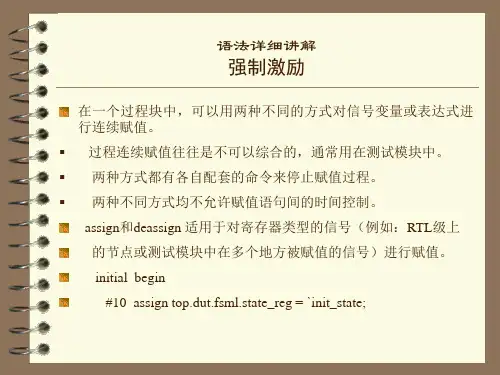

语法详细讲解

强制激励

在一个过程块中,可以用两种不同的方式对信号变量或表达式进 行连续赋值。 ▪ 过程连续赋值往往是不可以综合的,通常用在测试模块中。 ▪ 两种方式都有各自配套的命令来停止赋值过程。 ▪ 两种不同方式均不允许赋值语句间的时间控制。 assign和deassign 适用于对寄存器类型的信号(例如:RTL级上

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,k注延,,,,,,,,:迟,,,,,,,,这期,,,#,,(两间,p,,e,个一,r,i,o,时直,d,,/,2钟 是,,),,,模低,,,,,,,,型电,c,l,k,有平,=,,,!些,,c,,l,不而同门,级行描为述描的述模的型模开型始