USB3.0芯片CYUSB3014硬件设计指南

- 格式:pdf

- 大小:706.50 KB

- 文档页数:16

CYPEESS USB3.0程序解读解读同步FIFO的一个例子。

生产者,消费者首先看DMA的回调函数:typedef void (*CyU3PDmaCallback_t) (CyU3PDmaChannel *handle, /* Handle to the DMA channel. */CyU3PDmaCbType_t type, /* The type of callback notification being generated. */ CyU3PDmaCBInput_t*input /* Union that contains data related to the notification. The input parameter will be a pointer to a CyU3PDmaBuffer_t variable in the cases where the callback type isCY_U3P_DMA_CB_RECV_CPLT or CY_U3P_DMA_CB_PROD_EVENT. */);根据其说明,解读如下:1.对每一个DMA通道,回调函数必须被注册。

如果没有注册或者相应的通知事件没有被注册,则回调函数不会被执行。

2.回调函数不能被阻塞。

即不能用SLEEP()之类的函数。

如果数据需要处理,必须在回调函数之外。

3.在生产者事件中,应用希望尽可能快地处理输入的数据。

如果缓冲的处理不能在规定的时间内完成,则输入的可能是陈旧的数据。

在自动信号通道中,输入参量指向最新的数据。

如果处理延时,生产者socket可能复盖部分数据。

4.在手动或手动IN通道模式时,输入参量指向第一个缓冲(用于去消费者socket).如果在第二次调用时,这个缓冲仍没有被处理,输入参量中将是被陈旧的数据。

如果数据处理必须在通道中做,CyU3PDmaChannelGetBuffer函数必须被应用,而回调函数必须作为一个通知。

基于CYUSB3014 USB3.0总线开发技术[导读]本文介绍了以FPGA为控制核心,以cypress的FX3系列CYUSB3014芯片为总线接口芯片,实现了对USB3.0总线技术的开发应用,实际测试的传输速度能够达到1.43Gbps。

1.引言USB(Universal Serial Bus,通用串行总线)以其无需配置、即插即用等特性获得了广泛的应用。

2004年提出的USB2.0标准,传输速度最大能够达到480Mbps。

但在 USB3.0标准中,它的最大传输速度几乎是传统USB2.0传输速度的10倍,达到了5.0Gbps,被定义为“超高速U S B接口”。

本文基于CYPRESS的FX3系列USB3.0芯片,对USB3.0总线进行研究开发。

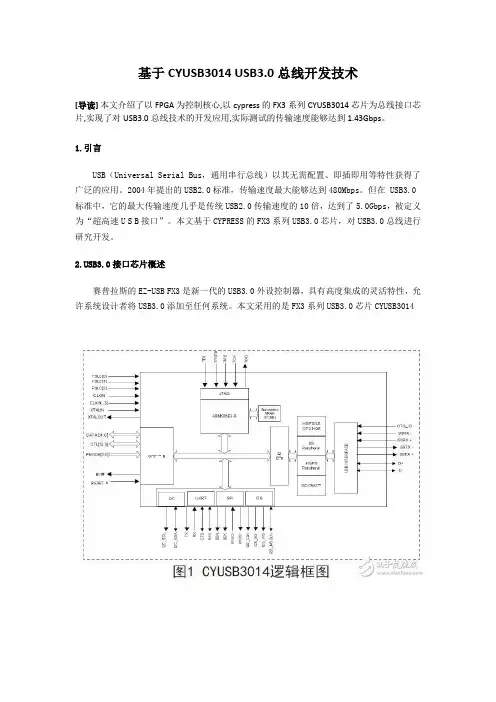

B3.0接口芯片概述赛普拉斯的EZ-USB FX3是新一代的USB3.0外设控制器,具有高度集成的灵活特性,允许系统设计者将USB3.0添加至任何系统。

本文采用的是FX3系列USB3.0芯片CYUSB3014FX3是完全兼容USB3.0 V1.0和USB2.0规范的,集成的USB2.0 OTG控制器允许芯片作为主从设备使用。

另外,它还支持一些常用的外设接口,如SPI,I2C,UART和I2S可以与外部设备进行通信。

FX3具有一个可进行完全配置的并行通用可编程接口GPIF II,它可以与任何处理器、ASIC或是FPGA连接。

它可以轻松无缝地连接至多种常用接口,比如异步SRAM、异步和同步地址数据复用式接口、并行 ATA等等。

EZ-USB FX3集成了USB3.0和USB2.0物理层(PHY)以及32位ARM926EJ-S微处理器,具有强大的数据处理能力,并可用于构建定制应用。

3.系统整体设计本系统设计主要由软件部分和硬件部分组成。

软件部分主要包括三大部分:PC机应用程序、FX3固件程序FPGA程序。

硬件部分主要由FPGA、USB3.0芯片和DDR2组成,硬件的系统框图如图2所示。

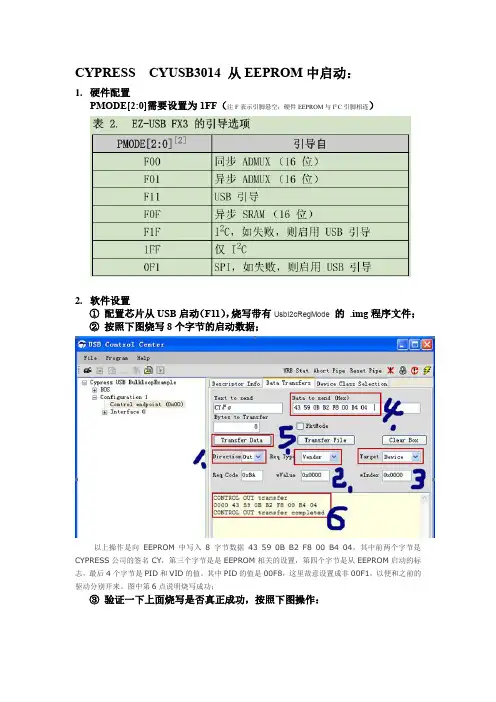

CYPRESS CYUSB3014 从EEPROM中启动:1.硬件配置PMODE[2:0]需要设置为1FF(注F表示引脚悬空;硬件EEPROM与I²C引脚相连)2.软件设置①配置芯片从USB启动(F11),烧写带有UsbI2cRegMode的.img程序文件;②按照下图烧写8个字节的启动数据;以上操作是向EEPROM中写入8字节数据43 59 0B B2 F8 00 B4 04,其中前两个字节是CYPRESS公司的签名CY,第三个字节是是EEPROM相关的设置,第四个字节是从EEPROM启动的标志,最后4个字节是PID和VID的值。

其中PID的值是00F8,这里故意设置成非00F1,以便和之前的驱动分别开来。

图中第6点说明烧写成功;③验证一下上面烧写是否真正成功,按照下图操作:上图中第3,说明从EEPROM中读出的8个字节,正是前一个过程烧写进去的8个字节,烧写成功;④拔掉USB线,将硬件启动模式设置为从EEPROM启动(1FF或F1F);⑤出现下图画面,说明USB芯片已经从EEPROM启动了,由于PID=0081,是新设备,因此需要安装驱动程序。

3.软件编写①Initialize the I2C interface for the EEPROM of page size 64 bytes.→status = CyFxI2cInit (CY_FX_USBI2C_I2C_PAGE_SIZE);②Start the USB functionality.打开USB的功能→status = CyU3PUsbStart();③④⑤→4.I2C 接口采用VIO5 供电,该电压独立于其他串行外设。

这样,I2C接口可以灵活地在不相同的电压下工作,这个不同于其他串行接口。

I2C控制器所支持的总线频率为100 kHz、400kHz和1MHz。

当VIO5为1.2V时,支持的最大工作频率为100kHz。

当VIO5 为1.8 V、2.5 V或3.3 V时,支持的工作频率为400 kHz和1MHz。

cyusb3014硬件设计方案CYUSB3014是一款高性能USB 3.1 Gen 1外围设备控制器,广泛应用于各种USB接口设备中。

本文将详细介绍CYUSB3014的硬件设计方案,包括电路原理图、PCB布局、供电系统等关键设计要点。

一、总体设计方案CYUSB3014的硬件设计方案主要包括如下几个方面:电源管理、时钟系统、传输接口、外设接口以及调试接口等。

1. 电源管理CYUSB3014采用3.3V供电,需要提供一个稳定可靠的电源系统。

一般建议使用线性稳压器或者开关稳压器来提供3.3V电源,同时要遵循电源滤波、去耦、综合保护等设计原则。

2. 时钟系统CYUSB3014需要外部提供参考时钟,常用的方案是使用晶体振荡器与时钟输入引脚相连,振荡器的频率一般为19.2MHz。

此外,还需要为CYUSB3014提供一个时钟源,用于USB通信的时钟同步。

3. 传输接口CYUSB3014支持USB 3.1 Gen 1传输接口,可通过SuperSpeed USB 连接到主机。

在设计传输接口时,需要合理布局USB差分信号对,保证信号传输的稳定性和可靠性。

此外,还需要为数据线提供合适的阻抗匹配电路,以减少信号损耗。

4. 外设接口CYUSB3014支持多种外设接口,如UART、SPI、I2C等。

在设计外设接口时,需要根据实际需求选择合适的接口类型,并遵循相应的电气规范和信号传输原则。

5. 调试接口为了方便调试和测试,CYUSB3014提供了JTAG调试接口。

在设计时,需要保留JTAG接口的引脚,并为其提供合适的连接器,以便于联机调试和故障排除。

二、电路原理图设计电路原理图是CYUSB3014硬件设计的基础,它展示了CYUSB3014与其他电路元件之间的连接关系。

在绘制电路原理图时,需要清晰标注各个元器件的型号、数值和引脚信息,并按照信号流的方向进行布局。

三、PCB布局设计PCB布局设计是CYUSB3014硬件设计中至关重要的一环,它直接关系到电路的稳定性和性能。

USB3.0调试⼿册宁波舜宇车载光学技术有限公司USB3.0数据采集系统FPGA+USB3.0韩斌2017/6/9USB3.0数据采集系统⽤户⼿册批准:审核:作成:⽇期⼀、USB协议概述关于USB的协议在《IFLabs USB3.0核⼼板开发⼿册V1.4》介绍的很详细,接下来主要介绍我在此间所学的⼀些总结和概括。

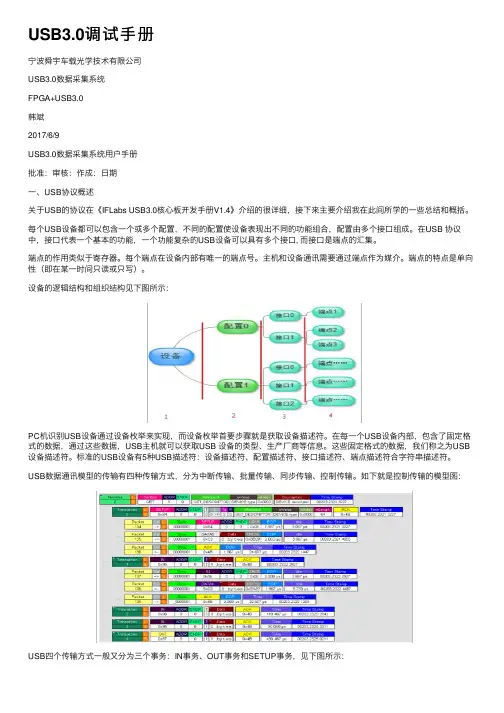

每个USB设备都可以包含⼀个或多个配置,不同的配置使设备表现出不同的功能组合,配置由多个接⼝组成。

在USB 协议中,接⼝代表⼀个基本的功能,⼀个功能复杂的USB设备可以具有多个接⼝, ⽽接⼝是端点的汇集。

端点的作⽤类似于寄存器。

每个端点在设备内部有唯⼀的端点号。

主机和设备通讯需要通过端点作为媒介。

端点的特点是单向性(即在某⼀时间只读或只写)。

设备的逻辑结构和组织结构见下图所⽰:PC机识别USB设备通过设备枚举来实现,⽽设备枚举⾸要步骤就是获取设备描述符。

在每⼀个USB设备内部,包含了固定格式的数据,通过这些数据,USB主机就可以获取USB 设备的类型、⽣产⼚商等信息。

这些固定格式的数据,我们称之为USB 设备描述符。

标准的USB设备有5种USB描述符:设备描述符、配置描述符、接⼝描述符、端点描述符合字符串描述符。

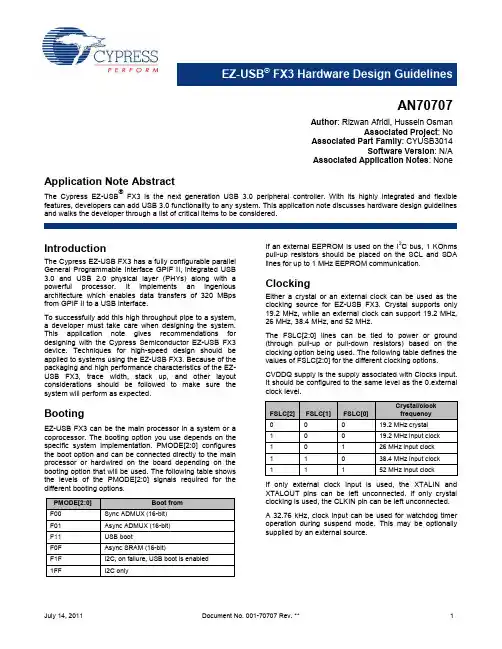

USB数据通讯模型的传输有四种传输⽅式,分为中断传输、批量传输、同步传输、控制传输。

如下就是控制传输的模型图:USB四个传输⽅式⼀般⼜分为三个事务:IN事务、OUT事务和SETUP事务,见下图所⽰:事务⼜分为令牌包(setup)、数据包(data)、握⼿包(ACK)、特殊包,如下图所⽰:⼀个包分为同步域(SYNC),标识域(PID),地址域(ADDR),端点域(ENDP),帧号域(FRAM),数据域(DATA)和校验域(CRC),见下图所⽰:USB正常⼯作之前,第⼀件事就是设备枚举,⽬的就是让主机认得这个USB设备,并且为这个设备配置资源,建⽴好主机与设备之间的数据传输通道。

设备枚举分为如下8个步骤:1,获取设备描述符2,复位3,设置地址4,再次获取设备描述符5,获取配置描述符6,获取端点、配置描述符7,获取字符串描述符8,选择设备配置⼆、CYUSB3014的SDK概述2.1介绍CYUSB3014的开发⽀持包由Cypress⽀持和提供,取名为FX3 SDK。

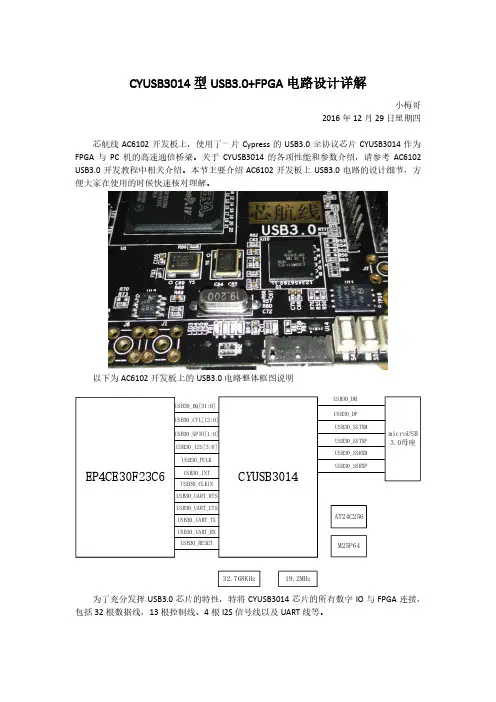

CYUSB3014型USB3.0+FPGA 电路设计详解小梅哥2016年12月29日星期四芯航线AC6102开发板上,使用了一片Cypress 的USB3.0全协议芯片CYUSB3014作为FPGA 与PC 机的高速通信桥梁。

关于CYUSB3014的各项性能和参数介绍,请参考AC6102 USB3.0开发教程中相关介绍。

本节主要介绍AC6102开发板上USB3.0电路的设计细节,方便大家在使用的时候快速核对理解。

以下为AC6102开发板上的USB3.0电路整体框图说明为了充分发挥USB3.0芯片的特性,特将CYUSB3014芯片的所有数字IO 与FPGA 连接,包括32根数据线,13根控制线、4根I2S 信号线以及UART 线等。

复位CYUSB3014有一个复位输入接口,当复位输入为低电平时,芯片处于复位状态。

只有当该引脚为高电平时,芯片才能正常工作,AC6102开发板在设计时,充分考虑了实际应用和系统调试时的情况,给CYUSB3014设计了两种复位方式,分别为FPGA控制复位和上电自动复位。

默认使用上电自动复位方式,该方式非常适合我们调试系统原型时使用,这样不必担心因为重新下载FPGA 的sof固件而导致USB芯片复位,影响USB3.0芯片的正常运行。

增加调试时候的工作量。

(如果使用fpga控制复位,那么每次下载完fpga的sof后,都会对USB芯片执行一次复位操作,从而使芯片内烧写的固件丢失,那么用户只能再烧写一次usb 芯片固件,从而增加了调试时候的工作量)。

如下图,R64默认没有焊接,即断开了CYUSB 芯片与FPGA芯片的连接,从而避免受到FPGA固件的影响,如果产品最终定型需要测试使用FPGA直接控制USB芯片复位,给R64安装100R左右的电阻即可。

时钟晶振CYUSB3014支持外部晶振提供时钟信号,支持19.2、26、38.4和52MHz的时钟频率,AC6102开发板上使用19.2MHz的晶振为CYUSB3014提供时钟源。

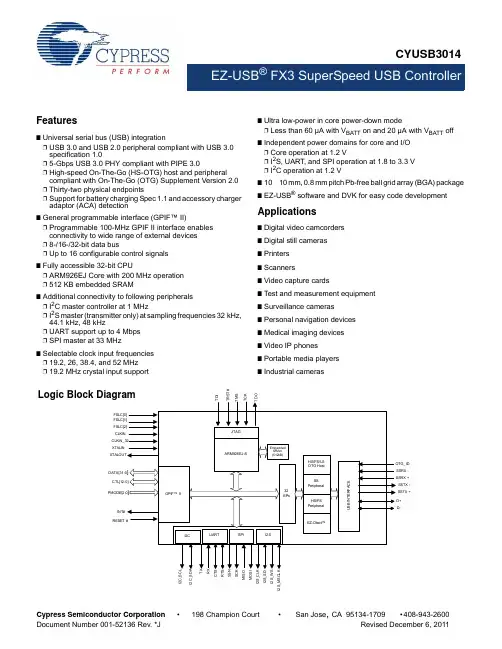

特性n通用串行总线 (USB) 集成p符合 USB 3.0 规范 1.0 版的 USB 3.0 和 USB 2.0 外设p符合 PIPE 3.0 的 5-Gbps USB 3.0 PHYp符合移动 (OTG) 补充标准 2.0 版的高速移动 (HS-OTG) 主机和外设p32 个物理端点p支持电池充电规范 1.1 版和辅助充电器适配器 (ACA) 检测n通用可编程接口 (GPIF™ II)p可编程的 100-MHz GPIF II 接口能连接多种类型外部器件p8/16/32 位数据总线p多达 16 种可配置的控制信号n无障碍访问 32 位 CPUp运行频率为 200MHz 的 ARM926EJ 内核p512 KB 嵌入式 SRAMn还可连接下列外设p频率为 1 MHz 的 I2C 主控制器p采样频率为 32kHz、44.1kHz、48kHz 的 I2S 主控(仅发射器)p支持高达 4 Mbps 的 UARTp33MHz 的 SPI 主控n多种时钟输入频率可供选择p19.2、26、38.4 和 52 MHzp支持 19.2 MHz 晶振输入n内核断电模式下功耗超低p开启 V BATT 时低于 60 µA,关闭 V BATT 时低于 20 µA n内核和 I/O 各有独立电域p内核工作电压为 1.2Vp I2S、UART 和 SPI 的工作电压为 1.8 至 3.3Vp I2C 工作电压为 1.2Vn10 × 10 mm,0.8 mm 间距无铅球栅阵列 (BGA) 封装n EZ-USB® 软件和 DVK,可轻松进行代码开发应用n数字视频摄录机n数字照相机n打印机n扫描仪n视频采集卡n测试和测量设备n监控摄像机n个人导航设备n医疗成像设备n视频 IP 电话n便携式媒体播放器n工业摄像头逻辑框图目录功能概述 (3)应用示例 (3)USB 接口 (4)OTG (4)ReNumeration (5)EZ-Dtect (5)VBUS 过电压保护 (5)Carkit UART 模式 (5)GPIF II (6)CPU (6)JTAG 接口 (7)其他接口 (7)UART 接口 (7)I2C 接口 (7)I2S 接口 (7)SPI 接口 (7)引导选项 (7)复位 (8)硬复位 (8)软复位 (8)时钟 (8)32-kHz 看门狗定时器时钟输入 (8)功耗 (9)功耗模式 (9)配置选项 (12)数字 I/O (12)通用 I/O (12)系统电平 ESD...................................... 12绝对最大额定值 (13)运行条件 (13)交流电时序参数 (15)GPIF II 时序 (15)从器件 FIFO 接口 (18)同步从器件 FIFO 序列说明 (19)同步从器件 FIFO 写序列说明 (21)异步从器件 FIFO 读序列说明 (22)异步从器件 FIFO 写序列说明 (24)串行外设时序 (25)复位序列 (29)引脚说明 (31)封装图 (34)订购信息 (34)订购代码定义 (34)缩略语 (35)文档规范 (35)测量单位 (35)文档修订记录页 (36)销售、解决方案和法律信息 (37)全球销售和设计支持 (37)产品 (37)PSoC 解决方案 (37)功能概述赛普拉斯 EZ-USB FX3 是新一代 USB3.0 外设控制器,具有高度集成的灵活特性,可帮助开发人员为任何系统添加 USB 3.0 功能。

基于CYUSB3014 USB3.0总线开发技术

(Universal Serial Bus,通用串行)以其无需配置、即插即用等特性获得了广泛的应用。

2004年提出的USB2.0标准,传输速度最大能够达到480Mbps。

但在 USB3.0标准中,它的最大传输速度几乎是传统USB2.0传输速度的10倍,达到了5.0Gbps,被定义为“超高速USB接口”。

本文基于CYPRESS的FX3系列USB3.0芯片,对USB3.0总线举行讨论开发。

B

3.0接口芯片概述

的EZ-USB FX3是新一代的USB3.0外设控制器,具有高度集成的灵便特性,允许系统设计者将USB3.0添加至任何系统。

本文采纳的是FX3系列USB3.0芯片CYUSB3014 FX3是彻低兼容USB3.0 V1.0和USB2.0规范的,集成的USB2.0 OTG控制器允许芯片作为主从设备用法。

另外,它还支持一些常用的外设接口,如SPI,I2C,UART和I2S可以与外部设备举行通信。

FX3具有一个可举行彻低配置的并行通用可编程接口GPIF II,它可以与任何处理器、ASIC或是衔接。

它可以轻松无缝地衔接至多种常用接口,比如异步SRAM、异步和同步地址数据复用式接口、并行 ATA等等。

EZ-USB FX3集成了USB3.0和USB2.0物理层(PHY)以及32位926EJ-S 微处理器,具有强大的数据处理能力,并可用于构建定制应用。

3.系统整体设计

第1页共6页。

CYUSB3014原理图注意,USB3.0连接器规格,插座封装CYUSB3014的官方原理图中我们会发现USB3.0 插座的RX- RX+分别接到了CYUSB3014的RX+ 和RX-,咋一看好象不太对。

其实是正确的,CYUSB3014内部会自动判断自适应正负,所以为了LAYOUT方便,正负互换都没关系。

USB3.0连接器引脚、接口定义及封装尺寸USB 3.0中定义的连接器包括(本文不包含连接线缆):USB 3.0 A型插头和插座USB 3.0 B型插头和插座USB 3.0 Powered-B型插头和插座USB 3.0 Micro-B型插头和插座USB 3.0 Micro-A型插头USB 3.0 Micro-AB型插座1、USB 3.0 A型USB插头(plug)和插座(receptacle)引脚顺序(左侧为Plug,右侧为Receptacle):引脚定义:封装尺寸(单PIN Receptacle):2、USB 3.0 B型USB插头(plug)和插座(receptacle)引脚顺序(左侧为Plug,右侧为Receptacle,注意箭头所指斜口向上,USB端口朝向自己):引脚定义:封装尺寸(单PIN Receptacle):3、USB 3.0 Powered-B型USB插头(plug)和插座(receptacle)引脚顺序(左侧为Plug,右侧为Receptacle,注意宽边在上,USB端口朝向自己):引脚定义:封装尺寸(Receptacle):4、USB 3.0 Micro USB插头和插座USB 3.0 Micro USB插头和插座变化相当大,而官方的协议文档中,涉及该部分的插图仍然存在模糊情况,这里不再抓图,前面文章介绍过Micro USB接口主要是用于蜂窝电话和便携设备的,体积相比Mini-USB更小。

Micro USB插头和插座分为三种:USB 3.0 Micro-B型插头和插座USB 3.0 Micro-A型插头USB 3.0 Micro-AB型插座USB 3.0 Micro-B连接器引脚定义:USB 3.0 Micro-AB/-A连接器引脚定义如下:分享:。

第33卷㊀第1期2018年1月㊀㊀㊀㊀㊀㊀㊀液晶与显示㊀㊀㊀C h i n e s e J o u r n a l o fL i q u i dC r y s t a l s a n dD i s p l a ys ㊀㊀㊀㊀㊀V o l .33㊀N o .1㊀J a n .2018㊀㊀收稿日期:2017G07G18;修订日期:2017G09G26.㊀㊀基金项目:国家自然科学基金资助项目(N o .11603024)S u p p o r t e db y Na t i o n a lN a t u r a l S c i e n c eF o u n d a t i o no fC h i n a (N o .11603024)㊀㊀∗通信联系人,E Gm a i l :z h a o j y @c i o m p.a c .c n 文章编号:1007G2780(2018)01G0061G06基于F T 600的U S B 3.0接口设计陈㊀涛1,2,赵金宇1∗,贾建禄1(1.中国科学院长春光学精密机械与物理研究所,吉林长春130033;2.中国科学院大学,北京100049)摘要:为了简化相机调试系统,降低调试成本,设计了基于F T D I 公司的F T 600芯片的U S B 3.0接口.首先,对C a m e r a L i n k 接口相机调试的复杂性和U S B 3.0接口调试的优势做了简要介绍,接着,对整个接口的硬件电路设计过程进行了说明,根据相应的数据手册,完成了对F T 600芯片外围电路及控制芯片,现场可编程门阵列(F P G A )外围电路的设计.最后,用V e r i l o g 硬件描述语言(V e r i l o g H D L )对F P G A 内部完成编程,并通过F T D I 公司提供的上位机程序对所设计的接口进行了测试.测试结果表明,该U S B 3.0接口电路能够通过上位机软件对工作模式进行设置,并能以200M B /s 左右的速率对数据进行传输.能够满足相机调试时的需求,达到简化调试系统的目的.关㊀键㊀词:U S B 3.0;F P G A ;F T 600中图分类号:T N 911.73㊀㊀文献标识码:A㊀㊀d o i :10.3788/Y J Y X S 20183301.0061D e s i gno fU S B 3.0i n t e r f a c e b a s e d o nF T 600C H E N T a o 1,2,Z H A OJ i n Gyu 1∗,J I AJ i a n Gl u 1(1.C h a n g c h u nI n s t i t u t e o f O p t i c s ,F i n eM e c h a n i c s a n dP h ys i c s ,C h i n e s eA c a d e m y o f S c i e n c e s ,C h a n gc h u n 130033,C h i n a ;2.U n i v e r s i t y o f C h i n e s eA c ade m y of S c i e n c e s ,B e i j i ng 100049,C h i n a )A b s t r a c t :I no r d e r t o s i m p l i f y t h e s y s t e mf o r c a m e r a t e s t i n g an d r e d u c e t h e c o s t ,a nU S B 3.0i n t e r f a c e b a s e do nF T 600o f F T D I C o m p a n y i s d e s i g n e d .F i r s t ,a b r i e f i n t r o d u c t i o n o f t h e c o m p l e x i t y f o r t e s t i n gt h e c a m e r aw i t hC a m e r a l i n k i n t e r f a c e a n d t h e a d v a n t a g e f o r u s i n g US B 3.0i n t e r f a c e i s p r e s e n t e d .T h e n a n e x p l a n a t i o n f o r c i r c u i t d e s i g no f t h e i n t e r f a c e i s s h o w e d ,a n d a c c o r d i n g t o t h e d a t a s h e e t ,t h e c i r c u i t d e s i g no f t h eF T 600a n d t h eF P G Ai s a c c o m p l i s h e d .F i n a l l y ,t h eF P G Ai s p r o g r a mm e db y u s i n g t h e V e r i l o g H D La n d t h eU S B 3.0i n t e r f a c e i s t e s t e db y u s i n g t h e s o f t w a r e p r o v i d e db y t h eF T D I .E x pe r i Gm e n t a l r e s u l t s i n d i c a t et h a t t h ew o r k m o d eof t h e U S B 3.0i n t e r f a c ec a nb ec o n f ig u r e da c c o r d i n g to s o f t w a r e ,a n d t h e i n t e r f a c e c a n t r a n s f e r t h e d a t a a t 200M b y t e /s .I t c a n s a t i s f y t h e c a m e r a t e s t r e q u i r e Gm e n t s a n d s i m p l i f y t h e s y s t e mf o r t e s t i n g .K e y wo r d s :U S B 3.0;F P G A ;F T 600. All Rights Reserved.1㊀引㊀㊀言㊀㊀目前相机的主流接口为C a m e r aL i n k接口和U S B3.0接口,在C a m e r aL i n k相机的使用过程中,需要配备专业的图像采集卡㊁专业C a m e r aL i n k电缆和携带P C I E卡槽的P C.这导致相机调试系统变得复杂㊁体积庞大㊁成本高昂且相应的组件选择有限.而U S B3.0以其布线经济㊁安装简单㊁高达500M B/s的带宽㊁可支持热插拔㊁与更多计算平台之间存在兼容性等特点备受用户喜爱[1].通过调研,我们发现目前的U S B3.0接口的设计都是基于C Y P R E S S公司的C Y U S B3014芯片完成的,C Y U S B3014芯片由于内部集成了A R M9内核,虽然功能较为全面,但也造成了整体结构较为复杂,后期的开发难度高的缺点,同时C Y U S B3014芯片采用B G A封装,布线难度高,在P C B(P r i n t e dC i r c u i t B o a r d,印刷电路板)布线阶段会增加很多过孔,降低信号质量[2G4].本设计采用F T D I公司的F T600芯片作为U S B3.0与F I F O的桥接芯片,在性能上能够满足绝大部分应用场合的需求.且该芯片采用Q F NG56封装,在P C B布线阶段不会增加过孔数量,在保持信号质量的同时,能够显著降低布线难度.本文采用F T600芯片,以X i l i n x公司的V i r t e x5系列现场可编程门阵列(F i e l dGP r o g r a mm a b l eG a t eA r r a y, F P G A)作为主控芯片,实现了U S B3.0接口的设计.测试表明该设计具有良好的传输性能,同时该设计后续能够进行扩展,实现对C a m e r aL i n k 等接口的转换,达到简化相机调试系统的目的.2㊀硬件电路设计本系统采用X i l i n x公司的V i r t e x5系列F P G A作为主控芯片,对F T600芯片进行控制,实现与P C之间的通信.本系统的硬件电路主要分为F T600芯片外围电路设计和F P G A控制电路设计两部分.2.1㊀U S B3.0接口电路U S B3.0也被称为S u p e rGS p e e d U S B,是新一代 即插即用 通用串行总线规范,它以U S B 2 0的优势为基础,同时也纠正了其弱点[5].当使用B u l k端点传送方法时,U S B3.0可提供约400M B/s的有效可用带宽,大约是U S B2.0的10倍,是I E E E1394b(F i r e W i r eGb)带宽的5倍. U S B3.0还能够为所连接的设备提供更大的供电能力:900m A(U S B2.0为500m A),可实现在没有外接电源的情况下操作许多设备.同时,电源管理也得到了改善.U S B3.0允许设备从不同的待机模式转入挂起模式,从而节省大量能源.本设计中采用的U S B3.0接口控制芯片为F T D I(F u t u r eT e c h n o l o g y D e v i c e sI n t e r n a t i o n a l L t d)公司的F T600芯片.这款芯片是U S B3.0与F I F O的桥接芯片,内置16K bF I F O数据缓存R AM,兼容U S B3.0和U S B2 0接口,同时支持两种并行从F I F O总线通信协议: 多通道F I F O 总线协议和 245同步F I F O 总线协议,具有16位并行F I F O总线接口,能够满足绝大部分的应用需求.F T600芯片结构示意图如图1所示,整个U S B3.0接口电路原理图如图2所示[6].图1㊀F T600芯片结构示意图F i g.1㊀B l o c kd i a g r a mo fF T600图2㊀F T600外围电路原理图F i g.2㊀S c h e m a t i c o fF T6002.2㊀F P G A控制电路作为本系统的主控芯片,本设计中采用了26㊀㊀㊀㊀液晶与显示㊀㊀㊀㊀㊀㊀第33卷㊀. All Rights Reserved.X i l i n x公司的V i r t e x5系列的X C5V L X30T芯片,该芯片采用F F323封装,提供172个用户可编程I/O,共6个b a n k,完全满足系统需要[7].F PG A为其他芯片提供了数据缓存中转以及控制驱动信号,使得系统可以仅由F P G A及其配置芯片㊁U S B3.0控制芯片等几个主要芯片以及一些供电电路组成,极大地简化了板级电路设计.F PG A控制电路部分主要包括F P G A配置电路和电源电路.2.2.1㊀配置电路由于F P G A大多采用S R AM工艺,断电之后所有内部的数据都无法保存,如果每次上电都重新从电脑上烧写程序势必会带来很大的不便,因此需要为F P G A专门配备一个用来装载程序的非易失性存储器,以便在系统上电时能快速向F P G A导入配置比特流.本设计将X i l i n x公司的X C F16P与F P G A搭配使用,该芯片采用1.8V供电,最大可存储16M b i t程序,与F P G A之间可以实现高达33MH z的串行或并行配置[8G10].本设计采用最常用的主串模式和J T A G模式相结合,调试阶段通过J T A G在线配置F P G A,调试完成后以主串模式将配置比特流下载到X C F16P中,实现系统的脱机工作.2.2.2㊀电源电路F PG A芯片工作时需要提供内核电压V c c i n t㊁辅助电压V c c a u x以及输出驱动电压V c c o.具体到本设计所选的V i r t e xG5系列芯片,内核电压为+1.0V,辅助电压为+2.5V,V c c o则根据各b a n k所连接的电平标准而各不相同[11G12].由于U S B3.0接口芯片F T600内部集成了L D O1.0V稳压器,且该芯片I/O模块的供电电压支持+1.8/+2.5/+3.3V三种电平,为了方便,统一选取+3.3V 为V c c o和F T600芯片供电[6].另一方面,P R O M芯片X C F16P需要1.8V的供电电压.因此,还需要提供+1.8V电压,为X C F16P芯片进行供电.3㊀系统软件设计整个系统的数据传输过程如图3所示.P C端经过U S B3.0接口传入F I F O的数据存储在F I F OR X缓存区中,通过F P G A发送R D_N 命令,从缓存区中读出这些数据;通过F P G A发送WR_N命令写入F I F O的数据存储在F I FO图3㊀数据传输过程示意图F i g.3㊀B l o c kd i a g r a mo f d a t a t r a n s f e rT X缓存区中,P C端通过发送数据请求信号,从缓存区中读出数据.在245同步F I F O模式下, R XF I F O和T XF I F O的大小均为4K Bˑ2.在数据传输过程中,C L K信号是输出到F P G A控制器的并行F I F O时钟输出信号,其频率可以配置成66MH z或100MH z;R X F_N信号是接收F I F O满输出信号,该信号表示接收F I F O至少有1字节能够被读出,当该信号为0时,只能对F I F O进行读操作;同理,T X E_N信号是发送F I F O空输出信号,该信号表示发送F I F O至少还有1字节的空间能够被写入,当该信号为0时,只能对F I F O进行写操作.B E[1ʒ0]是并行F I F O 总线字节使能信号,高电平有效,信号O E_N引脚是数据输出使能信号,低电平有效.F PG A逻辑设计主要包括I/O控制模块㊁有限状态机模块㊁单口R AM控制模块.I/O控制模块实现外部端口与内部模块之间信号的连接,同时控制双向I O口,D A T A和B E 的方向;有限状态机模块控制F P G A内部S R AM (主F I F O)的所有操作,实现其与F T600芯片内部F I F O(从F I F O)的数据传输过程;F I F O控制模块控制内部F I F O的读写操作;8Kˑ16S R AM 为单端口S R AM,通过调用X i l i n xI S EI P核生成,大小为8K,读写的数据宽度都为16位.I/O控制模块主要实现外部端口与内部模块之间信号的连接,功能较为简单,在此不作详述.我们重点讨论有限状态机模块和S R AM模块的设计.3.1㊀有限状态机模块有限状态机模块主要实现S R AM读写状态的转换,其状态转换过程如图4所示.在状态转换过程中,R X F_N和T X E_N信号是从F I F O的输入信号,用来指示F T600芯片中从F I F O的状态,R X F_N信号是接收F I F O满输出信号,该信号表示接收F I F O至少有1字节能够被读出,当该信号为0时,只能对接收F I F O进行读操作;同理,T X E_N信号是发送F I F O空输36第1期㊀㊀㊀㊀㊀㊀㊀陈㊀涛,等:基于F T600的U S B3.0接口设计. All Rights Reserved.图4㊀有限状态机状态转换示意图F i g.4㊀B l o c kd i a g r a mo fF S M(F i n i t e s t a t em a c h i n e)出信号,该信号表示发送F I F O至少还有1字节的空间能够被写入,当该信号为0时,只能对发送F I F O进行写操作.B U F_F U L和B U F_E M P信号是F PG A内部S R AM的状态指示信号,当B U F_F U L信号为1时,表示内部S R AM满,同理,B U F_E M P为1时,表示内部S R MA状态为空.系统复位时,状态机处于I D L E状态,此时,若R X F_N信号为0,且B U F_F U L信号也为0时,F P G A将对F T600芯片的接收F I F O进行读操作,状态机转入M A S T E R_R D状态.在M A S T E R_R D状态下,倘若满足R X F_N为1,或B U F_F U L为1,状态机将转入M I D D L E状态,否则继续停留在MA S T E R_R D状态,继续对接收F I F O进行读操作;当状态机处于M I D D L E状态时,需要对T X E_N信号和B U F_E M P信号的状态进行判断,倘若T X E_N信号为0且B U F_E M P信号也为0时,状态机将进入MA S T E R_WR状态,对F T600芯片的发送F I F O进行写操作.否则状态机将跳转至I D L E状态;在MA S T E R_WR 状态下,将对T X E_N信号和B U F_E M P信号的状态进行检测,如果T X E_N为1或者B U F_E M P信号为1,则状态机的状态回到I D L E状态,否则保持在MA S T E R_WR状态,继续对发送F I F O进行写操作.3.2㊀单口R AM控制模块内嵌的块R AM是F P G A内部的重要资源,它使得F P G A的使用更加方便,应用更加广泛.本系统采用X i l i n xV i r t e x5系列的X C5V L X30TGF F G323芯片,内部有1296K b的块R AM容量,这些块R AM的访问速度快,不占用额外的逻辑资源.可利用F P G A开发工具通过配置实现单口或双口R AM㊁R OM㊁F I F O等.本系统采用单口R AM.根据系统的需要,单口R AM读写的数据宽度都设为16位,深度为8192,大小为16K B.利用单口R AM可以实现数据在F P G A内部的缓存,方便外部设备通过U S B3.0接口与P C进行数据交换.4㊀测试过程利用X i l i n x公司的I S E集成开发环境,对编写的F P G A控制代码进行综合㊁实现之后,我们能够生成比特流文件,利用I S E自带的i M P A C T 调试工具,通过J T A G接口,将比特流文件烧入F P G A,完成对F P G A的编程工作[13].通过U S B3.0连接线将电路与P C相连,通过F T D I公司的F T60X C h i p C o n f i g u r a t i o n P r aGg r a mm e r软件对F T600芯片进行配置.图5是对F T600芯片进行配置的图片,图中可以看出,能够对芯片的F I F O时钟㊁通道数量以及工作模式进行设置,以使其满足不同的传输需求.本设计中设置F I F O时钟为100MH z,工作模式为245模式,通道数量为1[14].图5㊀芯片配置示意图F i g.5㊀B l o c kd i a g r a mo f c o n f i g u r a t i o no fF T600在完成对芯片的配置之后,通过F T D I公司提供的上位机程序示例,对所设计的电路性能进行了测试[15].图6是进行压力测试的结果.从图中可以看出,将需要传输的字节长度设为随机值,系统能够有效地完成这些随机长度的数据的发送和接收任务.并且由于每个时钟周46㊀㊀㊀㊀液晶与显示㊀㊀㊀㊀㊀㊀第33卷㊀. All Rights Reserved.图6㊀压力测试结果图F i g.6㊀R e s u l t o f s t r e s s t e s t 期,传输的数据位数为16位,即2B y t e ,数据传输时钟频率为100MH z ,因此能够计算出系统的数据传输速度约为200M B /s ,能够满足大多数场合的数据传输任务.5㊀结㊀论测试表明,基于F T 600芯片所设计的U S B 3 0接口电路能够按照需求进行相应的配置,并能以200M B /s 左右的速度对数据进行传输,能够满足大多数场合的数据传输任务.同时F P G A 芯片具有高灵活性㊁快速的定制性㊁较强的通用性和扩展性,有利于后续进行相应的功能扩展,在需要时能够完成对其他接口,如C a m e r aL i n k 等的转换,使其转换为更加通用常见的U S B 3.0接口,达到简化调试系统的目的.参㊀考㊀文㊀献:[1]㊀D o m i n i kL a p p e n k üpe r .U S B3.0可以替代C a m e r aL i n k G转换相机接口的主要因素[E B /O L ].(2016G12)[2017G06G05].h t t p s ://w w w.b a s l e r w e b .c o m /c n /s u p p o r t /d o w n l o a d s /d o c u m e n t Gd o w n l o a d s /w h i t e Gp a p e r Gu s b 3G0Gi n s t e a d Gof Gc a m Ge r a Gl i n k/.D o m i n i kL a p p e n k üp e r .U S B3.0a s a n a l t e r n a t i v e t o c a m e r a l i n k Gk e y f a c t o r sw h e n s w i t c h i n g ca m e r a i n t e r f a c e s [E B /O L ].(2016G12)[2017G06G05].h t t p s ://w w w.b a s l e r w e b .c o m /c n /s u p po r t /d o w n l o a d s /d o c u m e n t Gd o w n l o a d s /w h i t e Gp a pe r Gu s b 3G0Gi n s t e a d Gof Gc a m e r a Gl i n k /.(i nC h i n e s e )[2]㊀赵慧洁,刘小康,张颖.声光可调谐滤波成像光谱仪的C C D 成像电子学系统[J ].光学精密工程,2013,21(5):1291G1296.Z HA O HJ ,L I U XK ,Z HA N GY.C C D i m a g i n g e l e c t r i c a l s y s t e mo fA O T F i m a g i n g s p e c t r o m e t e r [J ].O pt i c s a n d P r e c i s i o nE n g i n e e r i n g ,2013,21(5):1291G1296.(i nC h i n e s e )[3]㊀贾建禄,王建立,郭爽,等.基于C a m e r aL i n k 的高速图像采集处理器[J ].液晶与显示,2010,25(6):914G918.J I AJL ,WA N GJL ,G U OS ,e t a l .H i g hs p e e d i m a ge g r a b b e r a n d p r o c e s s o rb a s e do nc a m e r a l i n k [J ].C h i n e s e J o u r n a l of L i q u i dC r y s t a l s a n dD i s p l a ys ,2010,25(6):914G918.(i nC h i n e s e )[4]㊀余达,郭永飞,周怀得,等.面阵C C D K A I G0340D M 高速相机的设计[J ].光学精密工程,2011,19(11):2791G2799.Y U D ,G U O YF ,Z HO U H D ,e t a l .D e s i g no f h i g h s p e e d c a m e r a s y s t e m w i t h a r e a GC C DK A I G0340D M [J ].O pGt i c s a n dP r e c i s i o nE n g i n e e r i n g ,2011,19(11):2791G2799.(i nC h i n e s e )[5]㊀韩力,王世赞,王军,等.多传感器动态参数实时采集与存储方法研究[J ].液晶与显示,2017,32(5):372G379.HA NL ,WA N GSZ ,WA N GJ ,e t a l .R e a l Gt i m e c o l l e c t i o na n ds t o r a g eo fm u l t i Gs e n s o rd yn a m i c p a r a m e t e r s [J ].C h i n e s eJ o u r n a l o f L i q u i dC r y s t a l s a n dD i s p l a ys ,2017,32(5):372G379.(i nC h i n e s e )[6]㊀F T D I .D S _F T 600Q GF T 601QI CD a t a s h e e t (V e r s i o n1.04)[E B /O L ].(2016G10G17)[2017G06G05].h t t p ://w w w.f t Gd i c h i p .c o m /S u p p o r t /D o c u m e n t s /D a t a S h e e t s /I C s /D S _F T 600Q GF T 601Q%20I C %20D a t a s h e e t .pd f .[7]㊀X i l i n x .D S 100GV i r te x G5f a m i l y o v e r v i e w (v e r5.1)[E B /O L ].(2015G08G21)[2017G06G05].h t t p s ://w w w.x i l i n x .c o m /s u p p o r t /d o c u m e n t a t i o n /d a t a _s h e e t s /d s 100.pd f .[8]㊀X i l i n x .U G 191GV i r te x G5F P G Ac o nf ig u r a t i o nu s e r g u i d e (v e r 3.12)[E B /O L ].(2017G05G08)[2017G06G05].h t t p s ://w w w.xi l i n x .c o m /s u p p o r t /d o c u m e n t a t i o n /u s e r _g u i d e s /u g 191.p d f .[9]㊀X i l i n x .U G 161GP l a t f o r mf l a s hP r o m U s e rG u i d e (V e r 1.5)[E B /O L ].(2009G10G26)[2017G06G05].h t t ps ://w w w.56第1期㊀㊀㊀㊀㊀㊀㊀陈㊀涛,等:基于F T 600的U S B 3.0接口设计. All Rights Reserved.66㊀㊀㊀㊀液晶与显示㊀㊀㊀㊀㊀㊀第33卷㊀x i l i n x.c o m/s u p p o r t/d o c u m e n t a t i o n/u s e r_g u i d e s/u g161.p d f.[10]㊀X i l i n x.D S123GP l a t f o r m f l a s hi nGs y s t e m p r o g r a mm a b l ec o n f i g u r a t i o n P R OM sd a t as h e e t(v e r2.19)[E B/O L].(2016G06G06)[2017G06G05].h t t p s://w w w.x i l i n x.c o m/s u p p o r t/d o c u m e n t a t i o n/d a t a_s h e e t s/d s123.p d f.[11]㊀X i l i n x.D S202GV i r t e xG5F P G A d a t as h e e t:D Ca n ds w i t c h i n g c h a r a c t e r i s t i c s(v e r5.5)[E B/O L].(2016G06G17) [2017G06G05].h t t p s://w w w.x i l i n x.c o m/s u p p o r t/d o c u m e n t a t i o n/d a t a_s h e e t s/d s202.p d f.[12]㊀X i l i n x.U G195GV i r t e xG5F P G A p a c k a g i n g a n d p i n o u t s p e c i f i c a t i o n(v e r4.8.1)[E B/O L].(2012G06G14)[2017G06G05].h t t p s://w w w.x i l i n x.c o m/s u p p o r t/d o c u m e n t a t i o n/u s e r_g u i d e s/u g195.p d f.[13]㊀X i l i n x.A N_376X i l i n xF P G AF I F O m a s t e r p r o g r a mm i n gg u i d e(V e r s i o n1.0)[E B/O L].(2015G09G03)[2017G06G05].h t t p://w w w.f t d i c h i p.c o m/S u p p o r t/D o c u m e n t s/A p p N o t e s/A N_376%20X i l i n x%20F P G A%20F I F O%20m a s t e r%20P r o g r a mm i n g%20G u i d e.p d f.[14]㊀F T D I.A N_370F T600c o n f i g u r a t i o n p r o g r a mm e r u s e r g u i d e(V e r s i o n1.3)[E B/O L].(2016G07G07)[2017G06G05].h t t p://w w w.f t d i c h i p.c o m/S u p p o r t/D o c u m e n t s/A p p N o t e s/A N_370%20F T600%20C o n f i g u r a t i o n%20P r o g r a mm e r%20U s e r%20G u i d e.p d f.[15]㊀F T D I.A N_375F T600d a t a l o o p b a c ka p p l i c a t i o nu s e r g u i d e(V e r s i o n1.0)[E B/O L].(2015G09G03)[2017G06G05].h t t p://w w w.f t d i c h i p.c o m/S u p p o r t/D o c u m e n t s/A p p N o t e s/A N_375%20F T600%20D a t a%20L o o p b a c k%20A p p l i c a t i o n%20U s e r%20G u i d e.p d f.作者简介:陈涛(1993-),男,重庆荣昌人,硕士研究生,2015年于吉林大学获得学士学位,主要从事F P G A的硬件开发与设计.EGm a i l:c h e n t a o19930107@163.c o m赵金宇(1976-),男,内蒙通辽人,研究员,2006年于中科院长春光学精密机械与物理研究所获得博士学位,主要从事地基大口径光电设备研制和空间目标探测领域技术研究.EGm a i l:z h a o j y@c i o m p.a c.c n. All Rights Reserved.。