Qsys系统设计指南

- 格式:docx

- 大小:23.17 KB

- 文档页数:27

1.系统设计特点及概述鉴于该系统设计包括多个专业扩声系统,为了达到系统整合的目的,同时又要保证系统稳定性和先进性,这里我们选用QSC公司最新推出的大型网络音频矩阵Q—sys系统为整套系统的核心。

由于Q-Sys系统具有极大的音频处理能力以及通道处理能力,实现Q-Sys 网络音频处理系统最大利用率,达到资源配置最优化.1.Q—Sys系统介绍Q—Sys系统是美国QSC公司最新研制推出的一套大型网络音频矩阵处理系统。

该系统重新诠释了网络音频系统,具有:非凡的音频处理能力、超强的系统整合能力、磐石般的系统稳定性、简单易懂的可操作性。

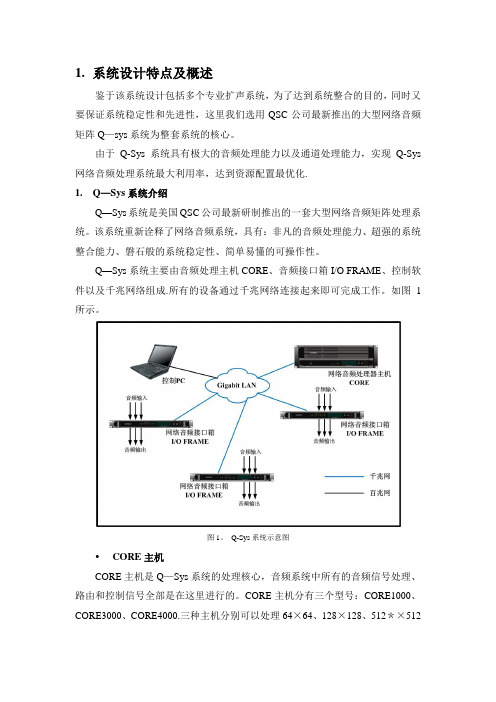

Q—Sys系统主要由音频处理主机CORE、音频接口箱I/O FRAME、控制软件以及千兆网络组成.所有的设备通过千兆网络连接起来即可完成工作。

如图1所示。

图1。

Q-Sys系统示意图CORE主机CORE主机是Q—Sys系统的处理核心,音频系统中所有的音频信号处理、路由和控制信号全部是在这里进行的。

CORE主机分有三个型号:CORE1000、CORE3000、CORE4000.三种主机分别可以处理64×64、128×128、512*×512*个音频通道,是当今世界上处理能力最强的音频处理主机。

CORE 主机摒弃了传统音频处理主机采用DSP 芯片进行音频信号处理的老方式,而采用全新的音频处理核心-多核64位中央处理单元进行音频信号处理。

采用这种全新的处理引擎后,CORE主机的信号处理能力远远大于传统采用DSP 芯片作为处理核心的音频处理主机。

对比此前处理能力最强的PEA VEY 的NION N6型音频处理主机,最小型的音频处理主机—CORE1000的音频处理能力是NION N6的五倍。

CORE 主机内部内置了多种音频处理模块,如:分频器、混音器、自动混音台、噪声门、路由器、动态处理器、噪声发生器、参量/图示均衡器、动态显示器、音频文件播放器、RTA 测试工具等等,能够满足各类场所音频系统的需要。

控制系统设计指南英文原版Control systems play a crucial role in various industries, from manufacturing to aerospace. Good control system design is essential for ensuring the stability, performance, and safety of these systems.控制系统在各个行业中起着至关重要的作用,从制造业到航空航天业。

良好的控制系统设计对于确保这些系统的稳定性、性能和安全性至关重要。

One aspect of control system design is the selection of appropriate control algorithms. Different systems require different control algorithms, and it is important to choose the one that best fits the specific requirements and constraints of the system.控制系统设计的一个方面是选择适当的控制算法。

不同的系统需要不同的控制算法,选择最适合系统特定要求和约束条件的算法至关重要。

Another important consideration in control system design is the identification of system dynamics. Understanding the dynamics of the system is crucial for designing an effective control system that can accurately predict and respond to changes in the system.控制系统设计中另一个重要的考虑因素是系统动态的识别。

Qsys 系统设计指南Ch1. 绪论软硬件需求概述下载、安装设计实例打开实例工程Ch2.建立Qsys系统建立数据模式发生器( Data Pattern Generator )建立新的带有时钟源的Qsys 系统加入管道桥( Pipeline Bridge ) 加入定制模式发生器( Custom PatternGenerator )加入PRBS莫式发生器加入2-1 流复用器( Two-to-One Streaming Multiplexer ) 校验存储器地址映射( Memory Address Map) 连接复位信号( Reset Signals )和插入适配器( Adapters )建立数据莫式校验器( Data Pattern Checker ) 建立新的Qsys 系统并设置时钟源加入管道桥( Pipeline Bridge )加入1-2 流解复用器( One-to-Two Streaming Demultiplexer ) 加入定制模式校验器( Custom Pattern C )加入PRB S莫式校验器校验存储器地址映射( Memory Address Map) 连接复位信号Ch3. 装配层级系统( Assembling Hierarchical Systems )建立层级存储器检测器( Hierarchical Memory Tester ) 加入数据莫式发生器( Data pattern Generator ) 加入莫式校验器( Data pattern Checker ) 加入存储器主元件( Memory Master Components) 连接复位信号指定存储器地址映射( Memory Address Map)完成顶层系统( Top-Level System )编译并下载软件到开发板Ch.4 在系统控制台( System Console )验证硬件理解脚本( Understanding the Scripts )打开实例工程( Tutorial Project )加入JTAG-to-Avalon 主桥( Master Bridge ) 编译并使用系统控制台控制开发板Ch5. 仿真定制元件( Custom Components)在Qsys 中产生Testbench 系统打开实例工程( Tutorial Project )为设计测试( Design Under Test )建立一个新的Qsys 系统导出所有设计测试接口( Design Under Test Interfaces ) 产生一个Qsys Testbench 系统产生Qsys Testbench 系统仿真模型在ModelSim-Altera 软件中执行仿真设置仿真环境执行仿真附加信息文档版本历史如何联系AlteraChi.绪论本指南介绍可在Quartusll软件中使用的Qsys系统集成工具。

qsys工具的使用方法qsys工具是一款用于嵌入式系统设计的软件工具,它提供了一种图形化的方式来设计和配置系统,使得硬件和软件之间的协同开发更加方便和高效。

本文将介绍qsys工具的使用方法,包括系统的创建、组件的添加和连接、以及系统的生成和验证等步骤。

一、系统的创建在使用qsys工具之前,首先需要创建一个新的系统。

打开qsys工具后,点击菜单栏中的"File",选择"New",然后选择"Empty System"。

在弹出的对话框中,可以设置系统的名称和保存路径等信息。

点击"OK"按钮后,qsys工具将创建一个空的系统,准备接下来的设计工作。

二、组件的添加在qsys工具中,系统是由各种不同的组件组成的。

组件可以是处理器、外设、存储器等。

要添加一个组件,可以点击工具栏中的"Library"按钮,然后选择需要的组件。

在弹出的组件库中,可以浏览和搜索各种不同的组件。

选择一个组件后,可以将其拖拽到系统设计窗口中。

三、组件的连接在将组件添加到系统中之后,需要对组件进行连接,以建立各个组件之间的通信和数据传输。

在qsys工具中,可以使用线条来连接组件。

要添加一个连接线,可以点击工具栏中的"Wire"按钮,然后在系统设计窗口中按住鼠标左键拖拽,连接两个组件。

可以根据需要添加多条连接线,以实现不同组件之间的数据传输。

四、系统的生成在完成系统的设计和连接之后,可以生成系统的代码和配置文件。

点击菜单栏中的"Generate",选择"Generate HDL",qsys工具将根据系统设计生成相应的硬件描述语言代码。

在生成过程中,可以选择输出的目标平台和相关参数。

生成完成后,可以在指定的输出路径中找到生成的代码文件。

五、系统的验证在生成系统代码之后,可以使用相应的仿真工具对系统进行验证。

QII51024-13.0.0© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified astrademarks or service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of itssemiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products andservices at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or servicedescribed herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relyingon any published information and before placing orders for products or services.Quartus II 13.0手册卷1:设计与综合2013年5月ISO 9001:2008 Registered 反馈订阅Twitter10.优化Qsys 系统性能本章节对Altera ® Qsys 系统集成工具生成的设计提供了优化系统互联性能的信息。

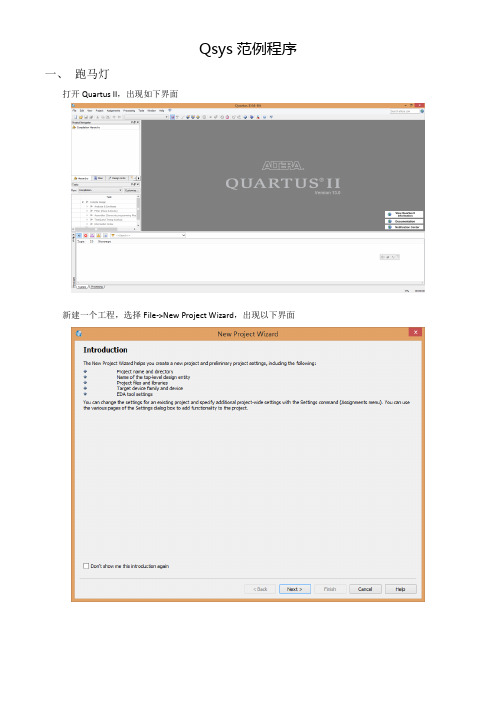

Qsys范例程序一、跑马灯打开Quartus II,出现如下界面新建一个工程,选择File->New Project Wizard,出现以下界面选择Next > ,出现以下对话框给新工程命名并选择工程目录,本例使用RunningLED作为工程名。

点击两次Next >,出现如下对话框在Family中选择Cyclone II,Available devices中选择EP2C35F672C6,为我们使用的FPGA芯片型号。

然后点击Finish,至此就建立好了新工程。

再点击Quartus II软件右上方工具栏的,打开Qsys程序。

本例将建立一个包含CPU核、8kB片上RAM、一个定时器和8个IO口的最小片上系统以演示跑马灯程序。

Qsys 启动后界面如下:首先在系统中添加片上RAM。

在程序左侧列表中选择Memory and Memory Controllers -> On-Chip -> On-Chip Memory (RAM or ROM),双击添加至系统中。

在弹出的对话框中指定片上RAM的属性。

设置内存大小为8192Byte。

再添加CPU。

双击Embedded Processors-> Nios II Processor,在弹出的对话框中间选择第一个Nios II/e,表示economy,最小的NIOS II核心。

其它的都保留默认设置即可。

点击Finish添加CPU核。

添加定时器。

在列表中选择Peripherals -> Microcontroller Peripherals -> Interval Timer,弹出如下对话框。

定时器在本系统中主要作用是产生一个固定间隔的中断信号,让CPU改变LED灯的状态。

因此在Period中选择500ms,表示灯的状态每500ms改变一次。

在右侧Library中双击Simple periodic interrupt。

Altera 公司 2011年5月322.0Subscribe© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html . Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.101 Innovation DriveSan Jose, CA 95134 从SPOC Builder 到Qsys 的移植指南本应用笔记介绍了如何将您的设计从SOPC Builder 移植到Qsys 的指南以及涉及到的其它相关问题。

[FPGA]基于Qsys的第一个Nios II系统设计一、基本说明1、软件平台:Quartus II 13.0(64-bit)Nios II 13.0 Software Build Tools for Eclipse2、硬件平台:Altera Cyclone II EP2C8Q208C8N二、设计目标完成FPGA平台上的“Hello Word”实现,实现方式:基于Qsys的Nios II系统设计。

三、具体步骤1、打开Quartus II 13.0(64-bit),新建一个工程,File -> New Project Wizard…,忽略Introduction,之间单击Next> 进入下一步。

分别设置工程工作目录、工程名称。

这里需要注意的是工程工作目录中请使用英文,不要含有空格等,否则在后面使用Nios II IDE的时候会出现问题。

设置好后如图1所示。

然后进行下一步。

图 1 设置工程工作目录、工程名称2、添加已经存在的文件,这里我们没有需要添加的文件,直接单击Next> 进入下一步。

进行器件设置。

我们使用的Cyclone II 家族的EP2C8Q208C8 芯片,选择好后直接进入下一步。

进行EDA工具设置,由于我们工程中不进行仿真等,故不进行设置,如果需要进行ModelSim仿真,则在Simulation行中,选择Tool Name 为ModelSim-Altera(这里根据所安装的ModelSim版本进行选择),Format(s)选择为Verilog HDL(这里也是根据所掌握的硬件描述语言进行选择)。

点击Next> ,进入了Summary(摘要)页面,然后单击Finish 完成即可。

3、新建Block Diagram/Schematic File (方块图/原理图文件)。

单击File -> New..,选择Design Files 中的Block Diagram/Schematic File,单击OK即可。

Qsys系统设计指南Ch1. 绪论软硬件需求概述下载、安装设计实例打开实例工程Ch2. 建立Qsys系统建立数据模式发生器(Data Pattern Generator)建立新的带有时钟源的Qsys系统加入管道桥(Pipeline Bridge)加入定制模式发生器(Custom Pattern Generator)加入PRBS模式发生器加入2-1流复用器(Two-to-One Streaming Multiplexer)校验存储器地址映射(Memory Address Map)连接复位信号(Reset Signals)和插入适配器(Adapters)建立数据模式校验器(Data Pattern Checker)建立新的Qsys系统并设置时钟源加入管道桥(Pipeline Bridge)加入1-2流解复用器(One-to-Two Streaming Demultiplexer)加入定制模式校验器(Custom Pattern C)加入PRBS模式校验器校验存储器地址映射(Memory Address Map)连接复位信号Ch3. 装配层级系统(Assembling Hierarchical Systems)建立层级存储器检测器(Hierarchical Memory Tester)加入数据模式发生器(Data Pattern Generator)加入模式校验器(Data Pattern Checker)加入存储器主元件(Memory Master Components)连接复位信号指定存储器地址映射(Memory Address Map)完成顶层系统(Top-Level System)编译并下载软件到开发板Ch.4 在系统控制台(System Console)验证硬件理解脚本(Understanding the Scripts)打开实例工程(Tutorial Project)加入JTAG-to-Avalon主桥(Master Bridge)编译并使用系统控制台控制开发板Ch5. 仿真定制元件(Custom Components)在Qsys中产生Testbench系统打开实例工程(Tutorial Project)为设计测试(Design Under Test)建立一个新的Qsys系统导出所有设计测试接口(Design Under Test Interfaces)产生一个Qsys Testbench系统产生Qsys Testbench系统仿真模型在ModelSim-Altera软件中执行仿真设置仿真环境执行仿真附加信息文档版本历史如何联系AlteraCh1. 绪论本指南介绍可在QuartusII软件中使用的Qsys系统集成工具。

本指南介绍了如何设计一个使用不同的测试模式来测试一个外部存储器件的系统。

通过系统需求分析,硬件设计任务,以及系统性能分析,重点在于构架系统。

在理解Qsys 开发流程的基础上,可以进一步设计自己的Qsys系统。

1.1 软硬件需求本指南需要下面的软件支持:Altera QuartusII V11.0以上软件系统需求及安装指令请参考Altera Software Installation andLicensingNios II EDS V11.0以上Tt_qsys_design.zip设计实例文件,可以从Qsys Tutorial DesignExample 网站下载。

该设计实例文件包括可设置选择Altera开发板的工程文件。

如果满足下面的要求,可以根据本指南建立任何Altera开发板或自定制板的Qsys系统。

板上必须包括Altera的Arria、Cyclone或Stratix系列FPGA。

FPGA必须包括至少12K逻辑单元(LEs)或自适应查找表(ALUTs)。

FPGA必须包括至少150Kb嵌入式存储器。

板上必须有JTAG接口,用于主机监控板上FPGA内部存储器程序执行。

板上必须包括用于设计测试的存储器。

例如,任意具有Avalon-MM从接口的基于Qsys控制器的存储器。

为了在开发板上完成本指南,请参考开发板文档中对时钟频率和引脚描述。

对于Altera开发板,可以在相关参考手册中找到对应信息。

1.2 概述本指南中建立的Qsys系统用来测试一个同步动态随机存储器(SDRAM)。

最终的系统在层级子系统中包括SDRAM控制器,一个NiosII处理器和一些嵌入式外设。

通过添加不同的Qsys元件来产生测试数据,访问存储器以及验证返回数据,从而完成Qsys系统。

最终系统包括下面的元件:基于Nios II/e的处理器子系统(包含在Altera完整的设计套件中)SDRAM控制器(包含在Altera完整的设计套件中)伪随机二进制序列(Pseudo-random binary sequence,PRBS)模式发生器和校验器定制模式发生器和校验器模式选择复用器(Multiplexer)和解复用器(Demultiplexer)模式读写器(Pattern writer and reader)存储器测试控制器无需license即可在硬件中应用本最终系统。

通过Altera免费的OpenCore Plus评估特性,可以进一步完成下面的工作:仿真系统行为以及验证其功能产生时限的器件编程文件器件编程并进行硬件验证设计实例文件包含了在任何设计中均可免费使用的元件。

Nios II/e处理器核和DDR SDRAM IP核可以免费在Quartus II订购license中使用。

为了匹配开发板上的存储器,设计文件对于不同的开发板使用不同的DDR SDRAM控制器。

关于OpenCore Plus更多信息,请参考AN320:OpenCore Plus Evaluationof Megafunctions.图1-1给出了设计实例完整的顶层系统。

图1-1给出了作为一个Qsys系统,在存储器测试器系统中的元件,具有三个主要设计功能,如图中虚线框内所示。

本指南采用层级结构表示——将数据模式发生器和数据模式校验器分别例化为两个独立系统,然后包含在存储器检测器(Memory Tester)系统中。

在一个高层系统中,层次表示可以例示某个系统作为一个元件。

图1-1 顶层系统结构1.2.1 下载、安装设计实例按照下面的步骤下载并安装本指南设计实例:(1)从Qsys Tutorial Design Example网站下载Qsys Tutorial Design Example(.zip)文件;(2)解压缩文件中所有内容到某个目录中,注意在目录路径名种不要使用空格。

1.2.2 打开实例工程本指南设计实例文件提供必需的定制IP设计模块和工程文件用于开始工作,并包括部分完成的QuartusII工程和Qsys系统。

设计实例文件包括下面全部工程:QuartusII工程I/O引脚分配,指定的Synopsys设计约束(.sdc)时序分配。

参数化的Nios II处理器核,可与主PC机通讯来控制存储器测试系统。

参数化的DDR SDRAM控制器,用于开发板上的存储器。

按照下面的步骤打开实例工程:(1)打开Quartus II软件。

(2)对应所用的开发板,打开Quartus II工程文件(.qpf):a. 在File菜单中,点击Open Project。

b. 浏览目录“tt_qsys_design\quartus_ii_projects_for_boards\<development_board>\”目录。

c. 选择相关开发板.qpf文件,点击Open。

设计中的定制存储器测试元件是Verilog HDL元件,随同硬件元件描述文件(_hw.tcl)描述了每个元件的接口和参数。

这些文件在tt_qsys_design\memory_tester_ip目录中。

在Qsys中查看这些元件,在Component Libray标签上展开Memory Test Microcores,如下图中红色圆圈所示。

一个IP索引(.ipx)文件为包含这些存储器测试元件的memory_tester_ip 目录提供了参考。

图展开Memory Test MicrocoresCh2. 建立Qsys系统本章介绍如何例化(Instantiate)、参数化(Parameterize)以及连接元件到新建的Qsys系统。

本章建立如图1-1所示的Qsys系统,包括下列设计模块:数据模式发生器(Data Pattern Generator)数据模式校验器(Data Pattern Checker)如果已经熟悉创建Qsys系统的过程,可以跳过本章直接进入第三章。

实例设计文件包括了本章完整的系统。

数据模式校验器产生高速流数据,完成PRBS或者软可编程序列,例如,“walking ones”。

设计通过Avalon-ST连接发送数据到存储器主控器的模式写入器和控制逻辑。

数据模式发生器根据控制逻辑发出的命令将数据写入存储器。

当设计将数据写入存储器时,模式读逻辑读回内容并将它们发送给数据模式验证逻辑。

数据模式校验器接收由模式读出器从Avalon-ST连接读回的数据。

设计验证数据模式(Data Pattern),确保其写入存储器的模式与其读回的数据相同。

当在系统中加入元件并产生连接时,Qsys Messages标签中的错误和警告信息指明了在系统完成之前必须要完成的步骤。

某些错误信息不能立即解决,可能需要在后续步骤中得以解决。

2.1 建立数据模式发生器(Data Pattern Generator)本节将建立数据模式发生器系统,包括两个用来产生测试模式的元件,以及一个用来处理器控制的数据多路复用的第三个元件。

数据模式发生器可以配置成匹配不同的存储器接口宽度。

由于数据模式发生器在每个时钟周期可以提供一个完整字的数据,配置该元件来匹配存储器宽度可以提供足够的带宽来快速访问存储器。

在建立该Qsys系统之前,确保已经下载并安装了本指南实例文件,并打开Quartus II工程。

2.1.1 建立新的带有时钟源的Qsys系统请按照下面的步骤来建立一个新的Qsys系统,并设置时钟源:(1)在Quartus II软件中,选择Tools菜单,并点击Qsys。

(2)在Qsys,选择File菜单,点击New System。

Qsys打开并显示一个新的空系统。

在System Contents标签,Qsys显示出一个时钟源实例,clk_0。

(3)右键点击clk_0并选择Edit,或在clk_0实例上双击即可打开时钟源的设置。

(4)在建立系统时,关掉Clock frequency is known选项,意味着由例化该子系统的高层系统提供时钟频率。

(5)点击Finish。

(6)保存并命名系统:a.在File菜单,点击Save As。