锁相环常见问题解答要点

- 格式:doc

- 大小:198.59 KB

- 文档页数:26

数字(鉴相)环失锁现象及解决办法八一无线数字(鉴相)环失锁现象及解决办法【摘要】通过比较正弦鉴相器与数字鉴相器特性,本文指出锁相环设计者选用数字鉴相器存在的问题,并分析了其失锁原理,最后提出解决办法。

【关键词】锁相环鉴频鉴相器失锁牵引一、前言传统的正弦鉴相器(P。

D)相对来说比较笨重,数字器件广泛使用之后,在锁相环路中亦多采用数字鉴相器,它小巧(可以表面贴装)可靠,而且经济方便, 所以传统的正弦鉴相器日渐少用,在许多无线电设备中为求电路简洁高效,经常使用含有“数字鉴相器”的“组合式锁相环”(见图四)这种锁相环的特点是VCO频率fo不直接送至鉴相器,而是先将fo与第二基频fi2混频,取其差频fR经N分频后再送鉴相器与第一基频fi1进行相位比较,这就产生了一个问题,两个互为镜相的频率(fi2+fR =fo和fi2-fR= f o#)都可能产生同样差频fR,在初始值或大跨度切换(如110Mhz跳到 455KHz)频率时,(当N 改变时VCO fo不会瞬变)压控震荡频率很可能超过镜相频率f o#,这对于正弦鉴相器来说(只检相差)对频差不敏感,不会造成麻烦,而对“数字鉴相器”则不尽然,因为许多“数字鉴相器”实质上是为“鉴频- 鉴相器”,存在频差时以“鉴频”方式工作,而且不能识别是否镜相频率,把已经“超出”镜相频率F o#的VCO震荡误判为“低于”Fo,于是它随即改变误差电压驱使VCO频率进一步超出镜相频率f o#,如此恶性循环而形成逆牵性失锁,整个电路工作瘫痪,对此,PLL设计者宜慎审电路防此一患(这种故障在整机出厂检测中常不出现,而在不同的时间、不同的工作环境中个别元件工作点发生微小变化后突然显露出来),今将逆牵性失锁形成机制和消除方法剖叙如下:二、两种鉴相器的特性A. 正弦监相器(P。

D)将压控震荡器(VCO)输出频率fo的相位qo与基准频率fi的相位qi进行比较,输出随相位差qe变化的误差电压Ue,正弦鉴相器不能识别频率差,它的输出电压Ue随相位差qe作正弦变化,经LPF滤除高频成分,输出控制电压UF用来控制VCO,(即VCO的震荡频率是随UF变化的)见(1)及(2)式:UF =KP Sin(qi-qo)=KP Sinqe (1)fo(t)=fom+Kvco UF(t)(2)qe的变化范围不会超出360度,故控制电压UF是以2兀为周期的曲线函数,见(图二)。

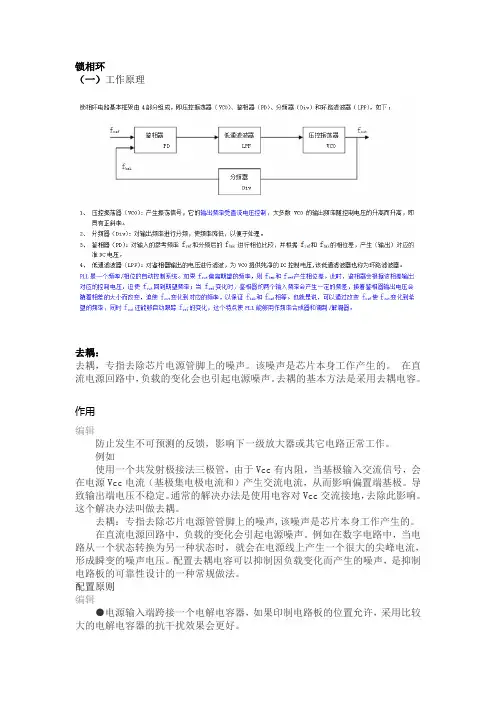

锁相环(一)工作原理去耦:去耦,专指去除芯片电源管脚上的噪声。

该噪声是芯片本身工作产生的。

在直流电源回路中,负载的变化会也引起电源噪声。

去耦的基本方法是采用去耦电容。

作用编辑防止发生不可预测的反馈,影响下一级放大器或其它电路正常工作。

例如使用一个共发射极接法三极管,由于Vcc有内阻,当基极输入交流信号,会在电源Vcc电流(基极集电极电流和)产生交流电流,从而影响偏置端基极。

导致输出端电压不稳定。

通常的解决办法是使用电容对Vcc交流接地,去除此影响。

这个解决办法叫做去耦。

去耦:专指去除芯片电源管管脚上的噪声,该噪声是芯片本身工作产生的。

在直流电源回路中,负载的变化会引起电源噪声。

例如在数字电路中,当电路从一个状态转换为另一种状态时,就会在电源线上产生一个很大的尖峰电流,形成瞬变的噪声电压。

配置去耦电容可以抑制因负载变化而产生的噪声,是抑制电路板的可靠性设计的一种常规做法。

配置原则编辑●电源输入端跨接一个电解电容器,如果印制电路板的位置允许,采用比较大的电解电容器的抗干扰效果会更好。

●为每个集成电路芯片配置一个0.01uF的陶瓷电容器。

如遇到印制电路板空间小而装不下时,可每4~10个芯片配置一个1~10uF钽电解电容器,这种器件的高频阻抗特别小,在500kHz~20MHz范围内阻抗小于1Ω,而且漏电流很小(0.5uA以下)。

●对于噪声能力弱、关断时电流变化大的器件和ROM、RAM等存储型器件,应在芯片的电源线(Vcc)和地线(GND)间直接接入去耦电容。

●去耦电容的引线不能过长,特别是高频旁路电容不能带引线。

目录1.1分类2.2常见的电源噪声及解决方案分类编辑根据传播方向的不同,分为两类:1.从电源进线引入的外界干扰;2.由电子设备产生并经电源线传导出去的噪声。

从形成特点看,噪声干扰分为串模干扰和共模干扰两种:1.串模干扰是两条电源线之间(简称线对线)的噪声;2.共模干扰则是两条电源线对大地(简称线对地)的噪声。

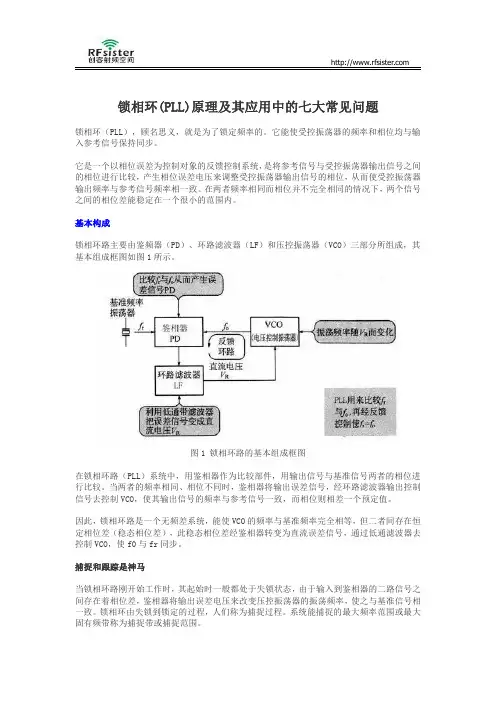

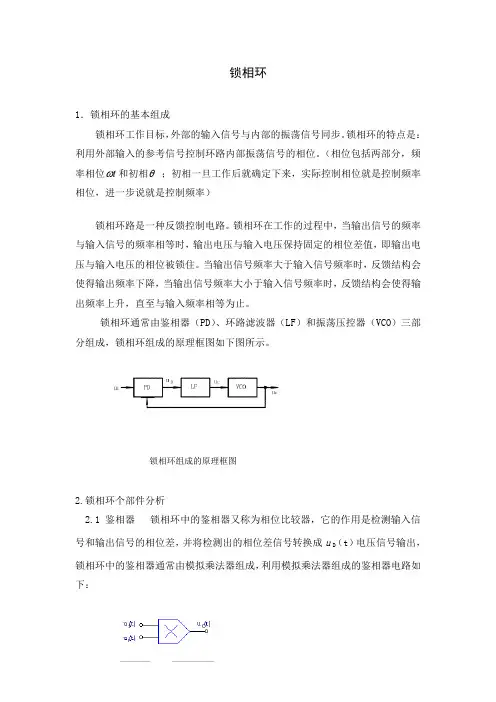

锁相环1.锁相环的基本组成锁相环工作目标,外部的输入信号与内部的振荡信号同步。

锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的相位。

(相位包括两部分,频率相位tω和初相θ;初相一旦工作后就确定下来,实际控制相位就是控制频率相位,进一步说就是控制频率)锁相环路是一种反馈控制电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住。

当输出信号频率大于输入信号频率时,反馈结构会使得输出频率下降,当输出信号频率大小于输入信号频率时,反馈结构会使得输出频率上升,直至与输入频率相等为止。

锁相环通常由鉴相器(PD)、环路滤波器(LF)和振荡压控器(VCO)三部分组成,锁相环组成的原理框图如下图所示。

锁相环组成的原理框图2.锁相环个部件分析2.1鉴相器锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如下:*说明:1.cos 为sin 的相差900的形式,影响只在于初始相位值差900,只为后边数学处理的方便而已。

2.()()i o t t θθ 对于非调制信号(调相调频)可以认为是不随t 改变的,i o θθ,按照一般理解就是初相。

模拟乘法器的输出电压u D 为:2.2.低通滤波器由于u D 中包括和频分量(u D 中第一项),用低通滤波器LF 可以将其滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t )。

2.3 振荡压控器压控振荡器的压控特性下图所示,该特性说明压控振荡器的振荡频率ωu以ω0为中心,随输入信号电压u c (t )的变化而变化。

该特性的表达式为上式说明当uc(t)随时间而变时,压控振荡器的振荡频率ωu也随时间而变,锁相环进入“频率牵引”,自动跟踪捕捉输入信号的频率,使锁相环进入锁定的状态,并保持ω0=ωi的状态不变。

锁相环指标-回复什么是锁相环指标?锁相环(PLL)是一种电子反馈系统,用于调节信号的频率和相位。

锁相环指标是用来描述锁相环性能的量化指标。

锁相环指标通常包括锁定时间、锁定范围、抖动、输入偏置等。

锁相环指标的详细解释如下:1. 锁定时间:锁相环的锁定时间是指从输入信号发生变化到锁相环稳定在新的输出状态所需要的时间。

锁定时间越短,锁相环的响应速度越快。

2. 锁定范围:锁相环的锁定范围是指锁相环能够跟踪的输入信号的频率范围。

锁定范围越广,锁相环适应不同频率的输入信号能力越强。

3. 抖动:锁相环的抖动是指输出信号在稳定锁定状态下的频率和相位误差。

抖动越小,锁相环的稳定性和精度越高。

4. 输入偏置:锁相环的输入偏置是指输入信号与锁相环内部参考信号之间的相位差。

输入偏置越小,锁相环的跟踪效果越好。

为何需要锁相环指标?锁相环指标对于电子系统设计和应用至关重要。

它们是评估锁相环性能和判断锁相环是否满足系统需求的依据。

锁相环指标的合理选择可以确保系统的稳定性、精度和实时性。

以移动通信系统为例,锁相环指标的好坏直接影响信号的传输、检测和处理。

在无线通信中,移动信号的频率、相位和稳定性要求非常高,锁相环用于调整持续变化的信号以保持稳定性。

如果锁相环指标不达标,信号将可能失真、丢失或传输不及时。

如何评估锁相环指标?评估锁相环指标需要进行一系列测试和分析。

常见的锁相环指标测试方法有以下几种:1. 测试锁定时间:在输入信号变化时,观察输出信号的响应时间。

多次测试并取平均值以获得可靠的结果。

2. 测试锁定范围:逐渐改变输入信号的频率,观察锁相环的跟踪能力和输出信号的稳定性。

一般使用频谱仪或示波器进行测试。

3. 测试抖动:使用高精度的频率计或相位计对输出信号进行测量,计算其频率和相位误差。

抖动可以通过信号处理和滤波来减小。

4. 测试输入偏置:输入一个稳定的参考信号和待测试信号,测量两者的相位差。

使用示波器或均衡器等仪器进行测量。

通俗点说,设置PLL锁相环就相当于超频,单片机超频的原因和PC机是一个道理。

分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY,这也和PC机南北桥的原理类似。

相对来说,PLL锁相环的设置还是比较简单的,因为东西很死,完全可以照搬。

只是大家也不要太贪,设置太高相对来说不够稳定,进行过PC机超频的应该很有体会,一般我们现在用的XS128我觉得设置在80MHz是比较合适的,相比前几届比赛用的DG128,这个频率已经蛮高的了。

还有就是SYNR,REFDV只有在CLKSEL_PLLSEL=0的情况下才能写入,不过这是系统默认状态。

多半大家可能还会有以下几点疑问:1.PLL锁相环怎么设置?答:通过写REFDV(CRG参考分频寄存器)和SYNR(CRG合成器寄存器)进行设置2.代码里while(!CRGFLG_LOCK);这句是干什么的?答:时钟校正同步3.为什么代码中会有多多少少的几句空语句?答:锁相环从设定到最后稳定还是需要一点点时间的,所以需要加几条空指令OSC、FOSC、OSCCLK:我认为这三者一样,是振荡器频率,即是我们外加晶振频率SYNR 时钟合成寄存器VCOFRQ[7:6]:不知道,跪求高人解答!!!SYNDIV[5:0]:不知道,跪求高人解答!!!REFDV时钟分频寄存器REFFRQ[7:6]:不知道,跪求高人解答REFDIV[5:0]:不知道,跪求高人解答FVCO:应该是系统频率(有错请更正)FPLL、PLLCLK:我认为是一样的,即锁相环频率FBUS、Bus Clock:我认为是一样的,即总线频率POSTDIV:貌似是分频控制,应该是控制FVCO和PLLCLK的分频比,一般设置为0,这时FPLL= FVCO/1=FVCO初步设想:1、FVCO= 2*FOSC*(SYNDIV + 1)/(REFDIV + 1),我认为OSC、FOSC、OSCCLK都是一样的,即晶振频率2、FPLL= FVCO/(2 × POSTDIV),FPLL应该和PLLCLK一样,都是锁相环频率,POSTDIV 等于0时默认为分子为1,即FPLL= FVCO/1=FVCO3、FBUS= FPLL/2,FBUS为总线时钟频率所以综合起来就有:FBUS=[2*FOSC*(SYNDIV + 1)/(REFDIV + 1)]/2=FOSC*(SYNDIV + 1)/(REFDIV + 1)再看看龙丘80MHz的超频源代码void SetBusCLK_80M(void){CLKSEL=0X00; //disengage PLL to systemPLLCTL_PLLON=1; //开启锁相环SYNR =0xC0 | 0x09; //我理解,SYNR只是低6位有效,所以经过运算后SYNR=9 REFDV=0x80 | 0x01; //我理解,REFDV只是低4位有效,所以经过运算后REFDV=1 POSTDIV=0x00; //POSTDIV=0x00=0,则FPLL=FVCO=PLLCLK,所以PLLCLK=FVCO=2*16*(1+9)/(1+1)=160MHz;_asm(nop); //所以总线时钟BUS CLOCK=PLLCLK/2=80MHz_asm(nop);while(!(CRGFLG_LOCK==1)); //when pll is steady ,then use it;CLKSEL_PLLSEL =1; //engage PLL to system;}好了,个人意见发表完毕,有错误的请更正,别扔砖头哈砖头我自己仍就行了synr和refdv都是低6位来设定所要超的频率,其高2位是根据你要超的频率来配置,通过合理的配置VCOFRQ,REFFRQ来提高系统时钟稳定性。

几种常见锁相环分析并网变换器对锁相环的基本要求:(1)电网电压经常发生跌落、闪变等动态电能质量问题,并且这些异常的出现均是不可预计而且需要及时补偿的。

所以要求并网变换器能够对电网电压相位的变化在ms级的时间内能做出快速的响应,即要求并网变换器的锁相方法要有良好的动态性能,保证当电压跌落和骤升时不对锁相性能造成太大影响。

(2)三相电压不平衡时,要求电力电子装置的锁相方法能够捕获正序基波分量的相位,对三相不平衡情况有很强的抑制作用。

(3)锁相环应该能快速检测到电网电压发生相位、频率突变等问题。

(4)要求锁相方法对畸变电压要有很强的抑制作用。

(5)对于一些电力补偿装置如动态电压恢复器,锁相方法不仅要实时检测网侧电压的相位,而且要实时监测网侧电压的幅值变化状况用来判断并决定电力补偿装置的工作模式1、基于低通滤波器的锁相方法Karimi-Ghartemani.M和Reza Iravani.A提出了基于低通滤波器的锁相方法,其原理如图所示。

三相电网电压从三相静止坐标系转换为两相静止坐标系,利用常见的低通滤波器滤除电网中的谐波干扰,然后对信号进行标么化处理,从而得到电网电压的相位,旋转矩阵R用于补偿滤波器所造成的相位滞后。

原理及R优点:避免检测过零点带来的问题缺点:1、在设计低通滤波器时,需要在系统滤波器的鲁棒性和动态响应之间做出折中的选择,较低的截止频率可以抑制系统谐波对相位检测的干扰,但是也相应的降低了系统的响应速度。

2、这种方法需求得反三角函数值,计算速度较慢,尤其在系统频率变动和三相电压不平衡时,对畸变电压的抑制作用弱,因此无法正确锁相。

参考文献Method for Synchronization of Power Electronic Converters in Polluted and Variable-Frequency2、基于空间矢量滤波器(SVF)的锁相方法空间矢量滤波器是一种用于空间矢量滤波的新型滤波器,它是基于电网电压的αβ分量相互关系相互影响的基础上提出的。

ADI官网下载了个资料,对于PLL学习和设计来说都非常实用的好资料,转发过来,希望对大家有帮助(原文链接/zh/content/cast_faq_PLL/fca.html#faq_pll_01)∙参考晶振有哪些要求?我该如何选择参考源?∙请详细解释一下控制时序,电平及要求?∙控制多片PLL芯片时,串行控制线是否可以复用?∙请简要介绍一下环路滤波器参数的设置?∙环路滤波器采用有源滤波器还是无源滤波器?∙PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器?∙如何设置电荷泵的极性?∙锁定指示电路如何设计?∙PLL对射频输入信号有什么要求?∙PLL芯片对电源的要求有哪些?∙内部集成了VCO的ADF4360-x,其VCO中心频率如何设定?∙锁相环输出的谐波?∙锁相环系统的相位噪声来源有哪些?减小相位噪声的措施有哪些?∙为何我测出的相位噪声性能低于ADISimPLL仿真预期值?∙锁相环锁定时间取决于哪些因素?如何加速锁定?∙为何我的锁相环在做高低温试验的时候,出现频率失锁?∙非跳频(单频)应用中,最高的鉴相频率有什么限制?∙频繁地开关锁相环芯片的电源会对锁相环有何影响?∙您能控制PLL芯片了么?,R分频和N分频配置好了么?∙您的晶振输出功率有多大?VCO的输出功率有多大?∙您的PFD鉴相极性是正还是负?∙您的VCO输出频率是在哪一点?最低频率?最高频率?还是中间的某一点?VCO 的控制电压有多大?∙您的PLL环路带宽和相位裕度有多大?∙评价PLL频率合成器噪声性能的依据是什么?∙小数分频的锁相环杂散的分布规律是什么?∙到底用小数分频好还是整数分频好?∙ADI提供的锁相环仿真工具ADISimPLL支持哪些芯片,有什么优点?∙分频–获得高精度时钟参考源?∙PLL,VCO闭环调制,短程无线发射芯片?∙PLL,VCO开环调制?∙时钟净化----时钟抖动(jitter)更小?∙时钟恢复(Clock Recovery)?问题:参考晶振有哪些要求?我该如何选择参考源?答案:波形:可以使正弦波,也可以为方波。

第一章锁相环路的基本工作原理:1.锁相环路是一个闭环的相位控制系统;锁相环路(PLL)是一个相位跟踪系统,它建立了输出信号顺时相位与输入信号瞬时相位的控制关系。

2. 若输入信号是未调载波,θi(t)即为常数,是u i(t)的初始相位;若输入信号时角调制信号(包括调频调相),θi(t)即为时间的函数。

3.ωo是环内被控振荡器的自由振荡角频率;θo(t)是以自由振荡的载波相位ωo t为参考的顺时相位,在未受控制以前它是常数,在输入信号控制之下,θo(t)即为时间的函数。

4. 输入信号频率与环路自由振荡频率之差,称为环路的固有频率环路固有角频差:输入信号角频率ωi与环路自由振荡角频率ωo之差。

瞬时角频差:输入信号频率ωi与受控压控振荡器的频率ωv之差。

控制角频差:受控压控振荡器的频率ωv与自由振荡频率ωo之差。

三者之间的关系:瞬时频差=固有频差-控制频差。

5. 从输入信号加到锁相环路的输入端开始,一直到环路达到锁定的全过程,称为捕获过程。

6. 对一定环路来说,是否能通过捕获而进入同步完全取决于起始频差。

7. 锁定状态又叫同步状态:①同频②相位差固定8. 锁定之后无频差,这是锁相环路独特的优点。

9. 捕获时间T p的大小除决定于环路参数之外,还与起始状态有关。

10.若改变固有频差∆ωo,稳定相差θe(∞)会随之改变。

11.锁相环路基本构成:由鉴相器(PD)、环路滤波器(LF)和电压控制振荡器(VCO)组成。

12.鉴相器是一个相位比较装置,鉴相器的电路总的可以分为两大类:第一类是相乘器电路,第二类是序列电路。

13.环路滤波器具有低通特性。

常见的环路滤波器有RC积分滤波器、无源比例积分滤波器和有源比例积分滤波器三种。

(会推导它们的传输算子)14.电压振荡器是一个电压-频率变换装置,它的振荡频率应随输入控制电压u c(t)线性的变化。

15.压控振荡器应是一个具有线性控制特性的调频振荡器。

要求压控振荡器的开环噪声尽可能低,设计电路时应注意提高有载品质因素和适当增加振荡器激励功率,降低激励级的内阻和振荡管的噪声系数。

第1步:验证通信第一步是验证PLL响应编程的能力。

如果PLL没有锁定,无法读回,则尝试发送需要最小量硬件命令工作的软件命令。

一种方法是通过软件(而非引脚)调节PLL的通电断电寻找引脚的可预测电流变化或偏置电压电平变化。

许多PLL在其输入(OSCin)引脚的电平在通电时为Vcc/2,在断电时为0V。

如果PLL集成了压控振荡器(VCO),则查看低压差(LDO)输出引脚电压是否对通电和断电命令做出反应。

还可能可以切换输入/输出(I/O)引脚,比如许多LMX系列PLL的MUXout引脚。

如果采用上述方法能够验证通信,就可以继续尝试进行锁定。

如果无法验证通信,则查找常见的原因,例如以下原因:编程串行锁存使能(也称为芯片选择条(CSB))过高对软件输入的低通滤波过多与串行外围设备接口总线(SPI)存在时序问题电源引脚焊接有误第2步:建立锁定验证通信后,下一步就是尝试对PLL进行锁定。

下面是PLL无法锁定的一些更常见的原因:对锁定检测引脚的错误解读。

如果配置有误,锁定检测引脚会在实际已经锁定的情况下显示出PLL 未锁定。

可以通过查看频谱分析仪输出或VCO调谐电压验证这一情况。

编程问题。

向PLL发送错误的信息会很容易导致无法锁定。

一些常见的编程错误包括:VCO编程频率超出范围、VCO校准设置不正确或寄存器时序有误。

VCO校准问题。

对于集成VCO的PLL而言,频率范围通常分成几个不同的频段。

错误的编程会导致VCO锁定错误的频段。

对特定寄存器的编程通常会启动VCO校准;因此必须确定在编程此寄存器时,其他软件和硬件(尤其是基准输入)状态正确,以确保校准正常工作。

输入或反馈路径问题。

如果VCO输入或基准输入因电源水平较低、压摆率较低、匹配较差或谐波较高而存在问题,会导致PLL打开锁定。

大多数PLL有方法输出内部频率计数器的实际频率输出,将其发送到引脚。

环路滤波器中与地连接或短路。

可以通过查看调谐电压或切换鉴相器两极,根据频率变化确定连接或短路。

模拟锁相环实验注意事项

在进行模拟锁相环实验时,有几个注意事项需要注意:

1. 实验环境:确保实验环境稳定,避免干扰源的干扰。

可以将实验室内的干扰源降到最低,例如关闭电视、关闭电脑风扇等。

2. 确保电源稳定:使用稳定的电源为实验提供电力。

对于模拟锁相环实验中的电源,可以使用准确稳定的直流电源,以避免电源的波动对实验结果的影响。

3. 连接正确的信号源:将正确的信号源与锁相环电路连接。

确保信号源的输出与锁相环电路的输入匹配,并使用合适的信号线来连接它们。

4. 设置合适的参考信号频率:根据实验目的,选择适当的参考信号频率。

参考信号频率应该与待测信号频率相匹配,以获得最佳的锁定效果。

5. 调整参数:对于模拟锁相环电路,可能需要调整一些参数,如放大倍数、相位偏移、环路滤波器等。

根据实验需求,逐步调整这些参数,以获得最佳的实验结果。

6. 观察实验结果:在实验过程中,及时观察实验结果。

可以使用示波器等仪器来监测锁相环电路的输出信号,以确保实验正常进行。

请注意,以上只是一般的注意事项,具体的实验操作和注意事项会根据具体的锁相环实验设备和实验目的而有所不同。

建议在实验前详细阅读设备的使用说明书,并遵循相关安全操作规程。

ADI官网下载了个资料,对于PLL学习和设计来说都非常实用的好资料,转发过来,希望对大家有帮助(原文链接/zh/content/cast_faq_PLL/fca.html#faq_pll_01)∙参考晶振有哪些要求?我该如何选择参考源?∙请详细解释一下控制时序,电平及要求?∙控制多片PLL芯片时,串行控制线是否可以复用?∙请简要介绍一下环路滤波器参数的设置?∙环路滤波器采用有源滤波器还是无源滤波器?∙PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器?∙如何设置电荷泵的极性?∙锁定指示电路如何设计?∙PLL对射频输入信号有什么要求?∙PLL芯片对电源的要求有哪些?∙内部集成了VCO的ADF4360-x,其VCO中心频率如何设定?∙锁相环输出的谐波?∙锁相环系统的相位噪声来源有哪些?减小相位噪声的措施有哪些?∙为何我测出的相位噪声性能低于ADISimPLL仿真预期值?∙锁相环锁定时间取决于哪些因素?如何加速锁定?∙为何我的锁相环在做高低温试验的时候,出现频率失锁?∙非跳频(单频)应用中,最高的鉴相频率有什么限制?∙频繁地开关锁相环芯片的电源会对锁相环有何影响?∙您能控制PLL芯片了么?,R分频和N分频配置好了么?∙您的晶振输出功率有多大?VCO的输出功率有多大?∙您的PFD鉴相极性是正还是负?∙您的VCO输出频率是在哪一点?最低频率?最高频率?还是中间的某一点?VCO 的控制电压有多大?∙您的PLL环路带宽和相位裕度有多大?∙评价PLL频率合成器噪声性能的依据是什么?∙小数分频的锁相环杂散的分布规律是什么?∙到底用小数分频好还是整数分频好?∙ADI提供的锁相环仿真工具ADISimPLL支持哪些芯片,有什么优点?∙分频–获得高精度时钟参考源?∙PLL,VCO闭环调制,短程无线发射芯片?∙PLL,VCO开环调制?∙时钟净化----时钟抖动(jitter)更小?∙时钟恢复(Clock Recovery)?问题:参考晶振有哪些要求?我该如何选择参考源?答案:波形:可以使正弦波,也可以为方波。

功率:满足参考输入灵敏度的要求。

稳定性:通常用TCXO,稳定性要求< 2 ppm。

这里给出几种参考的稳定性指标和相位噪声指标。

名称频率范围(MHz)频率稳定度(ppm)相位噪声dBc/Hz@10kHz 价格普通晶体振荡器SPXO 1~100 +/-10~+/-100 低压控晶体振荡器VCXO 1~60 +/-1~+/-50温度补偿晶体振荡器1-60 +/-0.1~+/-5TCXO压控振荡器VCO 宽-110恒温控制晶体振荡器10~20 0.0005~0.01 -150, -120@10Hz 非常高OCXO频率范围:ADI提供的PLL产品也可以工作在低于最小的参考输入频率下,条件是输入信号的转换速率要满足给定的要求。

例如,ADF4106的数据手册要求的最小参考输入信号REFIN为20MHz,功率最小为-5dBm,这相当于转换速率(slew rate)为22.6V/us,峰峰值为360mV的正弦波。

具体计算如下:对正弦波Vp*sin(2*pi*f*t)而言,转换速率Slew Rate=dv/dt|max=2*pi*f*Vp。

那么我们来考察功率为-5dBm(50欧姆系统)(Vp=180mV)的信号,其峰峰值为360mV,其转换速率为Slew Rate=dv/dt|max=2*pi*f*Vp=22.6V/us所以,只要REFIN功率满足要求,并且输入信号的转换速率高于22.6V/us ,REFIN可以工作在低于20MHz的条件下。

具体实现是,一个转换时间为146ns的3.3V CMOS输入可以很容易的满足该项要求。

总的来说,用功率较大的方波信号作为参考可以使REFIN工作在低于数据手册上给出的最低频率限制。

在PLL频率综合器的设计中,我们推荐使用温度补偿型晶振(TCXO)。

在需要微调参考的情况下使用VCXO,需要注意VCXO灵敏度比较小,比如100Hz/V,所以设计环路滤波器的带宽不能很大(比如200Hz),否则构成滤波器的电容将会很大,而电阻会很小。

普通有源晶振,由于其温度稳定性差,在高精度的频率设计中不推荐使用。

问题:请详细解释一下控制时序,电平及要求?答案:ADI的所有锁相环产品控制接口均为三线串行控制接口。

如图1所示。

要注意的是:在ADI的PLL产品中,大多数的时序图如图7中上面的图所示,该图是错误的,正确的时序图如图7中下面的图所示,LE 的上升沿应跟Clock的上升沿对齐,而非Clock的下降沿。

图1 PLL频率合成器的串行控制接口(3 Wire Serial Interface)控制接口由时钟CLOCK,数据DATA,加载使能LE构成。

加载使能LE 的下降沿提供起始串行数据的同步。

串行数据先移位到PLL频率合成器的移位寄存器中,然后在LE的上升沿更新内部相应寄存器。

注意到时序图中有两种LE的控制方法。

SPI控制接口为3V/3.3V CMOS电平。

另外,需要注意的是对PLL芯片的寄存器进行写操作时,需要按照一定的次序来写,具体请参照芯片资料中的描述。

特别地,在对ADF4360的寄存器进行操作时,注意在写控制寄存器和N计数器间要有一定的延时。

控制信号的产生,可以用MCU,DSP,或者FPGA。

产生的时钟和数据一定要干净,过冲小。

当用FPGA产生时,要避免竞争和冒险现象,防止产生毛刺。

如果毛刺无法避免,可以在数据线和时钟线上并联一个10~47pF的电容,来吸收这些毛刺。

问题:控制多片PLL芯片时,串行控制线是否可以复用?答案:一般地,控制PLL的信号包括:CE,LE,CLK,DATA。

CLK和DATA信号可以共用,即占用2个MCU的IO口,用LE信号来控制对哪个PLL芯片进行操作。

多个LE信号也可以共用一个MCU的IO口,这时需要用CE信号对芯片进行上电和下电的控制。

问题:请简要介绍一下环路滤波器参数的设置?答案:ADISimPLL V3.0使应用工程师从繁杂的数学计算中解脱出来。

我们只要输入设置环路滤波器的几个关键参数,ADISimPLL就可以自动计算出我们所需要的滤波器元器件的数值。

这些参数包括,鉴相频率PFD,电荷泵电流Icp,环路带宽BW,相位裕度,VCO控制灵敏度Kv,滤波器的形式(有源还是无源,阶数)。

计算出的结果往往不是我们在市面上能够买到的元器件数值,只要选择一个最接近元器件的就可以。

通常环路的带宽设置为鉴相频率的1/10或者1/20。

相位裕度设置为45度。

滤波器优先选择无源滤波器。

滤波器开环增益和闭环增益以及相位噪声图之间的关系。

闭环增益的转折频率就是环路带宽。

相位噪声图上,该点对应于相位噪声曲线的转折频率。

如果设计的锁相环噪声太大,就会出现频谱分析仪上看到的转折频率大于所设定的环路带宽。

问题:环路滤波器采用有源滤波器还是无源滤波器?答案:有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的PLL产生的频率的相位噪声性能会比采用无源滤波器的PLL输出差。

因此在设计中我们尽量选用无源滤波器。

其中三阶无源滤波器是最常用的一种结构。

PLL频率合成器的电荷泵电压Vp一般取5V或者稍高,电荷泵电流通过环路滤波器积分后的最大控制电压低于Vp或者接近Vp。

如果VCO/VCXO的控制电压在此范围之内,无源滤波器完全能够胜任。

当VCO/VCXO的控制电压超出了Vp,或者非常接近Vp的时候,就需要用有源滤波器。

在对环路误差信号进行滤波的同时,也提供一定的增益,从而调整VCO/VCXO控制电压到合适的范围。

那么如何选择有源滤波器的放大器呢?这类应用主要关心一下的技术指标:低失调电压(Low Offset Voltage)[通常小于500µV]低偏流(Low Bias Current)[通常小于50pA]如果是单电源供电,需要考虑使用轨到轨(Rail-to-Rail)输出型放大器。

这里提供几种常见的PLL滤波器应用放大器的型号。

AD711/2, AD797, AD820/2, AD8510/2, AD8605/6, AD8610/20, AD8651/2, OP162/262, OP184/284, OP249, OP27.问题:PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器?答案:选择VCO时,尽量选择VCO的输出频率对应的控制电压在可用调谐电压范围的中点。

选用低控制电压的VCO可以简化PLL设计。

VCO的输出通过一个简单的电阻分配网络来完成功率分配。

从VCO的输出看到电阻网络的阻抗为18+(18+50)//(18+50)=52ohm。

形成与VCO的输出阻抗匹配。

下图中ABC三点功率关系。

B,C点的功率比A点小6dB。

如图是ADF4360-7输出频率在850MHz~950MHz时的输出匹配电路,注意该例是匹配到50欧的负载。

如果负载是75欧,那么匹配电路无需改动,ADF4360-7的输出级为电流源,负载值的小变动不会造成很大的影响,但要注意差分输出端的负载需相等。

ADF4360-7 输出匹配电路o喜爱显示0 喜欢(0)o操作∙∙Re: 非常实用、超详细的锁相环常见问题解答~∙∙小爬7262014-6-17 下午3:04 (回复小爬726 )∙问题:如何设置电荷泵的极性?∙答案:在下列情况下,电荷泵的极性为正。

∙o环路滤波器为无源滤波器,VCO的控制灵敏度为正(即,随着控制电压的升高,输出频率增大)。

在下列情况下,电荷泵的极性为负。

o环路滤波器为有源滤波器,并且放大环节为反相放大;VCO的控制灵敏度为正。

o环路滤波器为无源滤波器,VCO的控制灵敏度为负。

o PLL分频应用,滤波器为无源型。

即参考信号直接RF反馈分频输入端,VCO 反馈到参考输入的情况。

问题:锁定指示电路如何设计?答案:PLL锁定指示分为模拟锁定指示和数字锁定指示两种鉴相器和电荷泵原理图数字锁定指示:当PFD的输入端连续检测到相位误差小于15ns的次数为3(5)次,那么PLL就会给出数字锁定指示。

数字锁定指示的工作频率范围:通常为5kHz~50MHz。

在更低的PFD频率上,漏电流会触发锁定指示电路;在更高的频率上,15ns的时间裕度不再适合。

在数字锁定指示的工作频段范围之外,推荐使用模拟锁定指示。

模拟锁定指示对电荷泵输入端的Up脉冲和Down脉冲进行异或处理后得出的脉冲串。

所以当锁定时,锁定指示电路的输出为带窄负脉冲串的高电平信号。

图为一个典型的模拟锁定指示输出(MUXOUT输出端单独加上拉电阻的情况)。

模拟锁定指示的输出级为N沟道开漏结构,需要外接上拉电阻,通常为10KOhm~160kohm。

我们可以通过一个积分电路(低通滤波器)得到一个平坦的高电平输出,如图所是的蓝色框电路。