Altera的FPGA_常见问题汇总

- 格式:pdf

- 大小:553.39 KB

- 文档页数:9

FPGA设计中常见的时序收敛问题分析FPGA设计中常见的时序收敛问题是指在FPGA设计过程中出现的时序约束无法满足的情况。

时序约束是指设计中需要满足的时钟周期、时钟频率、数据传输延迟等时间要求。

时序收敛问题会导致设计无法工作正常,甚至无法通过时序分析和布局布线。

时序收敛问题的主要原因包括时钟频率过高、逻辑路径过长、时钟抖动、布线延迟不稳定等。

下面我们将分析常见的时序收敛问题及解决方法。

首先,时钟频率过高是导致时序收敛问题的常见原因之一。

当时钟频率过高时,逻辑电路需要更短的时间完成计算,容易产生时序违例。

解决方法包括优化逻辑电路、减小时钟分频比、增加集成电路的时钟域等。

其次,逻辑路径过长也会导致时序收敛问题。

逻辑路径过长会增加逻辑延迟,使得数据无法在规定的时间内到达目的地。

解决方法包括优化逻辑电路结构、增加缓冲器减小电路路径、合理分配信号路径等。

时钟抖动也是时序收敛问题的常见原因。

时钟抖动会导致时钟信号的不稳定,使得同步电路无法正常工作。

解决方法包括使用低抖动的时钟源、优化时钟分配网络、提高时钟质量等。

布线延迟不稳定也是导致时序收敛问题的原因之一。

不同的布线路径会导致不同的延迟,使得时序约束无法满足。

解决方法包括合理规划布线路径、优化布线约束、降低布线时钟偏移等。

总的来说,时序收敛问题在FPGA设计中是一个常见且重要的问题。

设计工程师需要综合考虑时钟频率、逻辑路径、时钟抖动和布线延迟等因素,合理设计电路结构,优化时序约束,确保设计能够满足时序要求。

只有充分理解和解决时序收敛问题,才能保证FPGA设计的稳定性和可靠性。

FPGA设计常犯错误大全,你中招了吗?FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。

现在的FPGA不仅包含以前的LE,RAM也更大更快更灵活,管教IOB也更加的复杂,支持的IO类型也更多,而且内部还集成了一些特殊功能单元,包括:DSP:实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。

换言之,FPGA可以更容易实现多个DSP core功能。

在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

SERDES:高速串行接口。

将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。

有了SERDES模块,FPGA可以很容易将这些高速串行接口集成进来,无需再购买专门的接口芯片。

CPU core:分为2种,软core和硬core.软core是用逻辑代码写的CPU模块,可以在任何资源足够的FPGA中实现,使用非常灵活。

而且在大容量的FPGA中还可以集成多个软core,实现多核并行处理。

硬core是在特定的FPGA内部做好的CPU core,优点是速度快、性能好,缺点是不够灵活。

不过,FPGA还是有缺点。

对于某些高主频的应用,FPGA就无能为力了。

现在虽然理论上FPGA可以支持的500MHz,但在实际设计中,往往200MHz以上工作频率就很难实现了。

FPGA设计要点之一:时钟树对于FPGA来说,要尽可能避免异步设计,尽可能采用同步设计。

同步设计的第一个关键,也是关键中的关键,就是时钟树。

一个糟糕的时钟树,对FPGA设计来说,是一场无法弥补的灾难,是一个没有打好地基的大楼,崩溃是必然的。

具体一些的设计细则:1)尽可能采用单一时钟;2)如果有多个时钟域,一定要仔细划分,千万小心;3)跨时钟域的信号一定要做同步处理。

对于控制信号,可以采用双采样;对于数据信号,可以采用异步fifo.需要注意的是,异步fifo不是万能的,一个异步fifo也只能解决一定范围内的频差问题。

=====================第1章FPGA基础知识=================== FPGA设计工程师努力的方向SOPC,高速串行I/O,低功耗,可靠性,可测试性和设计验证流程的优化等方面。

随着芯片工艺的提高,芯片容量、集成度都在增加,FPGA 设计也朝着高速、高度集成、低功耗、高可靠性、高可测、可验证性发展。

芯片可测、可验证,正在成为复杂设计所必备的条件,尽量在上板之前查出bug,将发现bug的时间提前,这也是一些公司花大力气设计仿真平台的原因。

另外随着单板功能的提高、成本的压力,低功耗也逐渐进入FPGA设计者的考虑范围,完成相同的功能下,考虑如何能够使芯片的功耗最低。

高速串行IO的应用,也丰富了FPGA 的应用范围,象xilinx的v2pro中的高速链路也逐渐被应用。

总之,学无止境,当掌握一定概念、方法之后,就要开始考虑FPGA其它方面的问题了。

简述FPGA等可编程逻辑器件设计流程系统设计电路构思,设计说明与设计划分,电路设计与输入(HDL代码、原理图),功能仿真与测试,逻辑综合,门级综合,逻辑验证与测试(综合后仿真),布局布线,时序仿真,板级验证与仿真,加载配置,在线调试。

常用开发工具(AlteraFPGA)HDL语言输入:TextEditor(HDL语言输入),还可以使用UltraEdit原理图输入:SchematicEditorIPCore输入:MegaWinzad综合工具:Synplify/SynplifyPro,QaustusII内嵌综合工具仿真工具:ModelSim实现与优化工具:QuartusII集成的实现工具有AssignmentEditor(约束编辑器)、LogicLock(逻辑锁定工具)、PowerFitFitter(布局布线器)、TimingAnalyzer(时序分析器,STA分析工具)、FloorplanEditor(布局规划器)、ChipEditor(底层编辑器)、DesignSpaceExplorer(设计空间管理器)、DesignAssistant(检查设计可靠性)等。

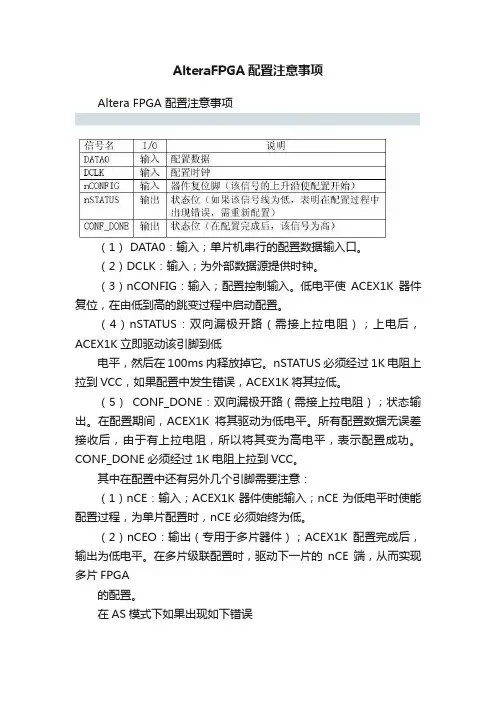

AlteraFPGA配置注意事项Altera FPGA 配置注意事项(1) DATA0:输入;单片机串行的配置数据输入口。

(2)DCLK:输入;为外部数据源提供时钟。

(3)nCONFIG:输入;配置控制输入。

低电平使ACEX1K器件复位,在由低到高的跳变过程中启动配置。

(4)nSTATUS:双向漏极开路(需接上拉电阻);上电后,ACEX1K立即驱动该引脚到低电平,然后在100ms内释放掉它。

nSTATUS必须经过1K电阻上拉到VCC,如果配置中发生错误,ACEX1K将其拉低。

(5)CONF_DONE:双向漏极开路(需接上拉电阻);状态输出。

在配置期间,ACEX1K将其驱动为低电平。

所有配置数据无误差接收后,由于有上拉电阻,所以将其变为高电平,表示配置成功。

CONF_DONE必须经过1K电阻上拉到VCC。

其中在配置中还有另外几个引脚需要注意:(1)nCE:输入;ACEX1K器件使能输入;nCE为低电平时使能配置过程,为单片配置时,nCE必须始终为低。

(2)nCEO:输出(专用于多片器件);ACEX1K配置完成后,输出为低电平。

在多片级联配置时,驱动下一片的nCE端,从而实现多片FPGA的配置。

在AS模式下如果出现如下错误Error: Can't recognize silicon ID for device 11。

确认你的QII中选择的配置芯片是否和电路板中的芯片一致2。

检查你的下载线是否损坏,据说下载线长不应该超过30CM 但是我自己做的大概有50CM也可以正常使用3。

确定你的配置芯片是否损坏,可以使用JTAG烧写配置芯片测试下,如果可写那就可以排除该错误4。

检查你的电路中的AS模式中的上拉电阻和下拉电阻是否虚焊,还有MSEL0与MSEL1是否选择正确和nSTATUS是否接上拉电阻等。

说明:本文内容来自网络1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同一变量赋值,这个细节一般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:大意了,端口类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时用非阻塞赋值,有时用阻塞赋值,这是禁止的。

在初学的时候,可能分得不是很清楚,所以在检查时,一定要一步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细心点。

6.Error (10171): Verilog HDL syntax error at ir_ctrl.v(149) near end of file ; expecting an identifier, or "endmodule", or a parallel statement解析:最后上了endmodule。

FPGA基础知识问答500问连载(二)Q16:FPGA设计中对时钟的使用?(例如分频等)FPGA芯片有固定的时钟路由,这些路由能有减少时钟抖动和偏差。

需要对时钟进行相位移动或变频的时候,一般不允许对时钟进行逻辑操作,这样不仅会增加时钟的偏差和抖动,还会使时钟带上毛刺。

一般的处理方法是采用FPGA芯片自带的时钟管理器如PLL,DLL或DCM,或者把逻辑转换到触发器的D输入(这些也是对时钟逻辑操作的替代方案)。

Q17:FPGA设计中如何实现同步时序电路的延时?首先说说异步电路的延时实现:异步电路一半是通过加buffer、两级与非门等(我还没用过所以也不是很清楚),但这是不适合同步电路实现延时的。

在同步电路中,对于比较大的和特殊要求的延时,一半通过高速时钟产生计数器,通过计数器来控制延时;对于比较小的延时,可以通过触发器打一拍,不过这样只能延迟一个时钟周期。

Q18:FPGA中可以综合实现为RAM/ROM/CAM的三种资源及其注意事项?三种资源:block ram;触发器(FF),查找表(LUT);注意事项:1:在生成RAM等存储单元时,应该首选block ram 资源;其原因有二:第一:使用block ram等资源,可以节约更多的FF和4-LUT等底层可编程单元。

使用block ram 可以说是“不用白不用”,是最大程度发挥器件效能,节约成本的一种体现;第二:block ram是一种可以配置的硬件结构,其可靠性和速度与用LUT和register构建的存储器更有优势。

2:弄清FPGA的硬件结构,合理使用block ram资源;3:分析block ram容量,高效使用block ram资源;4:分布式ram资源(distribute ram)Q19:Xilinx中与全局时钟资源和DLL相关的硬件原语:常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG,IBUFGDS,BUFG,BUFGP,BUFGCE,BUFGMUX,BUFGDLL,DCM等。

altera cyclone器件告别AS下载模式,直接用JTAG配置器件进行编程看CYCLONE II的器件手册时,看到一段关于配置器件的描述:可以通过JTAG接口对串行配置器件进行编程,可是里面没有详细的使用方法,在altera的网站上找到了一些关于这个的资料先介绍一下SFL:Serial Flash Loader,它是通过JTAG接口在系统编程(isp)串行配置器件。

这种方法主要是通过FPGA作为一个JTAG与串行配置器件之间的桥梁,优点是能通过一个JTAG接口对器件进行配置,缺点是慢,因为在编程前要对FPGA进行配置。

废话少说,首先编译生成SOF文件,也就是JTAG方式下的下载文件,然后1 在“文件”里选择“Convert Programming Files”,出现对话框后2 在programming file type里选.jic3 在configuration device里选择相应的串行配置器件4 file name选择转换文件5 选sof data,单击add file选择sof文件6 flash loader单击add device选择FPGA器件然后OK生成JIC文件,后面的事情跟JTAG下下载一样,只是将文件类型选为JIC文件,可惜我转换的时候选EPCS1时,老提示容量不够,选EPCS4就没有问题了,大家可以试试。

cyclone器件, jtag和as下载模式JTAG是直接烧到FPGA里面的,由于是SRAM,所以断电后要重烧;AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里;pof文件可以通过as方式下载(保证byteblasterII/usb blaster连接正确);sof文件或者转换的jic可以通过jtag方式下载;这两种下载模式使用的接口外形是完全一样的,要注意区分!使用Flash Loader(JTAG模式)下载EPCS器件一般来说Altera公司Cyclone或者CycloneII系列FPGA相应的配置器件会选择EPCS系列串行FLASH。

Altera的FPGA下载常见问题经验小结软件部分:对于QUARTUS II 4.0版本软件,在安装完成后,需要做如下设置,软件才能够正常工作。

第一:设置license。

第二:安装驱动:Win2000/XP:1、打开控制面板(开始->设置->控制面板)2、双击“添加/删除硬件”图标,启动添加/删除硬件向导,然后按下一步继续。

3、在“选择一个硬件任务”面板上,选择“添加/排除设备故障”,然后按下一步继续。

WIN2000将会在新的硬件检测窗口里搜索新的即插即用设备。

4、在“选择一个硬件设备”面板上,选择“添加新设备”。

按下一步继续。

5、在“查找新硬件”面板上,选择“否,我想从列表选择硬件“。

按下一步继续。

6、在”硬件类型“面板上,选择”声音、视频和游戏控制器“。

按下一步继续。

7、在”选择一个设备驱动程序“窗口,点击”从磁盘安装“按钮。

8、指定win2000.inf文件的完整路径(例如安装目录>\drivers\win2000)。

按下一步继续。

9、在“没有找到数字签名”窗口,点击“是”按钮。

10、在“选择一个设备驱动程序”窗口,如果您使用ByteblasterMV或AlteraByteBlasterII,请安装相应驱动。

11、在“开始硬件安装”窗口,点击下一步继续。

12、在“没有找到数字签名”窗口,点击“是”按钮,继续安装。

13、在“完成添加/删除硬件向导”窗口,点击“完成”按钮14、在弹出的系统对话选择是否重新启动计算机。

驱动程序要在重新启动后才能使用。

重新启动后,即可在quartusII里进行program了。

第三:programer设置。

点击桌面图标Quartus II 4.0启动软件。

A)在tools菜单下,执行Programer命令。

B)点击hardware setup,点击select hardware,选择Byteblaster,---→add hardware---→close.C)完成后,在Hardware setup 右侧出ByteBlaster[LPT1],mode 的下拉菜单有JTAG,Passive Serial,Active Serial programing为设置正确的标志。

可编程逻辑器件设计技巧1. 什么是.scf?答:SCF文件是MAXPLUSII的仿真文件, 可以在MP2中新建.1.用Altera_Cpld作了一个186(主CPU)控制sdram的控制接口, 发现问题:要使得sdram 读写正确, 必须把186(主CPU)的clk送给sdram, 而不能把clk经cpld的延时送给sdram.两者相差仅仅4ns. 而时序通过逻辑分析仪测试没有问题. 此程序在xilinx器件上没有问题. 这是怎么回事?答:建议将所有控制和时钟信号都从PLD输出, 因为SDRAM对时钟偏移(clock skew)很敏感, 而Altera的器件PLL允许对时钟频率和相位都进行完全控制. 因此, 对于所有使用SDRAM的设计, Altera的器件PLL必须生成SDRAM时钟信号.要利用SDRAM作为数据或程序存储地址来完成设计, 是采用MegaWizard还是Plug-In Manager来将一个PLL在采用Quartus II软件的设计中的顶层示例?可以选择创建一个新的megafuntion变量, 然后在Plug-In manager中创建ALTCLKLOCK(I/P菜单)变量. 可以将PLL 设置成多个, 或是将输入划分开来, 以适应设计需求. 一旦软件生成PLL, 将其在设计中示例, 并使用PLL的“Clock”输出以驱动CPU时钟输入和输出IP引脚.2.在max7000系列中, 只允许有两个输出使能信号, 可在设计中却存在三个, 每次编译时出现“device need too many [3/2] output enable signal”. 如果不更换器件(使用的是max7064lc68). 如何解决这个问题?答:Each of these unique output enables may control a large number of tri-stated signals. For example, you may have 16 bidirectional I/O pins. Each of these pins require an output enable signal. If you group the signals into a 16-bit bus, you can use one output enable to control all of the signals instead of an individual output enable for each signal. (参考译文:这两个独特的输出使能中每个都可能控制大量三相信号. 例如, 可能有16个双向I/O引脚. 每个引脚需要一个输出使能信号. 如果将这些信号一起分组到一个16位总线, 就可以使用一个输出使能控制所有信号, 而不用每个信号一个输出使能. )3.关于vhdl的问题:process(a, b, c) begin… end process; 如果a、b、c同时改变, 该进程是否同时执行三次?答:PROCESS STATEMENTS 中的执行跟逻辑有关系, 假如是同步逻辑, 则在每次时钟的触发沿根据A, B, C的条件来执行一次;假如是异步逻辑, 则根据判断A、B、C的条件来执行. 一般我们都推荐使用同步逻辑设计4.在设计最初, 由于没有将时钟信号定义在全局时钟引脚上, 导致MAXPLUS II 在时间分析时提示错误:(时钟偏斜加上信号延迟时间超过输入信号建立时间). 全局时钟引脚的时钟信号到各个触发器的延时最小, 有没有可能通过编译软件设置, 将普通I/O脚上的时钟信号也经过芯片内部的快速通道以最小的延迟送到每个触发器时钟引脚?答:you can register that signal and assign it as the global signal, by the step flow: assign->logic option->Individual logic options->Global signal. But you'd better input the clock signal through the dedicated input pin. (参考译文:可以寄存这个信号, 并将它指定为全局信号, 步骤如下:指定—>逻辑选项—>个别逻辑选项—>全局信号. 但是, 最好通过专用输入引脚输入时钟信号. )5.用MaxplusII 软件设计完后, 用Delay Matrix查看延迟时间. 由于内部触发器的时钟信号用了一个输出引脚的信号, 譬如将一引脚ClkOut定义为Buffer, Clkout是一时钟信号, 然后反馈到内部逻辑, 内部逻辑用此信号作为时钟信号, 但用Delay Matrix, 却查看不到一些信号相应于ClkOut的延迟, 因为ClkOut是一Output引脚, 在Delay Matrix source 一栏中没有ClkOut信号, 如何解决这个问题?答:这种做法在逻辑设计中称为GATE CLOCK, 所谓GATE CLOCK就是将设计中的组合逻辑结果拿来做时钟信号, 这是一种异步逻辑设计.现在都推荐使用同步逻辑设计方法. 可以将该信号(CLKOUT)拿来作使能信号, 即ENABLE信号, 而时钟信号还是采用原来的统一时钟, 使设计用尽量少的同步时钟, 这样一来就还是用DELAY MATRIX来分析原有的时钟.6.我是一个epld的初学者, 目前看到xilinx的Virtex-II中嵌入大量的资源如:powerpc、ram 等, 究竟如何在fpga中使用这些资源?答:Xilinx Virtex-II中嵌入的资源非常丰富, 如BlockRAM、Digital Clock Manager、On-chip termination等等. ISE 4.2i软件完全支持这些资源. 可以举出单元库中相应基本数据的实例. Xilinx Core Generator中也还支持BlockRAM等特性. 至于PowerPC和MGT设计, 可以使用Virtex-II Pro开发者套件.7.在设计中, 往往需要对某个信号做一定(任意长)的延时, 有没有好的方法来实现?而不是采用类似移位寄存器的方法来延时.答:使用移位寄存器在FPGA中对信号进行延时是一种好方法. Xilinx Virtex架构中每个对照表(LUT)都能够设置成为具有可编程深度(最多为16)的移位寄存器. 这就提供了一种高效的途径来在FPGA中实现移位寄存器. 无须使用触发器就可以实现一个16位寄存器. 作为一个好的设计习惯, 任何情况下都不要通过闸延迟来实现延迟逻辑.8.ISE中的PAD TO PAD CONSTRAINT 是否是包括输入输出的pad时延之和再加上输入输出之间的组合逻辑的时延?还是只是输入输出之间的组合逻辑的时延?答:Xilinx PAD-to-PAD contraint的确涉及到输入输出PAD时延. 这从布局后时序报告中可以看出.9.由于现在的设计基本上都是同步设计, 那么PAD TO PAD CONSTRAINT 在什么情况下使用?答:虽然现今多数设计都是完全同步, 但仍有一些情况需要从一个输入引脚到另一个输出引脚的纯粹组合路径. 因此, 仍然需要PAD-to-PAD constraint控制这些路径的时延.10.如何在ISE 中看到PAD TO PAD 的布线情况?答:通常不必在意信号在FPGA内的路线, 只要它涉及到时序问题. 这种工具将对以优化的方式对设计进行路由. 如果希望检查具体路由, 可以使用Xilinx FPGA Editor, 它包含在ISE4. 2i软件中.11.在Xilinx Foundation 3. 1i下用JTAG PROGRAMER下载程序到芯片中, 可是总是出现如下错误:If the security flag is turned on in the bitstream, programming status can not be confirmed;others, programming terminated due to error. 测量电路信号, 没有相应的波形, 显然下载没有成功. 所用的芯片是:Xilinx Spartan2 XC2S50TQ144. 怎么解决?答:This is a security feature. By disabling readback, the configuration data cannot be read back from the FPGA. This prevents others from pirating your intellectual properties. You can enable or disable this feature during bitstream generation.The proper way to determine if the configuration is finished without error is to check the status of the DONE pin on the FPGA. DONE pin should goes high if the bitstream is received correctly. Also, since you are using JTAG configuration, please make sure you have selected JTAG clock (not CClk) as your Startup clock during bitstream generation. (参考译文:这是保密功能. 通过禁用回读, 配置数据不能从FPGA回读. 这可以防止其他人盗用你的成果. 在生成位元流过程中, 可以启用或禁用这个功能.确定配置是否准确无误地完成, 适合的方法就是检查FPGA上DONE引脚的状态. 如果正确地接收了位元流, 则DONE引脚将会升高. 而且, 既然使用JFAG配置, 就要确保在生成位元流过程中, 已经将JGAG时钟(而不是CClk)选作了Startup时钟. )12.Xilinx Virtex架构中每个对照表(LUT)都能够设置成为具有可编程深度(最多为16)的移位寄存器. 可否理解为, 在写设计的时候如果设计了一个深度不大于16位的移位寄存器, ISE综合时就会用一个LUT来替代它?答:Most synthesis tools (e. g. Synplify Pro, Xilinx XST) are able to infer LUT based shift register (SRL16E) from your source code. Even for depth greater than 16, the tool is smart enough to infer multiple SRL16E to realize the shift register. Another way to utilize this feature is to instantiate an SRL16E in the source code. You can refer to the Library Guide in the Xilinx ISE software package for more details. (参考译文:大多数综合工具, 例如Synplify Pro和Xilinx XST, 都能根据源代码中的移位寄存器SRL16E来推断 LUT. 即使是深度大于16的情况, 此类工具也能够推断出多SRL16E, 从而实现移位寄存器. 利用此功能的另一种途径是在原代码中例示一个SRL16E. 详细说明可以参考Xilinx ISE软件包中的库指南. )13.LUT是实现组合逻辑的SRAM, 怎样实现一个时序的移位寄存器, 是不是必须加一个触发器来配合LUT?答:The LUTs in Xilinx Virtex architecture are not simply combinational logic. When it is configured as 16x1 RAM, the write operation is synchronous. When it is configured as shift register, there is no need to consume any flip-flop resource. In fact the internal circuitry of a Virtex LUT is more complicated than what it looks like. (参考译文:Xilinx Virtex结构中的LUT不是简单的组合逻辑。

FPGA编程中的常见错误及调试方法在FPGA(Field-Programmable Gate Array)编程过程中,即使经验丰富的工程师也可能会遇到各种错误。

这些错误可能导致设计不稳定、功能异常或性能下降。

因此,了解FPGA编程中常见的错误并学会相应的调试方法非常重要。

本文将介绍几种常见的FPGA编程错误,并提供相应的调试方法。

1. 时序错误时序错误是FPGA设计中最常见的错误之一。

当时序不正确时,FPGA可能无法按照预期的方式工作。

常见的时序错误包括时钟速度不正确、过长的路径延迟以及未正确处理时序约束等。

要调试时序错误,可以采取以下方法:- 确保时钟频率设置正确。

检查时钟输入和输出引脚,确保时钟频率与设计中的要求一致。

- 分析路径延迟。

使用FPGA开发工具提供的时序分析器,分析信号路径延迟,并找到可能引起问题的路径。

- 添加时序约束。

通过为设计添加时序约束,告知FPGA开发工具如何优化时序,以满足设计要求。

2. 逻辑错误逻辑错误是指FPGA设计中逻辑电路的错误,可能导致设计功能不正确。

常见的逻辑错误包括逻辑表达式错误、门级电路错误以及逻辑冲突等。

要调试逻辑错误,可以采取以下方法:- 检查逻辑表达式。

仔细检查设计中的逻辑表达式,确保其正确性。

可以使用模拟工具或仿真器对逻辑电路进行验证。

- 使用约束编码风格。

采用约束编码风格可以防止逻辑冲突和歧义。

例如,使用带有清晰优先级的选择结构而不是使用多个if-else语句。

- 利用重要信号的断言与检查。

在设计中添加断言和检查语句,对设计的关键信号进行验证,并在错误条件下触发警告或停机。

3. 配置错误在FPGA编程过程中,配置错误可能导致FPGA芯片无法正确地加载所需的逻辑配置信息,而无法正常工作。

常见的配置错误包括配置位流不匹配、配置位流损坏以及配置文件错误等。

要调试配置错误,可以采取以下方法:- 检查配置文件。

仔细检查使用的配置文件,确保其正确性和完整性。

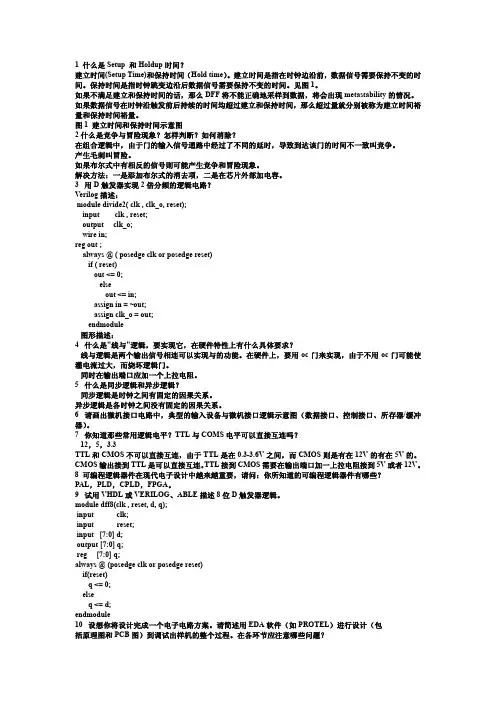

1 什么是Setup 和Holdup时间?建立时间(Setup Time)和保持时间(Hold time)。

建立时间是指在时钟边沿前,数据信号需要保持不变的时间。

保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。

见图1。

如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现metastability的情况。

如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

图1 建立时间和保持时间示意图2什么是竞争与冒险现象?怎样判断?如何消除?在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。

产生毛刺叫冒险。

如果布尔式中有相反的信号则可能产生竞争和冒险现象。

解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。

3 用D触发器实现2倍分频的逻辑电路?Verilog描述:module divide2( clk , clk_o, reset);input clk , reset;output clk_o;wire in;reg out ;always @ ( posedge clk or posedge reset)if ( reset)out <= 0;elseout <= in;assign in = ~out;assign clk_o = out;endmodule图形描述:4 什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?线与逻辑是两个输出信号相连可以实现与的功能。

在硬件上,要用oc门来实现,由于不用oc门可能使灌电流过大,而烧坏逻辑门。

同时在输出端口应加一个上拉电阻。

5 什么是同步逻辑和异步逻辑?同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系。

6 请画出微机接口电路中,典型的输入设备与微机接口逻辑示意图(数据接口、控制接口、所存器/缓冲器)。

FPGA常见的警告以及处理方法1.路由失败警告:路由失败警告可能是由于资源不足或者设计错误导致的。

处理方法包括:a.添加更多的资源或优化资源利用率;b.检查设计中的错误或冲突;c.调整设计中的约束条件。

2.时序约束不满足警告:时序约束不满足警告可能是由于时钟分频错误、时钟抖动、时序路径过长等原因导致的。

处理方法包括:a.检查时钟分频、抖动等问题;b.优化时序路径,减少时序路径长度;c.调整时序约束,放宽限制。

3.信号未驱动警告:信号未驱动警告可能是由于设计错误或者信号漏洞导致的。

处理方法包括:a.检查设计中的信号是否正确连接;b.确保所有的输入和输出信号都经过合适的逻辑处理;c.优化设计结构,避免信号漏洞。

4.逻辑冗余警告:逻辑冗余警告可能是由于设计中存在多余的逻辑、冗余的操作等原因导致的。

处理方法包括:a.优化设计,删除多余的逻辑;b.减少冗余的操作,简化逻辑功能。

5.存储资源不足警告:存储资源不足警告可能是由于存储器资源不足或者使用不当导致的。

处理方法包括:a.优化存储器资源利用率,减少存储器的使用;b.添加更多的存储器资源。

6.时序路径延迟不一致警告:时序路径延迟不一致警告可能是由于时钟频率不均匀或者时钟分配错误导致的。

处理方法包括:a.检查时钟频率,确保时钟频率的均匀分布;b.重新分配时钟,避免时钟频率过高或过低。

7.电源/地引脚警告:电源/地引脚警告可能是由于电源或地引脚连接错误、电源噪声等原因导致的。

处理方法包括:a.检查电源和地引脚的连接是否正确;b.检查电源噪声问题,减少噪声干扰。

8.IP核版本不匹配警告:IP核版本不匹配警告可能是由于IP核版本不兼容导致的。

处理方法包括:a.更新IP核版本,确保版本兼容;9.建议使用异步复位警告:建议使用异步复位警告可能是由于设计中缺少异步复位电路导致的。

处理方法包括:a.添加异步复位电路,确保设计在复位时正常工作。

10.高温警告:高温警告可能是由于FPGA工作温度超过限制导致的。

近来在用NIOS2完成一个项目,遇到一个奇葩问题:前些天,用Quartus II 11.0 配合Qsys搭建了NIOS2 Project,程序调好了,打算用板子上的EPCS64N 固化一下代码。

首先,把NIOS2的Reset Vector设置为EPCS基地址,EPCS基地址则配置为0x00,然后在NIOS2中导出EPCS的四个引脚DCLK,SDO,SCE,DATA0并且连接和分配,再把Dual-Pourpose Pin 都设置为Regular I/O Pins。

然后使用的是EDS 11.0,用EDS 11.0的NIOS2 Flash Programmer,可以识别CPU ID(Name ,Timestamp都OK),发现可以正常擦出和烧写程序,但是……奇怪的事情是,Run as Hardware NIOS2 程序可以正常运行。

EDS11 Flash Programmer 烧写之后,FPGA的硬逻辑部分可以正常运行,NIOS2 的软逻辑(ELF文件生成的flsh)部分却始终无法执行,断电重启,复位都不好使,心拔凉拔凉的……按照别人帖子和Altera官方的JIC格式转化下载,同样还是NIOS2逻辑无法运行,以至于整个人都不好了。

后来发现很多人都遇到这个奇葩问题,开始怀疑是软件的bug(因为不少人提到),后来把Quartus 11,12.1,13.0都遍历一个遍,还是没有解决……今天,决定不用Quartus 11 的Qsys了,随便用SPPC Builder配置了一个系统,发现竟然可以烧写了成功了,NIOS2程序部分可以正常执行了……这尼玛太让我抓狂了……我感觉是Qsys有bug,为毛SOPC下使用NIOS2 IDE就可以正常烧写,这说明我的硬件没有问题。

唯一区别就是,SOPC的ECPS可以正常烧写和启动,但是Qsys搭建的系统在EPCS烧写下就boot不起来了……Nios II下载程序到串行配置芯片EPCS方法:1 在SOPC Builder内添加epcs_controller模块,将cpu的reset地址设置在epcs_controller上2 重新编译Quartus3 在Nios II IDE里将system library的Program memory(.text)和Read_only data memory(.rodata)设置为onchip_mem或者sdram,编译。

Implementation and Timing of Reset Circuitsin Altera FPGAsABSTRACTMost circuit designs employing FPGAs and ASICs are synchronous systems using a largenumber of flip-flops or registers. It is usually important that these synchronous elementsare capable of starting or being returned to a known state (logic ‘1’ or ‘0’). This functionis normally handled by a reset. There are usually one or more reset signals that arebrought into the device and used, alone or in conjunction with additional circuitry toperform this function. This Tech Note examines the various types of resets; synchronous,asynchronous, and synchronized asynchronous with respect to their advantages anddisadvantages, various techniques of implementation in FPGAs, and their proper timinganalysis in Altera’s TimeQuest timing analysis engine.Synchronous circuits are typically reset with one of two types of resets; synchronous or asynchronous resets. Synchronous resets are frequency synchronous with the clock domain of the registers they reset. Asynchronous resets by nature will arrive at the registers they are affecting with a non-deterministic timing relationship to the clock domain of the registers. Because of this, it is difficult to time these types of resets.A third category or resets is discussed here which, for the lack of a better name, will be referred to as synchronized asynchronous resets. These resets have some of the benefits of synchronous resets without some of their disadvantages, and they also avoid some of the pitfalls that can be associated with purely asynchronous resets. As shall be shown, for most situations, synchronized asynchronous resets are the preferred method when designing FPGA circuits.Synchronous ResetsSynchronous resets are based on the premise that the reset signal will only affect the state of a register on the active edge of the clock signal to that register. Synchronous resets have the advantage that they generally insure that the circuit is 100% synchronous. They also have the advantage that they can be easily timed with static timing analysis tools such as the Altera® Quartus® II TimeQuest timing engine. Since the reset signal is launched and latched by clocks that are synchronous to each other, the Data Arrival and Data Required times can be easily determined for proper slack analysis. Another advantage of synchronous resets is that they can be much easier to work with when using cycle-based simulators.These resets do have their disadvantages however. For example, they may require pulse stretchers to guarantee a reset pulse width wide enough to ensure reset is present during an active edge of the clock. Perhaps even more importantly, these resets require a clock in order to reset a circuit. If something is causing the launch clock to fail, the resulting circuit will not get the reset.In Altera FPGAs, there are two methods by which a reset can reach a register; either by being gated in with the data input (see Figure 1), or by using a LAB-wide control signal, synclr (see Figure 2). The first method has the potential disadvantage that an additional gate delay may have to be added to the circuit to accommodate the reset signal causing increased Data Arrival times. In that event, it would have a negative impact on setup slack. The second method relies on dedicated routing in the Logic Array Block (LAB) to each register, but is also slower than an asynchronous reset would be to the same register. Figure 3 shows that the path for synchronous clear traverses an AND gate, whereas the asynchronous clear path goes directly to the register.1 In addition, there is only one synchronous synclr control signal per LAB, but there 1 In fact, this path is slightly slower than the path through the LC. The potential advantage of the LAB-wide synclr is to save on LCs.Version 1.0 Page 1 of 17 Q4’08are two asynchronous labclr control signals per LAB. Using a large number of synchronous resets in a design can cause the fitter to run out of LABs due to this. However, without the use of these LAB-wide synchronous clear signals, the logic cell (LC) utilization could increase. These are the tradeoffs that must be made when using synchronous resets in FPGAs. Fortunately, Quartus II does offer some control over which of these two methods will be used. This can be controlled on a global level, or on a module (entity) level, but not on an individual register level.2 There are two settings that can be assigned in the Assignment Editor: ALLOW_SYNCH_CLEAR_USAGE and FORCE_SYNCH_CLEAR. The first setting will allow the synthesis engine to use the LAB-wide synchronous clear signal when needed, and the second one forces the tool to always use it. Either way, synchronous resets will be slower than asynchronous resets and are not the preferred method in FPGAs.Figure 1: Synchronous Reset Using Logic CellFigure 2: LAB-Wide Control Signals [Stratix® III FPGAs]2 One could control this on an individual register basis by controlling the source code and by using a synthesis directive to force the tool not to optimize out the gate in front of the register.Figure 3: Adaptive Logic Module (ALM) Details [Stratix III FPGAs]When examining the timing analysis of synchronous resets, there are two types that need to be addressed; externally synchronized and internally synchronized. Externally synchronized resets are synchronized tothe clock domain outside the FPGA. These are not very common.Figure 4: Schematic for Externally Synchronized ResetAn example of an externally synchronized reset is shown in Figure 4. A power-on asynchronous resetpor_n is dual-rank synchronized externally to the system clock and then brought into the FPGA. Inside the FPGA, this reset is gated with the data input to the registers to implement a synchronous reset. Figure 5 shows the Verilog equivalent of the schematic. The important thing to note here is that when using synchronous resets, the reset signal is not put in the sensitivity list as it would be for an asynchronous reset.Figure 5: Verilog Code for Externally Synchronized ResetThe constraints for this design are shown in Figure 6. Since the external reset is synchronous, one only needs to constrain the reset_n signal as a normal input signal with a set_input_delay statement.Figure 6: SDC Constraints for Externally Synchronized ResetMore often, resets coming into the device are asynchronous. In this case, the resets must be synchronized internally before being sent to the registers. As shown in Figure 7, the synchronization registers are now inside the FPGA.Figure 7: Schematic for Internally Synchronized ResetThe equivalent Verilog code is shown in Figure 8. Again, note that only the clock edge is in the sensitivity list for a synchronous reset.Figure 8: Verilog Code for Internally Generated ResetThe SDC constraints are similar to the external case except that now the input reset cannot be constrained since it is asynchronous, and should be cut with a set_false_path statement as shown in Figure 9 to avoid these being considered unconstrained paths.Figure 9: SDC Constraints for Internally Synchronized ResetAnother issue with synchronous resets is their behavior with respect to short pulses (less than a period) on the asynchronous input to the synchronizer flip-flops. On the one hand, this could be viewed as a disadvantage in that there is a requirement on the asynchronous reset that it be at least one period wide in order to guarantee that it will be captured by the first flip-flop. On the other hand, this could be viewed as an advantage in that this circuit increases noise immunity. Spurious pulses on the asynchronous input would have a lower chance of being captured by the first flip-flop, so they would not trigger a synchronous reset. In some cases, one might want to increase noise immunity further and reject any asynchronous input reset that is less than n periods wide. This would also be useful for debouncing an asynchronous input reset. In order to do this, the following modification (Figure 10) should be made to the internally synchronized reset:Figure 10: Schematic for Internally Synchronized Reset with Pulse ExtenderMany designs have more than one clock signal. In these cases, a separate reset synchronization circuit should be used for each clock domain in the design. When PLLs are involved, extra caution should be used. When creating synchronizers for the PLL output clocks, these clock domains will not be reset until the PLL has locked and the PLL output clocks are stable. Also worth noting, if the reset to the PLL is used, this reset does not have to be synchronous to the input clock to the PLL. An asynchronous reset can be used for this. Again, using a reset to the PLL will further delay the assertion of a synchronous reset to the PLLoutput clock domains when using internally synchronized resets. As will be demonstrated in a later section of this document, synchronized asynchronous resets solve this problem rather nicely.Asynchronous ResetsAsynchronous resets have been the most common form of resets used in circuit design for a very long time. It has been very popular to have one asynchronous reset come into the device and then put on a global buffer and connect to the asynchronous reset pin of every (or almost every) register in the device. This approach has its advantages under certain circumstances, but it is not without pitfalls. It is not always the case that every register in a design requires a reset. This approach is not without its costs in terms ofrouting resources and use of LAB-wide control signals. It is good practice to only reset those registers that require it.One of the biggest advantages of asynchronous resets is that they are not inserted in the data path as synchronous resets are. Hence, they do not negatively impact the data arrival times between registers. Another advantage is that they take effect essentially immediately. As soon as the registers get the reset pulse, regardless of the timing relationship relative to the clock, the registers are reset. It is not dependent on a clock as synchronous resets are.There isn‟t any problem with going into reset asynchronously. Problems can arise however when the reset is released, also referred to as “reset removal ”. When reset is removed, it must meet the asynchronous µt SU time. This is checked in TimeQuest with a Recovery time check. Also, when reset is removed, it must meet the asynchronous µt H time. This is checked in TimeQuest with a Removal time check. Together, these checks are referred to as Recovery/Removal Analysis.3clockµt COreset_nMetastability ZoneFigure 11: Metastability CurveWhen the reset signal is deasserted and does not pass the recovery or removal time check, the edge is said to have fallen in the metastability zone as shown in Figure 11 above. The consequence of this is that the time it takes for the output of the register to settle to the correct state (based on the data input to the 3 For further information on this topic, refer to Tech Note : Understanding Recovery/Removal Analysis in TimeQuest.register) is increased. This additional delay can lead to setup time failures to registers downstream, leading to system failure. Obviously, this situation should be avoided at all costs.One method of avoiding this is to add a couple of follower registers after the register with the asynchronous reset and use the output of these registers in the design. The follower registers act to synchronize the data to the clock in a manner to remove the metastability issues. The closer these registers can be placed to each other in the device, the better to keep the routing delays to a minimum, which decreases data arrival times and increases MTBF. Note that it is important that these follower registers themselves are not reset, but rather will be initialized over a period of several clock cycles by “flushing out” their current or initial state. Figure 12 below shows a schematic example of this circuit.Figure 12: Schematic of Asynchronous Reset with Follower RegistersIn general, for pipelined designs like this without feedback circuits where there is no sequence dependence on initialization, and when the design can wait several cycles after coming out of reset before beginning operation, this type of reset is acceptable.The equivalent Verilog code is shown in Figure 13 below. Note how this differs from the synchronous reset code. The active edge of the reset is now in the sensitivity list for the procedural block. It is also important that the follower register s are not in the “else” part of the first procedural block as this would infer a clock enable on the follower registers with the inverse of the reset signal tied to the clock enable. The follower registers should be in a separate procedural block as shown using non-blocking assignments.Figure 13: Verilog Code of Asynchronous Reset with Follower Registers Constraining an asynchronous reset is simple. By definition, asynchronous resets have a non-deterministic relationship to the clock domains of the registers they are resetting. Therefore, static timing analysis of these resets is not possible; they are usually cut with a set_false_path statement (as shown at the bottom of Figure 14). Because the relationship of the reset to the clock at the register is not known, recovery and removal analysis cannot be run in TimeQuest for this path. Attempting to do so will yield no paths reported. Even without the false path statement cutting this path, no paths would be reported for recovery and removal.Figure 14: SDC Constraints for Asynchronous ResetBesides the potential metastability issues with asynchronous resets, another issue is their susceptibility to noise. A noisy asynchronous reset could cause a spurious reset. For this reason, it is important that the asynchronous reset is debounced and filtered. As mentioned previously, synchronous resets are less susceptible to this problem (although not immune) because they are registered by the clock. In the next section on Synchronized Asynchronous Resets, methods are discussed for avoiding this problem altogether. Perhaps the biggest problem with asynchronous resets is again related to reset removal. Besides the potential for metastability issues, there is no guarantee that every register connected to the reset will have the same timing relationship to the clock due to register placement and routing within the device. The effect of this is that within a given clock period, some registers w ould come out of reset while others won‟t until the following clock period. This has the potential for disastrous effects with feedback circuits where the next output of a register is dependent on the current output of other registers. A common example of this is with state machines. One-hot state machines are particularly problematic since only one state bit is set at a time. If more than one state bit is high due to some state bits coming out of reset and not others, then the state machine could enter an illegal state.4 With binary encoded state machines, it is possible to create transitions for unused states back to the reset state, this making it a deterministic state machine. This would allow for graceful recovery from an illegal or unused state.4Fortunately, one of the Synthesis settings available now is called “Safe State Machines” that will gracefully recover from an illegal state. However, this setting is OFF by default and would have to be turned ON to take effect.Despite the potential for recovery from these cases, they should be avoided whenever possible. One method for avoiding them all together is to use a different reset scheme, referred to as Synchronized Asynchronous Resets, which are discussed in detail in the next section.Synchronized Asynchronous ResetsIn order to avoid some of the problems associated with purely synchronous resets and purely asynchronous reset, a third class of reset called Synchronized Asynchronous Resets can be used. These resets combine the advantages of asynchronous resets (no involvement of the data path for speed and taking effect almost instantaneously) with the advantages of synchronous resets (100% synchronous for timing analysis and resistance to noise). These resets are asynchronously asserted and synchronously deasserted to achieve these goals. As discussed previously, going into reset asynchronously is fine, but coming out of reset asynchronously leads to potential problems with metastability and hazards of unwanted situations with synchronous circuits involving feedback.Some of the methods of implementing these resets are discussed below. The circuit shown in Figure 15 uses synchronizer registers in a similar manner to synchronous resets, but the asynchronous reset is gated with the output of the registers to assert the resulting reset asynchronously. This circuit will assert the reset asynchronously and deassert it asynchronously; however, it has the disadvantage that there will be a gate delay in the resulting reset path.Figure 15: Schematic of Synchronized Asynchronous Reset with Gated ResetA better way to implement this is shown in Figure 16. This takes the gate delay out of the path of the resulting reset. The asynchronous reset input is connected directly to the CLRN pin of the synchronizer registers asserting the resulting reset immediately. When the reset is dea sserted, a logic …1‟ is clocked though the synchronizers to deassert the resulting reset synchronously.Figure 16: Schematic of Synchronized Asynchronous Reset without Gate DelayThe equivalent Verilog code is shown below in Figure 17. The first procedural block creates the synchronized reset rst_n which then becomes the asynchronous reset for the second procedural block. Inboth of these blocks, the active edge of the reset is used in the sensitivity list.Figure 17: Verilog Code for Synchronized Asynchronous ResetAgain, in order to minimize metastability effects between the two synchronization registers and to increase MTBF, these registers should be located as close as possible in the device to minimize routing delay. The Quartus II Fitter will recognize these registers as synchronizers and do this automatically. In this example, they are both placed within the same LAB.While the input reset signal reset_n still must be cut with a set_false_path command, the reset that comes from the synchronization registers rst_n can now be timed in TimeQuest with Recovery and Removal Analysis. The SDC file to constrain this design is identical to the one shown in Figure 14. Compiling thisdesign in Quartus II and running TimeQuest timing anaylsis will now yield the Recovery and Removal slacks as shown in Figure 18.Figure 18: Recovery and Removal Analysis of Synchronized Asynchronous ResetThe results show that both paths (reg4 to reg1 and reg4 to reg2) are checked for both Recovery and Removal. The Recovery time check (similar to Setup time check) has almost 9 ns of slack in this example, and the Removal time check (similar to Hold time check) has less than 1 ns of slack. Both checks pass, and there are no failing paths in this example design.One of the prices paid for the instantaneous assertion of the Synchronized Asynchronous Resets is that they are susceptible to noise and runt pulses. Again, the asynchronous reset should be debounced and filtered before it enters the device if possible. The circuit in Figure 16 guarantees that the Synchronized Asynchronous Reset will be at least one full clock period in length. In order to extend this time to n clock periods, increase the number of synchronizer registers to n + 1. Be sure to connect the asynchronous input reset reset_n to the CLRN pin of all the synchronizer registers in order to maintain the asynchronous assertion of the Synchronized Asynchronous Reset.Figure 19: Schematic of Incorrect Implementation of Synchronized Asynchronous Reset with PLL Special considerations are needed when PLL clocks are involved. Consider the circuit in Figure 19 above. The synchronized reset is connected to the CLRN of the registers reg1 and reg2 as before, and is also connected to the areset pin of the PLL. The clock used to clock all of the registers, including the synchronizer registers, is the output clock from the PLL. While it might seem to make sense to use the synchronized reset to the P LL, this actually won‟t work. When the PLL is in reset, no clock comes out of the c0 output, and hence the synchronizer registers will not be able to clear the reset. As a result, this circuit will never come out of reset!Figure 20: Schematic of Correct Implementation of Synchronized Asynchronous Reset with PLLTo fix this, the reset to the PLL should be reset with the (in this case inverted) input reset_n instead of the synchronized reset. In addition, it is good practice to use the locked output from the PLL as a clock enable for the synchronizer registers. This will prevent the synchronized reset from going away before the clock from the PLL has stabilized.The Verilog equivalent of this schematic is shown in Figure 21.Figure 21: Verilog Code for Synchronized Asynchronous Reset Circuit with PLLNote that the procedural block for the synchronizer registers now has a conditional on the locked signal, which synthesizes to a clock enable on the registers. Also notice the PLL instantiation near the bottom and that the clock for the second procedural block is now the output clock from the PLL, pll_clk. These are the only changes required when adding a PLL to the circuit.Figure 22: SDC Constraints for Synchronized Asynchronous Reset with PLLThe timing constraints shown in Figure 22 are similar to the case without the PLL, except that now a create_generated_clock statement must be added for the PLL output clock.5There is one more case that is worth mentioning. As discussed previously, each clock domain in a design that requires registers to be reset should have its own set of synchronizer registers. Sometimes it may be necessary to release different parts of the design from reset before others. In this case of ordered reset removal, the synchronizer registers can be chained in the manner shown below with the highest priority reset at the top coming out first. In Figure 23 below, all resets are asserted at the same time, but rst_a_n is the highest priority and comes out of reset first, followed by rst_b_n at medium priority, and lastly followed by rst_c_n coming out of reset last. Of course if longer periods of time are required between reset removals, the number of registers in the synchronizer can be increased to any length.Figure 23: Prioritized Reset Removal of Synchronizer RegistersSummaryThis Tech Note describes the advantages and disadvantages of the various types of resets: synchronous, asynchronous, and synchronized asynchronous. Synchronous resets require a clock, and thus short reset pulses could be missed; however, this also gives them better noise immunity. They are 100% synchronous so metastability is not an issue, but they consume extra resources and add delay to the data path. For this reason, synchronous resets are not usually the best option. Synchronous resets are timed in TimeQuest like any other data path.5 Notice in this example and all of the SDC constraints used in the examples in the document, only the inputs and the internals have been constrained for simplicity.Asynchronous resets are immediate, easy to implement, and are the fastest since they do not involve the data path. They also consume the least amount of resources. Unfortunately, they cannot be timed in TimeQuest (or any other static timing analyzer) and can lead to metastability issues if not handled properly. The biggest drawback to asynchronous resets is the fact that they cannot guarantee that all registers will come out of reset on the same clock edge. This is problematic for synchronous designs with feedback, such as state machines.Adding a synchronizer to the reset before bringing it to the asynchronous input to the registers creates synchronized asynchronous resets. These resets provide the immediate assertion advantage of asynchronous resets as well as increased speed since the data path is not involved. They also avoid the metastability issues and will guarantee all registers come out of reset on the same clock edge similar to synchronous resets. Unlike asynchronous resets, they can be timed in TimeQuest using Recovery and Removal analysis. It is for these reasons that for most FPGA designs, synchronized asynchronous resets are usually the preferred method to use.References[1] Clifford E. Cummings and Don Mills; “Synchronous Resets? Asynchronous Resets? I am soconfused! How will I ever know which to use?”; SNUG San Jose, 2002 User Papers;/papers/CummingsSNUG2002SJ_Resets.pdf[2] Clifford E. Cummings, Don Mills, and Steve Golson; “Asynchronous & Synchronous Reset DesignTechniques –Part Deux”; SNUG Boston, 2003 User Papers;http://ens.ewi.tudelft.nl/Education/courses/et4351/CummingsSNUG2003Boston_Resets.pdf[3] Richard Katz; “Reset Circuit Topologies”; 2004 MAPLD International Conference,/mapld04/tutorials/vhdl/presentations/reset_circuit_topologies.ppt。

说明:本文内容来自网络1.Error (10028): Can't resolve multiple constant drivers for net ……解析:不能在两个以上always内对同一变量赋值,这个细节一般看书看资料会看到,但是编程时,就是没想到。

2.Error (10158): Verilog HDL Module Declaration error at clkseg.v(1): port "XXXX" is not declared as port解析:大意了,端口类型还没定义啊!3.Error (10110): variable "en" has mixed blocking and nonblocking Procedural Assignments -- must be all blocking or all nonblocking assignments解析:en在程序中有时用非阻塞赋值,有时用阻塞赋值,这是禁止的。

在初学的时候,可能分得不是很清楚,所以在检查时,一定要一步步观察慢慢来。

4.Error (10161): Verilog HDL error at clkseg.v(36): object "count" is not declared解析:这个错误应该很明显啦,只要能读得懂。

5.Error (10170): Verilog HDL syntax error at clkseg.v(37) near text "***"; expecting ";"解析:意思应该也很简单,就是检查的时候要细心点。

6.Error (10171): Verilog HDL syntax error at ir_ctrl.v(149) near end of file ; expecting an identifier, or "endmodule", or a parallel statement解析:最后上了endmodule。

Cyclone II系列FPGA器件问答1.问:Cyclone II系列器件是什么?答:Cyclone II系列器件是Altera低成本Cyclone系列的第二代产品,Cyclone II FPGA 的成本比第一代Cyclone 器件低30%,逻辑容量大3倍多。

Cyclone II器件采用TSMC 经验证的90nm 低K 绝缘材料工艺技术,是业界成本最低的FPGA。

Cyclone II 器件容量有4608~68416个逻辑单元,还具有新的增强特性,包括多达1.1Mbit的嵌入存储器、多达150个嵌入18×18乘法器、锁相环、支持外部存储器接口及差分和单端I/O标准。

2.问:Cyclone II器件系列采用什么样的工艺技术?答:Cyclone II器件系列是采用TSMC的1.2V、90nm、低K 绝缘材料工艺。

3.问:Cyclone II器件系列满足了哪些市场的需求?答:Cyclone II器件系列是多种不同市场上大批量应用最优的低成本方案,包括消费电子、电信和无线、计算机外设、工业和汽车。

Cyclone II器件包含了许多新的增强特性,如嵌入存储器、嵌入乘法器、PLL和低成本的封装,这些都为诸如视频显示、数字电视、机顶盒、DVD 播放器、DSL调制解调器、家用网关和中低端路由器等批量应用进行了优化。

4.问:为什么Cyclone II 器件是ASIC 理想的替代方案?答:Cyclone II系列提供了一种灵活的无风险的,且没有前期一次性工程费用或最小定货量的开发方式。

Cyclone II器件除了具有其它任何FPGA 无可匹敌的成本结构之外,还具有先进的特性,如用于高性能数字信号处理应用的嵌入式18×18乘法器和支持如DDR2(高达334Mbps)和QDRII(高达688Mbps)的存储器接口。

5.问:Cyclone II器件有哪些产品,提供哪些封装?答:Cyclone II系列包括6种器件,容量从4608~68416个逻辑单元。

FPGA常犯错误集锦1) QuartusII对代码进行时序仿真时出现Error: Can't continue timing simulation because delay annotation information for design is missing.原因:如果只需要进行功能仿真,不全编译也是可以进行下去的,但时序仿真就必须进行全编译(即工具栏上的紫色实心三角符号那项)。

全仿真包括四个模块:综合器(Synthesis)、电路装配器(Fitter)、组装器(Assember)和时序分析器(Timing Analyzer),任务窗格中会有成功标志(对号)。

2) 在下载运行的时候,出现下面的错误:Warning: The JTAG cable you are using is not supported for Nios II systems. You may experience intermittent JTAG communicationfailures with this cable. Please use a USB Blaster revision B.在运行之前已经将.sof文件下载到开发板上面了,但是依然出现上面的问题。

解决:在配置的时候,在run之后,进行配置,选择target connection,在最后一项:NIOS II Terminal Communication Device中,要选择none(不要是Jtag_uart)如果采用USB Blaster,可以选择Jtag_uart。

之后再run就ok了!3)Error: Can't compile duplicate declarations of entity "count3" into library "work"此错误一般是原理图文件的名字和图中一个器件的名字重复所致,所以更改原理图文件的名字保存即可。

常见问题汇总1. alt2gxb模块的每个发送端都需要一个高速的pll_inclk时钟(至少100M以上),请问这个时钟一定要从FPGA外面引进来吗?通常情况下一定要从FPGA外面引进来,首选是GXB模块的专用时钟引脚,或上下BANK 的专用时钟输入脚。

时钟是至少60M以上。

2. 如果我一个FPGA里面有多个alt2gxb模块,是否能共用一个这样的输入时钟?可以。

3. gxb模块里面的Calibration clk 是干嘛用的,能不能不用它?校准内部匹配电阻用。

此时钟可以内部提供,频率在10M到125M都可以,如果外部时钟不合适的话,甚至可以用逻辑来分频(比如参考钟是156M,内部触发器作个2分频就可以用了。

4. 用到gxb模块的bank的参考电压是否必须接1.5V?因为我看到资料上有3.3V的CML和LVDS电平(附件里面的截图)gxb用1.5V 或 1.2V, 推荐客户用1.5V. 3.3v是用在别的普通bank的。

5. gxb模块的输入端如果平时不需要传数据,是否置0?还是需要我们在数据线上发送别的数据,是否gxb模块能自动发送同步码?平时可以置0,但在上电后,你必须首先发送对端接收侧的word aligner码型(通常用k28.5), 这是需要手工控制的。

6. LVDS模块没有同步码,做接收时好像没办法数据对其,比如8比特数据容易错开2、3位,我们现在是另外加逻辑把它调整过来的,请问有别的好的同步的方法吗通常需要逻辑去进行word aligner操作,如同GXB一样。

某些特定情况下可以预先知道边界。

这个问题讨论过好多次了,所谓的特定情况你可以看STRATIX II手册(不是Stratix II GX 手册),搜索“Differential I/O Bit Position”7.请问在alt2gxb模块,有两个时钟:pll_inclk和cali_clk,手册上说cali_clk要求不是很高,可以用计数器产生,那么输入的并行数据txdata_in应该用哪个时钟锁存呢?cali_clk仅用于校准内部匹配电阻用的状态机,跟业务是完全独立的。

txdata_in应该用tx_clkout锁存。

8.pll_inclk可不可以用内部锁相环产生,然后输出经过一个差分时钟驱动,再送到gxb所在bank的REFCLK引脚?或者直接内部锁相环产生,直接送给gxb模块使用?出于时钟质量考虑,我们不推荐用FPGA内部的锁相环来提供GXB的参考时钟,尤其是2SGX工作在3Gbps以上时。

速率低时如果客户一定要用PLL级联,在quartus.ini文件(注意该文件不是自动产生的,需要用户自己创建,放在当前工程根目录下)中包含下面这句话,如你描述的通过外部走线绕一下提供参考时钟没有必要。

siigx_allow_pll_cascade_to_tx_pll=on9.在仿真时我直接加入激励数据给发送模块,它的串行输出再直接复制给接收模块,可是没有任何结果,请问有没有一种有效的仿真方法来仿真alt2gxb模块?仿真时你需要激励一下powerdown信号,起始给高电平,过一会儿拉低。

同时提供准确频率的参考时钟。

10.如果某个bank用到了LVDS模块,是不是这个bank的参考电压应该接2.5V,而IO电压仍然3.3V?对lvds, IO电压是3.3V,参考电压不需要提供11. 我在130 II gx里面放了几个GXB模块,设置的是100M输入时钟,数据率4G,线宽是32位,这样模块就没有rx_outclk这个信号线了,那么receiver的输出数据靠哪个时钟来锁呢?你把rate matcher那个功能取消掉就可以由rx_outclk的输出了12. 还有综合的时候报错说:CRU output frequency 2398.1M of the receiver PLL of GXB receiver channel atom .... must be in the frequency range of 310.9M to 1564.9M请问这个问题怎么解决?因为客户选的是C5,Transceiver速率到不了4G。

详见IIGX Handbook Table 6-6和Table 6-713、如果GXB的引脚硬件上p\n画反了怎么办?在软件中设置下面管脚可以控制p\n的极性。

14、GXB输出电平是什么标准?跟光收发器怎么接?GXB输出为1.5V PCML电平,与LVPECL不同,LVPECL支持速度一般不高,<2Gbps,CML适用于高速场合。

通过交流耦合,可以和LVDS、LVPECL、3.3V PCML接口相连。

跟光收发器间需要加交流耦合,跟距离无关,主要是隔直流,使得GXB和光收发器可以独立供电;对光收发器接口没有特殊要求。

15、IIGX设计时,电源用多大的合适?客户用EP2SGX90EF1152C5,核电压和IO电压分别用3A线性电源供电,不过他只用了一路光纤,逻辑资源也用的不是很多。

用EP2SGX130GF1508C5时,7路光纤3.125Gbps,资源按80%,EPE估算结果为7W 多,客户按10W设计。

详细数据见“D:\资料\Altera\datasheet\总结\功耗估算”。

16、仿真时是否可以设置字节对齐字符为任意字符?可以,不过需要选择Flip word alignment pattern bits。

如果选择了8B/10B编码还是建议选择标准K码。

17、数据8bits,速率2Gbps,那加了8B/10B后速率是多少呢?速率还是2Gbps,但是效率变为80%,因为加了2bits的开销。

18、使用GXB时,发送数据前是不是必须发Control Pattern,应该发多少个?Yes. It's depend on how many frequency offset (sucha as +/-100ppm or +/-300ppm) you want to compensate, this is included in the protocol specification.19、Skip pattern和Control pattern有何区别?You can refer to data sheet for details. In following picture, K28.5 is control pattern and K28.0 is skip pattern.20、接收时,PLL和参考时钟何时匹配?详见IIGX Transceiver User Guide 2-6321、用语言调用GXB,Fit始终报下面错误:Error: Can't place input pin "rx_datain_1" in Pin_E1 because the pin is not connected to GXB Transceiver logic but the location is GXB Receiver pin.Error: The node "rx_datain_1" is connected to or is part of a gigabit transceiver that must be placed into region "CUSTOM_REGION_X62_Y0_X62_Y37". However, your location assignment "PIN E1" is incompatible.Error: Can't place input pin "rx_datain_1" in Pin_E1 because the pin is not connected to GXB Transceiver logic but the location is GXB Receiver pin.Error: Can't fit design in deviceYou don't use any output of the GXB receiver side, so the receiver is synthesized off. Please use virtual pin or STP file to reserve the GXB receiver.22、导致 rx_pll_locked=0的是输入时钟不好还是电路板上没有串行数据输入(或串行输入数据不好)?注意gx器件的rx pll和rx cru是共用一个VCO的。

在正常情况下(自动模式),上电后,VCO会先锁定参考时钟,rx_pll_locked变高之后,VCO会切换到锁输入数据状态,此时rx_freqlocked会变高。

当VCO锁定在输入数据时,也就是rx_freqlocked信号是高电平时,VCO的频率跟本地参考时钟的频率没有本质关系了,所以rx_pll_locked失去了意义了,无论高或低不代表任何含义。

用户只需要关心rx_freqlocked信号能否稳定在高电平,稳定在高电平表示输入数据能够正确锁定,如果rx_freqlocked在高低变化,说明输入数据还没有锁定,可能时没有串行数据输入或者数据不好。

rx_pll_locked通常情况下不需要去关心,只有rx_freqlocked无法稳定在高电平,用户又认为输入数据是好的的情况下,可以采用手动模式,强行把vco锁定在参考时钟上,来观察rx_pll_locked信号,作为一种问题定位的辅助手段。

23、 GXB的复位信号应该如何给?24、EP2SGX90EF1152和EP2SGX60EF1152在QII7.2做Migration时,显示如下(IIGX90在前),L9竟然是NC。

查阅pin定义后发现,从06-08-10的1.3版本开始,IIGX90已经将L9更改为VCCA了,并有注释(3):Prior designs using the F1152 packages which assign L9 or W12 as NCs do not require any modification to the board. Assigning VCCA to L9 and W12 is required for future designs with the need for vertical migration。

说明QII7.2中L9显示的有问题,需要特别注意!25.请问是否有预加重和均衡的参数调试指导手册?或者对通常应用的经验值参考?The settings of preemphasis and equalization are depended on the channel attenuation. No common setting for individual case.You must use scope to adjust the preemphais, or simulate it to get the right preemphasis and equalization value.Altera just released the "Plug & Play Signal Integrity" which enable the ADCE in SIIGX, then the customer doesn't need to set the equalization manually. You can refer to webpage:/technology/signal/ppsi/sgl-plug-and-play-si.html(08年后新的技术问题)26、关于JIC文件的加载:由于JIC文件可以通过JTAG口加载到EPCS中,可以省掉AS 插座,对于电路板面积比较紧张的工程很有帮助。