华中科技大学Verilog语言实验报告

- 格式:docx

- 大小:1.11 MB

- 文档页数:31

西安邮电大学Verilog HDL大作业报告书学院名称:电子工程学院学生姓名:专业名称:电子信息工程班级:实验一异或门设计一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容my_or,my_and和my_not门构造一个双输入端的xor门,其功能是计算z=x’y+xy’,其中x和y为输入,z为输出;编写激励模块对x和y的四种输入组合进行测试仿真1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真实验描述如下:module my_and(a_out,a1,a2);output a_out;input a1,a2;wire s1;nand(s1,a1,a2);nand(a_out,s1,1'b1);endmodulemodule my_not(n_out,b);output n_out;input b;nand(n_out,b,1'b1); endmodulemodule my_or(o_out,c1,c2);output o_out;input c1,c2;wire s1,s2;nand(s1,c1,1'b1);nand(s2,c2,1'b1);nand(o_out,s1,s2); endmodulemodule MY_XOR(z,x,y);output z;input x,y;wire a1,a2,n1,n2;my_not STEP01(n1,x);my_not STEP02(n2,y);my_and STEP03(a1,n1,y);my_and STEP04(a2,n2,x);my_or STEP05(z,a1,a2); Endmodulemodule stimulus;reg X,Y;wire OUTPUT;MY_XOR xor01(OUTPUT,X,Y);initialbegin$monitor($time,"X=%b,Y=%b --- OUTPUT=%b\n",X,Y,OUTPUT);endinitialbeginX = 1'b0; Y = 1'b0;#5 X = 1'b1; Y = 1'b0;#5 X = 1'b1; Y = 1'b1;#5 X = 1'b0; Y = 1'b1;endendmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim 软件,掌握了Modelsim 软件的编译、仿真方法。

Verilog实验报告班级:学号:姓名:实验1 :用 Verilog HDL 程序实现直通线1 实验要求:(1) 编写一位直通线的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 建议用模式 52 试验程序:module wl(in,out);input in;output out;wire out;assign out=in;endmodule3 测试基准:`include “wl.v”module wl_tb;reg in_tb;wire out_tb;initialbeginin_tb =0;#100 in_tb =1;#130 in_tb =0;endendmodule4 仿真图形:实验2 :用 Verilog HDL 程序实现一位四选一多路选择器1实验要求:(1) 编写一位四选一多路选择器的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4)建议用模式 52 试验程序:module mux4_to_1 (out,i0,i1,i2,i3,s1,s0);output out;input i0,i1,i2,i3;input s1, s0;reg out;always @ (s1 or s0 or i0 or i1 or i2 or i3)begincase ({s1, s0})2'b00: out=i0;2'b01: out=i1;2'b10: out=i2;2'b11: out=i3;default: out=1'bx;endcaseendendmodule3 测试基准:`include "mux4_to_1.v"module mux4_to_1_tb1;reg ain,bin,cin,din;reg[1:0] select;reg clock;wire outw;initialbeginain=0;bin=0;cin=0;din=0;select=2'b00;clock=0;endalways #50 clock=~clock;always @(posedge clock)begin#1 ain={$random} %2;#3 bin={$random} %2;#5 cin={$random} %2;#7 din={$random} %2;endalways #1000 select[0]=!select[0];always #2000 select[1]=!select[1];mux4_to_1 m(.out(outw),.i0(ain),.i1(bin),.i2(cin),.i3(din),.s1(select[1]),.s0(select[0])); endmodule4 仿真图形:实验3:用 Verilog HDL 程序实现十进制计数器1实验要求:(1) 编写十进制计数器的 Veirlog HDL 程序. 有清零端与进位端, 进位端出在输出为 9 时为高电平.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2 实验程序:module counter_10c (Q, clock, clear, ov);output [3:0] Q;output ov;input clock, clear;reg [3:0] Q;reg ov;initial Q=4'b0000;always @ (posedge clear or negedge clock)beginif (clear)Q<=4'b0;else if (Q==8)beginQ<=Q+1;ov<=1'b1;endelse if (Q==9)beginQ<=4'b0000;ov<=1'b0;endelsebeginQ<=Q+1;ov<=1'b0;endendendmodule3 测试基准:`include"./counter_10c.v"module counter_10c_tb;wire[3:0] D_out;reg clk,clr;wire c_out;reg[3:0] temp;initialbeginclk=0;clr=0;#100 clr=1;#20 clr=0;endalways #20 clk=~clk;counter_10c m_1(.Q(D_out),.clear(clr),.clock(clk),.ov(c_out)); endmodule4 仿真波形:实验4 :用 Verilog HDL 程序实现序列检测器1 实验要求:、(1) 编写序列检测器的 Veirlog HDL 程序. 检测串行输入的数据序列中是否有目标序列5'b10010, 检测到指定序列后, 用一个端口输出高电平表示.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2试验程序:module e15d1_seqdet( x, z, clk, rst);input x,clk, rst;output z;reg [2:0] state;wire z;parameter IDLE = 3 'd0,A = 3'd1,B = 3'd2,C = 3'd3,D = 3'd4,E = 3'd5,F = 3'd6,G = 3'd7;assign z =(state==D && x==0)?1:0;always @(posedge clk or negedge rst)if(!rst)beginstate<=IDLE;endelsecasex(state)IDLE: if(x==1)state<=A;else state<=IDLE;A: if (x==0)state<=B;else state<=A;B: if (x==0)state<=C;else state<=F;C: if(x==1)state<=D;else state<=G;D: if(x==0)state<=E;else state<=A;E: if(x==0)state<=C;else state<=A;F: if(x==1)state<=A;else state<=B;G: if(x==1)state<=F;else state <=G;default: state<=IDLE;endcaseendmodule3测试基准:`include"e15d1_seqdet.v"`timescale 1ns/1ns`define halfperiod 20module e15d1_seqdet_tb;reg clk, rst;reg [23:0] data;wire z;reg x;initialbeginclk =0;rst =1;#2 rst =0;#30 rst =1;data= 20 'b1100_1001_0000_1001_0100;#(`halfperiod*1000) $stop;endalways #(`halfperiod) clk=~clk;always @ (posedge clk)begin#2 data={data[22:0],data[23]};x=data[23];ende15d1_seqdet m(.x(x),.z(z),.clk(clk),.rst(rst)); endmodule4仿真波形:。

verilog实验报告Verilog实验报告引言:Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

它是一种高级语言,能够描述电路的行为和结构,方便工程师进行数字电路设计和验证。

本实验报告将介绍我在学习Verilog过程中进行的实验内容和所获得的结果。

实验一:基本门电路设计在这个实验中,我使用Verilog设计了基本的逻辑门电路,包括与门、或门和非门。

通过使用Verilog的模块化设计,我能够轻松地创建和组合这些门电路,以实现更复杂的功能。

我首先创建了一个与门电路的模块,定义了输入和输出端口,并使用逻辑运算符和条件语句实现了与门的功能。

然后,我创建了一个测试模块,用于验证与门的正确性。

通过输入不同的组合,我能够验证与门的输出是否符合预期。

接下来,我按照同样的方法设计了或门和非门电路,并进行了相应的测试。

通过这个实验,我不仅学会了使用Verilog进行基本门电路的设计,还加深了对逻辑电路的理解。

实验二:时序电路设计在这个实验中,我学习了如何使用Verilog设计时序电路,例如寄存器和计数器。

时序电路是一种具有状态和时钟输入的电路,能够根据时钟信号的变化来改变其输出。

我首先设计了一个简单的寄存器模块,使用触发器和组合逻辑电路实现了数据的存储和传输功能。

然后,我创建了一个测试模块,用于验证寄存器的正确性。

通过输入不同的数据和时钟信号,我能够观察到寄存器的输出是否正确。

接下来,我设计了一个计数器模块,使用寄存器和加法电路实现了计数功能。

我还添加了一个复位输入,用于将计数器的值重置为初始状态。

通过测试模块,我能够验证计数器在不同的时钟周期内是否正确地进行计数。

通过这个实验,我不仅学会了使用Verilog设计时序电路,还加深了对触发器、寄存器和计数器的理解。

实验三:组合电路设计在这个实验中,我学习了如何使用Verilog设计组合电路,例如多路选择器和加法器。

组合电路是一种没有状态和时钟输入的电路,其输出只取决于当前的输入。

Verilog实验报告实验一简单组合逻辑电路的设计一实验要求1.用verilog HDL语言描写出简单的一位数据比较器及其测试程序;2.用测试程序对比较器进行波形仿真测试;画出仿真波形;3.总结实验步骤和实验结果。

二实验原理与内容4.这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

5.模块源代码测试模块:6.波形图:四结实验步骤和实验结果由图可看出,每当输入的电位值不同时输出为0,这与实验要求一致,相同时输出为1,故此程序是可行的。

实验三在verilog HDL中使用函数一实验要求1.掌握函数在模块中的使用2.用测试程序进行波形仿真测试;画出仿真波形3.总结实验步骤和实验结果二实验原理与内容与一般的程序设计语言一样;verilog HDL也可以使用函数已是应对不同变量采取同一运算的操作。

verilog HDL函数在综合时被理解成具有独立运算功能的电路,每调用一次函数相当于改变这部分电路的输入以得到相应的计算结果。

模块源代码:module ex3(clk,n,result,reset);output[31:0] result;input[3:0] n;input reset,clk;reg[31:0] result;always @(posedge clk)beginif(!reset)result <= 0;elsebeginresult <= n*factorial(n)/((n*2)+1);endendfunction[31:0] factorial;input[3:0] operand;reg[3:0] index;beginfactorial = operand ? 1:0;for(index = 2;index <= operand;index = index+1) factorial = index*factorial;endendfunctionendmodule`timescale 1ns/100ps`define clk_cycle 50module ex3_t();reg[3:0] n,i;reg reset,clk;wire[31:0] result;initialbeginn=0;reset=1;clk=0;#100 reset=0;#100 reset = 1;for(i=0;i <= 15;i=i+1)begin#200 n=i;end#100 $stop;endalways #`clk_cycle clk =~ clk;ex3 ex30(.clk(clk),.n(n),.result(result),.reset(reset)); always @(negedge clk)$display("at n=%d,result=%d",n,result);endmodule波形图:实验四在verilog HDL中使用任务一实验要求1.掌握任务在结构化verilog HDL设计中的应用2.用测试程序进行波形仿真测试;画出仿真波形3.总结实验步骤和实验结果二实验原理与内容仅有函数并不能满足verilog HDL中的运算需求。

HDL实验报告专业电子科学与技术姓名学号指导老师1 实验一Modelsim仿真软件的使用1.1 实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法;(3)熟练运用Modelsim 软件进行HDL 程序设计开发。

1.2 实验步骤(1)学习使用Modelsim软件;(2)分析原理及功能;(3)用Verilog HDL编写程序;(4)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

1.3 实验内容用Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果。

1.4.1 程序module my_xor(ina,inb,out);input ina,inb;output out;assign out=ina^inb;endmodulemodule t_xor;reg ina,inb;wire out;initialbeginina=1'b0;forever #20 ina=~ina;endinitialbegininb=1'b0;forever #10 inb=~inb;endmy_xor tt(.ina(ina),.inb(inb),.out(out));endmodule2 实验二简单组合电路设计2.1 实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法2.2 实验步骤(1)分析原理及功能;(2)根据原理用Verilog HDL编写程序;(3)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

2.3 实验内容设计一个三人表决器(高电平表示通过) ,实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

verilog hdl实验报告《Verilog HDL实验报告》Verilog HDL(硬件描述语言)是一种用于描述电子系统的硬件的语言,它被广泛应用于数字电路设计和硬件描述。

本实验报告将介绍Verilog HDL的基本概念和使用方法,并通过实验展示其在数字电路设计中的应用。

实验目的:1. 了解Verilog HDL的基本语法和结构2. 掌握Verilog HDL的模块化设计方法3. 熟悉Verilog HDL的仿真和综合工具的使用实验内容:1. Verilog HDL的基本语法和结构Verilog HDL是一种硬件描述语言,其语法和结构类似于C语言。

它包括模块定义、端口声明、信号赋值等基本元素。

在本实验中,我们将学习如何定义Verilog模块,并使用端口声明和信号赋值描述数字电路的行为。

2. Verilog HDL的模块化设计方法Verilog HDL支持模块化设计,可以将复杂的电路分解为多个模块,每个模块描述一个子电路的行为。

在本实验中,我们将学习如何设计和实现Verilog模块,并将多个模块组合成一个完整的数字电路。

3. Verilog HDL的仿真和综合工具的使用Verilog HDL可以通过仿真工具进行功能验证,也可以通过综合工具生成实际的硬件电路。

在本实验中,我们将使用Verilog仿真工具对设计的数字电路进行功能验证,并使用综合工具生成对应的硬件电路。

实验步骤:1. 学习Verilog HDL的基本语法和结构2. 设计一个简单的数字电路,并实现Verilog模块描述其行为3. 使用仿真工具对设计的数字电路进行功能验证4. 使用综合工具生成对应的硬件电路实验结果:通过本实验,我们学习了Verilog HDL的基本概念和使用方法,并成功设计和实现了一个简单的数字电路。

我们使用仿真工具对设计的数字电路进行了功能验证,并使用综合工具生成了对应的硬件电路。

实验结果表明,Verilog HDL在数字电路设计中具有重要的应用价值。

Verilog 实验报告一、实验目的本次 Verilog 实验的主要目的是通过实际编写代码和进行仿真,深入理解 Verilog 语言的基本语法、逻辑结构和时序特性,掌握数字电路的设计方法和实现过程,并能够运用Verilog 实现简单的数字逻辑功能。

二、实验环境本次实验使用的软件工具是 Xilinx Vivado 20192,硬件平台是Xilinx Artix-7 开发板。

三、实验内容(一)基本逻辑门的实现1、与门(AND Gate)使用 Verilog 语言实现一个两输入的与门。

代码如下:```verilogmodule and_gate(input a, input b, output out);assign out = a & b;endmodule```通过编写测试激励文件对该模块进行仿真,验证其逻辑功能的正确性。

2、或门(OR Gate)同样实现一个两输入的或门,代码如下:```verilogmodule or_gate(input a, input b, output out);assign out = a | b;endmodule```3、非门(NOT Gate)实现一个单输入的非门:```verilogmodule not_gate(input a, output out);assign out =~a;endmodule```(二)组合逻辑电路的实现1、加法器(Adder)设计一个 4 位的加法器,代码如下:```verilogmodule adder_4bit(input 3:0 a, input 3:0 b, output 4:0 sum);assign sum = a + b;endmodule```2、减法器(Subtractor)实现一个 4 位的减法器:```verilogmodule subtractor_4bit(input 3:0 a, input 3:0 b, output 4:0 diff);assign diff = a b;endmodule```(三)时序逻辑电路的实现1、计数器(Counter)设计一个 4 位的计数器,能够在时钟上升沿进行计数,代码如下:```verilogmodule counter_4bit(input clk, output 3:0 count);reg 3:0 count_reg;always @(posedge clk) begincount_reg <= count_reg + 1;endassign count = count_reg;endmodule```2、移位寄存器(Shift Register)实现一个 4 位的移位寄存器,能够在时钟上升沿进行左移操作:```verilogmodule shift_register_4bit(input clk, input rst, output 3:0 data_out);reg 3:0 data_reg;always @(posedge clk or posedge rst) beginif (rst)data_reg <= 4'b0000;elsedata_reg <={data_reg2:0, 1'b0};endassign data_out = data_reg;endmodule```四、实验结果与分析(一)基本逻辑门的结果通过仿真,与门、或门和非门的输出结果与预期的逻辑功能完全一致,验证了代码的正确性。

数字电路与逻辑设计课程小设计题目:简单运算器运算电路设计专业:计算机科学与技术班级:CS1409学号:U201414813姓名:唐礼威指导教师:徐老师一、设计题目每位同学自选下列题目之一。

(1)时序信号发生器设计(2)地址译码电路设计(3)自选(容要求参见(1)、(2))二、设计容要求2.1、简单运算器设计用Verilog实现一个满足设计要求的简单运算器的运算电路。

2.1.1设计要求设计一个能实现两种算术运算和两种逻辑运算的4 位运算器。

参加运算的4 位二进制代码分别存放在4个寄存器A、B、C、D 中,要求在选择变量控制下完成如下4种基本运算:(1)实现A加B,显示运算结果并将结果送寄存器A;(2)实现A减B,显示运算结果并将结果送寄存器B;(3)实现A与C,显示运算结果并将结果送寄存器C;(4)实现A异或D,显示运算结果并将结果送寄存器D。

2.1.2 功能描述根据设计要求,为了区分4种不同的运算,需设置2个运算控制变量。

设运算控制变量为S1 和S O,可列出运算器的功能,如表1所示。

根据功能描述可得出运算器的结构框图,如图1所示。

整个电路可由传输控制电路、运算电路、显示电路3部分组成。

简单运算功能说明表运算器的结构框图由简单运算器的结构图可知其由传输控制电路、运算电路和运算结果显示电路三个大部分构成,其中运算电路又由算术运算电路、逻辑运算电路构成。

这次设计主要是利用Verilog语言设计运算器中运算电路部分。

2.1.3 电路设计运算电路的逻辑电路图如下:由运算电路的逻辑电路图可以看出运算器中的逻辑关系,运算器主要由一片74LS283芯片和4个寄存器及8个异或门和4个与门构成。

由运算电路逻辑电路图可以初步构思设计个子模块的功能。

但是仅有运算电路的逻辑电路图还不够,还需要整体运算器的逻辑电路图才能确定各个子模块的输入与输出关系。

运算电路的完整逻辑电路图如下:可以看到运算电路逻辑图只是其中一部分,其中74LS283芯片功能为超前进位的全加器,可以将它设计为一个加法器模块。

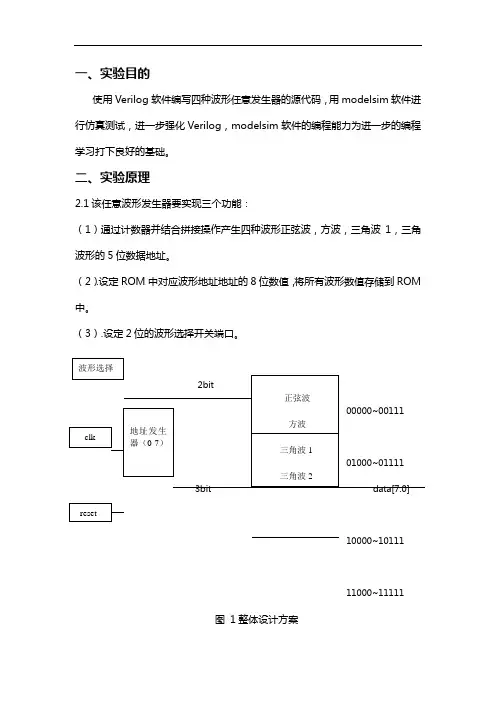

一、实验目的使用Verilog软件编写四种波形任意发生器的源代码,用modelsim软件进行仿真测试,进一步强化Verilog,modelsim软件的编程能力为进一步的编程学习打下良好的基础。

二、实验原理2.1该任意波形发生器要实现三个功能:(1)通过计数器并结合拼接操作产生四种波形正弦波,方波,三角波1,三角波形的5位数据地址。

(2).设定ROM中对应波形地址地址的8位数值,将所有波形数值存储到ROM 中。

(3).设定2位的波形选择开关端口。

10000~1011111000~11111图1整体设计方案2.2 四种波形要在一个周期内等间隔取8个点,定义对应的数据,下图为示意图,由于编程序需要,数据会进行相应的修改。

图2 四种波形一个周期内的取样示意图2.3 四种波形数据地址对应的数据的存储器ROM根据示意图,由于实际情况需要,将正弦波平移至x 轴以上,并将所有波形的峰峰值取大100倍。

下表1是ROM 存储器波形选择地址 取样点的地址 ROM 数据00 000 171 00 001 200 000101711-111正弦波正弦波方波三角波1三角波2y xx88yyx 81表1 ROM存储器三、实验内容3.1 任意波形发生器verilog程序代码:module wave(data,clk,add1,reset);//顶层模块端口定义output[7:0]data;input clk,reset;input[1:0] addr1;Wire[1:0] addr1;wire clk,reset;//输入输出变量定义ADDR 4(addr,clk,addr1,reset);//地址发生器模块调用rom 1(addr,data);//ROM存储器模块调用endmodulemodule ADDR(addr,clk,addr1,reset);output[4:0] addr;input clk,reset;wire clk,reset;reg[2:0] addr2;wire[1:0] addr1;reg[4:0] addr;initial addr2=3'b000; //定义计数初值always @(posedge clk or posedge reset)//每当有clk,或reset信号开启程序beginif(reset)beginaddr2<=0;//同步复位addr<=0;endelse if(addr2>=7)//addr2计数至7时,addr2复位beginaddr2<=0;endelsebeginaddr2<=addr2+1;//addr2由0至7计数addr<={addr1,addr2};//addr1与addr2地址拼接为addr的最终地址endendendmodulemodule rom(addr,data);//数据存储器模块input[4:0] addr;output[7:0] data;function[6:0] romout;//定义函数,存储32个波形取样点地址的数据input[4:0] addr;reg[4:0] addr;wire[7:0] data;case(addr)//根据不同地址,得到不同数据。

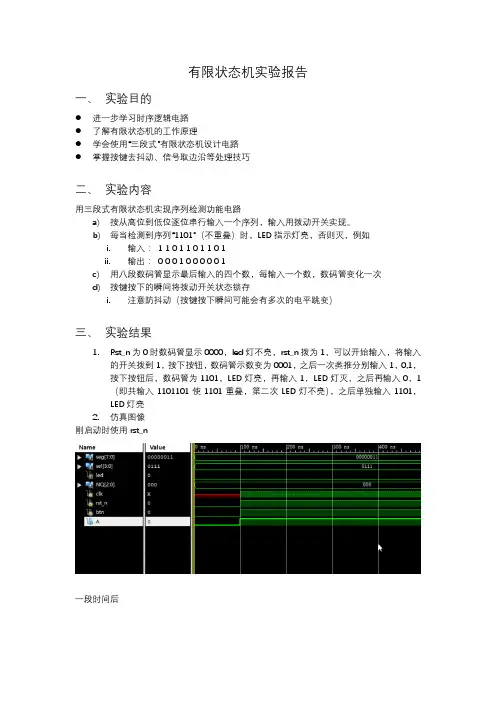

有限状态机实验报告一、实验目的●进一步学习时序逻辑电路●了解有限状态机的工作原理●学会使用“三段式”有限状态机设计电路●掌握按键去抖动、信号取边沿等处理技巧二、实验内容用三段式有限状态机实现序列检测功能电路a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。

b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如i.输入:1 1 0 1 1 0 1 1 0 1ii.输出:0 0 0 1 0 0 0 0 0 1c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次d)按键按下的瞬间将拨动开关状态锁存i.注意防抖动(按键按下瞬间可能会有多次的电平跳变)三、实验结果1.Rst_n为0时数码管显示0000,led灯不亮,rst_n拨为1,可以开始输入,将输入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1,0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入1101,LED灯亮2.仿真图像刚启动时使用rst_n一段时间后其中Y代表输出,即控制led灯的信号,sel表示数码管的选择信号,seg表示数码管信号四、实验分析1、实验基本结构其中状态机部分使用三段式结构:2、整体结构为:建立一下模块:Anti_dither.v输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op这一模块实现思路是利用按钮按下时会持续10ms以上而上下抖动时接触时间不超过10ms来给向下接触的时间计时,达到上限时间才产生输出。

Num.v输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。

输出的num即为即将在数码管上显示的值Scan.v输入时钟信号,对其降频以产生1ms一次的扫描信号。

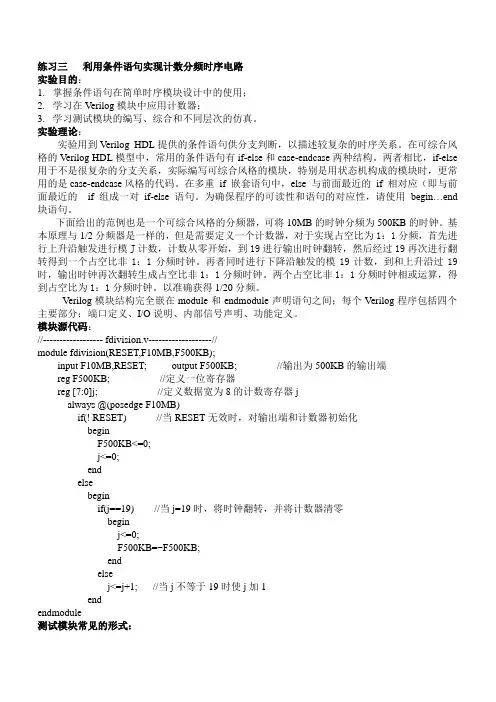

练习三利用条件语句实现计数分频时序电路实验目的:1.掌握条件语句在简单时序模块设计中的使用;2.学习在Verilog模块中应用计数器;3.学习测试模块的编写、综合和不同层次的仿真。

实验理论:实验用到Verilog HDL提供的条件语句供分支判断,以描述较复杂的时序关系。

在可综合风格的Verilog HDL模型中,常用的条件语句有if-else和case-endcase两种结构。

两者相比,if-else 用于不是很复杂的分支关系,实际编写可综合风格的模块,特别是用状态机构成的模块时,更常用的是case-endcase风格的代码。

在多重if 嵌套语句中,else 与前面最近的if 相对应(即与前面最近的if 组成一对if-else 语句。

为确保程序的可读性和语句的对应性,请使用begin…end 块语句。

下面给出的范例也是一个可综合风格的分频器,可将10MB的时钟分频为500KB的时钟。

基本原理与1/2分频器是一样的,但是需要定义一个计数器,对于实现占空比为1:1分频,首先进行上升沿触发进行模J计数,计数从零开始,到19进行输出时钟翻转,然后经过19再次进行翻转得到一个占空比非1:1分频时钟。

再者同时进行下降沿触发的模19计数,到和上升沿过19时,输出时钟再次翻转生成占空比非1:1分频时钟。

两个占空比非1:1分频时钟相或运算,得到占空比为1:1分频时钟。

以准确获得1/20分频。

Verilog模块结构完全嵌在module和endmodule声明语句之间;每个Verilog程序包括四个主要部分:端口定义、I/O说明、内部信号声明、功能定义。

模块源代码://------------------ fdivision.v-------------------//module fdivision(RESET,F10MB,F500KB);input F10MB,RESET; output F500KB; //输出为500KB的输出端reg F500KB; //定义一位寄存器reg [7:0]j; //定义数据宽为8的计数寄存器jalways @(posedge F10MB)if(! RESET) //当RESET无效时,对输出端和计数器初始化beginF500KB<=0;j<=0;endelsebeginif(j==19) //当j=19时,将时钟翻转,并将计数器清零beginj<=0;F500KB=~F500KB;endelsej<=j+1; //当j不等于19时使j加1endendmodule测试模块常见的形式:module t;reg …; //被测模块输入/输出变量类型定义wire…; //被测模块输入/输出变量类型定义initial begin …; …; …; end … …//产生测试信号always #delay begin …; end … …//产生测试信号Testedmd m(.in1(ina), .in2(inb), .out1(outa), .out2(outb) );//被测模块的实例引用initial begin ….; ….; …. end //记录输出和响应endmodule测试模块源代码:`timescale 1ns/100ps`define clk_cycle 50module division_Top;reg F10MB,RESET;wire F500KB_clk;always #`clk_cycle F10MB=~F10MB;initialbeginRESET=1;F10MB=0;#100 RESET=0;#100 RESET=1;#10000 $stop;endfdivision fdivision (.RESET(RESET),.F10MB(F10MB),.F500KB(F500_clk));endmodule仿真结果:练习:利用10MB的时钟,设计一个单周期形状的周期波形。

verilog课程设计实验报告一、教学目标本课程旨在通过Verilog硬件描述语言的学习,让学生掌握数字电路设计的自动化工具,理解并实践硬件描述语言在数字系统设计中的应用。

通过本课程的学习,学生应达到以下目标:1.知识目标:–理解Verilog的基本语法和结构。

–掌握Verilog中的模块化设计方法。

–学习常用的Verilog描述技巧,包括逻辑门级建模、行为级建模和结构级建模。

2.技能目标:–能够运用Verilog语言进行简单的数字电路设计。

–学会使用至少一种Verilog仿真工具进行电路功能验证。

–能够阅读和理解Verilog代码,进行简单的代码优化。

3.情感态度价值观目标:–培养学生的团队合作意识,在实验报告中能够体现分工合作的精神。

–培养学生的问题解决能力,鼓励学生在遇到问题时积极寻找解决方案。

–培养学生对新技术的好奇心和学习兴趣,激发他们对电子工程领域的热爱。

二、教学内容依据教学目标,本课程的教学内容将围绕Verilog语言的基础知识、实践应用和项目设计展开。

教学大纲安排如下:1.第一部分:Verilog基础知识(2周)–介绍Verilog的背景和基本概念。

–详细讲解Verilog的数据类型、运算符和语句。

2.第二部分:模块化设计(2周)–讲解模块的定义和封装。

–实践模块的端口声明和模块实例化。

3.第三部分:数字电路的Verilog描述(2周)–通过实例教学,掌握逻辑门、触发器等基本组件的Verilog建模。

–学习组合逻辑和时序逻辑的设计方法。

4.第四部分:仿真与测试(1周)–学习使用仿真工具进行电路功能验证。

–理解并实践测试台(testbench)的编写。

5.第五部分:项目设计(3周)–小组合作完成一个较为复杂的数字系统设计项目。

–包括系统模块的划分、编码、仿真和测试。

三、教学方法为了提高学生的学习效果,将采用多种教学方法相结合的方式进行授课:1.讲授法:用于讲解Verilog的基本概念和语法。

实验报告格式要求一、实验报告内容包括:(1)实验名称。

(2)实验目的。

(3)实验仪器及编号。

写明仪器名称、型号、编号。

(4)实验原理。

简单表达有关实验原理(包括电路图或光路图或实验装置示用意)及测量中依据的的公式,式中各量的物理含义及单位,公式成立所应知足的实验条件等。

(5)实验内容及步骤。

依如实验内容及实际的实验进程写明关键步骤和平安注意要点。

(6)实验观测记录。

记录原始测量数据、图形等有关原始量,形式上要求整齐标准。

(7)数据处置结果。

依如实验要求,采纳适合的方式进行数据处置,误差分析,最后写出实际结果。

(8)小结或讨论。

内容不限。

能够是实验中的现象分析,对实验关键问题的体会,实验的收成和建议,也可解答试探题。

二、书写顺序(1)到(5)是进行实验预习时就应该完成的。

(6)在实验中完成。

做完实验后再在预习报告基础上完成(7)(8)两项。

完成一个实验,确实是一次最大体的科研训练,从预习到写出一个实验报告,每一步都有极为丰硕的学习内容,要踊跃试探,认真对待。

实验(一)简单的组合逻辑设计实验日期 2021-10-31 同组者姓名一、实验目的[1] 把握大体组合逻辑电路的实现方式[2] 初步了解两种大体组合逻辑电路的生成方式[3] 学习测试模块的编写[4] 通过综合和布局布线了解不同层次仿真的物理意义二、实验仪器运算机、FPGA开发板三、实验内容[1] 在ISE软件环境中进行一次完整的设计流程,并在FPGA开发板上实现与门的功能。

[2] 完成一个可综合的数据比较器的程序。

[3] 完成数据比较器的测试模块。

[4] 发挥部份:设计一个多位(2位)的数据比较器并在FPGA开发板上实现该比较器。

四、实验步骤、分析及结果(在下面写出你的代码)代码:module compare(input a,input b,output c);assign c=a&b;endmodule结果如下图:拓展代码如下:module compare( Y ,A ,B ); input [1:0] A ;input [1:0] B ;output reg [1:0] Y ;always @ (A or B )beginif ( A > B )Y <= 3'b01; else if ( A == B) Y <= 3'b10; elseY <= 3'b11; endendmodule结果如下:指导师(签名)时刻实验(二)简单分频时许逻辑电路的设计实验日期 2021-11-7 同组者姓名一、实验目的[1] 把握最大体时序电路的实现方式。

硬件描述语言实验报告班级: 2016133班学号: 201613354姓名: 齐方目录硬件描述语言·····················································································································- 0 - 实验报告·································································································································- 0 - 实验一简单组合逻辑设计·································································································- 2 - 实验二简单分频时序逻辑电路的设计·············································································- 5 - 实验三利用条件语句实现计数分频时序电路·································································- 8 - 实验四阻塞赋值与非阻塞赋值的区别·········································································· - 14 - 实验五用always块实现较复杂的组合逻辑电路 ························································· - 18 -实验一简单组合逻辑设计一、实验目的1.掌握基本组合逻辑电路的实现方法。

微机原理实验报告课程:微机原理指导老师姓名:学号:实验名称:Lab 02: MIPS处理器部件实现A微机原理实验报告一、实验目的本实验旨在实现MIPS处理器的部件—控制器和ALU,理解CPU控制器,理解ALU的原理,使用Verilog语言设计CPU控制器和ALU ,使用ISim进行行为仿真。

二、实验原理及说明MIPS的基本架构如图1所示,包括Control,ALU这样的组合逻辑单元,也包括如instruction memory,Data memory和Registers file存储单元。

本实验主要实现CPU Control和ALU两个部分。

(一)CPU控制器的实现CPU Control单元输入为指令的opCode字段,即操作码;以及R指令的funct编码。

操作码和Funct编码经过主控制单元的译码,给ALU,Data Memory,Registers ,Muxs等部件输出正确的控制信号。

图2. MIPS基本指令格式图: 控制模块的IO定义注:Jump指令编码是000010,Jump输出信号为1,其他输出信号都为0图3. OpCode与控制输出的编码关系图4. Funct,ALUOp与ALU Control编码关系(二) ALU的实现ALU是CPU核心的计算单元,实现诸如加,减,或,与等操作。

算术操作的编码三、实验verilog代码(一)CPU控制器的实现module Ctr(input [5:0] OpCode,input [5:0] Funct,output regRegDst,output regALUSrc,output regRegWrite,output regMemWrite,output regMemRead,output regMemtoReg,output reg Branch,output reg Jump,output reg [3:0] ALUControl);reg [1:0] ALUOp;always @(OpCode)begincase(OpCode)//R type6'b000000:beginRegDst=1; ALUSrc=0; RegWrite=1; MemWrite=0; MemRead=0; MemtoReg=0;Branch=0;ALUOp=2'b10; Jump=0;end//beq6'b000100:beginRegDst=1'bx; ALUSrc=0; RegWrite=0; MemWrite=0; MemRead=0; MemtoReg=1'bx; Branch=1;ALUOp=2'b01; Jump=0;end//lw6'b100011:beginRegDst=0; ALUSrc=1; RegWrite=1; MemWrite=0; MemRead=1; MemtoReg=1;Branch=0;ALUOp=2'b00; Jump=0;end//sw6'b101011:beginRegDst=1'bx;ALUSrc=1;RegWrite=0;MemWrite=1;MemRead=0;MemtoReg=1'bx;Branch=0;ALUOp=2'b00;Jump=0;end//Jump6'b000010:beginRegDst=0;ALUSrc=0;MemtoReg=0;RegWrite=0;MemRead=0;MemWrite=0;Branch=0;ALUOp=2'b00;Jump=1;endendcaseendalways @(ALUOp or Funct)begincasex({ALUOp,Funct})8'b00xxxxxx: ALUControl=4'b0010;8'b01xxxxxx: ALUControl=4'b0110;8'b1xxx0000: ALUControl=4'b0010;8'b1xxx0010: ALUControl=4'b0110;8'b1xxx0100: ALUControl=4'b0000;8'b1xxx0101: ALUControl=4'b0001;8'b1xxx1010: ALUControl=4'b0111;default: ALUControl=4'b0000;endcaseendendmodule(二) ALU的实现module ALU(input [31:0] SrcA,input [31:0] SrcB,input [3:0] ALUCtr,output Zero,output reg [31:0] ALURes);assign Zero=(ALURes==1'b0);always @(SrcA or SrcB or ALUCtr)begincase(ALUCtr)4'b0000: ALURes=SrcA&SrcB; //AND4'b0001: ALURes=SrcA | SrcB; //OR4'b0010: ALURes=SrcA + SrcB; //add4'b0110: ALURes=SrcA - SrcB; //substract4'b0111: ALURes=SrcA<SrcB ? 1:0; //set on less than 4'b1100: ALURes=~(SrcA | SrcB); //NORdefault ALURes=32'h0;endcaseendendmodule四、仿真测试1.代码(一)CPU控制器的实现module Ctr_tb;// Inputsreg [5:0] OpCode;reg [5:0] Funct;// Outputswire RegDst;wire ALUSrc;wire RegWrite;wire MemWrite;wire MemRead;wire MemtoReg;wire Branch;wire Jump;wire [3:0] ALUControl;// Instantiate the Unit Under Test (UUT)Ctruut (.OpCode(OpCode),.Funct(Funct),.RegDst(RegDst),.ALUSrc(ALUSrc),.RegWrite(RegWrite),.MemWrite(MemWrite),.MemRead(MemRead),.MemtoReg(MemtoReg),.Branch(Branch),.Jump(Jump),.ALUControl(ALUControl) );initial begin// R-type AddOpCode=6'b000000;Funct=6'b100000;// R-type Subtract#10;OpCode=6'b000000;Funct=6'b100010;// Lw#10;OpCode=6'b100011;Funct=6'bxxxxxx;// Sw#10;OpCode=6'b101011;Funct=6'bxxxxxx;// Beq#10;OpCode=6'b000100;Funct=6'bxxxxxx;// R-type AND#10;OpCode=6'b000000;Funct=6'b100100;// R-type OR#10;OpCode=6'b000000;Funct=6'b100101;// R-type set on less than#10;OpCode=6'b000000;Funct=6'b101010;// Jump#10;OpCode=6'b000010;endendmodule(二) ALU的实现module ALU_tb;// Inputsreg [31:0] SrcA;reg [31:0] SrcB;reg [3:0] ALUCtr;// Outputswire Zero;wire [31:0] ALURes;// Instantiate the Unit Under Test (UUT)ALU uut (.SrcA(SrcA),.SrcB(SrcB),.ALUCtr(ALUCtr),.Zero(Zero),.ALURes(ALURes));initial begin// ANDSrcA =32'hf0f0ffff;SrcB =32'h0000f0f0;ALUCtr =0;// OR#10;ALUCtr =4'b0001;// Add#10;ALUCtr =4'b0010;// Subtract#10;ALUCtr =4'b0110;// set on less than#10;ALUCtr =4'b0111;//NOR#10;ALUCtr =4'b1100;//Other situation#10;ALUCtr =4'b1111;endendmodule2.仿真截图(一)CPU控制器的实现(二) ALU的实现五、实验总结实验名称:Lab03: MIPS处理器部件实现B微机原理实验报告一、实验目的本实验旨在使读者实现MIPS处理器的部件—Data memory, Instruction memory和Registers 三大存储器件。

可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握Quartus II 软件的基本使用方法,完成基本时序电路设计实验时间: 2014 年 06 月 19 日地点: 803实验室学生姓名:学号:实验名称:简单D触发器实验一简单D触发器1、实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

(2)创建文件选择菜单File—>New—>Verilog HDL File,创建一个Verilog HDL文件,在Verilog HDL文件中编写能够完成实验功能的Verilog HDL代码。

(3)编译工程选择菜单Processing —>Start Compilation,或者单击按钮。

(4)观察RTL视图选择菜单Tools—>Netlist Viewers—>RTL Viewer即可生成RTL视图。

(5)仿真1).创建VWF文件选择菜单File—>New—>Vector Waveform File2). 设定“End Time”选择菜单Edit File—> End Time,在弹出的对话框中将Time设置为20us。

3).在VWF文件中输入信号节点选择菜单View—>Utility Windows—>Node Finder,在出现的对话框中将Filter框中设置为Pins:all,再单击List按钮,从端口列表中选择需要观察的并拖到波形编辑窗口中。

4).编辑输入信号波形5).观察仿真结果选择菜单Processing—>Start Simulation,或者单击按钮,观察输出波形。

2. VerilogHDL代码module _DFF (clk,d,q);input clk,d;output q;reg q;always@ (posedge clk)beginq<=d;endendmodule3. RTL 视图4.仿真波形实验二同步置数的D触发器1.实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

一、8位数字显示的简易频率计设计要求:①能够测试10Hz~10MHz方波信号;②电路输入的基准时钟为1Hz,要求测量值以8421BCD码形式输出;③系统有复位键;④采用分层次分模块的方法,用Verilog HDL进行设计。

⑤写出测试仿真程序1.设计原理频率计的原理即测量给定信号每秒钟脉冲个数,则系统时钟宽度应为2s,通过分频模块将基准时钟进行二分频实现;当系统时钟高电平时计数模块开始计数,低电平时清零;之后将结果存入锁存模块使其稳定显示。

2.设计方案该频率计由分频模块,计数模块,锁存模块和顶层模块构成,其中:1)分频模块(FC_div):由于基准时钟(clk_d)频率为1Hz,高电平宽度为0.5s,因此通过一个二分频模块得到一个频率为0.5Hz,高电平宽度为1s的时钟(clk_out),并作为计频器的系统时钟。

2)计数模块(FC_counter):频率计核心模块,在接入的系统时钟(clk_c)处于高电平时对输入信号(freq_in)的上升沿进行计数,从而测得输入信号的频率。

由于要把测量值以8421BCD码输出,且量程上限为10MHz。

因此程序内采用8个4位寄存器分别从低到高地按位存储测量值,最后再按位排列输出一个32位的BCD 码序列(CT)。

3)锁存模块(FC_latch):将计数模块输出的结果存储以稳定显示。

4)顶层模块(FC_top):将各模块连接实现计频器。

3.程序代码1)分频模块module FC_div(clk_d,rst_d,clk_out);input clk_d,rst_d;output clk_out;reg clk_out;always@(posedge clk_d or negedge rst_d)beginif(rst_d==0)clk_out<=0;elseclk_out<=~clk_out;endendmodule2)计数模块module FC_counter(clk_c,freq_in,CT);input clk_c;input freq_in;output [31:0] CT;reg [31:0] CT;reg [3:0] C0,C1,C2,C3,C4,C5,C6,C7;always@(posedge freq_in)beginif(!clk_c)beginC0<=0;C1<=0;C2<=0;C3<=0;C4<=0;C5<=0;C6<=0;C7<=0;endelsebeginif(C0!=4'b1001)C0<=C0+1;elsebeginC0<=0;if(C1!=4'b1001)C1<=C1+1;elsebeginC1<=0;if(C2!=4'b1001)C2<=C2+1;elsebeginC2<=0;if(C3!=4'b1001)C3<=C3+1;elsebeginC3<=0;if(C4!=4'b1001)C4<=C4+1;elsebeginC4<=0;if(C5!=4'b1001)C5<=C5+1;elsebeginC5<=0;if(C6!=4'b1001)C6<=C6+1;elsebeginC6<=0;if(C7!=4'b1001)C7<=C7+1;elseC7<=0;endendendendendendendendassign CT={C7,C6,C5,C4,C3,C2,C1,C0};endendmodule3)锁存模块module FC_latch(freq,Cl,Rl);input freq;input [31:0] Cl;output [31:0] Rl;reg [31:0] Rl;always@(negedge freq)Rl<=Cl;Endmodule4)顶层模块module FC_top(clk,rst,Freq_in,Nt);input clk,rst;input Freq_in;output [31:0] Nt;wire c0;wire [31:0] w0;FC_div d(.clk_d(clk),.rst_d(rst),.clk_out(c0));FC_counter c(.clk_c(c0),.freq_in(Freq_in),.CT(w0));FC_latch l(.freq(Freq_in),.Cl(w0),.Rl(Nt));Endmodule5)测试程序`timescale 100ns/1ns;module FC_top_test;reg clk,rst;reg Freq_in;wire [31:0] Nt;initialbeginclk=0;rst=0;Freq_in=0;#4999 rst=1;#500000$stop();endalways #50000 clk=~clk;always #5 Freq_in=~Freq_in;FC_top t(.clk(clk),.rst(rst),.Freq_in(Freq_in),.Nt(Nt));Endmodule4.仿真测试如测试程序所示,取时间单位为100ns,精度为1ns,为方便起见,定义此基准时钟为1Hz,则待测信号频率为10kHz。

专业:计算机科学与技术班级:CS1409学号:U**********名:***电话:158****5005邮件:*****************完成日期:2016.6.13 2016Verilog 语言·实验报告·计算机科学与技术学院目录1数据通路实验 (1)1.1实验目的 (1)1.2实验内容及要求 (1)1.3实验方案 (2)1.4实验步骤 (2)1.5故障及分析 (2)1.6仿真与结果 (3)1.7心得与体会 (4)2FSM实验 (5)2.1实验目的 (5)2.2实验内容及要求 (5)2.3实验方案 (6)2.4实验步骤 (6)2.5故障及分析 (7)2.6仿真与结果 (7)2.7心得与体会 (8)3意见和建议 (9)4附录 (10)1 数据通路实验1.1 实验目的综合应用掌握的简单组合电路和时序电路的设计方法,完成一个简单的数据通路的设计。

1.2 实验内容及要求1. 根据下图给出的数据通路(图中R0、R1和ACC是寄存器,+是加法器,其它则是多路选择器),完成相应的Verilog程序设计,图中数据线的宽度为8位,要求可以扩充至16位或者是32位;2. 根据下图给出的数据通路(图中SUM和NEXT是寄存器,Memory是存储器,+是加法器,==0是比较器,其它则是多路选择器),完成相应的Verilog程序设计,图中数据线的宽度为8位,要求可以扩充至16位或者是32位。

实验要求:程序必须自己编写,满足数据通路设计要求,综合结果正确。

1.3 实验方案根据要求,先把选择器、加法器、寄存器、比较器和存储器分模块编写,在主模块中根据数据通路调用即可。

题目中要求数据线宽度为8位,并且可以扩充至16位或32位,所以在前面定义WIDTH,利用parameter的参数传递功能来实现。

1.4 实验步骤1.分模块编写代码(见附录)2.运行综合Run Synthesis3.综合成功后检查RTL Analysis中的电路图Schematic1.5 故障及分析刚开始跑出来很多线是断的,后来发现是引脚对应部分的代码没有写完整。

后来加法器和ACC的参数顺序写错,导致接线与题给的不一致,发现问题后及时改正了。

1.6 仿真与结果Schematic图形如下:第一个数据通路:第二个数据通路:由以上两图可得,成功完成了要求的数据通路的设计,满足了各基本器件的输入输出链接要求;改变数据线宽度后再检查电路图,发现数据线做出相应改变,完成该实验。

1.7 心得与体会对数据通路的设计有了更好的理解,明白了数据通路的基本器件构成,熟悉了这些器件的功能和端口,掌握了Verilog完成基本运算器件的设计,完成了数据通路的设计。

2 FSM实验2.1 实验目的掌握用Verilog语言进行FSM设计、实现和仿真的方法。

2.2 实验内容及要求5.1_1、用FSM实现一个mealy型序列检测器,对一位的串行输入序列中的“1”的数量进行检测。

如果“1”的总数可以被3整除,输出“1”,否则输出“0”。

5.1_2、用FSM实现一个moore型序列检测器,对两位的串行输入序列进行检测。

输入01,00时,输出0,输入11,00时,输出1,输入10,00时,输出反向。

5.1_3、用FSM实现一个计数器(采用存储器),对一位的输入进行计数。

计数序列为:000,001,011,101,111,010。

5.2、用FSM实现一个序列识别器,该FSM的状态转移图如下所示,它能够对一位的串行输入序列中的“1”的数量进行检测。

如果FSM发现输入“1”的总数可以被3整除时,输出“1”;否则,输出“0”。

同时针对“***********”输入序列,写出相应的仿真程序并进行真波测试。

2.3 实验方案先根据要求画出状态图,根据状态图编写程序,根据程序编写仿真程序,最后得出结果和结论。

2.4 实验步骤5.1_1状态图:in=1/0in=0/0in=1/0 in=1/0in=1/15.1_2状态图:in=00in=01 in=10 in=11in=00 in=00 in=00out=0 out 翻转 out=1S0 S1S4 S3S0S1 S2S3S4 S5 S65.1_3状态图:1.根据以上状态图编写源程序(见附录)2.运行综合Run Synthesis3.综合正确后编写仿真程序4.仿真,得到仿真波形,验证结果2.5 故障及分析无故障2.6 仿真与结果5.1_1:如图,1的个数是3的倍数时输出1与预期一致5.1_2:如图,输入01后再输入00,输出0;输入11后再输入00,输出1;输入10后再输入00,输出翻转:与预期一致5.1_3:如图,输出序列为000,001,011,101,111,010(重复)与预期一致5.2:如图,1的个数是3的倍数时输出1与预期一致2.7 心得与体会这次实验通过FSM设计明白了设计的过程和步骤,首先要知道分为哪些状态,设计的是何种电路,如何选择用mealy还是moore型电路,状态转移要如何实现。

知道了mealy型和moore型电路的区别:当要求输出对输入快速响应并希望电路简单时选择mealy型,当要求时序输出稳定,能接受输出序列晚一个周期,即选择moore型电路不增加电路复杂性时,选择moore型电路。

3 意见和建议建议老师上课还是用中文PPT比较好,另外作业练习也用中文给出来,题目要求也尽量具体些,这样会减少我们学习的成本,更加有效的学习这门课。

4 附录源程序:4.1(第一个数据通路)//主模块module text4(S0,S1,S2,S3,Clk,reset,load,outR0,outR1,outACC,outS0,outS1,outS2,outS3,outA); parameter WIDTH=8; //位宽8位input S0,S1,S2,S3,Clk,reset,load;output [WIDTH-1:0] outR0,outR1,outACC,outS0,outS1,outS2,outS3,outA;register #(8) R0(inR0,Clk,reset,load,outR0);register #(8) R1(inR1,Clk,reset,load,outR1);register #(8) ACC(inACC,Clk,reset,load,outACC);mux #(8) S0(S0,inS00,inS01,outS0);mux #(8) S1(S1,inS10,inS11,outS1);mux #(8) S2(S2,inS20,inS21,outS2);mux #(8) S3(S3,inS30,inS31,outS3);add #(8) W1(inA0,inA1,outA);assign inS00=outS3;assign inS10=outS3;assign inS01=outR0;assign inS20=outR0;assign inS11=outR1;assign inS21=outR1;assign inA0=outACC;assign inS31=outACC;assign inACC=outA;assign inA1=outS2;assign inS30=outS2;assign inR1=outS1;assign inR0=outS0; endmodule//加法器模块module add(A,B,C);parameter WIDTH=8;input [WIDTH-1:0] A, B; output [WIDTH-1:0] C;wire [WIDTH:0] DA TA; assign DATA=A+B;assign C=DATA[7:0]; endmodule//寄存器模块module register(D,Clk,reset,load,Q); parameter WIDTH=8;input [WIDTH-1:0] D;input Clk,reset,load;output reg [WIDTH-1:0] Q; always @(posedge Clk)if (reset)beginQ <= 8'b0;end else if (load)beginQ <= D;endendmodule//二路选择器模块module mux(s,x,y,m);parameter WIDTH=8;input [WIDTH-1:0] x,y;input s;output [WIDTH-1:0] m;assign m =(s?y:x);endmodule4.2(第二个数据通路)//主模块moduletext2(SUM_SEL,NEXT_SEL,A_SEL,LD_SUM,LD_NEXT,NEXT_ZERO,outSUM_SEL,outNEXT_SE L,outA_SEL,outSUM,outNEXT,outA1,outA2,outMEM);parameter WIDTH=8;input SUM_SEL,NEXT_SEL,A_SEL,LD_SUM,LD_NEXT;wire [WIDTH-1:0]inSUM_SEL00,inSUM_SEL01,outSUM_SEL,inNEXT_SEL00,inNEXT_SEL01,outNEXT_SEL;output [WIDTH-1:0]outSUM_SEL,outNEXT_SEL,outA_SEL,outSUM,outNEXT,outA1,outA2,outMEM;output NEXT_ZERO;mux #(WIDTH) SUM_SEL(SUM_SEL,inSUM_SEL00,inSUM_SEL01,outSUM_SEL);mux #(WIDTH) NEXT_SEL(NEXT_SEL,inNEXT_SEL00,inNEXT_SEL01,outNEXT_SEL);mux #(WIDTH) A_SEL(A_SEL,inA_SEL00,inA_SEL01,outA_SEL);register #(WIDTH) SUM(inSUM,Clk,reset,LD_SUM,outSUM);register #(WIDTH) NEXT(inNEXT,Clk,reset,LD_NEXT,outNEXT);add #(WIDTH) A1(inA10,inA11,outA1);add #(WIDTH) A2(inA20,inA21,outA2);ROM #(WIDTH,WIDTH) MEM(outMEM,inMEM);COM #(WIDTH) COM(inCOM0,inCOM1,NEXT_ZERO); assign inA10=outSUM;assign inA11=outMEM;assign inNEXT_SEL00=outMEM;assign inNEXT_SEL01=0;assign inSUM_SEL00=outA1;assign inSUM_SEL01=0;assign inSUM=outSUM_SEL;assign inNEXT=outNEXT_SEL;assign inA20=outNEXT;assign inA21=1;assign inA_SEL00=outNEXT;assign inA_SEL01=outA2;assign inMEM=outA_SEL;assign inCOM0=outNEXT_SEL;assign inCOM1=0;endmodulemodule COM(a,b,out);parameter WIDTH=8;input [WIDTH-1:0] a,b;output out;reg out;always @(a or b)beginif(a>b)out=1;else out=0;endendmodule//存储器模块module ROM(ROM_data, ROM_addr);parameter data_WIDTH=8;parameter addr_WIDTH=8;output [addr_WIDTH-1:0] ROM_data;input [addr_WIDTH-1:0] ROM_addr;reg [addr_WIDTH-1:0] ROM [data_WIDTH-1:0]; // defining 4x2 ROMassign ROM_data = ROM[ROM_addr]; // reading ROM content at the address ROM_addr initial $readmemb ("ROM_data.txt", ROM, 0, 3); // load ROM content from ROM_data.txt file endmodule//寄存器模块module register(D,Clk,reset,load,Q);parameter WIDTH=8;input [WIDTH-1:0] D;input Clk,reset,load;output reg [WIDTH-1:0] Q;always @(posedge Clk)if (reset)beginQ <= 8'b0;end else if (load)beginQ <= D;endendmodule//加法器模块module add(A,B,C);parameter WIDTH=8;input [WIDTH-1:0] A, B;output [WIDTH-1:0] C;wire [WIDTH:0] DA TA;assign DATA=A+B;assign C=DATA[7:0];endmodule//二路选择器模块module mux(s,x,y,m);parameter WIDTH=8;input [WIDTH-1:0] x,y;input s;output [WIDTH-1:0] m;assign m =(s?y:x);endmodule5.1_1module lab5_1_1(input clk, input reset, input ain, output reg yout, output reg [3:0] count);reg [1:0] state, nextstate;parameter S0=0, S1=1, S2=2, S3=3;always @(posedge clk) // always block to update stateif (reset) beginstate <= S0;count = 0;endelsestate <= nextstate;always @(state or ain) // always block to compute output beginyout = 0;case(state)S0: if(!ain)yout = 1;S1: yout = 0;S2: yout = 0;S3: if(ain)yout = 1;endcaseendalways @(posedge clk) // always block to compute output beginif(ain)count = count + 1;endalways @(state or ain) // always block to compute nextstate begincase(state)S0: if(ain)nextstate = S1;else nextstate = S0;S1: if(ain)nextstate = S2;else nextstate = S1;S2: if(ain)nextstate = S3;else nextstate = S2;S3: if(ain)nextstate = S1;else nextstate = S3;endcaseendendmodule仿真程序:module lab5_1_1_tb();reg clk,reset,ain;wire yout;wire [3:0] count;integer i;parameter TIME = 400;parameter DELAY = 5;lab5_1_1 DUT (.clk(clk), .ain(ain), .count(count), .reset(reset), .yout(yout));initial begin#TIME $finish;endinitial beginclk = 0;for(i = 0; i < (TIME/DELAY); i = i + 1)#DELAY clk = ~clk;endinitial beginreset = 1;#(4*DELAY) reset = 0;#(34*DELAY) reset = 1;#(2*DELAY) reset = 0;endinitial beginain = 0;#(8*DELAY) ain = ~ain;#(4*DELAY) ain = ~ain;#(12*DELAY) ain = ~ain;#(8*DELAY) ain = ~ain;#(4*DELAY) ain = ~ain;#(6*DELAY) ain = ~ain;#(6*DELAY) ain = ~ain;endendmodule5.1_2module lab5_1_2(input clk, input reset, input [1:0] x, output reg yout, output reg [2:0] nextstate);reg [2:0] state;parameter S0=0, S11=1, S21=2, S31=3, S12=4, S22=5, S32=6;always @(posedge clk) // always block to update stateif (reset) beginstate <= S0;nextstate = S0;yout = 0;endelsestate <= nextstate;always @(state) // always block to compute output begincase(state)S0: yout = yout;S12: yout = 0;S22: yout = 1;S32: yout = ~yout;endcaseendalways @(state or x) // always block to compute nextstate begincase(state)S0: if(x == 1)nextstate = S11;else if(x == 3)nextstate = S21;else if(x == 2)nextstate = S31;S11: if(x == 0) nextstate = S12;else if(x == 1) nextstate = S11;else if(x == 3) nextstate = S21;else if(x == 2) nextstate = S31;S12: if(x == 1) nextstate = S11;else if(x == 3) nextstate = S21;else if(x == 2) nextstate = S31;S21: if(x == 0) nextstate = S22;else if(x == 1) nextstate = S11;else if(x == 3) nextstate = S21;else if(x == 2) nextstate = S31;S22: if(x == 1) nextstate = S11;else if(x == 3) nextstate = S21;else if(x == 2) nextstate = S31;S31: if(x == 0) nextstate = S32;else if(x == 1) nextstate = S11;else if(x == 3) nextstate = S21;else if(x == 2) nextstate = S31;S32: if(x == 1) nextstate = S11;else if(x == 3) nextstate = S21;else if(x == 2) nextstate = S31;endcaseendendmodule仿真程序:module lab5_1_2_tb();reg clk,reset;reg [1:0] x;wire [2:0] nextstate;wire yout;integer i;parameter TIME = 200;parameter DELAY = 5;lab5_1_2 DUT (.clk(clk), .x(x), .reset(reset), .yout(yout), .nextstate(nextstate));initial begin#TIME $finish;endinitial beginclk = 0;for(i = 0; i < (TIME/DELAY); i = i + 1)#DELAY clk = ~clk;endinitial beginreset = 1;#(4*DELAY) reset = 0;endinitial beginx = 0;#(8*DELAY) x = 3;#(2*DELAY) x = 2;#(2*DELAY) x = 0;#(4*DELAY) x = 2;#(2*DELAY) x = 0;#(2*DELAY) x = 3;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 2;#(2*DELAY) x = 3;#(2*DELAY) x = 0;#(6*DELAY) x = 2;#(6*DELAY) x = 0;endendmodule5.1_3module lab5_1_3(input clk, input reset, input x, output reg [2:0] yout, output reg [2:0] nextstate);reg [2:0] state;parameter S0=0, S1=1, S2=2, S3=3, S4=4, S5=5;always @(posedge clk) // always block to update stateif (reset) beginstate <= S0;nextstate = S0;endelsestate <= nextstate;always @(state or x) // always block to compute outputbegincase(state)S0: yout = 0;S1: yout = 1;S2: yout = 3;S3: yout = 5;S4: yout = 7;S5: yout = 2;endcaseendalways @(x or state) // always block to compute nextstate begincase(state)S0: if(x)nextstate = S1;else nextstate = S0;S1: if(x)nextstate = S2;else nextstate = S1;S2: if(x)nextstate = S3;else nextstate = S2;S3: if(x)nextstate = S4;else nextstate = S3;S4: if(x)nextstate = S5;else nextstate = S4;S5: if(x)nextstate = S0;else nextstate = S5;endcaseendendmodule仿真程序:module lab5_1_3_tb();reg clk,reset;reg x;wire [2:0] nextstate;wire [2:0] yout;integer i;parameter TIME = 400;parameter DELAY = 5;lab5_1_3 DUT (.clk(clk), .x(x), .reset(reset), .yout(yout), .nextstate(nextstate));initial begin#TIME $finish;endinitial beginclk = 0;for(i = 0; i < (TIME/DELAY); i = i + 1)#DELAY clk = ~clk;endinitial beginreset = 1;#(4*DELAY) reset = 0;endinitial beginx = 0;#(8*DELAY) x = 1;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 0;#(2*DELAY) x = 1;#(2*DELAY) x = 0;endendmodule5.2module lab5_2_1(input clk, input reset, input ain, output reg yout, output reg [3:0] count);reg [1:0] state, nextstate;parameter S0=0, S1=1, S2=2, S3=3;always @(posedge clk) // always block to update stateif (reset) beginstate <= S0;count = 0;endelse beginstate <= nextstate;if(ain)count = count + 1;endalways @(state) // always block to compute outputbeginyout = 0;case(state)S0: yout = 0;S1: yout = 0;S2: yout = 0;S3: yout = 1;endcaseendalways @(posedge clk) // always block to compute output beginendalways @(state or ain) // always block to compute nextstate begincase(state)S0: if(ain)nextstate = S1;else nextstate = S0;S1: if(ain)nextstate = S2;else nextstate = S1;S2: if(ain)nextstate = S3;else nextstate = S2;S3: if(ain)nextstate = S1;else nextstate = S3;endcaseendendmodule仿真程序:module lab5_2_1_tb();reg clk,reset,ain;wire yout;wire [3:0] count;integer i;parameter TIME = 400;parameter DELAY = 5;lab5_2_1 DUT (.clk(clk), .ain(ain), .count(count), .reset(reset), .yout(yout));initial begin#TIME $finish;endinitial beginclk = 0;for(i = 0; i < (TIME/DELAY); i = i + 1)#DELAY clk = ~clk;endinitial beginreset = 1;#(4*DELAY) reset = 0;#(34*DELAY) reset = 1;#(2*DELAY) reset = 0;endinitial beginain = 0;#(8*DELAY) ain = ~ain;#(4*DELAY) ain = ~ain;#(12*DELAY) ain = ~ain;#(8*DELAY) ain = ~ain;#(4*DELAY) ain = ~ain;#(6*DELAY) ain = ~ain;#(6*DELAY) ain = ~ain;endendmodul·指导教师评定意见·一、原创性声明本人郑重声明本报告内容,是由作者本人独立完成的。