存储器及其与系统的连接

- 格式:pptx

- 大小:837.64 KB

- 文档页数:39

存储器测试方法、设备及系统与流程随着计算机技术的不断发展,计算机存储器的容量和性能越来越高,但存储器出现故障的概率并不会因此降低。

因此,为了保障计算机的正常运行,存储器的测试工作显得尤为重要。

本篇文章将详细介绍存储器测试方法、设备及系统与流程。

一、存储器测试方法:1、慢速测试法慢速测试是通过使用单元测试的方法来测试存储器中的每一个单元。

测试程序可以在存储器中对每个字节进行写入和读取,然后比较已读取的值与已写入的值是否相同,从而检测出存储器中是否存在故障。

2、快速测试法快速测试是在较短时间内对整个存储器进行测试。

测试程序将一组随机数据写入存储器,接着读取这些数据,然后再重新写入存储器。

最后再次读取存储器中数据,如果已读取的数据能够与写入的数据相匹配,就表明存储器无故障。

3、缺陷测试法缺陷测试是通过创建一些未写入正确值的未用存储器单元,从而测试出存储器中的故障。

测试程序将对存储器进行写入和读取操作,如果读取的数据与待读取的数据不同,就可以推断出存储器存在故障。

此方法需要测试时事先创建有缺陷的存储器单元。

二、存储器测试设备:1、存储器测试仪器存储器测试仪器主要用于检测存储器中是否存在故障,改善存储器的质量。

它主要由存储器测试板卡、测试软件、测试控制卡和测试工作站组成。

2、存储器测试芯片存储器测试芯片是一种专用的集成电路,用于测试 DRAM 和SRAM 存储器中的故障。

它可以与存储器芯片直接连接,进行数据交换,并根据测试程序对存储器单元进行写入和读取操作。

三、存储器测试系统与流程:1、存储器测试系统存储器测试系统主要由测试板卡、测试软件、测试控制卡和测试工作站组成。

测试软件由存储器测试程序和控制程序两部分组成,存储器测试程序用于测试存储器芯片,控制程序用于控制测试过程。

测试控制卡作为中间连接,负责存储器测试程序和工作站、测试板卡之间的数据传输。

2、存储器测试流程存储器测试流程包括以下几个步骤:(1)准备测试:将需要测试的存储器芯片连接至测试平台上,根据程序要求设置测试参数。

实验五 存储器连接(6116的使用)【实验名称】存储器连接(6116的使用)。

【实验目的】 掌握存储器译码及读写的方法。

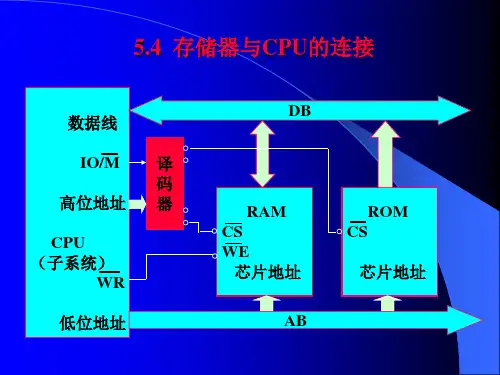

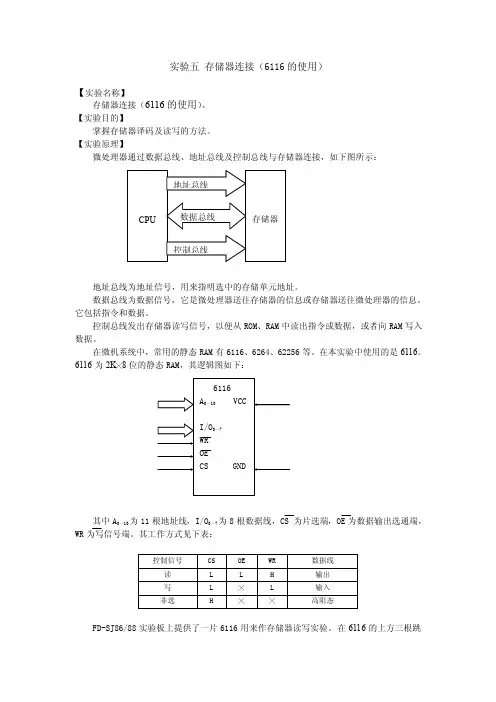

【实验原理】 微处理器通过数据总线、地址总线及控制总线与存储器连接,如下图所示:地址总线为地址信号,用来指明选中的存储单元地址。

数据总线为数据信号,它是微处理器送往存储器的信息或存储器送往微处理器的信息。

它包括指令和数据。

控制总线发出存储器读写信号,以便从ROM 、RAM 中读出指令或数据,或者向RAM 写入数据。

在微机系统中,常用的静态RAM 有6116、6264、62256等。

在本实验中使用的是6116。

6116为2K ╳8位的静态RAM ,其逻辑图如下:其中A 0~10为11根地址线,I/O 0~7为8根数据线,CS 为片选端,OE 为数据输出选通端,WR 为写信号端。

其工作方式见下表:FD-SJ86/88实验板上提供了一片6116用来作存储器读写实验。

在6116的上方三根跳线J57、J58、J59分别用来设置6116的片选端、读信号、写信号的连接状态。

当以短路块分别将J57、J58、J59上面两根针短路时,则6116片选端连接由U39产生的译码信号,其译码范围为0A0000H~0A07FFH,因6116为2K存储器,所以地址0A0000H~0A07FFH和0A0800H~0A0FFFH重叠。

6116的读写信号则分别接到系统总线上的存储器读写信号。

其数据通过74LS245(U38)接到系统的数据总线上。

【实验内容】在FD-SJ86/88实验板上的6116芯片内写入一些数据,然后读出显示在屏幕上以验证正确与否。

【实验连线】① 6264的地址线J8(A0~A10)接总线上的地址线A0~A10。

② J57、J58、J59的下面的两个脚以短路块连接。

【实验程序】DATA SEGMENTMESSAGE DB 'PLEASE ENTER A KEY TO SHOW THE CONTENTS',0DH,0AH,'$'DATA ENDSSTACK SEGMENT STACKSTA DW 50 DUP(?)TOP EQU LENGTH STASTACK ENDSCODE SEGMENTASSUME CS:CODE,DS:DATA,SS:STACK,ES:DATASTART: MOV AX,DATAMOV DS,AXMOV AX,STACKMOV SS,AXMOV SP,TOPMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26MOV DL,40HWRITE: INC DLMOV ES:[BX],DLINC BXCMP DL,5AHJNZ SS1MOV DL,40HSS1: LOOP WRITEMOV DX,OFFSET MESSAGEMOV AH,9INT 21HMOV AH,01HINT 21HMOV AX,0A000HMOV ES,AXMOV BX,0000HMOV CX,26READ: MOV DL,ES:[BX]MOV AH,02HINT 21HINC BXLOOP READMOV AH,4CHINT 21HCODE ENDSEND START【思考题】将字符‘0’~‘9’写入存储器,再将其读出,应如何修改程序?。

一、实验目的1. 了解存储器的结构及其与CPU的连接方式。

2. 掌握存储器的位扩展、字扩展和字位扩展方法。

3. 通过实际操作,加深对存储器扩展原理的理解,提高动手实践能力。

二、实验原理存储器扩展是计算机硬件设计中常见的技术,目的是为了满足系统对存储容量的需求。

存储器扩展主要分为位扩展、字扩展和字位扩展三种方式。

1. 位扩展:当存储芯片的数据位小于CPU对数据位的要求时,可以通过位扩展来解决。

位扩展是将多个存储芯片的数据总线并联,形成一个更高位宽的数据总线,与CPU的数据总线相连。

2. 字扩展:当存储芯片的存储容量不能满足CPU对存储容量的要求时,可以通过字扩展来解决。

字扩展是将多个存储芯片的数据总线、读写控制线并联,形成一个更大容量的存储器,与CPU的数据总线、读写控制线相连。

3. 字位扩展:字位扩展是位扩展和字扩展的结合,既能扩展存储容量,又能扩展数据位宽。

三、实验设备1. 实验箱2. 逻辑分析仪3. 逻辑门电路4. 实验指导书四、实验步骤1. 搭建存储器扩展电路(1)根据实验要求,选择合适的存储芯片,如SRAM、ROM等。

(2)根据存储芯片的规格,确定存储器的容量、数据位宽和地址线位数。

(3)根据存储器的容量和位宽,计算所需的存储芯片数量。

(4)搭建存储器扩展电路,包括存储芯片、地址译码器、数据线、读写控制线等。

2. 仿真实验(1)使用逻辑分析仪观察存储器扩展电路的信号波形。

(2)通过实验指导书提供的测试程序,对存储器进行读写操作。

(3)观察逻辑分析仪的信号波形,分析存储器扩展电路的工作情况。

3. 分析实验结果(1)根据实验结果,验证存储器扩展电路是否满足实验要求。

(2)分析存储器扩展电路的优缺点,提出改进措施。

五、实验结果与分析1. 实验结果通过实验,搭建了存储器扩展电路,实现了存储器的位扩展、字扩展和字位扩展。

逻辑分析仪的信号波形显示,存储器扩展电路工作正常,满足实验要求。

2. 实验分析(1)位扩展:通过位扩展,实现了存储器数据位宽的增加,满足了CPU对数据位宽的要求。

计算机原理-存储器和I/O设备和总线前言前一篇文章介绍了冯诺依曼体系结构的计算机的基本工作原理,其中主要介绍了CPU的结构和工作原理。

这一篇主要来介绍存储区,总线,以及IO设备等其他几大组件,来了解整个计算机是如何工作的。

这些东西都是看得见摸得着的硬件,平时我们买电脑时最关注的就是CPU的速度,内存的大小,主板芯片等等的参数。

1. 存储器前面我们以一个简单通用的计算机模型来介绍了CPU的工作方式,CPU执行指令,而存储器为CPU提供指令和数据。

在这个简单的模型中,存储器是一个线性的字节数组。

CPU可以在一个常数的时间内访问每个存储器的位置,虽然这个模型是有效的,但是并不能完全反应现代计算机实际的工作方式。

1.1 存储器系统层次结构在前面介绍中,我们一直把存储器等同于了内存,但是实际上在现代计算机中,存储器系统是一个具有不同容量,不同访问速度的存储设备的层次结构。

整个存储器系统中包括了寄存器、Cache、内部存储器、外部存储。

下图展示了一个计算机存储系统的层次图。

层次越高速度越快,但是价格越高,而层次越低,速度越慢,价格越低。

相对于CPU来说,存储器的速度是相对比较慢的。

无论CPU如何发展,速度多块,对于计算机来说CPU总是一个稀缺的资源,所以我们应该最大程度的去利用CPU。

其面我们提到过CPU周期,一个CPU周期是取1条指令的最短的时间。

由此可见,CPU周期在很大程度上决定了计算机的整体性能。

你想想如果当CPU去取一条指令需要2s,而执行一个指令只需要2ms,对于计算机来说性能是多么大的损失。

所以存储器的速度对于计算机的速度影响是很大的。

对于我们来说,总是希望存储器的速度能和CPU一样或尽量的块,这样一个CPU周期需要的时钟周期就越少。

但是现实是,这样的计算机可能相当的昂贵。

所以在计算机的存储系统中,采用了一种分层的结构。

速度越快的存储器容量越小,这样就能做到在性能和格之间的一个很好的平衡。

价1.2 存储技术计算机的发展离不开存储器的发展,早起的计算机没用硬盘,只有几千字节的RAM可用。

8086系统连接两片存储器的方法

8086系统可以连接两片存储器的方法主要有两种:并行连接和串行连接。

1. 并行连接:

并行连接是指将两片存储器同时连接到8086的数据总线上,并且使用不同的地址线来选择不同的存储器。

这种连接方式可以同时访问两片存储器,提高了数据传输的速度。

具体的连接方式如下:

- 将两片存储器的数据引脚连接到8086的数据总线上。

- 将两片存储器的地址引脚连接到8086的地址总线上,并使用不同的地址线来选择不同的存储器。

- 将两片存储器的读写控制引脚连接到8086的读写控制引脚上,以控制存储器的读写操作。

2. 串行连接:

串行连接是指将两片存储器连接到8086的一个存储器模块上,通过串行方式进行数据传输。

具体的连接方式如下:

- 将两片存储器连接到8086的存储器模块的数据引脚上。

- 将两片存储器的地址引脚连接到8086的地址总线上,并使用相同的地址线来选择存储器。

- 将两片存储器的读写控制引脚连接到8086的读写控制引脚上,以控制存储器的读写操作。

- 在8086的存储器模块中配置相应的控制逻辑,以实现对两片

存储器的串行读写操作。

需要注意的是,无论是并行连接还是串行连接,都需要保证两片存储器的地址范围不重叠,以避免冲突。

此外,还需要根据具体的存储器类型和接口来选择适当的连接方式和电路设计。

作业题目:141页第6、7题。

上交时间:2020年11月7日23:59:59学生姓名:侯永志学号:1960170124评分标准:第6题6分、第7题14分,共20分。

特别提醒:①凡发现复制粘贴他人作业者,就视为抄袭。

抄袭者和被抄袭者本次作业均按0分处理。

②用Word排版不易的内容,可以先手写,在拍照,把照片插入Word中。

③作业文件的命名格式:学号姓名,例如:1919202021张三.doc。

6.在8086系统中,若用1024×1位的RAM芯片组成16K×8位的存储器,需要多少芯片?在CPU的地址线中有多少位参与片内寻址?多少位用作芯片组选择信号?解:(1)1024*1位的RAM芯片即1K*1位的RAM芯片,组成16K×8位的存储器,需要16*8=128片芯片。

(2)分16组合成,每组8片构成1K*8位,16组共16K*8位,每组均为10个地址脚(2^10=1024),因此地址线中有10位参与片内寻址。

(3)每组都需要1个选择信号,16组需要16个选择信号,2^4=16,因此地址线中有4位作为片选信号。

7.试使用62512(64K*8位)和28C512(64K*8位),在8086系统(最小工作模式)中设计具有256KB RAM、128KB E^2PROM的存储体,RAM的地址从0000:0000H开始、E^2PROM的地址从E000:0000H开始。

解:62512是64K×8容量的芯片,组成256KB需要四片62512,起始地址为:00000H,地址范围为:00000H~3FFFFH。

28C512是64K×8容量的芯片,组成128KB需要两片28C512。

起始地址为:E0000H,地址范围为:E0000H~FFFFFH。

地址范围分配表如下:注:U1、U3、U5为偶地址存储体,U2、U4、U6为奇地址存储体。

62512(64K*8位):U1、U2、/3、/4;28C512(64K*8位):U5、U6。