第8章 CMOS基本逻辑单元

- 格式:pdf

- 大小:969.83 KB

- 文档页数:13

CMOS电路基础原理CMOS(互补金属氧化物半导体)电路是现代电子领域中常用的集成电路设计技术。

它在数字逻辑电路和模拟电路中广泛应用,并且具有低功耗、高集成度以及较强的抗干扰能力等优点。

本文将介绍CMOS电路的基础原理。

一、CMOS电路结构CMOS电路由N沟道金属氧化物半导体场效应管和P沟道金属氧化物半导体场效应管构成。

N沟道和P沟道管具有互补的传输特性,能够有效降低功耗。

CMOS电路结构包括传输门、组合逻辑电路和时钟电路等。

1. 传输门传输门是CMOS电路的基本单元,常见的有与门、或门以及非门等。

与门由一对并联的P沟道和N沟道管组成,当且仅当两个输入信号同时为高电平时,输出为高电平。

或门由一对串联的P沟道和N沟道管组成,当且仅当两个输入信号中至少一个为高电平时,输出为高电平。

非门由两个逆并联的P沟道和N沟道管组成,当输入信号为高电平时,输出为低电平。

2. 组合逻辑电路CMOS电路中的组合逻辑电路包括与非门、异或门等。

与非门由与门和非门级联而成,输入信号经过与门进行与操作,然后再经过非门进行取反操作。

异或门由与非门和异或非门级联而成,输入信号经过与非门进行与非操作,然后再经过异或非门进行异或操作。

3. 时钟电路CMOS电路中的时钟电路包括振荡电路和触发器等。

振荡电路用于产生稳定的时钟信号,常见的电路有RC振荡电路和LC振荡电路等。

触发器用于存储和传输信息,常见的触发器有RS触发器、D触发器以及JK触发器等。

二、CMOS电路工作原理CMOS电路的工作原理基于PN结和MOSFET的特性。

当控制电压施加于PN结时,PN结正向偏置导通,反向偏置截止。

同时,对于MOSFET来说,当栅极电压低于阈值电压时,沟道断开;当栅极电压高于阈值电压时,沟道导通。

CMOS电路中,P沟道MOSFET和N沟道MOSFET的栅极交替连接,形成互补对。

当输入信号为低电平时,P沟道MOSFET导通,N 沟道MOSFET截止;当输入信号为高电平时,P沟道MOSFET截止,N沟道MOSFET导通。

CMOS逻辑门电路CMOS逻辑门电路是在TTL电路问世之后,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件。

CMOS电路的工作速度可与TTL 相比较,而它的功耗和抗干扰能力则远优于TTL。

此外,几乎所有的超大规模存储器件,以及PLD器件都采用CMOS艺制造,且费用较低。

早期生产的CMOS门电路为4000系列,随后发展为4000B系列。

当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。

下面首先讨论CMOS反相器,然后介绍其他CMO逻辑门电路。

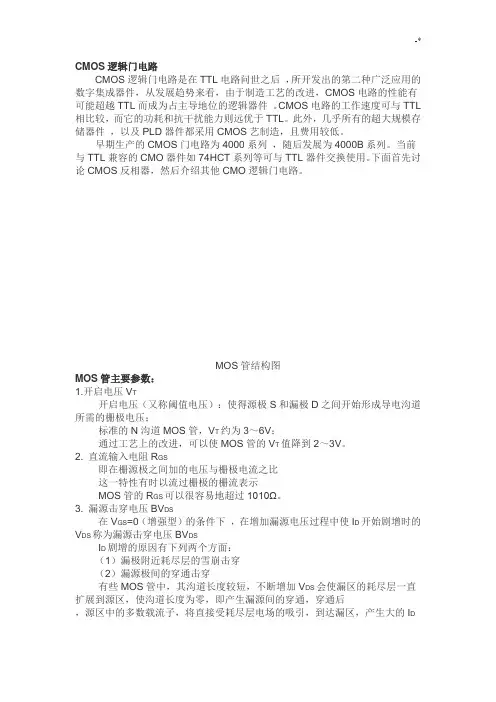

MOS管结构图MOS管主要参数:1.开启电压V T·开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;·标准的N沟道MOS管,V T约为3~6V;·通过工艺上的改进,可以使MOS管的V T值降到2~3V。

2. 直流输入电阻R GS·即在栅源极之间加的电压与栅极电流之比·这一特性有时以流过栅极的栅流表示·MOS管的R GS可以很容易地超过1010Ω。

3. 漏源击穿电压BV DS·在V GS=0(增强型)的条件下,在增加漏源电压过程中使I D开始剧增时的V DS称为漏源击穿电压BV DS·I D剧增的原因有下列两个方面:(1)漏极附近耗尽层的雪崩击穿(2)漏源极间的穿通击穿·有些MOS管中,其沟道长度较短,不断增加V DS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后,源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的I D4. 栅源击穿电压BV GS·在增加栅源电压过程中,使栅极电流I G由零开始剧增时的V GS,称为栅源击穿电压BV GS。

5. 低频跨导g m·在V DS为某一固定数值的条件下,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导·g m反映了栅源电压对漏极电流的控制能力·是表征MOS管放大能力的一个重要参数·一般在十分之几至几mA/V的范围内6. 导通电阻R ON·导通电阻R ON说明了V DS对I D的影响,是漏极特性某一点切线的斜率的倒数·在饱和区,I D几乎不随V DS改变,R ON的数值很大,一般在几十千欧到几百千欧之间·由于在数字电路中,MOS管导通时经常工作在V DS=0的状态下,所以这时的导通电阻R ON可用原点的R ON来近似·对一般的MOS管而言,R ON的数值在几百欧以内7. 极间电容·三个电极之间都存在着极间电容:栅源电容C GS 、栅漏电容C GD和漏源电容CDS·C GS和C GD约为1~3pF·C DS约在0.1~1pF之间8. 低频噪声系数NF·噪声是由管子内部载流子运动的不规则性所引起的·由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化·噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)·这个数值越小,代表管子所产生的噪声越小·低频噪声系数是在低频范围内测出的噪声系数·场效应管的噪声系数约为几个分贝,它比双极性三极管的要小一、CMOS反相器由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。

CMOS电平转换电路详解COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。

COMS电路的供电电压VDD范围比较广在+5~+15V均能正常工作,电压波动允许10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0。

CMOS电路输出高电平约为0.9Vcc,而输出低电平约为0.1Vcc.当输入电压高于VDD-1.5V时为逻辑1,输入电压低于VSS+1.5V(VSS为数字地)为逻辑0。

TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑1,0V 等价于逻辑0,这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。

标准TTL输入高电平最小2V,输出高电平最小2.4V,典型值3.4V,输入低电平最大0.8V,输出低电平最大0.4V,典型值0.2V(输入H》2V,输入L《0.8V;输出H 》2.4V(3.4V),输出L《0.4V(0.2V)。

CMOS电平是数字信号还是模拟信号?CMOS电平是数字信号,COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许10,当输出电压高于VDD-0.5V 时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0,一般数字信号才是0和1 。

cmos电平转换电路1、TTL电路和CMOS电路的逻辑电平VOH:逻辑电平1 的输出电压VOL:逻辑电平0 的输出电压VIH :逻辑电平1 的输入电压VIH :逻辑电平0 的输入电压TTL电路临界值:。

第8章存储器与可编程逻辑器件8.1存储器概述自测练习1.存储器中可以保存的最小数据单位是()。

(a)位(b)字节(c)字2.指出下列存储器各有多少个基本存储单元?多少存储单元?多少字?字长多少?(a)2K×8位()()()()(b)256×2位()()()()(c)1M×4位()()()()3.ROM是()存储器。

(a)非易失性(b)易失性(c)读/写(d)以字节组织的4.数据通过()存储在存储器中。

(a)读操作(b)启动操作(c)写操作(d)寻址操作5.RAM给定地址中存储的数据在()情况下会丢失。

(a)电源关闭(b)数据从该地址读出(c)在该地址写入数据(d)答案(a)和(c)6.具有256个地址的存储器有()地址线。

(a)256条(b)6条(c)8条(d)16条7.可以存储256字节数据的存储容量是()。

(a)256×1位(b)256×8位(c)1K×4位(d)2K×1位答案:1. a2.(a)2048×8;2048;2048;8(b)512;256;256;2(c)1024×1024×4;1024×1024;1024×1024;43.a4.c5.d6.c7.b8.2随机存取存储器(RAM)自测练习1.动态存储器(DRAM)存储单元是利用()存储信息的,静态存储器(SRAM)存储单元是利用()存储信息的。

2.为了不丢失信息,DRAM必须定期进行()操作。

3.半导体存储器按读、写功能可分成()和()两大类。

4.RAM电路通常由()、()和()三部分组成。

5.6116RAM有()根地址线,()根数据线,其存储容量为()位。

答案:1.栅极电容,触发器2.刷新3.只读存储器,读/写存储器4.地址译码,存储矩阵,读/写控制电路5.11,8,2K×8位8.3 只读存储器(ROM)自测练习1.ROM可分为()、()、()和()几种类型。

第八章半导体存储器和可编程逻辑器件一、填空题1、一个10位地址码、8位输出的ROM,其存储容量为或。

2、将一个包含有32768个基本存储单元的存储电路设计16位为一个字节的ROM。

该ROM有根地址线,有根数据读出线。

二、综合题1、试写出图6-1所示阵列图的逻辑函数表达式和真值表,并说明其功能。

01F2F3图6-1 例6-1逻辑图2、试用256×4位的RAM扩展成1024×8位存储器。

3、下列RAM各有多少条地址线?⑴512×2位⑵1K×8位⑶2K×1位⑷16K×1位⑸256×4位⑹64K×1位4、写出由ROM所实现的逻辑函数的表达式。

(8分)Y1Y25、四片16×4RAM 和逻辑门构成的电路如图6-7所示。

试回答:AB AB 4AB AB 0地址线数据线图6-7 多片RAM 级联逻辑图⑴单片RAM 的存储容量,扩展后的RAM 总容量是多少?⑵图6-7所示电路的扩展属位扩展,字扩展,还是位、字都有的扩展? ⑶当地址码为00010110时,RAM0~RAM3,哪几片被选中?6.用ROM 设计一个组合逻辑电路,用来产生下列一组逻辑函数。

画出存储矩阵的点阵图。

D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=1 D C B A D C B A D C B A D C B A Y ⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=2 D C B D B A Y ⋅⋅+⋅⋅=3D B D B Y ⋅+⋅=47、画出实现下面双输出逻辑函数的PLD 表示。

D C AB CD B A D C B A D C B A D C B A f ABCC B A C B A C B A f ),,,( ),,(21+++=++=三、简答题1、可编程逻辑器件是如何进行分类的?2、GAL16V8的OLMC 中4个数据选择器各有多少功能?3、ROM 和RAM 有什么相同和不同之处?ROM 写入信息有几种方式?4、为什么用ROM 可以实现逻辑函数式?第八章 习题答案一、填空题1、2138K 2、11 16 二、综合题1、解:根据与阵列的输出为AB 的最小项和阵列图中有实心点·为1,无·为0,可以写出AB W F ==30B A AB B A B A W W W F +=++=++=3211B A B A B A F ⊕=+=2AB B A B A B A B A W W W F =+=++=++=2103从上述逻辑表达式可以看出,图6-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。

半导体集成电路复习题及答案第8章动态逻辑电路填空题对于⼀般的动态逻辑电路,逻辑部分由输出低电平的⽹组成,输出信号与电源之间插⼊了栅控制1、极为时钟信号的 ,逻辑⽹与地之间插⼊了栅控制极为时钟信号的。

【答案:NMOS, PMOS, NOMS】对于⼀个级联的多⽶诺逻辑电路,在评估阶段:对PDN⽹只允许有跳变,对 PUN⽹只允许有跳变,2、PDN与PDN相连或PUN与PUN相连时中间应接⼊。

【答案:】解答题从逻辑功能,电路规模,速度3⽅⾯分析下⾯2电路的相同点和不同点。

从⽽说明CMOS动态组合逻辑1、电路的特点。

【答案:】图A是CMOS静态逻辑电路。

图B是CMOS动态逻辑电路。

2电路完成的均是NAND的逻辑功能。

图B的逻辑部分电路使⽤了2个MOS管,图A使⽤了4个MOS管,由此可以看出动态组合逻辑电路的规模为静态电路的⼀半。

图B的逻辑功能部分全部使⽤NMOS管,图A即使⽤NMOS也使⽤PMOS,由于NMOS的速度⾼于PMOS,说明动态组合逻辑电路的速度⾼于静态电路。

2、分析下⾯的电路,指出它完成的逻辑功能,说明它和⼀般动态组合逻辑电路的不同,说明其特点。

【答案:】该电路可以完成OUT=AB的与逻辑。

与⼀般动态组合逻辑电路相⽐,它增加了⼀个MOS管M kp,这个MOS 管起到了电荷保持电路的作⽤,解决了⼀般动态组合逻辑电路存在的电荷泄漏的问题。

3、分析下列电路的⼯作原理,画出输出端OUT的波形。

【答案:】答案:4、结合下⾯电路,说明动态组合逻辑电路的⼯作原理。

【答案:】动态组合逻辑电路由输出信号与电源之间插⼊的时钟信号PMOS,NMOS逻辑⽹和逻辑⽹与地之间插⼊的时钟信号NMOS组成。

当时钟信号为低电平时,PMOS导通,OUT被拉置⾼电平。

此时电路处于预充电阶段。

当时钟信号为低电平时,PMOS截⾄,电路与V DD的直接通路被切断。

这时NOMS导通,当逻辑⽹处于特定逻辑时,电路输出OUT被接到地,输出低电平。

《半导体集成电路》课程教学大纲(包括《集成电路制造基础》和《集成电路原理及设计》两门课程)集成电路制造基础课程教学大纲课程名称:集成电路制造基础英文名称:The Foundation of Intergrate Circuit Fabrication课程类别:专业必修课总学时:32 学分:2适应对象:电子科学与技术本科学生一、课程性质、目的与任务:本课程为高等学校电子科学与技术专业本科生必修的一门工程技术专业课。

半导体科学是一门近几十年迅猛发展起来的重要新兴学科,是计算机、雷达、通讯、电子技术、自动化技术等信息科学的基础,而半导体工艺主要讨论集成电路的制造、加工技术以及制造中涉及的原材料的制备,是现今超大规模集成电路得以实现的技术基础,与现代信息科学有着密切的联系。

本课程的目的和任务:通过半导体工艺的学习,使学生掌握半导体集成电路制造技术的基本理论、基本知识、基本方法和技能,对半导体器件和半导体集成电路制造工艺及原理有一个较为完整和系统的概念,了解集成电路制造相关领域的新技术、新设备、新工艺,使学生具有一定工艺分析和设计以及解决工艺问题和提高产品质量的能力。

并为后续相关课程奠定必要的理论基础,为学生今后从事半导体集成电路的生产、制造和设计打下坚实基础。

二、教学基本要求:1、掌握硅的晶体结构特点,了解缺陷和非掺杂杂质的概念及对衬底材料的影响;了解晶体生长技术(直拉法、区熔法),在芯片加工环节中,对环境、水、气体、试剂等方面的要求;掌握硅圆片制备及规格,晶体缺陷,晶体定向、晶体研磨、抛光的概念、原理和方法及控制技术。

2、掌握SiO2结构及性质,硅的热氧化,影响氧化速率的因素,氧化缺陷,掩蔽扩散所需最小SiO2层厚度的估算;了解SiO2薄膜厚度的测量方法。

3、掌握杂质扩散机理,扩散系数和扩散方程,扩散杂质分布;了解常用扩散工艺及系统设备。

4、掌握离子注入原理、特点及应用;了解离子注入系统组成,浓度分布,注入损伤和退火。

CMOS集成电路基础知识CMOS是ComplementaryMetal-OxideSemiconductor一词的缩写。

在业余电子制作中我们经常会用到它,这里系统、详细的介绍一些CMOS 集成电路基础知识及使用注意事项。

CMOS集成电路的性能及特点功耗低CMOS集成电路采用场效应管,且都是互补结构,工作时两个串联的场效应管总是处于一个管导通,另一个管截止的状态,电路静态功耗理论上为零。

实际上,由于存在漏电流,CMOS电路尚有微量静态功耗。

单个门电路的功耗典型值仅为20mW,动态功耗(在1MHz工作频率时)也仅为几mW。

工作电压范围宽CMOS集成电路供电简单,供电电源体积小,基本上不需稳压。

国产CC4000系列的集成电路,可在3~18V电压下正常工作。

逻辑摆幅大CMOS集成电路的逻辑高电平“1”、逻辑低电平“0”分别接近于电源高电位VDD及电影低电位VSS。

当VDD=15V,VSS=0V时,输出逻辑摆幅近似15V。

因此,CMOS集成电路的电压电压利用系数在各类集成电路中指标是较高的。

抗干扰能力强CMOS集成电路的电压噪声容限的典型值为电源电压的45%,保证值为电源电压的30%。

随着电源电压的增加,噪声容限电压的绝对值将成比例增加。

对于VDD=15V的供电电压(当VSS=0V时),电路将有7V 左右的噪声容限。

输入阻抗高CMOS集成电路的输入端一般都是由保护二极管和串联电阻构成的保护网络,故比一般场效应管的输入电阻稍小,但在正常工作电压范围内,这些保护二极管均处于反向偏置状态,直流输入阻抗取决于这些二极管的泄露电流,通常情况下,等效输入阻抗高达103~1011Ω,因此CMOS集成电路几乎不消耗驱动电路的功率。

温度稳定性能好由于CMOS集成电路的功耗很低,内部发热量少,而且,CMOS电路线路结构和电气参数都具有对称性,在温度环境发生变化时,某些参数能起到自动补偿作用,因而CMOS集成电路的温度特性非常好。

CMOS图像传感器原理与应用简介摘要:本文介绍了CMOS图像传感器器件的原理、性能、优点、问题及应对措施,以及CMOS图像传感器的市场状况和一些应用领域。

Brief introduction of principle and applications of CMOS imagesensorAbstract: This paper introduces the principle, performance, advantages also with the problems and solutions of CMOS image sensor. The market status and applications are also given in this essay.北京航空航天大学李育琦1引言图像传感器是将光信号转换为电信号的装置,在数字电视、可视通信市场中有着广泛的应用。

60年代末期,美国贝尔实脸室发现电荷通过半导体势阱发生转移的现象,提出了固态成像这一新概念和一维CCD(Charge-Coupled Device电荷耦合器件)模型器件。

到90年代初,CCD技术已比较成热,得到非常广泛的应用。

但是随着CCD应用范围的扩大,其缺点逐渐暴露出来。

首先,CCD技术芯片技术工艺复杂,不能与标准工艺兼容。

其次,CCD技术芯片需要的电压功耗大,因此CCD技术芯片价格昂贵且使用不便。

目前,最引人注目,最有发展潜力的是采用标准的CMOS(Complementary Metal Oxide Semiconductor 互补金属氧化物场效应管)技术来生产图像传感器,即CMOS图像传感器。

CMOS图像传感器芯片采用了CMOS工艺,可将图像采集单元和信号处理单元集成到同一块芯片上。

由于具有上述特点,它适合大规模批量生产,适用于要求小尺寸、低价格、摄像质量无过高要求的应用,如保安用小型、微型相机、手机、计算机网络视频会议系统、无线手持式视频会议系统、条形码扫描器、传真机、玩具、生物显微计数、某些车用摄像系统等大量商用领域。

CMOS门电路以MOS(Metal-Oxide Semiconductor)管作为开关元件的门电路称为MOS门电路。

由于MOS型集成门电路具有制造工艺简单、集成度高、功耗小以及抗干扰能力强等优点,因此它在数字集成电路产品中占据相当大的比例。

与TTL 门电路相比,MOS门电路的速度较低。

MOS门电路有三种类型:使用P沟道管的PMOS电路、使用N沟道管的NMOS电路和同时使用PMOS和NMOS 管的CMOS电路。

其中CMOS性能更优,因此CMOS门电路是应用较为普遍的逻辑电路之一。

1. CMOS非门图3-16所示是一个N沟道增强型MOS管TN和一个P沟道增强型MOS管TP组成的CMOS非门。

图3-16 CMOS非门电路图3-17 CMOS与非门电路两管的栅极相连作为输入端,两管的漏极相连作为输出端。

TN的源极接地,TP的源极接电源。

为了保证电路正常工作,VDD需要大于TN管开启电压VTN和TP管开启电压VTP的绝对值的和,即UDD> UTN+ |UTP|。

当Ui=0V 时,TN截止,TP导通,Uo≈UDD为高电平;当Ui=UDD时,TN导通,TP截止,Uo≈0V为低电平。

因此实现了非逻辑功能。

CMOS非门除了有较好的动态特性外,由于CMOS非门电路工作时总有一个管子导通,所以当带电容负载时,给电容充电和放电都比较快。

CMOS非门的平均传输延迟时间约为10ns。

另外由于它处在开关状态下总有一个管子处于截止状态,因而电流极小,电路的静态功耗很低,一般为微瓦(mW)数量级。

2. CMOS与非门图3-17所示为一个两输入端的CMOS与非门电路,它由两个串联的NMOS管和两个并联的PMOS管构成。

每个输入端连到一个PMOS管和一个NMOS管的栅极。

当输入A、B均为高电平时,TN1和TN2导通,TP1和TP2截止,输出端为低电平;当输入A、B中至少有一个为低电平时,对应的TN1和TN2中至少有一个截止,TP1和TP2中至少由一个导通,输出F为高电平。

8.2.1 CMOS 互补逻辑

图8.11 CMOS 互补逻辑

反相器

与非门

或非门

综合逻辑门

(1) 基本的CMOS 与非门、或非门

图CMOS 与非门和或非门

CMOS 与非门:P 并N 串

CMOS 或非门:P 串N 并

CMOS 与非门、或非门的不同表示符号

NAND2 logic circuit.

NAND2 VTC analysis.

Layout of NAND2 for V M calculation.

Simplification of the series-connected

nFETs.

Simplification of parallel-connected

pFETs.

,仅使用另一输入端作开关转换时

NOR2 VTC construction.

按最佳噪容要求,无论是与非门还是或非门,最佳噪容条件为为了稳定输出高低电平,可在输入输出端分别加倒相器作缓冲级。

下图所示为带缓冲级的二输入端与非门电路。

CMOS 集成门的输出缓冲级:输出特性与倒相器相同

B

A B A Y ⋅=+=带缓冲级的CMOS 与非门电路

带缓冲级的CMOS 或非门电路

B

A B A Y +=⋅=下图所示为带缓冲级的二输入端或非门电路。

静态CMOS 逻辑门具有以下特点

实现8个变量“与”的三种方案

用与或非门实现“异或”“同或”功能)

伪NMOS逻辑

(a) 与非门(b) 或非门

8.2.3 动态CMOS逻辑

()E

+

=简化电路

Z+

AB

C

D

NMOS传送晶体管传输门在传输高电平时,受到门导通阈电压的

传输门电路结

传输门导通电阻r=r||r,比传送晶体管导通电阻小。

CMOS传输门电路与表示

图传输门传输高电平过程

(2) 传输低电平

图传输门传输低电平过程

管为漏负载级(V=V),P管为源跟随器V

其分析过程与传输高电平时类似。

图九管CMOS传输门

3) 改进电路——九管CMOS传输门

一种改进的CMOS传输门电路如图所示。

TG的

流水线式两相N-P CMOSφ逻辑级

CMOS电路低功耗的特点。

预充电鉴别逻辑(2) 与经典的静态CMOS逻辑相比,P-E逻辑的优缺点:优点:

•不需互补结构(每个输入端勿需P、N管搭配)。

•无比电路,所有逻辑门可采用最小尺寸。

P-E逻辑的级联方式8.2.5 CMOS多米诺(Domino)逻辑

CMOS多米诺逻辑

图17

多米诺CMOS逻辑单元的级联

多米诺逻辑的级联方式

(多米诺逻辑可直接实现多级级联)

8.3 级联级的负载

影响门的电气和物理结构设计的因素

8.4.1 MOS管的串联和并联

串联方式工作时,相当于沟道长度增长并联方式工作时,等效为沟道宽度增大

8.4.3 源漏电容8.4.4 电荷的再分配

(MUX--Multiplexer )

多开关的一个典型)给P400F B A 图8.27

CMOS 结构的多路转换开关克服了NMOS 结构所存在的传输高电平阈值电压损耗和串联电阻大的问题,但晶体管数目增加了一倍。

图8.27

图8.27

V 图8.27

8.7 RS 触发器

特性表实际上是一种特殊的真值表,它对触发

器的描述十分具体。

这种真值表的输入变量(自变量)除了数据输入外,还有触发器的初态,而输出RS 触发器的状态转换图JK 触发器的状态转换图

T 触发器的状态转换图

N 阱

N 阱

N 阱

8.8.1 NMOS结构的时钟脉冲控制触发器

时,输入信号才会起作用。

同步RS触发器

结构的时钟脉冲控制触发器

8.9.2 CMOS D触发器

x接x

N阱N阱

N阱

Schmitt Trigger)

压,二者的差值称为回差。

输出电平的变化滞后于输入,形成回环。

②与双稳态触发器和单稳态触发器A Y

我们知道,门电路有一个阈值电压,当输入

利用施密特触发器可以将非矩形波变。