广工EDA数字逻辑第5章

- 格式:doc

- 大小:581.25 KB

- 文档页数:29

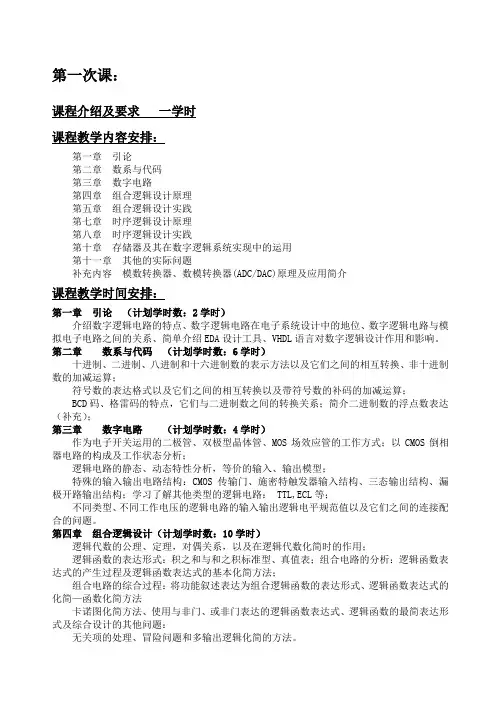

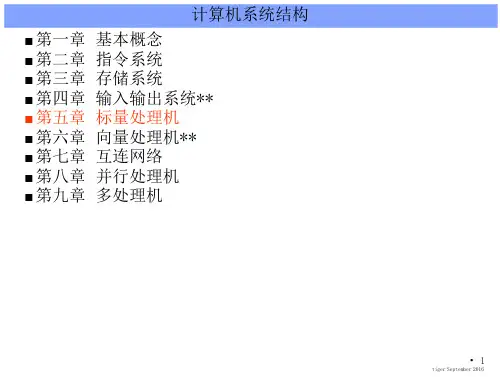

第一次课:课程介绍及要求一学时课程教学内容安排:第一章引论第二章数系与代码第三章数字电路第四章组合逻辑设计原理第五章组合逻辑设计实践第七章时序逻辑设计原理第八章时序逻辑设计实践第十章存储器及其在数字逻辑系统实现中的运用第十一章其他的实际问题补充内容模数转换器、数模转换器(ADC/DAC)原理及应用简介课程教学时间安排:第一章引论(计划学时数:2学时)介绍数字逻辑电路的特点、数字逻辑电路在电子系统设计中的地位、数字逻辑电路与模拟电子电路之间的关系、简单介绍EDA设计工具、VHDL语言对数字逻辑设计作用和影响。

第二章数系与代码(计划学时数:6学时)十进制、二进制、八进制和十六进制数的表示方法以及它们之间的相互转换、非十进制数的加减运算;符号数的表达格式以及它们之间的相互转换以及带符号数的补码的加减运算;BCD码、格雷码的特点,它们与二进制数之间的转换关系;简介二进制数的浮点数表达(补充);第三章数字电路(计划学时数:4学时)作为电子开关运用的二极管、双极型晶体管、MOS场效应管的工作方式;以CMOS倒相器电路的构成及工作状态分析;逻辑电路的静态、动态特性分析,等价的输入、输出模型;特殊的输入输出电路结构:CMOS传输门、施密特触发器输入结构、三态输出结构、漏极开路输出结构;学习了解其他类型的逻辑电路: TTL,ECL等;不同类型、不同工作电压的逻辑电路的输入输出逻辑电平规范值以及它们之间的连接配合的问题。

第四章组合逻辑设计(计划学时数:10学时)逻辑代数的公理、定理,对偶关系,以及在逻辑代数化简时的作用;逻辑函数的表达形式:积之和与和之积标准型、真值表;组合电路的分析:逻辑函数表达式的产生过程及逻辑函数表达式的基本化简方法;组合电路的综合过程:将功能叙述表达为组合逻辑函数的表达形式、逻辑函数表达式的化简—函数化简方法卡诺图化简方法、使用与非门、或非门表达的逻辑函数表达式、逻辑函数的最简表达形式及综合设计的其他问题:无关项的处理、冒险问题和多输出逻辑化简的方法。

(完整)数字逻辑第五章编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望((完整)数字逻辑第五章)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为(完整)数字逻辑第五章的全部内容。

第五章触发器------—----——-—--—-——-—-——------———--—-———--———————-——-—-—-———-—————-——-—---1 :具有:置0、置1、保持和翻转功能的触发器是( ).A:JK触发器B:SR触发器C:D触发器D:T触发器您选择的答案: 正确答案: A知识点:JK触发器的特性为:J=0, K=0时,Q状态为保持;J=0, K=1时,Q状态为置0;J=1, K=0时,Q状态为置1;J=1, K=1时,Q状态为翻转--—--———----—----—---—---—---—-——--—-——--——--—--------——--—--———-—--—-------2 :对于JK触发器,输入J=0,K=1,CLK脉冲作用后,触发器的次态应为()。

A:0B:1C:Q'D:不确定您选择的答案: 正确答案: A知识点:JK触发器的特性为:J=1, K=1时,Q状态为翻转,即Q= Q’-————---———---————--————--—-——-————--—---—-——-—-—---——--—--------——--—--—-—-3 :有一个或非门构成的SR锁存器,欲使该锁存器保持原态即Q*=Q,则输入信号应为()。

A:S=R=0B:S=R=1C:S=1,R=0D:S=0,R=1您选择的答案:正确答案: A知识点:或非门构成的SR锁存器的特性为:R=1, S=0 Q*=0, Q*'=1,即锁存器被置0(0状态);R=0, S=1 Q*=1, Q*'=0,即锁存器被置 1(1状态);R=S=0, Q*=Q,即锁存器保持原态;R= S=1 Q*=Q*'=0,此为不允许输入。

计算机学院专业班__组、学号姓名协作者______________ 教师评定_________________实验题目基于Libero的数字逻辑设计仿真及验证实验1、熟悉EDA工具的使用;仿真基本门电路。

2、仿真组合逻辑电路。

3、仿真时序逻辑电路。

4、基本门电路、组合电路和时序电路的程序烧录及验证。

5、数字逻辑综合设计仿真及验证。

实验报告1、基本门电路一、实验目的1、了解基于Verilog的基本门电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

3、学习针对实际门电路芯片74HC00、74HC02、74HC04、74HC08、74HC32、74HC86进行VerilogHDL设计的方法。

二、实验环境Libero仿真软件。

三、实验内容1、掌握Libero软件的使用方法。

2、进行针对74系列基本门电路的设计,并完成相应的仿真实验。

3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成74HC00、74HC02、74HC04、74HC08、74HC32、74HC86相应的设计、综合及仿真。

4、提交针对基本门电路的综合结果,以及相应的仿真结果。

四、实验结果和数据处理1、门电路...模块及测试平台代码清单注:文件命名要求。

工程(project)名要求:学号末4位+下划线+BasGate,例如陈静(3212005896)的工程名为“5896_BasGate”。

设计代码文件名1:要求同上,即“5896_BasGate.v”。

测试平台文件名:自己定义。

(1)// 模块一:2输入与门、或门、与非、或非、异或门各一,输入信号(1位A,1位B),输出信号(Y1,Y2,Y3,Y4,Y5)module gates_1(A,B,Y1,Y2,Y3,Y4,Y5);input A,B;output Y1,Y2,Y3,Y4,Y5;assign Y1=A&B;assign Y2=A|B;assign Y3=~(A&B);assign Y4=~(A|B);assign Y5=A^B;endmodule(2)// 模块二:6个非门(同74HC04)module gates_2(A,Y);input [1:6]A;output [1:6]Y;assign Y=~A;endmodule(3)测试平台代码`timescale 1ns/1nsmodule testgates_1();reg A,B;wire Y1,Y2,Y3,Y4,Y5;gates_1 v1(A,B,Y1,Y2,Y3,Y4,Y5);initialbeginA=0;B=0;#10 B=1;#10 A=1;#10 B=0;#10;endendmodulemodule testgates_2();reg [1:6]A;wire [1:6]Y;gates_2 v2(A,Y);initialbeginA=000001;#10 A=A<<1;#10 A=A<<1;#10 A=A<<1;#10 A=A<<1;#10 A=A<<1;endendmodule2、模块一第一次仿真结果(截图..,调整窗口至合适大..)。

广工数字逻辑课程设计一、课程目标知识目标:1. 理解数字逻辑电路的基本概念,掌握逻辑门、组合逻辑电路和时序逻辑电路的分类及功能;2. 学会分析并设计简单的数字逻辑电路,理解其工作原理;3. 掌握数字逻辑电路的测试与调试方法,能够运用所学知识解决实际问题。

技能目标:1. 培养学生运用数字逻辑电路设计软件进行电路设计的能力;2. 培养学生动手搭建和调试数字逻辑电路的技能;3. 培养学生团队协作和沟通表达的能力,能够就设计过程中遇到的问题进行讨论和解决。

情感态度价值观目标:1. 培养学生对数字逻辑电路的兴趣,激发学生的学习热情;2. 培养学生严谨、细心的科学态度,养成良好的实验习惯;3. 培养学生创新思维,敢于尝试新方法,勇于克服困难;4. 培养学生具备信息安全意识,了解数字逻辑电路在国家安全和社会发展中的重要作用。

课程性质:本课程为工程专业课程,旨在使学生掌握数字逻辑电路的基本知识,培养实际设计和应用能力。

学生特点:学生具备一定的电子技术基础知识,对数字逻辑电路有一定了解,但实际操作和设计经验不足。

教学要求:结合学生特点和课程性质,采用理论教学与实验操作相结合的方式,注重培养学生的实践能力和创新精神。

通过本课程的学习,使学生能够达到上述课程目标,为后续相关课程和实际工作打下坚实基础。

二、教学内容1. 数字逻辑基础:逻辑门电路、布尔代数及其应用、逻辑函数的化简与实现。

教材章节:第1章 数字逻辑基础2. 组合逻辑电路:编码器、译码器、数据选择器、算术逻辑单元等组合电路的设计与分析。

教材章节:第2章 组合逻辑电路3. 时序逻辑电路:触发器、计数器、寄存器等时序电路的原理、设计与实现。

教材章节:第3章 时序逻辑电路4. 数字电路设计方法:自上而下设计方法、层次化设计方法、EDA工具的应用。

教材章节:第4章 数字电路设计方法5. 数字逻辑电路测试与调试:故障诊断、测试生成、测试方法及测试设备。

教材章节:第5章 数字逻辑电路测试与调试6. 实践项目:结合所学知识,分组进行数字逻辑电路设计、搭建、调试及优化。

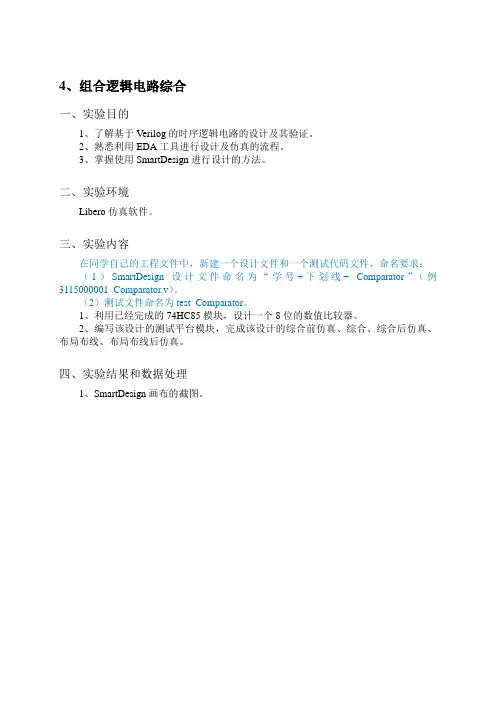

4、组合逻辑电路综合一、实验目的1、了解基于Verilog的时序逻辑电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

3、掌握使用SmartDesign进行设计的方法。

二、实验环境Libero仿真软件。

三、实验内容在同学自己的工程文件中,新建一个设计文件和一个测试代码文件,命名要求:(1)SmartDesign设计文件命名为“学号+下划线+ Comparator”(例3115000001_Comparator.v)。

(2)测试文件命名为test_Comparator。

1、利用已经完成的74HC85模块,设计一个8位的数值比较器。

2、编写该设计的测试平台模块,完成该设计的综合前仿真、综合、综合后仿真、布局布线、布局布线后仿真。

四、实验结果和数据处理1、SmartDesign画布的截图。

2、测试平台代码`timescale 1ns/1nsmodule test_Comparator;reg [7:0] ina,inb;reg ig,ie,is;wire qg,qe,qs;hyf5_Comparatoru10(.DataA(ina),.DataB(inb),.ing(ig),.ine(ie),.ins(is),.Qg(qg),.Qe(qe),.Qs(qs));initialbeginina=0;repeat(20)#20 ina=$random;endinitialbegininb=0;repeat(20)#20 inb=$random;endinitialbeginig=0;ie=0;is=0;repeat(40)#10 {ig,ie,is}=$random; endinitial#400 $finish;endmodule3、综合前仿真截图4、综合的截图5、综合后仿真截图6、布局布线后仿真的截图。

5、时序逻辑电路一、实验目的1、了解基于Verilog的时序逻辑电路的设计及其验证。

2、熟悉利用EDA工具进行设计及仿真的流程。

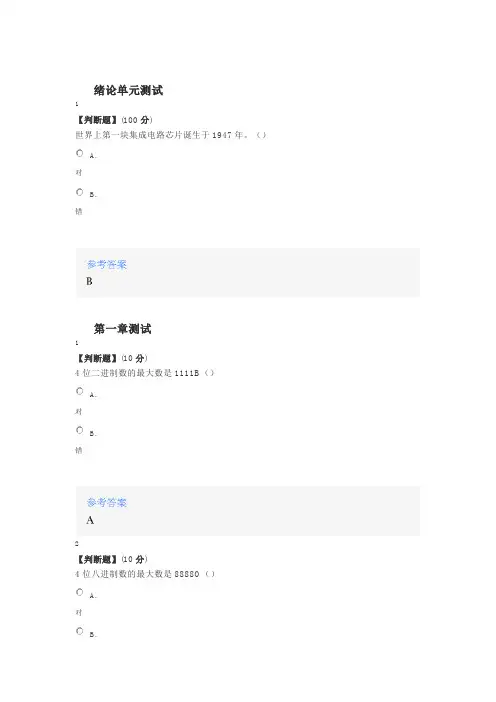

绪论单元测试1【判断题】(100分)世界上第一块集成电路芯片诞生于1947年。

()A.对B.错第一章测试1【判断题】(10分)4位二进制数的最大数是1111B()A.对B.错2【判断题】(10分)4位八进制数的最大数是8888O()A.对B.错3【判断题】(10分)4位十六进制数的最大数是FFFFH()A.错B.对4【判断题】(10分)与4位二进制数的最大值等值的十进制数是15()A.对B.错5【判断题】(10分)与4位八进制数的最大值等值的十进制数是4038()A.错B.对6【判断题】(10分)与4位十六进制数的最大值等值的十进制数为65535()A.对B.错7【判断题】(10分)二进制数(1011.11)2的十进制数是11.3()A.对B.错8【判断题】(10分)十进制数(26.335)10转换成二进制数是=(11010.011)2()A.错B.对9【判断题】(10分)(000101010000)8421BCD是(150)10也是(96)16()A.对B.错10【判断题】(10分)用BCD码表示十进制数(36)10=(00110111)8421BCD()A.错B.对第二章测试1【判断题】(10分)两个变量的异或运算和同或运算之间是反逻辑的关系。

()A.错B.对2【判断题】(10分)代入定理中对代入逻辑式的形式和复杂程度有限制。

()A.对B.错3【判断题】(10分)将一个约束项写人逻辑函数式或不写入逻辑函数式,对函数的输出有影响。

()A.错B.对4【判断题】(10分)将一个任意项写人逻辑函数式或不写入逻辑函数式,对函数的输出无影响。

()A.对B.错5【判断题】(10分)去掉无关项才能得到更简单的逻辑函数化简结果。

()A.对B.错6【判断题】(10分)逻辑运算是逻辑变量与及常量之间逻辑的算术运算,是数量之间的运算。

()A.错B.对7【判断题】(10分)在逻辑代数中交换律和普通代数的运算规则是相同的。

广工的数电课程设计一、课程目标知识目标:1. 理解数字电路的基本概念,掌握数字逻辑电路的组成、功能及表达方式;2. 学会分析简单的组合逻辑电路和时序逻辑电路,并能运用逻辑代数简化逻辑表达式;3. 掌握基本的数字电路设计方法,能够设计简单的数字系统。

技能目标:1. 能够运用所学知识对数字电路进行正确分析,具备解决实际问题的能力;2. 能够运用数字电路设计方法,设计简单的数字系统,并进行仿真验证;3. 能够熟练运用相关软件工具,如Multisim、Protel等,进行数字电路的原理图绘制和仿真。

情感态度价值观目标:1. 培养学生对数字电路的兴趣,激发学生主动探索、创新的精神;2. 培养学生具备良好的团队合作意识,学会与他人共同解决问题;3. 增强学生的工程意识,认识到数字电路在现代社会中的重要作用,培养学生的社会责任感。

分析课程性质、学生特点和教学要求,本课程目标旨在使学生在掌握数字电路基本知识的基础上,能够运用所学分析和解决实际问题,培养具备创新意识和实践能力的优秀人才。

通过课程学习,将目标分解为具体的学习成果,以便后续的教学设计和评估。

二、教学内容1. 数字电路基本概念:包括数字信号与模拟信号的区别、数字电路的特点及分类、数字电路的基本功能单元等。

- 教材章节:第1章 数字电路概述2. 逻辑门电路:介绍基本逻辑门电路(与门、或门、非门等)的工作原理、逻辑功能及其相互组合。

- 教材章节:第2章 逻辑门电路3. 组合逻辑电路:学习组合逻辑电路的分析方法、设计步骤,掌握常用组合逻辑电路(如编码器、译码器、数据选择器等)的功能和应用。

- 教材章节:第3章 组合逻辑电路4. 时序逻辑电路:学习时序逻辑电路的基本概念、分析方法,掌握常用时序逻辑电路(如触发器、计数器等)的工作原理和应用。

- 教材章节:第4章 时序逻辑电路5. 数字电路设计方法:学习数字电路的设计方法,包括逻辑代数简化、逻辑表达式转换、卡诺图应用等,并能够运用这些方法设计简单的数字系统。

习题答案第1章一、单选题(1)B (2)C (3)B (4)C (5)D (6)B (7)C (8)D (9)C (10)C (11)D(12)D(13)A(14)D二、判断题(1)√ (2)√ (3)× (4)× (5)×(6)×(7)√(8)×三、填空题(1)10000111.101、207.5、87.A (2)185.75 (3)1001 0100(4)B A ⋅、B A +、B A B A +、AB B A + (5)C B A ABC C AB ++ (6)C A AD ⋅ (7)B A B A + (8)2n (9)1 (10)1四、综合题(1)① BA B A AD B B A AD DE B B A AD C A A C DE C B B D C A A C B DE C B B BD C A A Y +=++=++=++++=+++++=+++++=)1()()()()(② BA B A B A D D B A B A A D B D B A B A B B A D B A D B A B A B A AB Y +=+++=++++=+++++=+++++=)1)(())(())()(())(( ③ DB C B A D C D B C B DE B B A B C DE B C A D BC A D B D C C B DE B A C B A AC DE B A D BC A C B A D C D B C B AC Y ++=+++++=+++++++=+++++++=+++++++=)1()1()()()((2)① BCD C B D B A B A D C B A Y ++++= 函数卡诺图如下:化简结果为:BD D A D C Y ++=② F(A,B,C,D)=Σm(0,2,4,5,6,7,8,10,12,14) 函数卡诺图如下:化简结果为:D B A D C B A F +=),,,(③ F(A,B,C,D)=Σm(1,2,6,7,10,11)+Σd(3,4,5,13,15)函数卡诺图如下:化简结果为:⎪⎩⎪⎨⎧=++=∑0)15,13,5,4,3(),,,(CB D AC AD C B A F(3)该逻辑图所对应的逻辑表达式如下 AC C B B A Y +⊕++=)(根据真值表,可写出标准与或式如下 ABC C AB C B A C B A C B A C B A Y +++++= (4)根据表达式画出逻辑图如下A BCY第2章一、单选题(1)B (2)CDA (3)D (4)C (5)C (6)B (7)D(8)B(9)A(10)B二、判断题(1)√ (2)√ (3)× (4)√ (5)√ (6)× (7)√ (8)×(9)×(10)√(11)√三、综合题1.解:由于 0110 + 1011 + 1 = 1 0010, 因此 C out 输出1,S 3 ~ S 1输出0010 2.解:(1)分析设计要求……(2)列真值表……(3)写逻辑表达式776655443322110001270126012501240123012201210120m D m D m D m D m D m D m D m D S S S D S S S D S S S D S S S D S S S D S S S D S S S D S S S D Y +++++++=+++++++=(4)画逻辑图D 0D 1D 2D 3SS YD 4D 5D 6D 7S3.解:(1)分析设计要求 …… (2)列编码表……(3)写逻辑表达式864200874301943212987653I I I I I Y I I I I I Y I I I I I Y II I I I Y ++++=++++=++++=++++= (4)画逻辑图1Y 2Y I 2I 0I 1I 3I 4I 5I 6I 7I 8I 9Y 3Y 04.解:(1)分析设计要求…… (2)列真值表(3)写逻辑表达式130********S DS Y S DS Y S S D Y S S D Y ==== (4)画逻辑图DY 0Y 1Y 2Y 35.解:根据乘法原理A 2 A 1 A 0 ×B 1B 0A 2B 0 A 1B 0 A 0B 0 + A 2B 1 A 1B 1 A 0B 1P 4P 3P 2P 1P 0显然,电路的输入输出信号有: 输入信号:被乘数A (A 2A 1A 0),乘数B (B 1B 0) 输出信号:乘积P (P 4P 3P 2P 1P 0)由乘法原理可见,此乘法器需要6个与门及一个4位加法器,故选择2片74HC08及1片74HC283。

5.7 EDA开发综合实例3:SmartDesign的使用在Libero中,除了可以编写程序实现相应设计外,还可通过可视化操作方式(“SmartDesign”软件),对现成的模块进行连线和拼装,实现特定的功能。

下例采用可视化方法实现1位全加器,再改造为2位串行进位加法器,操作过程既有通过编写代码建立模块,也有调用现成模块,还有通过IP核创建实例模块,并对多个模块进行拼装和测试。

5.7.1 使用半加器构造全加器通过半加器来构造全加器的方法在4.7.3中讨论了,以下的模块及其连接均基于图4-24完成。

1.新建工程打开Libero IDE,选择“Project”菜单的“New Project”命令,输入项目名称、选择项目存放路径,选择语言Verilog(如图5-62所示)。

设备的选择同5.6中的实例2。

2.新建SmartDesign设计在“Project Manager”中点击“SmartDesign”按钮(如图5-63),在弹出的对话框中输入设计名称,如图5-64所示。

工作区中会显示打开了“adders”设计的画布,但画布是一片空白,如图5-65所示。

3.添加半加器模块点击“Project Flow”切换回项目流程,点击“HDL Editor”按钮,输入并新建Verilog 程序文件。

如图5-66所示:在打开的文件中输入半加器程序代码,代码同4.7.3中的半加器设计。

项目会把第一个建立的模块或设计作为“根”(Root),并加粗显示,如果项目中的根不是“adders”,则可在“Design Explorer”窗口中对着“adders”按右键,选择“Set As Root”进行修改。

如图5-68所示:4.在设计中添加“半加器”模块对着“half_adder”模块右键,选择“Instantiate in adders”,或者按着“half_adder”模块拖拽至“adders”的画布(Canvas)上。

重复操作两次,在此需要两个半加器来构造全加器。

操作如图5-69所示:在图中可看到,添加两个模块后,设计中自动设定了模块的实例化名称(half_adder_0 和half_adder_1),直接双击可修改其实例名。

5.在设计中添加“或”模块在“Catalog”窗口中,列出了Libero IDE提供的各种现成可使用的IP核,包括宏单元(Actel Macros)、基本块(Basic Blocks)等。

在搜索栏输入“or2”(也可直接在“Actel Macros”列表中找),可找到在此需要用到的“or2”宏单元(即2输入“或”门)。

点击右键,选择“Instantiate in adders”,或者通过拖拽操作,添加至“adders”的画布(Canvas)上(如图5-70所示)。

6.连线到顶层整个画布就是一个“芯片”的设计,而刚才添加的模块只是该“芯片”的内部零件,故需要定义这些子模块中哪些端口是连接到整个设计的对外(输入/输出)端口上。

对着“half_adder_0”模块的“A”端口按右键,选择“Promote to Top Level”(如图5-71),可把该子模块的端口连接至顶层。

通过类似操作,将“half_adder_0”模块的“B”端口、“half_adder_1”的“B”端口“half_adder_1”的“S”端口、“or2_0”模块的“Y”端口连接到顶层。

由于“half_adder_0”和“half_adder_1”都有名为“B”的端口,故连接到顶层时会有命名上的冲突,如图5-72所示为弹出的对话框,如果选择“是”,则连接到一个新的端口,系统自动给这个端口改名(如“B_0”),如果选择“否”,就会将“half_adder_0”和“half_adder_1”的“B”端口都连接到同一个对外的顶层端口上。

可修改端口的名称,对着要修改的端口名按右键,选择“Modify Port”(或直接双击),输入新的端口名称(如图5-73所示)。

连接并修改端口名后的结果如图5-74所示:7.进行内部连线选择“half_adder_0”的“S”端口,按下“Ctrl”键同时,点击选择“half_adder_1”的“A”端口,同时选中了两个端口,点击右键,选择“Connect”命令,就可把这两个选中的端口进行连线。

如图5-75所示:用同样的方法,把“half_adder_0”的“C”端口与“or2_0”的“A”端口、“half_adder_1”的“C”端口与“or2_0”的“B”端口进行连接。

模块的布局看起来可能会比较乱,连线可能会产生视觉上的重叠,可调整各模块的位置达到较好的显示效果,如图5-76所示:8.规则检查选择“SmartDesign”菜单的“Check Design Rules”命令,工具会自动检查设计是否存在问题(如还有端口没有进行连接等),如果发现问题,按照检查结果的提示进行修正。

至此,一个全加器的设计已完成。

5.7.2 与现有的全加器对比在5.5综合实例1中,已经设计了全加器的模块并保存在磁盘中(“Fadd1.v”文件),在此可调用原来已经完成的模块,将两种设计思路都放到设计中,一起进行验证并对结果进行对比。

1.导入全加器模块在“File”菜单运行“Import Files”命令(如图5-77),找到已保存了的全加器设计文件“Fadd1.v”,点击“Import”按钮导入文件(如图5-78)。

导入文件后,Libero IDE会复制该文件到项目文件夹的“/ hdl”子文件夹下,对该文件中的代码进行改动,不会影响原文件。

2.添加全加器模块到设计中导入文件后,该模块会显示在项目层次结构图中,如图5-79所示:选择“FA_behav2”模块,添加到“adders”设计中(实例化),层次结构也会发生变化,如图5-80所示:3.连线由于“FA_behav2”模块是一个独立的整体,不需要进行内部连线,故全部端口都连接到顶层设计。

为了对比两个设计,将“FA_behav2_0”实例的输入(A,B,Cin)与“全加器1”(半加器组装的)的输入都接到同一个端口(DataA,DataB,Cin),输出端口直接接到顶层设计,如图5-81所示:注:在图5-81中,由于全加器1是由多个部件组装而成,为了更好的显示效果,加入了一个长方体和文字,这些元素可在画布内添加,而不会影响原来的设计。

4.生成设计选择“SmartDesign”菜单的“Check Design Rules”命令,提示“Design Rules Check of SmartDesign ‘adders’ found no errors and no warnings”表示检查无误。

选择“SmartDesign”菜单的“Generate Design”命令(如图5-82所示),或者对着画布区按右键,选择“Generate Design”命令。

提示“Design ‘adders’ was successfully generated”表示生成成功。

5.编写测试平台点击“Project Flow”切换回项目流程,点击“HDL Editor”按钮,在打开的对话框中选择“HDL Stimulus File”,输入测试平台的文件名,如图5-83所示:6.选项配置点击“Project Flow”切换回项目流程,对着“Simulation”按钮按右键,在弹出的菜单中选择“Options”,配置好测试平台模块名称及顶层实例名。

如图5-84所示:仅仅配置这个还不够,还要用右键点击“adders”设计,选择“Organize Stimulus”(如图5-85所示);在弹出的窗口中选择左边窗口中来源为“User”的激励文件“testbench.v”,点击“Add”按钮添加到右边窗口中,并点击“OK”(如图5-86所示)。

读者不禁奇怪,为什么会有两个“testbench.v”,还需额外进行配置才能进行仿真呢?那是因为在本project中调用了Actel提供的宏单元(or2),Libero会自动提供一个“testbench.v”文件,而恰好用户在此也用了“testbench.v”作为测试平台的文件名,故有两个“testbench.v”文件,一个来源是User(用户),一个来源是adders。

7.功能仿真在“Project Flow”中,点击“Simulation”按钮,进行功能仿真(综合前仿真),仿真结果如图5-87所示:说明:(1)由于测试平台中有“$finish”操作,故仿真结束时会提示是否结束“Are you sure you want to finish?”,在此不要选择“是”,否则ModelSim软件将退出。

(2)在波形结果中,两个全加器采用相同的输入(pa,pb,pCin),分别产生不同的输出(“Sum1”,“Cout1”为“全加器1”的输出,“Sum2”,“Cout2”为“FA_behav2”的输出)8. 综合结果对设计进行综合,RTL 视图如图5-88所示:接下来操作包括综合后仿真、布局布线等,实现步骤与5.6的综合实例2相同,在此不作赘述。

5.7.3 改造为2位串行进位加法器1. 设计结构图在第二章(2.3.5)中,讨论了如何通过1位全加器构造多位串行进位加法器,图2-42是一个4位的串行进位加法器,稍作删改,可得到如图5-89所示的2位串行进位加法器。

在此可将现有的2个全加器拼装为2位的串行进位加法器,。

C inC out12. 连线并修改端口名称按照图5-89对“adders ”设计进行改造,更改端口连线及端口名称为如图5-90所示的结构。

3.保存并生成设计选择“File”菜单的“Save adders As”命令,将设计另存为“adder_2”。

选择“SmartDesign”菜单的“Generate Design”命令,或者对着画布区按右键,选择“Generate Design”命令,生成设计。

4.编写测试平台新建测试平台,保存文件为“testbench2.v”。

代码如下:5.选项配置由于新建了另一个设计和测试平台,故须调整若干的选项设置:设置“adder_2”为根,设置方法跟前面是一致的,如图5-91所示:配置测试平台文件,对着“adder_2”模块按右键,选择“Organize Stimulus”(如图5-92所示),把“testbench2.v”文件加到测试平台关联项中(如图5-93所示)。

点击“Project Flow”切换回项目流程,对着“Simulation”按钮按右键,在弹出的菜单中选择“Options”,配置好测试平台模块名称及顶层实例名。

如图5-94所示:6.功能仿真功能仿真结果如图5-95所示:波形说明:(1)a1,a0表示两位输入数据,如“a1=1,a0=0”,则相当于输入两位“A[1:0]=2'b10”;(2)同理,b1,b0可理解为“B[1:0]”,s1,s0可理解为“S[1:0]”,计算的内容相当于“{cout,S[1:0]}=A[1:0] + B[1:0]+cin”;(3)由于是串行进位,仿真结果中考虑了延迟因素,出现了毛刺。