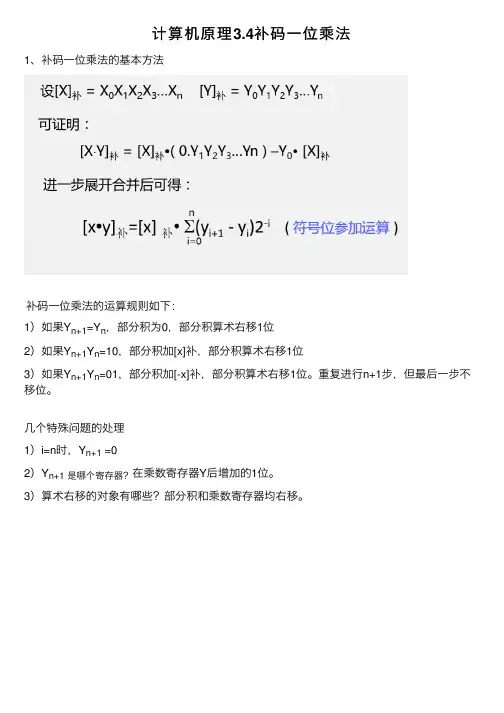

补码乘法

- 格式:docx

- 大小:43.70 KB

- 文档页数:3

6位有符号补码阵列乘法器一. 简介在计算机科学和数字电路设计中,6位有符号补码阵列乘法器是一种重要的电路组件。

补码是一种表示有符号数的编码方式,能够有效地表示负数。

本文将深入探讨6位有符号补码阵列乘法器的原理、设计和应用,并分享对该电路的观点和理解。

二. 原理1. 有符号补码表示有符号补码是一种在计算机中表示负数的常用编码方式。

在6位有符号补码中,最高位表示符号位,0代表正数,1代表负数。

其余位表示数值部分,通过取反加一的方式对负数进行编码。

2. 阵列乘法器阵列乘法器是一种用于执行乘法运算的电路。

6位有符号补码阵列乘法器能够以比较高的效率和较小的面积完成乘法运算。

其主要原理是将乘法运算拆分为多个部分,使用并行的方式进行计算,并最后将结果相加得到最终的乘积。

三. 设计1. 输入和输出6位有符号补码阵列乘法器一般包含两个输入,分别是被乘数和乘数,以及一个输出,即乘积。

被乘数和乘数的输入位数都为6位。

2. 乘法计算乘法计算是6位有符号补码阵列乘法器的核心部分。

它首先对乘数进行拆分,每一位与被乘数相乘,从而生成多个部分乘积。

接下来,对这些部分乘积进行累加,最后得到乘积的结果。

该阵列乘法器的设计需要考虑到乘法运算可能会出现的溢出和进位问题。

3. 控制逻辑6位有符号补码阵列乘法器还需要一些控制逻辑来控制乘法计算的顺序和结果的输出。

这些控制逻辑一般包括时钟信号、使能信号和清零信号等。

四. 应用1. 数字信号处理6位有符号补码阵列乘法器在数字信号处理领域得到广泛应用。

它能够高效地进行乘法运算,常用于滤波器等算法的实现。

2. 图像处理图像处理中经常需要进行像素之间的乘法运算,例如图像增强、滤波和特征提取等。

6位有符号补码阵列乘法器可以在图像处理中快速完成这些乘法运算。

3. 神经网络神经网络是人工智能领域的热门研究方向。

6位有符号补码阵列乘法器能够提供高效的乘法运算支持,可以在神经网络的训练和推理过程中扮演重要角色。

6位有符号补码阵列乘法器1. 介绍在计算机中,我们经常需要进行数字的乘法运算。

而对于有符号的整数,我们需要使用补码来表示。

本文将介绍一种用于进行6位有符号补码乘法运算的阵列乘法器。

2. 有符号补码表示首先,我们需要了解有符号补码的表示方法。

在6位有符号补码中,最高位为符号位,0代表正数,1代表负数。

其余5位用于表示数字的大小。

例如,+3可以用补码表示为0011,而-3可以用补码表示为1101。

3. 阵列乘法器结构阵列乘法器是一种常见且高效的硬件电路结构,用于实现数字乘法运算。

它由多个部件组成,包括乘法单元、加法单元和寄存器等。

在本文中,我们要设计一个6位有符号补码阵列乘法器。

它由以下几个部分组成:3.1 输入端口阵列乘法器需要接收两个输入操作数A和B。

每个操作数都是一个6位的二进制数,并且使用有符号补码表示。

3.2 控制单元控制单元用于控制乘法器的操作。

它根据输入操作数的符号位和乘法器的状态来确定乘法器的运算方式。

3.3 乘法单元乘法单元用于执行两个操作数的相乘操作。

对于6位有符号补码,我们可以使用标准的乘法算法,将两个6位数分别扩展到12位,并进行逐位相乘。

3.4 加法单元加法单元用于将乘法结果相加。

对于6位有符号补码,我们需要考虑进位和溢出情况。

3.5 结果寄存器结果寄存器用于存储最终的计算结果。

它是一个6位的寄存器,可以将计算结果保存在其中。

4. 工作原理下面我们将详细介绍6位有符号补码阵列乘法器的工作原理:1.首先,控制单元根据输入操作数A和B的符号位来确定运算方式。

2.如果A和B都为正数或者都为负数,则直接进行普通乘法运算。

3.如果A为正数而B为负数,则需要将B转换为正数,并在最后计算结果时取反。

4.如果A为负数而B为正数,则需要将A转换为正数,并在最后计算结果时取反。

5.控制单元将A和B送入乘法单元,进行逐位相乘操作。

6.乘法单元的输出经过加法单元,进行相加操作。

7.加法单元的输出经过结果寄存器,存储最终的计算结果。

定点补码一位乘法器的设计一、简介定点补码一位乘法器是一种常见的数字电路设计,用于完成两个定点补码数相乘的操作。

在计算机中,乘法是一个非常基础和重要的操作,因此定点补码一位乘法器的设计对于数字系统的性能有着直接的影响。

在本篇文章中,我们将详细介绍一位乘法器的设计思路与实现方法。

二、原理分析定点补码乘法器的原理基于二进制乘法的基本原理。

乘法的本质是累加多个被乘数与乘法因子相乘的结果。

一位乘法器是指每次只进行一位乘法运算的乘法器。

因为乘法运算是一个递归的过程,所以一位乘法器的设计方法对于多位乘法器的设计有着很高的实用价值。

定点补码的乘法过程中,首先需要将两个操作数分别转换为其对应的补码表示形式。

然后,将乘法因子的每一位与被乘数的每一位相乘,并将每一位的结果累加起来。

最终,我们需要将乘法的结果转换回原来的表示形式。

三、设计过程1.补码转换首先,我们需要将操作数转换为其对应的补码形式。

对于一个定点数(例如8位定点数),其补码形式可以通过将原码取反加一得到。

对于一个n位的定点数,其补码的范围是从-2^(n-1)到2^(n-1)-1、补码的转换可以通过比较操作数的最高位来判断是否为负数,如果是负数,则需要对其取反加一得到补码形式,否则保持原值不变即可。

2.乘法运算乘法运算过程中,我们需要将乘法因子的每一位与被乘数的每一位相乘,并将结果累加起来。

在这个过程中,乘法因子的每一位都需要与被乘数的每一位相乘,并将结果保存在一个暂存器中。

通过多次递进,我们可以求得最终的乘法结果。

3.结果转换乘法运算得到的结果是定点补码形式的。

因此,我们需要将其转换回原来的表示形式。

转换过程可以通过比较结果的最高位来判断是否为负数,如果是负数,则需要对其取反加一得到原码形式,否则保持原值不变即可。

四、设计示例下面我们给出一个8位定点补码一位乘法器的设计示例:输入:A(8位),B(8位)输出:Result (16位)1.补码转换A=(A[7]==1?~(A)+1:A)B=(B[7]==1?~(B)+1:B)2.乘法运算Result = 0for i = 0 to 7:if B[i] == 1:Result += (A << i)3.结果转换Result = (Result[15] == 1 ? ~(Result) + 1 : Result)五、总结定点补码一位乘法器是一种常见的数字电路设计,用于完成两个定点补码数相乘的操作。

补码乘法运算

补码乘法运算是指在计算机中进行的两个补码数相乘的运算。

补码乘法运算的步骤如下:1.将两个补码数的符号位相乘,得到结果的符号位。

2.将两个补码数的绝对值相乘,得到结果的绝对值。

3.将结果的绝对值转换为补码形式。

4.如果结果的符号位与原来两个补码数的符号位不同,则说明结果为负数,需要将结果取反并加1。

例如,计算-3乘以5的结果:-3的补码为11111101,5的补码为00000101。

符号位相乘得到1,结果为负数。

绝对值相乘得到11111011,转换为补码形式为10000101。

由于结果为负数,需要将结果取反并加1,得到补码为01111011,即-15。

因此,-3乘以5的结果为-15。

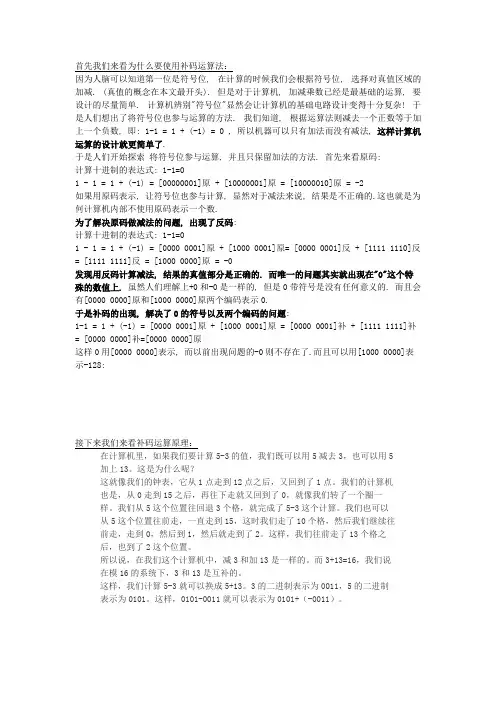

首先我们来看为什么要使用补码运算法:因为人脑可以知道第一位是符号位, 在计算的时候我们会根据符号位, 选择对真值区域的加减. (真值的概念在本文最开头). 但是对于计算机, 加减乘数已经是最基础的运算, 要设计的尽量简单. 计算机辨别"符号位"显然会让计算机的基础电路设计变得十分复杂! 于是人们想出了将符号位也参与运算的方法. 我们知道, 根据运算法则减去一个正数等于加上一个负数, 即: 1-1 = 1 + (-1) = 0 , 所以机器可以只有加法而没有减法, 这样计算机运算的设计就更简单了.于是人们开始探索将符号位参与运算, 并且只保留加法的方法. 首先来看原码:计算十进制的表达式: 1-1=01 - 1 = 1 + (-1) = [00000001]原 + [10000001]原 = [10000010]原 = -2如果用原码表示, 让符号位也参与计算, 显然对于减法来说, 结果是不正确的.这也就是为何计算机内部不使用原码表示一个数.为了解决原码做减法的问题, 出现了反码:计算十进制的表达式: 1-1=01 - 1 = 1 + (-1) = [0000 0001]原 + [1000 0001]原= [0000 0001]反 + [1111 1110]反= [1111 1111]反 = [1000 0000]原 = -0发现用反码计算减法, 结果的真值部分是正确的. 而唯一的问题其实就出现在"0"这个特殊的数值上.虽然人们理解上+0和-0是一样的, 但是0带符号是没有任何意义的. 而且会有[0000 0000]原和[1000 0000]原两个编码表示0.于是补码的出现, 解决了0的符号以及两个编码的问题:1-1 = 1 + (-1) = [0000 0001]原 + [1000 0001]原 = [0000 0001]补 + [1111 1111]补= [0000 0000]补=[0000 0000]原这样0用[0000 0000]表示, 而以前出现问题的-0则不存在了.而且可以用[1000 0000]表示-128:接下来我们来看补码运算原理:在计算机里,如果我们要计算5-3的值,我们既可以用5减去3,也可以用5加上13。

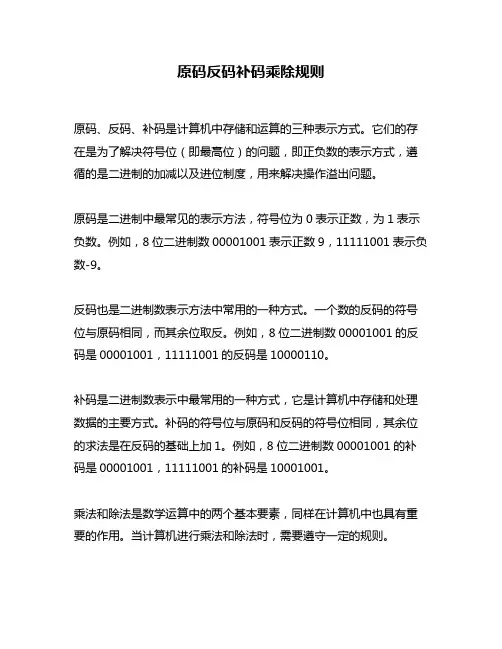

原码反码补码乘除规则原码、反码、补码是计算机中存储和运算的三种表示方式。

它们的存在是为了解决符号位(即最高位)的问题,即正负数的表示方式,遵循的是二进制的加减以及进位制度,用来解决操作溢出问题。

原码是二进制中最常见的表示方法,符号位为0表示正数,为1表示负数。

例如,8位二进制数00001001表示正数9,11111001表示负数-9。

反码也是二进制数表示方法中常用的一种方式。

一个数的反码的符号位与原码相同,而其余位取反。

例如,8位二进制数00001001的反码是00001001,11111001的反码是10000110。

补码是二进制数表示中最常用的一种方式,它是计算机中存储和处理数据的主要方式。

补码的符号位与原码和反码的符号位相同,其余位的求法是在反码的基础上加1。

例如,8位二进制数00001001的补码是00001001,11111001的补码是10001001。

乘法和除法是数学运算中的两个基本要素,同样在计算机中也具有重要的作用。

当计算机进行乘法和除法时,需要遵守一定的规则。

乘法规则:对于两个数相乘,如果两个数的符号相同,则结果为正数,反之为负数。

同时,对于乘数和被乘数的最高位,其符号位可以省略,因为它们的符号可以根据乘积的符号来推断。

除法规则:对于两个数相除,如果两个数的符号相同,则结果为正数,反之为负数。

当被除数和除数为0时,需要抛出异常,因为除数不能为0。

此外,在进行整数除法时,需要注意舍入的方式,应该向0舍入。

综上所述,原码、反码、补码是计算机中所使用的三种数值表示方法。

在进行乘法和除法时,应该遵守一定的规则。

这些知识对于理解计算机底层的运算过程以及提高计算机编程的能力具有重要的意义。

![定点补码一位乘法的实现算法 用[x]补×[y]补直接求[x×y]补](https://uimg.taocdn.com/941c3a6daf1ffc4ffe47ac2f.webp)

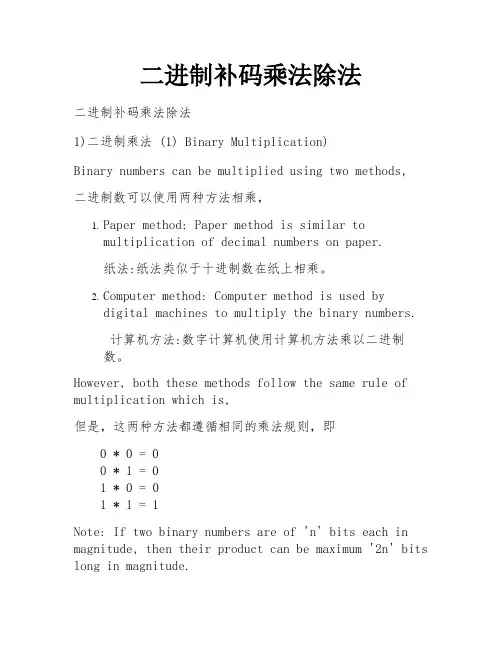

二进制补码乘法除法二进制补码乘法除法1)二进制乘法 (1) Binary Multiplication)Binary numbers can be multiplied using two methods,二进制数可以使用两种方法相乘,1.Paper method: Paper method is similar tomultiplication of decimal numbers on paper.纸法:纸法类似于十进制数在纸上相乘。

puter method: Computer method is used bydigital machines to multiply the binary numbers.计算机方法:数字计算机使用计算机方法乘以二进制数。

However, both these methods follow the same rule of multiplication which is,但是,这两种方法都遵循相同的乘法规则,即0 * 0 = 00 * 1 = 01 * 0 = 01 * 1 = 1Note: If two binary numbers are of 'n' bits each in magnitude, then their product can be maximum '2n' bits long in magnitude.注意:如果两个二进制数的大小均为'n'位,则它们的乘积最大为'2n'位。

长手乘法/纸张方法 (Long Hand Multiplication/Paper Method)The long Hand Multiplication technique is similar to decimal multiplication that we do on paper.长手乘法技术类似于我们在纸上做的十进制乘法。

booth乘法的工作原理

Booth乘法的工作原理是利用移位和加法,实现二进制无符号数的乘法。

具体步骤如下:

1.被乘数X与乘数Y均以补码的形式参加乘法运算,运算结果是积的补码。

2.部分积和被乘数X采用双符号位,乘数Y采用单符号位。

3.初始部分积为0。

运算前,在乘数Y的补码末位添加一位附加位Y,初始值

为0。

4.根据YₙY的值,按照上表进行累加右移操作,右移时遵循补码的移位规则。

5.累加n+1次,右移n次,最后一次不右移。

总的来说,Booth乘法通过特定的操作表进行操作,实现了通过硬件实现的简便算法。

二进制补码运算规则在计算机科学中,二进制补码运算规则是一种用于表示和处理有符号整数的方法。

它是计算机中最常用的表示有符号整数的方式之一,具有很多优点,比如可以方便地进行加法和减法运算,并且可以很容易地进行溢出判断。

二进制补码的表示方法是通过对正整数取反加一来得到负整数的表示。

具体来说,对于一个n位的二进制数,如果最高位是0,则表示一个正整数,数值的计算方式与普通的二进制数相同;如果最高位是1,则表示一个负整数,数值的计算方式为对剩余的n-1位取反加一。

以8位二进制数为例,来看一下二进制补码的运算规则:1. 加法运算:将两个二进制补码相加,如果结果溢出了8位,则溢出位被舍弃。

如果最高位是1,则表示一个负数,如果最高位是0,则表示一个正数。

在进行加法运算时,要注意如果两个数的符号位不同,则执行减法运算。

2. 减法运算:将减数取反得到其补码,然后将被减数与减数的补码相加。

同样,如果结果溢出了8位,则溢出位被舍弃。

如果最高位是1,则表示一个负数,如果最高位是0,则表示一个正数。

3. 取反运算:将一个二进制补码的每一位取反得到其补码的反码。

4. 加一运算:将一个二进制补码加一得到其补码的补码。

通过上述运算规则,我们可以方便地进行二进制补码的运算。

这种表示方法的一个重要优点是可以很容易地进行溢出判断。

在进行加法或减法运算时,如果最高位丢失了,那么就表示发生了溢出。

二进制补码还可以方便地进行乘法和除法运算。

乘法运算可以通过将两个数的补码相乘,再将结果的低位舍弃,得到正确的结果。

除法运算可以通过将两个数的补码相除,再将结果的商和余数进行处理,得到正确的结果。

二进制补码的运算规则在计算机硬件中得到了广泛应用。

计算机中的运算单元和控制单元都会使用二进制补码进行运算。

它不仅可以方便地进行加法和减法运算,还可以很容易地进行乘法和除法运算,从而实现了计算机中的各种运算操作。

总结一下,二进制补码运算规则是一种用于表示和处理有符号整数的方法。

计算机组成原理-定点整数的原码补码运算(待验证)计算机组成原理 - 定点整数的原码补码运算(待验证)⽬录〇、环境对象运算定点整数原码、定点整数补码移位、加、减、乘、除原码定义:x =x0≤x <2n 2n −x −2n <x ≤0其中,n 为x 的位数,最终原码有n+1位。

定义分析:当真值为正时,原码即为真值的⼆进制形式,但是在⼆进制最⾼位添加⼀个0作为符号位(定义没有体现)。

当真值为负时,去掉原码⼆进制形式的负号,在⼆进制最⾼位添加⼀个1作为符号位。

伸展和收缩:由定义分析可知,x 宽度变化时,⾮符号部分添加或移除⾼位0(也即整数的⼆进制形式调整宽度),符号部分不变。

在形式上,⽆论正负,都是在最⾼位新增或移除0。

例0-1 求11b 的8位原码表⽰解:为011,扩展到8位为0000 0011。

例0-2 求−11b 的8位原码表⽰解:100-(-11)=111,扩展到8位为0000 0111。

补码定义:x =x0≤x <2n 2n +1+x −2n ≤x <0其中n 为x 的位数,最终有n+1位(去掉⼀定为0的最⾼位)。

定义分析:当真值为正时,保留真值的⼆进制形式,并在最⾼位添加⼀个0作为符号位。

当真值为负时,则与10...0(共n+2位)相加,联系反码的特点,即将真值负号移除后每位取反,然后加1,然后最⾼位添加1作为符号位。

伸展与收缩:由定义分析,当真值为正时,则和原码⼀致,添加0即可。

当为负时,扩展添0,取反后则为添1,加1时不会影响扩展位(因为负值的⼆进制形式必不全为0),最后保持符号位不变。

形式上,正值在最⾼位添加和删除0,负值扩在最⾼位添加和删除1。

例0-3 求11的8位补码表⽰解:为011,扩展到8位为0000 0011。

例0-4 求-11的8位补码表⽰解:为1000-11=0101,即101,扩展到8位为1111 1101。

还可以利⽤性质来求:^11=00,00+1=01,添加符号位即101。

关于补码以及基本的补码运算0.最基本的,补码怎么得到,这里不讨论。

以及原码和补码的和是0,这个基础的结论,这里不做说明。

1.加法的时候,判断溢出的方法:当两个加数的符号位相同,且结果的符号位与加数符号位不同的时候,则产生了溢出。

显然,两个数,如果异号,显然不会溢出。

溢出,只会出现在同号的情况,则有上面的结论。

2.补码也是有权码。

假如总共有n个比特,除最高位(符号位)以外,每一位的权值为2^i。

而最高位的权值是-2^(n-1)!注意是负的!这一点很好理解:原码和补码的和是2^n,由于总共的位数只有n位,因此和的结果是0,因此补码的最高位权值就是负的。

3.有符号数的乘法(补码的乘法),例子-5*-3:10111101-----------0000011011-----------11101100000-----------111101111011------------1110011100101-------------00001111有符号数的乘法与无符号数的乘法的区别在于:a.在做每一位的乘法的时候,都要做一个位扩展,即扩展符号位。

如上的例子,第一步做1011*1的结果是11011,扩展了一位符号位1。

道理很简单,因为这一步的结果要和下一步做一个加法,而下一步的加数的位宽较现在这一步位宽要宽一位,而加法发生在位宽相同的两个数之间,因此要做一个符号位的扩展。

b.最高位的乘法与其他位稍有不同。

因为最高位的权值是-2^(n-1) ,所以乘法的结果要做一个取反加一的操作。

如上例,1011*1(最高位的1),结果是11011(做符号位扩展),然后做一个取反加一的操作,得到例子中的00101。

4.有符号数的除法:先将有符号数取绝对值,做无符号数的除法,得到结果,最后根据被除数和除数的符号,确定商以及余数的符号。

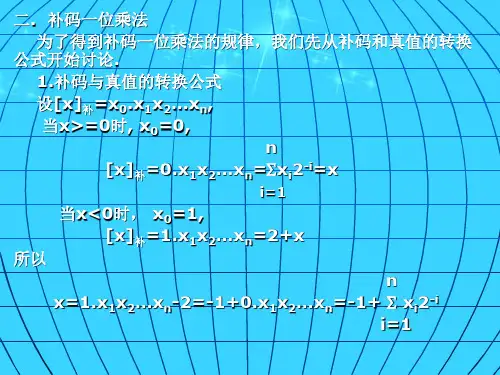

2.3.2 补码乘法[1]作者:pz整理来源:网络2010年4月2日发表评论进入社区2.3.2补码乘法1.补码与真值得转换公式补码乘法因符号位参与运算,可以完成补码数的“直接”乘法,而不需要求补级。

四位补码的表示范围摘要:一、补码的概念与作用二、四位补码的表示范围1.正数的表示2.负数的表示3.零的表示三、四位补码的应用场景四、如何计算四位补码1.加法运算2.减法运算3.乘法运算4.除法运算五、四位补码的优缺点六、总结正文:一、补码的概念与作用补码是一种数字表示法,主要用于计算机系统中。

它可以简化加法和减法运算的处理过程,减少硬件设备的复杂性。

补码的作用是在计算机内部将有符号数和无符号数统一处理,便于运算和存储。

二、四位补码的表示范围1.正数的表示四位补码可以表示0到255之间的正整数。

例如,整数50的补码为0101,整数127的补码为1111。

2.负数的表示四位补码可以表示-128到-1之间的负整数。

例如,整数-50的补码为1110,整数-127的补码为1111。

3.零的表示零在四位补码中表示为0000。

三、四位补码的应用场景四位补码广泛应用于计算机硬件设备、嵌入式系统以及数字信号处理等领域。

在这些场景中,四位补码可以简化运算过程,提高运算速度和硬件设备的性能。

四、如何计算四位补码1.加法运算当进行加法运算时,先将两个补码数进行按位对齐,然后从最低位开始逐位相加。

若某位数相加结果大于等于2,则向高位进位1。

最后得到的结果即为两个补码数的和。

2.减法运算减法运算可以转化为加法运算。

将被减数的补码取反再加1,得到一个与被减数相同范围的补码。

然后与减数进行加法运算,遵循加法运算的规则。

3.乘法运算乘法运算可以采用按位乘法的方法,将两个补码数逐位相乘。

对于乘积的每一位,先计算两个乘数的对应位相乘的结果,然后根据乘数的符号位确定乘积的符号。

4.除法运算除法运算可以转化为多次加法运算。

先将被除数的补码与除数的补码进行多次加法运算,直到被除数的补码小于除数的补码。

然后将得到的结果作为商,再将除数的补码与商的补码进行加法运算,直至结果小于等于除数。

五、四位补码的优缺点优点:简化加法和减法运算,降低硬件设备复杂性。

补码乘法因符号位参与运算,可以完成补码数的“直接”乘法,而不需要求补级。

这种直接的

方法排除了较慢的对2求补操作,因而大大加速了乘法过程。

首先说明与直接的补码乘法相联系数学特征。

对于计算补码数的数值来说,一种较好的表示

方法是使补码的位置数由一个带负权的符号和带正权的系数。

今考虑一个定点补码整数

[N]补=a n-1a n-2…a1a0,这里a n-1是符号位。

根据[N]补的符号,补码数[N]补和真值N 的关系

可以表示成:

N=

n-2

+∑a i2i当a n-1= 0([N]补为正)时i=0

n-2

-[1+∑(1-a i)2i] 当a n-1= 1([N]补为负)时i=0

如果我们把负权因数-2n-1强加到符号位a n-1上,那么就可以把上述方程组中的两个位置

表达式合并成下面的统一形式:

(2.29)

(2.30) [例19] 已知: [N]补= 01101,[-N]补=10011,求[N]补,[-N]补具有的数值。

[解:]

常规的一位全加器可假定它的3个输入和 2个输出都是正权。

这种加法器通过把正权或

负权加到输入/输出端,可以归纳出四类加法 单元。

如右表,0类全加器没有负权输入; 1类全加器有1个负权输入和2个正权输入;依次类推。

对0类、3类全加器而言有:

S =XYZ +XYZ +XYZ +XYZ C =XY +YZ +ZX 对1类、2类全加器,则有

S =XYZ +XYZ +XYZ +XYZ

C =XY +XZ +YZ

表2.3 四类一般化全加器的名称和逻辑符号 注意,0类和3类全加器是用同一对逻辑方程来表征的,它和普通的一位全加器(0类)是一致

的。

这是因为3类全加器可以简单地把0类全加器的所有输入输出值全部反向来得到,反之亦然。

1类和2类全加器之间也能建立类似的关系。

由于逻辑表达式具有两级与一或形式,可以用

“与或非”门来实现,延迟时间为2T 。

利用混合型的全加器就可以构成直接补码数阵列乘法器。

设被乘数A 和乘数B 是两个5位的二 进制补码数,即

A =(a 4)a 3a 2a 1a 0

B=(b

4

)a3a2a1a0

它们具有带负权的符号位a4和b4,并用括号标注。

如果我们用括号来标注负的被加项,例如

(a i b J),那么A和B相乘过程中所包含的操作步骤如下面矩阵所示:

(a4) a3a2a1

a

=A

×) (b4)b3b2b1

b0=B

(a4b0) a3b0 a1b0a1b0a0b0

(a4b1)a3b1 a2b1 a1b1a0b1

(a4b2) a3b2a2b2 a1b2a0b2

(a4b3) a3b3a2b3a1b3a0b3

+) a4b4(a3b4) (a2b4) (a1b4) (a0b4)

p 9 p

8

p

7

p

6

p5 p

4

p

3

p2 p

1

p

=P

5位乘5位的直接补码阵列乘法器逻辑原理演示

其中使用不同的逻辑符号来代表0类、1类、2类、3类全加器。

2类和1类全加器具有同样的结

构,但是使用不同的逻辑符号可使乘法阵列的线路图容易理解。

在n位乘n位的一般情况下,该乘法器需要(n-2)2个0类全加器,(n-2)个1类全加器,(2n-3)

个2类全加器,1个3类全加器,总共是n(n-1)个全加器。

故所需的总乘法时间是:

tp=Ta+2(n-1)Tf=2T+(2n-2)2T=(4n-2)T

(2.31)

[例20]设[A]补=(01101)2,[B]补=(11011)2,求[A×B]补=?。