C8051F34X-注解

- 格式:doc

- 大小:530.00 KB

- 文档页数:9

C8051F单片机使用注意事项C8051F单片机使用注意事项由于C8051F单片机是3.3V低功耗、高速单片机,与大家过去应用传统的5V供电低速单片机在引脚处理与PCB布板方面会有一些区别,我们总结了这方面的经验,提供给大家,以避免在应用设计上走弯路。

一、电源和地线方面的处理1、模拟电源和数字电源要分别供电,可以使用两个稳压源分别供电,但是两个电源之间的电压差必须满足数据手册中的规定(<0.5V,小于0.3V是比较理想的)。

实际应用中模拟电源和数字电源可以来自同一个稳压器的输出,只在AV+与VDD之间接简单的滤波器也是很有效的。

这里要加一个小电感,也可以用低阻值的电阻(通常2欧姆,电阻要有足够的寄生电感。

) 这种方式既能降低成本又能减少体积。

(关于这一点可以参考C8051F各种目标板的原理图的电源部分)。

2、在地线方面,模拟地和数字地要分开布线,然后在一点通过磁珠连接,在实际应用中也可以使用0欧姆绕线电阻连接的。

该绕线电阻要有寄生电感,另外,在布线时一定要注意地线应该尽可能的粗,或者采用大面积覆地,电源线也要尽量粗,并且在单片机所有电源和地之间以及每个外围集成电路的VDD和GND间加去耦合电容。

3、如果所使用的器件上有模拟电源,模拟地,数字电源和数字地,所有这些引脚不可以悬空,必须连接。

二、在严酷环境下使用C8051F器件时,在PCB设计时应注意那些问题?在严酷条件下使用C8051F器件时,我们提供给您的一般性建议如下:1) 在器件的每个电源引脚处放置0.1μF和1.0μF的去耦电容,而且要尽可能地靠近芯片。

这一点适用于板上所有的IC(集成电路)。

*2) 尽可能将板上不使用的空间接地,即所谓的大面积覆铜。

3) 在靠近器件外部振荡器引脚处放置外部晶体和其他振荡器元件(如果可行的话)。

4) 使用最短的连线以避免产生“天线”,尤其在下列引脚处:/RST,MONEN,XTAL1,XTAL2,TMS,TCK,TDI和TDO。

![[知识]C8051F单片机仿真器及开发板常见问题解答](https://img.taocdn.com/s1/m/82b7b1ce185f312b3169a45177232f60ddcce795.png)

C8051F单片机仿真器及开发板常见问题解答问题1:为什么我用你们的例程显示自己提取的汉字字模在液晶屏上显示乱码?答:字模的提取是有顺序的。

以ML-F020DK+开发板使用的16X16汉字字模为例,字模的提取顺序是先左后右、先上后下、纵向8点、下高位、的顺序提取的。

新的字模也要按照这个顺序,否则会显示乱码。

问题2:为什么我在做液晶显示的硬件仿真的时候正常,在实际运行的时候却是乱码?答:MCU在仿真的时候的速度和实际运行的速度是有细小差异的。

适当增加对LCD操作的时间间隔,延缓对LCD的操作速度。

问题3:为什么ML-F020DK+、 ML-F120DK+开发板以及ML-F020ICB工业测控板等C8051F系列MCU为核心的目标板无法使用其他公司的C8051F仿真器?答:ML-EC3的驱动能力比较强,所以可以对这些带抗干扰处理的目标板进行正常的仿真调试及程序下载。

如使用其他公司的仿真器,请将这些目标板的JTAG中的TMS、TDO、TDI三条走线上的下拉电阻取掉。

调试完毕或下载完毕后再复原。

问题4:如何对C8051F芯片加密?答:C8051F系列的芯片加密有两种方式:1、程序中通过设置相应的寄存器进行加密;2、专用程序下载软件的加密方式下载。

第一种方式请参考Datasheet,第二种方式在下载的时候选中相应的复选框后下载即可。

问题5:C8051F芯片加密后还能再擦除吗?还能再下载程序调试吗?答:可以擦除。

擦除后可继续使用。

问题6:如何擦除加密后的芯片?答:使用SILABS的程序下载软件Flash Programming Utility 2.51擦除加密后的MCU。

具体做法是:仿真器连接好计算机和目标板,目标板上电(此时保证有且只有Power指示灯是亮的)。

在FlashProgramming Utility 2.51软件的Flash Erase页中点击Erase Code Space按键进行擦除。

详细的芯片资料请参考Datasheet。

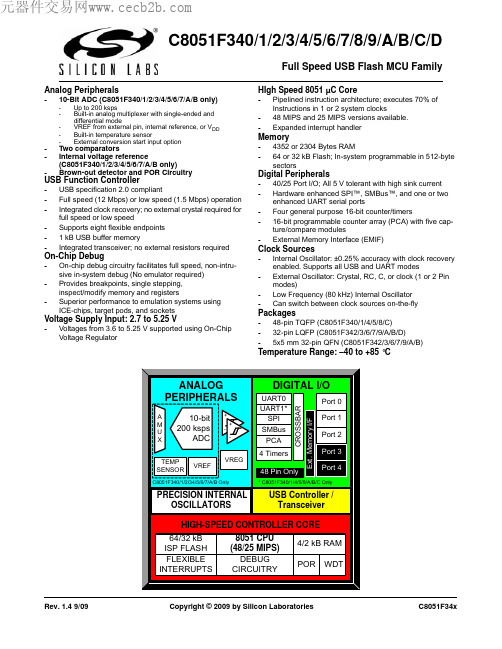

C8051F系列[编辑本段]C8051F系列CygnalC8051F(已被Silicon Lab收购)系列单片机是真正能独立工作的片上系统SOCCPU有效地管理模拟和数字外设可以关闭单个或全部外设以节省功耗FLASH存储器还具有在系线重新编程的能力即可用作程序存储器又可用作于非易失性数据存储应用程序可以使用MOVC和MOVX指令对FLASH进行读或改写。

一.Cygnal C8051F系列单片机特点1.片内资源8~12位多通道ADC1~2路12位DAC1~2路电压比较器内部或外部电压基准内置温度传感器±316位可编程定时/计数器阵列PCA可用于PWM等3~5个通用16位定时器8~64个通用I/O口带有I2C/SMBusSPI1~2个UART多类型串行总线8~64K Flash存贮器256~4K数据存贮器RAM片内时钟源内置电源监测看门狗定时器2.主要特点高速的20MIPS~25MIPS与8051全兼容的CIP51内核内部Flash存贮器可实现在系统编程即可作程序存贮器也可作非易失性数据存贮工作电压为2.7V~3.6V典型值为3VI/ORSTJTAG引脚均允许5V电压输入全系列均为工业级芯片-45℃~+85℃片内JTAG仿真电路提供全速的电路内仿真不占用片内用户资源支持断点单步观察点运行和停止等调试命令支持存贮器和寄存器校验和修改二.有关C8051F系列CPU1.与标准8051完全兼容Cygnal C8051F系列单片机采用CIP51内核Cygnal专利与MCS51指令系统全兼容可用标准的ASM51Keil C高级语言开发编译C8051F系列单片机的程序2.高速指令处理能力标准的8051一个机器周期要占用12个系统时钟周期执行一条指令最少要一个机器周期CygnalC8051F系列单片机指令处理采用流水线结构机器周期由标准的12个系统时钟周期降为1个系统时钟周期指令处理能力比MCS51大大提高CIP-51内核70% 的指令执行是在一个或两个系统时钟周期内完成只有四条指令的执行需4个以上时钟周期CIP-51指令与MCS51指令系统全兼容共有111条指令3.增加了中断源标准的8051只有7个中断源Cygnal C8051F系列单片机扩展了中断处理这对于时实多任务系统的处理是很重要的扩展的中断系统向CIP-51提供22个中断源允许大量的模拟和数字外设中断一个中断处理需要较少的CPU干预却有更高的执行效率4.增加了复位源标准的8051只有外部引脚复位Cygnal C8051F系列单片机增加了7种复位源使系统的可靠性大大提高每个复位源都可以由用户用软件禁止1 片内电源监视2 WDT看门狗定时器3 时钟丢失检测器4 比较器0输出电平检测5 软件强制复位6 CNVSTRAD转换启动7 外部引脚RST复位可双向复位8 提供内部时钟源标准的8051只有外部时钟Cygnal C8051F系列单片机有内部独立的时钟源C8 051F300/F302提供的内部时钟误差在2%以内在系统复位时默认内部时钟如果需要可接外部时钟并可在程序运行时实现内外部时钟的切换外部时钟可以是晶体RCC或外部时钟以上的功能在低功耗应用系统中非常有用。

1. 配置端口引脚为数字输入:通过设置输出方式为“漏极开路”并向端口数据寄存器中的相应位写‘1’(禁止低端输出驱动器)将端口引脚配置为数字输入。

例如,设置P3MDOUT.7 为逻辑‘0’并设置P3.7 为逻辑‘1’即可将P3.7 配置为数字输入。

2.配置P1端口的引脚为模拟输入注意: 通过向P1MDIN寄存器中的对应位写‘0’即可将端口引脚配置为模拟输入.(端口中仅P1可以作为模拟输入,所以它有输入方式寄存器) 被配置为模拟输入的引脚的输出驱动器并没有被明确地禁止。

因此被配置为模拟输入的引脚所对应的P1MDOUT位应被明确地设置为逻辑‘0’(漏极开路方式),对应的端口数据位应被设置为逻辑‘1’(高阻态)。

还需要注意的是,将一个端口引脚用作ADC2 模拟多路开关的输入时并要求将其配置为模拟输入,但强烈建议这样做。

3. 配置端口的引脚为输出方式: 每个端口引脚的输出方式都可被配置为漏极开路或推挽方式。

在推挽方式,向端口数据寄存器中的相应位写逻辑‘0’将使端口引脚被驱动到GND,写逻辑‘1’将使端口引脚被驱动到VDD。

在漏极开路方式,向端口数据寄存器中的相应位写逻辑‘0’将使端口引脚被驱动到GND,写逻辑‘1’将使端口引脚处于高阻状态.注意:不管交叉开关是否将一个端口引脚分配给某个数字外设,端口引脚的输出方式都PnMDOUT寄存器控制。

例外情况是:连接到SDA、SCL、RX0(如果UART0 工作于方式0)、RX1(如果UART1工作于方式0)的端口引脚总是被配置为漏极开路输出,而与PnMDOUT 寄存器中的对应位的设置值无关。

4.上电和PLL 初始化为了在器件上电后设置和使用PLL 作为系统时钟,应遵循下列步骤:1.确保要使用的参考时钟(内部或外部)处于稳定运行状态。

2.设置PLLSRC 位(PLL0CN.2),为PLL 选择时钟源。

3.将FLASH 读定时控制位FLRT(FLSCL.5-4)编程为适合于新时钟频率的值(见15. FLASH 存储器)。

C8051F320/1有一个可编程内部振荡器、一个外部振荡器驱动电路和一个4倍时钟乘法器。

系统时钟(SYSCLK)可以来自内部振荡器、外部振荡器电路或4倍时钟乘法器二分频。

USB时钟(USBCLK)可以来自内部振荡器、外部振荡器电路或4倍时钟乘法器。

可编程内部振荡器系统复位后内部振动器默认系统时钟并工作在1.5MHz。

两个寄存器:OSCICL(内部振荡器校准寄存器)和OSCICN(内部振荡器控制寄存器)。

OSCICL(内部振荡器校准寄存器)OSCICL复位值已经过工厂校准,对应的基频为12MHz,精度为±1.5%,该频率适合作为USB时钟。

软件可以下面所述修改内部振荡器的频率。

一般情况下是不用对OSCICL进行配置。

OSCICN(内部振荡器控制寄存器)IOSCEN:为内部振荡器使能位,0禁止,1使能,手册上写复位值为0,是错误的,应该为1,这样,复位后系统时钟默认为内部振荡器。

IFCN1-0:内部振荡器分频选择,复位后为00,系统默认为1.5MHz内部振荡器初始化OSCICN |= 0x03; //内部振荡器输出为12MHz程序也可以这样写OSCICN = 0x83;//内部振荡器输出为0x83——12MHz; 0x82——6MHz;0x81 3MHz当程序没有对振荡器初始化时,默认系统时钟采用内部振荡器,并运行在1. 5MHz频率下。

OSCICN = 0x83;外部振荡器驱动电路外部振荡器电路可以驱动外部晶体、陶瓷谐振器、电容或RC网络和外部C MOS时钟提供系统时钟。

当使用外部振荡器电路时,必须对所用端口引脚进行配置。

端口I/O交叉开关应被配置为跳过被振荡器占用的引脚。

当外部振荡器电路被配置为CMOS时钟方式时,端口引脚P0.3被用作X TAL2。

当外部振荡器电路被配置为晶体/谐振器方式时,端口引脚P0.2和P0.3分别被用作XTAL1和XTAL2当外部振荡器电路被配置为RC方式时,端口引脚P0.3被用作XTAL2。

C8051F单片机开发工具使用及常见故障排除V1.0新华龙电子有限公司 1 目 录1. 相关基本知识介绍及相关基本知识介绍及正确正确正确操作操作操作流程流程1.1. 调试器的作用与种类 1.2. 调试器接口1.3. 软件的种类与特色 1.4. 不同软件的不同设方法 1.4.1. IDE 1.4.2. KEIL1.5. 目标板接口 1.6. 连接流程2. 常见问题问答2.1. 软件问题2.1.1. 软件版本问题 2.1.2. 软件设置 2.2. 调试器问题 2.3. 目标板问题 2.4. USB 连接线问题 2.5. 10芯扁平线问题 2.6. 操作流程问题3. 使用特例4. 附件4.1. 调试器图片4.2. 软件下载及查找路径 4.2.1. IDE4.2.2. KEIL 环境下驱动 4.2.3. Flash Programming 4.2.4. Production Programmer 4.2.5. USB Reset4.3. 调试器接口描述 4.3.1. USB 接口 4.3.2. C2接口 4.3.3. JTAG 接口5. 其他其他::版本更新说明新华龙电子有限公司2 调试器的正常使用,会涉及诸多因素,比如,上位机软件的设置恰当与否,调试器本身的状态良好与否,目标板接口电路正确与否,甚至包括USB 连线、10芯扁平线是否良好连接等,都会直接影响调试或下载工作是否能够正常进行。

图 1-1 调试器连接示意图本文以调试器为中心,详细介绍其使用及在使用过程中、与其相关的软件、目标板等,并以问答形式,重点列举了在使用过程中可能出现的故障以及故障的排除方法。

1 相关基本知识介绍及正确操作流程1.1. 调试器的作用与种类应用于C8051Fxxx MCU 的调试器,区别传统的仿真器,其可执行在线调试、在线编程、在线擦除代码等动作,除用于开发调试,也可用于生产下载。

作为资深代理商,新华龙电子有限公司前后共推出多种型号:U-PDC ,U-EC3,U-EC5,以及最近新推出的U-EC6等。

C8051F34X (C8051F34X.pdf) 10-Bit ADCWhen in Single-ended Mode, conversion codes are represented as 10-bit unsigned integers. Inputs are measured from …0‟ to VREF x 1023/1024. 设置为单端模式时,转换的结果是10位的无符号整数,输入电压被转换为从0到VREF x 1023/1024之间。

When in Differential Mode, conversion codes are represented as 10-bit signed 2‟s complement numbers. Inputs are measured from –VREF to VREF x 511/512.设置为查分模式时,转换结果是10位的带符号整数,输入电压被转换为从–VREF 到VREF x 511/512之间。

When the CNVSTR input is used as the ADC0 conversion source, the associated Port pin should be skipped by the Digital Crossbar. 当CNVSTR作为启动ADC的信号时,交叉开关应该跳过对应的管脚。

Window Detector的使用原则:只要ADC0<ADC0LT,或者ADC0>ADC0GT,就会置位AD0WINT(ADC0 Window Compare Interrupt Flag),如果使能了对应的中断,就会产生中断请求。

根据以上使用原则,Window Detector主要有两种使用方法:一是控制采集电压在某一闭合区间,如果不在该区间则报警,如下图左边所示;二是控制采集电压不再某一闭合区间,如果进入该区间则报警,如下图右边所示。

一定要注意ADC0LT和ADC0GT的格式要与ADC0的格式相同。

SAR Conversion Clock的最高频率为3MHz,要通过ADC0CF将系统时钟分频到该范围内;转换所需的时间最少是10个转换时钟周期,至多是14个转换时钟周期。

Temperature SensorV TEMP = (Gain x Temp) + OffsetTemp= (V TEMP - Offset) / GainGain:2.86 mV/°CGain Error:±33.5 μV/ºCOffset(Temp = 0 °C):776 mVOffset Error:±8.51 mV使用VDD作为ADC的参考电压,由于VDD电压波动较大,会产生较大的误差,使温度传感器转换出来的温度误差很大。

如果对精度要求较低,可以使用片上的电压基准源(精度为2.4%)作为参考电压,可以获得一定的精度;如果需要较高的精度,需要使用片外高精度的电压基准源(如REF1112,精度0.2%);如果需要更高的精度,就需要使用独立的温度传感器(如DS18B20,分辨率为0.5摄氏度)。

V oltage ReferenceThe REFSL bit in the Reference Control register (REF0CN) selects the reference source. For the internal reference or an external source, REFSL should be set to …0‟; For V DD as the reference source, REFSL should be set to …1‟. REF0CN中的REFSL位决定了选中的参考源。

如果是用内部或者外部参考源,REFSL需要清零,如果选用VDD作为参考源,则要置位REFSEL。

The BIASE bit enables the internal ADC bias generator, which is used by the ADC and Internal Oscillator. This enable is forced to logic 1 when either of the aforementioned peripherals is enabled.The Reference bias generator (see Figure 6.1) is used by the Internal V oltage Reference, Temperature Sensor, and Clock Multiplier. The Reference bias is automatically enabled when any of the aforementioned peripherals are enabled. BIASE位使能供ADC和内部振荡器使用的内部ADC 偏压源。

如果ADC或内部振荡器已经被使能,那么该位被强制置1。

参考偏压源用于内部电压参考源、温度传感器和时钟倍频器,只要上述三种外设有一种启用,该偏压源就会被使能。

The output voltage of internal reference is: 2.38-2.44-2.50V(精度为2.4%)。

Port Input/Output1: Logic High Output (high impedance if corresponding P0MDOUT.n bit = 0).当向某一管脚对应的寄存器位写入1(比如P0.1 = 1),而该管脚设置为开漏输出模式(比如P0MDOUT.1 = 0)时,该管脚当前的状态即为高阻态。

When a pin is configured as an analog input, its weak pull-up, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is notrecommended. Additionally, all analog input pins should be configured to be skipped by theCrossbar. 当某一管脚配置为模拟输入时,对应的弱上拉、数字驱动和数字输入都被禁止,这样可以降低功耗,并减少模拟输入上的噪声。

已经配置为数字输入的引脚,仍然可以被模拟外设使用,但是我们不建议这样做(不知道这么干会有什么后果?不过估计没有特殊情况谁也不会这么干)。

另外,交叉开关要跳过所有配置为模拟输入的管脚。

Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is …0‟, a weak pull-up is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pull-up is turned off on an output that is driving a …0‟ to avoid unnecessary power dissipation.每个输出驱动均可配置为弱上拉或者推挽模式,即使通过XBRn选中的数字外设资源也不例外,因为这种配置不是自动的。

但是SMBus的两个管脚SDA和SCL例外,它们总是会被自动配置为开漏模式,而不管PnMDOUT的设置(因为I2C 总线协议中要求SDA和SCL必须是开漏的)。

当XBR1的WEAKPUD位清零时,所有被配置为开漏的管脚都会被加上弱上拉,但是不会影响配置为推挽模式的管脚。

此外,在管脚输出低电平时,对应的弱上拉会被关掉,以避免不必要的功率消耗。

F340的P4口是不能位寻址的,只能统一访问,不能单独访问其中某个位,如P4^3是非法的。

如果想单独控制P4口的某一个位的电平,可以有两种方法:一是使用位段,即将P4 口的每一个位定义为一个位段;二是使用位运算,比如要置位P4.5,就使用P4 |= 0x10,要清零就使用P4 &= ~0x10。

F340的管脚如果配置为Open-Drain(开漏)模式,则驱动能力很差,而且不能够输出足够好的方波(用原来的开发板试过,上升时间最少需要3uS),估计如果在开漏的管脚上加上拉会改善上升沿,减少上升时间;如果配置为Push-Pull(推挽)模式,由于驱动能力增大,则可以产生足够好的方波(上升时间最短只有2ns);如果将内部的弱上拉关掉,那么输出的电平将不确定,由后级负载决定。

下面是测试结果:开漏模式,上升时间有13.68us之多,已经不是方波了(频率为10.42KHz)推挽模式,上升时间只有41.9ns,(频率为228.1KHz)对已经配置为SPI,I2C或UART的管脚,不能通过直接控制相关寄存器的方式(如P1.3)改变管脚电平!指令集Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. 对于条件跳转指令,跳转发生要比不发生多消耗一个时钟周期。

In the typical configuration, the external interrupt pin should be skipped in the crossbar and configured as open-drain with the pin latch set to '1'. 典型的设置是,交叉开关要跳过外部中断的引脚,并将该引脚设置为开漏模式。